Beruflich Dokumente

Kultur Dokumente

JESTR Squaring CKT

Hochgeladen von

Pradeep SinglaOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

JESTR Squaring CKT

Hochgeladen von

Pradeep SinglaCopyright:

Verfügbare Formate

Jestr

JOURNAL OF

Journal of Engineering Science and Technology Review 7 (3) (2014) 50 54

Engineering Science and

Technology Review

Research Article

www.jestr.org

Reversible Squaring Circuit for Low Power Digital Signal Processing

Pradeep Singla1,* and Devraj Gautam2

Deptt. Of

Deptt. Of Elect. & Comm., Dronacharya Group of Institutions, Greater Noida, India

Elect. & Comm., Ambedkar Institute of advanced Communication Technologies & Research, New Delhi, India

Received 15 October 2013; Accepted 2 June 2014

___________________________________________________________________________________________

Abstract

With the high demand of low power digital systems, energy dissipation in the digital system is one of the limiting factors.

Reversible logic is one of the alternate to reduce heat/energy dissipation in the digital circuits and have a very significant

importance in bioinformatics, optical information processing, CMOS design etc. In this paper the authors propose the

design of new 2- bit binary Squaring circuit used in most of the digital signal processing hardware using Feynman &

MUX gate. The proposed squaring circuit having less garbage outputs, constant inputs, Quantum cost and Total logical

calculation i.e. less delay as compared to the traditional method of squaring operation by reversible multiplier. The

simulating results and quantized results are also shown in the paper which shows the greatest improvement in the design

against the previous methodology.

Keywords: Reversible logic, quantum cost, garbage outputs, Total logical calculation, constant inputs, MUX gate, Feynman gate.

__________________________________________________________________________________________

1. Introduction

Todays humans life cannot be imagine without the digital

electronic systems. There are endless examples of electronic

systems hardware can be found all around us: Radios,

computer systems, compact displayer, telephone systems,

video games, and microprocessor and digital watches- the

list seems to be going forever! This rapid growth in the

electronic industries also forces to designer to struggle for

the designing of the efficient low power digital systems

because the power loss and the energy loss is one of the

limiting factor in the digital systems [10]. The logic design

and the switches are the two main contributor of energy or

power loss in the digital systems [4][5][7][9]. Even if Rolf

Landauer in 1961 predicted that the irreversible logical

computation device designed by the conventional approach

having an entropy gain is S= K ln W. where W=2N, the

number of states [1]. The entropy of a system could be

defined as the ratio of heat to the temperature at which the

calculation is performed. So, by this we get the expression

for the energy or heat dissipation i.e. equal to the KT ln

2[1][4-11]. Where K is the Boltzmanns constant equal to

1.3806505 10-23 m2kg2k-1(J/K) and T is the temp. At which

the logical computation is performed. This dissipated energy

is directly correlated the number of lost bits [2]. On the other

hand, due to the switching action in the conventional

(irreversible) digital systems implemented by modern

CMOS technology consumes energy Esig = CV2 which is

the energy of the voltage-coded signal [7].

Furthermore, the co-founder of Intel (Gordon Moore)

stated that the processing power will double every 18

months, will stop functioning in the year 2010- 2020 called

Moores Law[4]. So, resultantly a new alternative approach

of designing the digital system has been arose with the

______________

* E-mail address: pradeepsingla7@gmail.com

ISSN: 1791-2377 2014 Kavala Institute of Technology. All rights reserved.

motto of reducing energy dissipation and subsequently

reducing the entropy increase called Reversible Logic

design. In 1973, C.H. Bennet showed that if the systems

designed by the reversible designing approach instead of the

conventional approach dissipated less heat or ideally no

heat[2][3].

Reversible logics use the charge recovery process to

save energy. These are the logic which does not loose

information. The reversible circuits are designed by the

special logical gates called reversible gates. Reversible logic

structure posses the property of one to one mapping between

the inputs and output state[4[[5][8][9] for the designing of

the reversible logic circuits there are two main conditions

has to be follows strictly[10]:

Fan-Out is not permitted

Feedback is not permitted

These reversible gates are having the very vast

applications in the field of quantum computing,

bioinformatics, CMOS designing optical computing etc.[9]

1.1 Motivation

The Arithmetic calculation is the one of the important part

of any of the digital hardware [11]. The squaring calculation

has its own advantages in different field like digital signal

processing: Convolution, deconvolution, cryptography etc.

where numbers of times we have to calculate fast square of

the number [12-13]. In order to calculate the square of the

binary numbers, there are number of faster reversible

multiplier by which we calculate the square of the numbers

[12]. The reversible multiplier proposes in the literature are

generally based on the recursive method [13]. But, to

designing of any of the digital hardware the circuit

complexity is one of the important measures which directly

correlate with the delay [4]. So, the main motivation behind

this work is to investigate the implementation of the efficient

Pradeep Singla and Devraj Gautam/Journal of Engineering Science and Technology Review 7 (3) (2014) 50 54

and low power squaring circuit architecture for the digital

hardware industries. In this paper, we are proposing a

reversible squaring circuit for the fast squaring calculation

instead of using multiplier for the squaring which increases

the complexity and the delay in the circuit. The proposed

circuit is much effective and having less complexity and the

less delay as compared to multiplier used for the squaring.

For the simplicity for the readers, we are proposing a 2 2

squaring circuit which can perform two bit square operation

and showing the results that this proposed architecture is

much efficient as compare to the square operation performs

by the reversible multiplier.

This paper is organizes in such a manner that the section

2 will provide the basic information about the reversible

logics. The logic configuration of the MUX gate, MUX gate

as a half adder and the Feynman gate is describes in this

section. Section3 will give the proposed architecture of the

reversible squaring circuit with the traditional reversible

multiplier. The section 4 will give the simulation results and

the quantized results for the proposed architecture against

the reversible multiplier for squaring computation. Last

section will provide the conclusion about the paper.

2.1 MUX gate [5]:

Fig.1 shows the pictorial representation of 33 reversible

gate called MUX (MG) gate. It is a conservative gate having

three inputs (A, B, C) and three outputs (P, Q, R). The

outputs are defined by P=A, Q=A XOR B XOR C and R=

AC XOR AB. The hamming weight of its input vector is

same as the hamming weight of its output vector and its

Quantum cost is 4.

P=A

A

B

Q=A XOR B XOR C

MG

R=A'C XOR AB

Fig.1. 33 MUX gate

2.1.1 MUX gate as Half Adder

The structure of MUX gate as Half adder is shown in the

fig1.1. If we provide 0 at third input C then the output Q

will provide the Sum of the half adder and R will provide

the AND combination of first & second input or Carry

output for the half adder.

1. Background of the Reversible Logics

The Reversible gates are the gates which have the same

numbers of inputs and outputs and for each input pattern

there must be a unique pattern. Thus, the reversible logics

has one to one mapping between their inputs and outputs[3].

So, to represent the N N reversible gate,

IV = (I1, I2, I3, IN)

P=A

MG

Ov = ( O1, O2,O3., ON)

R=AB

Where Iv and Ov are the input and output vectors

respectively. The conventional logic gates are irreversible

gate because the input and the output vector are not same.

The conventional inverter is the reversible gate[7].

For the reversibility in a circuit, not only logical but also

be physical reversibility must be present. The physically

reversibility means, the systems must be able to run

backward i.e. the input can be retrievable by the output [6].

Along with the design conditions, there are some main

measures of the reversible logics. However, the main

parameter in the convention or irreversible designs is

numbers of logic gate used. Unlike of convention logics, the

reversible gate has different parameters as follows[8][9]:

Q=A XOR B

Fig1.1. MUX gate as Half Adder

2.2 Feynman Gate [4]

Fig.2 shows the 22 reversible gate called Feynman gate.

Feynman gate is also recognized as controlled- not gate

(CNOT). It has two inputs (A, B) and two outputs (P, Q).

The outputs are defined by P=A, Q=A XOR B .This gate

can be used to copy a signal. Since fan-out is not allowed in

reversible logic circuits, the Feynman gate is used as the

fan-out gate to copy a signal. Quantum cost of a Feynman

gate is 1.

QC (Quantum cost) [6]: The number of reversible gates

(11 or 22) to realize the circuit is known as quantum

cost,

(CI) Constant inputs [6]: The number of inputs that are

kept constant (0 or 1) for synthesis the given functions,

GO (Garbage outputs) [6]: The number of outputs that

are not primary is known as Garbage outputs

Total logical calculation (T): Total logical calculation is

the count of the XOR, AND, NOT logic in the output

circuit [4].

P=A

Feynman

Gate

Q=A XOR B

Fig.2. 22Feynman gate structure

There are several reversible logic gates have been

proposed in the last years such as: Feynman gate [4],

Fredkin gate [8], Peres gate [9] Toffolli gate [3], Mux gate

[5] etc. Here we are reviewing the two gates i.e. Feynman,

and MUX gate because these gates are used in the targeted

design.

2.2.1 Feynman gate as Data Copier & as NOT gate[4]

The structure of Feynman gate as Data Copier & as NOT

gate is shown in the fig 2.1 & 2.2 resp.If we provide 0 at

second input B then the output Q will provide the copy of

51

Pradeep Singla and Devraj Gautam/Journal of Engineering Science and Technology Review 7 (3) (2014) 50 54

first input and if we If we provide 1 at second input B then

the output Q will provide the complement of the first input.

A

Feynman

Gate

0

O2 ( 1-bit) = A1B1+ O1+ C1 ( carry from O1)

O3 ( 1-bit) = C2 ( carry from O2)

A

Feynman

Gate

Fig 2.1. Feynman gate as Data copier

2. Proposed Architecture

Squaring Circuit

A'

Fig.2.2 Feynman gate as NOT

gate

of

New

Reversible

The Multiplication of the binary number is the basically a

recursive addition of the bits[8]. The reversible multiplier

which was discussed in the literature is used for the squaring

of the binary numbers. But in this paper, by seeing the use of

the binary square calculation in the different field, we

present the design of the reversible squaring circuit with the

aim of the optimizing hardware complexity to make it more

economical in terms of garbage outputs, constant inputs and

total logical calculations without losing the bits.

Fig 3(b) gate level logical diagram by using the MUX gate

3.1 Design of 2 2 reversible binary multiplier

The traditional reversible multiplier is used for the squaring

calculation of the bits.The fig.3(a) and fig 3(b) Shows the

2 2 reversible binary multiplier Block diagram and the

gate level logical diagram by using the MUX gate. In this

we uses feynman gate for copying the signal and avoiding

the feedback.

3.2 Design of 2 2 reversible binary multiplier

The fig.4(a) & fig 4(b) shows the 2 2 reversible binary

squaring circuit block diagram and gate level logical

diagram by Feynman and MUX gate.

Fig.4(a) 2 2 reversible binary squaring circuit block

diagram

Fig.3(a) 2 2 reversible binary multiplier Block diagram

In this, we have two bits number represented A1A0 & B1B0

then there is a ANDing of A0B0, A1B0, A0B, A1B1. The

Result O0 will be same as A0B0 and the O1 will be addition

of A1B0 and A0B1 through half adder , O2 will be the

addition of previous carry and the A0B1 through half adder

and the O3 will be the carry bit from that adder. This process

can be demonstrated as:

O0 ( 1-bit) = A0B0

O1 ( 1-bit) A1B0 + A0B1

Fig 4(b). Gate level logical diagram

52

Pradeep Singla and Devraj Gautam/Journal of Engineering Science and Technology Review 7 (3) (2014) 50 54

4.2.2 Number of Reversible Gates Used

As we have discussed previously, the delay in the

digital hardware is one of the limiting factor and this factor

is directly linked with the uses of the number of gates. So,

the number of reversible gates for the binary 22 reversible

multiplier for the squaring calculation is 4 Feynman gates

and 6 MUX gates. But the number of reversible gates for the

proposed 2-bit reversible squaring circuit is 2 Feynman

gates and 2 MUX gates.

3. Results

4.1 Simulation Results

The propose Reversible Squaring Circuit architecture

shown in previous section is implemented and resulted by

using VHDL and simulated in Xilinx ISE8.2i. For the

designing of the reversible squaring circuit we use the

structural and behavioral modeling. The VHDL codes for

the MUX gate and Feynman gate is written in behavioral

modeling and these gate are connected to each other by

structural modeling (port mapping)[14]. The simulated

results of the reversible squaring circuit can be seen in fig.5

4.2.3 Constant Inputs

The number of inputs that are kept constant (0 or 1) for

synthesis the given functions are constant inputs. The CI

produces the GO. So, it must be less for a pretty design of

the reversible circuit for producing secondary outputs (GO).

The number of constant inputs for the binary 22 reversible

multiplier for the squaring calculation is 10. But the number

of constant inputs for the proposed 2-bit reversible squaring

circuit 3

4.2.4 Garbage Outputs

The garbage outputs are the outputs which are not

primarily used or for a better designing of the reversible

circuit, the garbage outputs kept less as possible. So, the

number of garbage outputs for the binary 22 reversible

multiplier for the squaring calculation is 10. But the number

of garbage outputs for the proposed 2-bit reversible squaring

circuit 3

Fig.5.Simulated results of the reversible squaring circuit

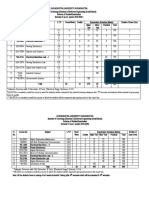

Table 1. Design Summery

Device Utilization

Parameters

(Spartan 3)

2-bit Squaring By

22 rev Multiplier

Proposed 2-bit rev

Squaring Circuit

Number of 4 I/p

LUTs

4/3840

2/3840

Number of slices

Number of bounded

IOBs

2/1920

8/173

4.2.5 Quantum Cost

As we have used Mux gate whose quantum cost is 4

and for Feynman gate the quantum cost is 1. So, if there is

m number of MUX gates used in the structure then

complete quantum cost becomes 4m and if there is f

number of Feynman gates used in the structure then

complete quantum cost becomes 1f. So, quantum cost for

the binary 22 reversible multiplier for the squaring

calculation is 4f+6m. But the quantum cost for the proposed

2-bit reversible squaring circuit is 2f+2m.

1/1920

6/173

4.2 Quantized evaluation of parameters in proposed

Reversible Squaring circuit

In case of reversible logic the important parameters are

total logical calculations, No. of gate used, Garbage outputs,

constant inputs and Quantum cost. These are calculated for

existing binary multiplier and for proposed squaring circuit

for the squaring operation. The comparative findings are

shown in table 2.

Table 2. Parameters comparison

Parameters

2-bit Squaring

By 22 rev

Multiplier

4 Feynman

6 MUX

Proposed 2-bit

rev Squaring

Circuit

2 Feynman

2 MUX

GO( Garbage

ouputs)

CI ( Constant

Inputs)

QC( Quantum Cost)

10

10

4f+6m =28

2f+2m =9

T(Total Logical

Calculation)

22 + 12+6

8 + 4+2.

Number of

Reversible Gates

4.2.1Total Logical calculation (T)

Assuming

= A two input XOR gate calculation

= A two input AND gate calculation

= A NOT gate calculation

T = Total logical calculation

The Total logical calculation is the count of the XOR,

AND, NOT logic in the output circuit. For example MUX

gate has three XOR gate and two AND gate and one NOT

gate in the output expression. Therefore T(!) = 3+2+.

In the binary 22 reversible multiplier for the squaring

calculation, the total number of logical calculation T is: T=

6 (3+2+)( for MUX gate)+ 41(for Feynman gate) =

22 + 12+6 and for proposed 2-bit reversible squaring

circuit , the total logical calculation T = 2 (3+2+)( for

MUX gate)+ 21(for Feynman gate) = 8 + 4+2.

So, by this calculation the total logical calculation for

the targeted number is less for the proposed design

Where f = No. of Feynman gates.

m = No. of Mux gates

This is the demonstration of the 2-bit squaring circuit.

For the higher bit quaking like for the 4- bit we have to use

only two 2- bit reversible squaring circuit and one 2 2

reversible multiplier instead of using four 2 2 reversible

multiplier and likewise for the 8-bit we have to use only two

4- bit reversible squaring circuit and one 4 bit reversible

multiplier.

53

Pradeep Singla and Devraj Gautam/Journal of Engineering Science and Technology Review 7 (3) (2014) 50 54

4. Conclusions

and hardware complexity as compared .The simulated

results of the proposed design is also shown which are

completely verified and correct in all sense. The design

summery is also shows the there is a saving of 50% in the 4

I/p LUTs and in number of slices with the 25% in the

bounded IOBs. Which shows that the proposed design have

high speed. So, the proposed design of squaring circuit is

highly efficient and we expect that, this work will definitely

provide a new approach for design of low power and speedy

squaring computing hardware for DSPs.

Squaring operation in the different field having their

own importance. The fast and efficient squaring calculation

is one of the demands in the convolution, de-convolution or

in other part of DSP. In this paper we emphasis on using

proposed hardware design low power Squaring circuit for

digital signal processing instead of multiplier for the

squaring operation. The proposed squaring circuit is much

cost efficient with the lesser garbage outputs, constant inputs

______________________________

References

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

11.

12.

13.

14.

R. Landauer, Irreversibility and heat generation in the

computational process, IBM J. Res. Develop., vol. 5, pp. 183-191,

1961.

C. H. Bennet, Logical reversibility of computation, IBM J. Res.

Develop., vol. 17, no. 6, pp. 525-532, 1973.

T.Toffoli.,

Reversible

Computing,

Tech

memo

MIT/LCS/TM-151,MIT Lab for computer science (1980).

Pradeep Singla, Naveen Kr. Malik, A cost- effective design of

reversible programmable logic array , International Journal of

computer application, vol 15., pp41-46, April-2012.

Abu Sadat Md.Sayem and Sajib Kumar Mitra, Efficient approach

to design low power reversible logic blocks for fieldprogrammable

gate arrays978-114244-8728-8/11/IEEE 2011

G.De Mey and A.De Vos, The minimum energy for a one bit

computation: a proof of the Landauer limit, proc.26th international

conf. On microelectronics IEEE, 2008.

Michael P.Frank, Introduction to reversible computing: motivation,

progress, and challenges, proceedings of 2nd international

conference on computing frontiers ACM newyork, 2005

Majid Haghparast, Majid Mohammadi, Mohammad Eshghi,

optimized reversible Multiplier circuit, Journal of circuits, system

and computers, pp 1-13.

H.R.Bhagyalakshmi, M.K.Venkeatesha, An improved design of a

multiplier using reversible logic gates, International journal of

engineering science and technology, vol.2 (8), pp.3838-3845, 2010

Ahsan Raja chowdhury,Rumana Nazmul,Hafiz Md.Hasan babu, A

new approach to synthesis multiple-output functions using

reversible programmable logic array proceedings of the 19th

international conference on vlsi design., 1063-9667,2006.

Madhumita mahapatro, M. suresh, Design of arithmatic circuits

using reversible logic gates and power dissipation calculation,

International Symposium on Electronic system design, IEEE 2010.

Prabha S. Kasiwal, B.P. Patil, D.K. Gautam, Performance

evaluation of squaring operation by Vedic mathematics, IETE

journal of Research, Vol 57, pp 39-41.

Kabiraj Sethi, Rutuparana Panda, An improved Squaring circuit

for binary numbers, International Journal of advance computer

science and applications, vol 3. No.2, pp111-116.

J. Bhasker, A VHDL Primer, Third edition, Pearson education.

54

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- ModuleDokument22 SeitenModulesugiartoNoch keine Bewertungen

- Ger 3620Dokument56 SeitenGer 3620pakistaniNoch keine Bewertungen

- Signal and SystemDokument1 SeiteSignal and SystemPradeep SinglaNoch keine Bewertungen

- ControlDokument1 SeiteControlPradeep SinglaNoch keine Bewertungen

- Energies 12 01822Dokument22 SeitenEnergies 12 01822Pradeep SinglaNoch keine Bewertungen

- Citizen Registration and Appointment For Vaccination User ManualDokument14 SeitenCitizen Registration and Appointment For Vaccination User ManualSahilNoch keine Bewertungen

- Entropy: Deep Residual Learning For Nonlinear RegressionDokument14 SeitenEntropy: Deep Residual Learning For Nonlinear RegressionPradeep SinglaNoch keine Bewertungen

- Apiit S.D. India, Panipat Apiit S.D. India, Panipat: Sessional - I Sessional - IDokument1 SeiteApiit S.D. India, Panipat Apiit S.D. India, Panipat: Sessional - I Sessional - IPradeep SinglaNoch keine Bewertungen

- IMF3Dokument96 SeitenIMF3Pradeep SinglaNoch keine Bewertungen

- Data Regarding Ph.D. Scholars of ECE Department, DCRUST, Murthal-131039Dokument3 SeitenData Regarding Ph.D. Scholars of ECE Department, DCRUST, Murthal-131039Pradeep SinglaNoch keine Bewertungen

- A Study of Soft Computing TechniquesDokument19 SeitenA Study of Soft Computing TechniquesPradeep SinglaNoch keine Bewertungen

- TT Btech & Bca 21.12.2020Dokument78 SeitenTT Btech & Bca 21.12.2020Pradeep SinglaNoch keine Bewertungen

- Bca 2011-12 PDFDokument39 SeitenBca 2011-12 PDFfunny videosNoch keine Bewertungen

- 160 Credit MECHATRONICS SYLLABUS FIRST-EIGHT SEMDokument117 Seiten160 Credit MECHATRONICS SYLLABUS FIRST-EIGHT SEMPradeep SinglaNoch keine Bewertungen

- A Study of Soft Computing TechniquesDokument19 SeitenA Study of Soft Computing TechniquesPradeep SinglaNoch keine Bewertungen

- Recent Trends in Electric Power and Energy Systems-2020 (RTEPES-2020)Dokument1 SeiteRecent Trends in Electric Power and Energy Systems-2020 (RTEPES-2020)Pradeep SinglaNoch keine Bewertungen

- Electrical Machines - I: Electric Circuit TheoryDokument22 SeitenElectrical Machines - I: Electric Circuit TheoryPradeep SinglaNoch keine Bewertungen

- TTDokument4 SeitenTTPradeep SinglaNoch keine Bewertungen

- Prediction Error For Identified Model - MATLAB Pe - MathWorks IndiaDokument4 SeitenPrediction Error For Identified Model - MATLAB Pe - MathWorks IndiaPradeep SinglaNoch keine Bewertungen

- TT Btech & Bca 14.09.2020 OnlineDokument50 SeitenTT Btech & Bca 14.09.2020 OnlinePradeep SinglaNoch keine Bewertungen

- Prediction Error For Identified Model - MATLAB Pe - MathWorks IndiaDokument4 SeitenPrediction Error For Identified Model - MATLAB Pe - MathWorks IndiaPradeep SinglaNoch keine Bewertungen

- List of B.tech 8619 Students - (3RD Sem)Dokument2 SeitenList of B.tech 8619 Students - (3RD Sem)Pradeep SinglaNoch keine Bewertungen

- TTDokument2 SeitenTTPradeep SinglaNoch keine Bewertungen

- Annexure - A12 (Electrical & Electronics Engg - )Dokument6 SeitenAnnexure - A12 (Electrical & Electronics Engg - )Pradeep SinglaNoch keine Bewertungen

- Subject Code: Basic Electronics EngineeringDokument5 SeitenSubject Code: Basic Electronics EngineeringPradeep SinglaNoch keine Bewertungen

- How To Model Residual Errors To Correct Time Series Forecasts With PythonDokument22 SeitenHow To Model Residual Errors To Correct Time Series Forecasts With PythonPradeep SinglaNoch keine Bewertungen

- COM 205 Multimedia Applications: St. Joseph's College Fall 2004Dokument45 SeitenCOM 205 Multimedia Applications: St. Joseph's College Fall 2004loadaNoch keine Bewertungen

- Renewable Energy For Sustainable Growth Assessment: EditorsDokument2 SeitenRenewable Energy For Sustainable Growth Assessment: EditorsPradeep SinglaNoch keine Bewertungen

- On The Use of Wavelets Packet Decomposition For Time Series PredictionDokument12 SeitenOn The Use of Wavelets Packet Decomposition For Time Series PredictionPradeep SinglaNoch keine Bewertungen

- Time Series Forecasting Using Deep Learning - MATLAB & SimulinkDokument7 SeitenTime Series Forecasting Using Deep Learning - MATLAB & SimulinkPradeep SinglaNoch keine Bewertungen

- The 8051 Microcontroller: Introduction To MicrocontrollersDokument8 SeitenThe 8051 Microcontroller: Introduction To MicrocontrollersPradeep SinglaNoch keine Bewertungen

- Hargreaves Samani PDFDokument13 SeitenHargreaves Samani PDFAnonymous M0tjyWNoch keine Bewertungen

- INV - 2229 Failure of Exciter Gearbox (DF601V) of Sinter Screens at SP4 - 124048Dokument25 SeitenINV - 2229 Failure of Exciter Gearbox (DF601V) of Sinter Screens at SP4 - 124048ghanshyam chandrakarNoch keine Bewertungen

- P23-Gears Pumps Cataloque - v0.6 - NZDokument38 SeitenP23-Gears Pumps Cataloque - v0.6 - NZRogerio DiasNoch keine Bewertungen

- MCAT Chemistry ReviewDokument9 SeitenMCAT Chemistry ReviewStellaNoch keine Bewertungen

- Spwla 2014 HHHDokument12 SeitenSpwla 2014 HHHclimaco20Noch keine Bewertungen

- Higher Mathematics 1 (H & B)Dokument3 SeitenHigher Mathematics 1 (H & B)joseph.kabaso96Noch keine Bewertungen

- U (1) 'S and Charge: Department of Physics, University of Toronto, Toronto, Ontario, Canada M5S IA 7Dokument3 SeitenU (1) 'S and Charge: Department of Physics, University of Toronto, Toronto, Ontario, Canada M5S IA 7Catrina MatasarNoch keine Bewertungen

- Cows and ChickensDokument9 SeitenCows and Chickensapi-298565250Noch keine Bewertungen

- Low Stress Mechanical Properties of Woven Silk Fabrics (Part-1)Dokument6 SeitenLow Stress Mechanical Properties of Woven Silk Fabrics (Part-1)Mohammed Atiqul Hoque ChowdhuryNoch keine Bewertungen

- CFD Analysis: Project Presentation byDokument19 SeitenCFD Analysis: Project Presentation byAkshayBhutadaNoch keine Bewertungen

- BillDipenser NCR 5633Dokument166 SeitenBillDipenser NCR 5633Amanda Brown100% (1)

- Incorporating Surface Roughness Into DEM Models of Crushable SoilsDokument5 SeitenIncorporating Surface Roughness Into DEM Models of Crushable SoilsLivaniel Viveros RoseroNoch keine Bewertungen

- Steady Incompressible Flow in Pressure Conduits (PartB)Dokument21 SeitenSteady Incompressible Flow in Pressure Conduits (PartB)naefmubarakNoch keine Bewertungen

- AudiV6TDI MechanicsDokument15 SeitenAudiV6TDI Mechanicsmarc4266Noch keine Bewertungen

- ZondST2D Eng PDFDokument148 SeitenZondST2D Eng PDFLilyOhhNoch keine Bewertungen

- 2 Manual de Proteccin Catdica Cathodic Protection HandbooDokument59 Seiten2 Manual de Proteccin Catdica Cathodic Protection Handboogoyote100% (1)

- Lexan 121RDokument4 SeitenLexan 121RJavier RuizNoch keine Bewertungen

- Simplified Model For Evaluating Soil Liquefaction Potential Using CPTUDokument8 SeitenSimplified Model For Evaluating Soil Liquefaction Potential Using CPTUIbrahim SuryaNoch keine Bewertungen

- ErrtDokument101 SeitenErrtMadhav KumarNoch keine Bewertungen

- IB Physics Answers ThemeADokument15 SeitenIB Physics Answers ThemeANicole El-hazhaliNoch keine Bewertungen

- SAT - Physics - 11 Grade - 4T - 2020-2021Dokument7 SeitenSAT - Physics - 11 Grade - 4T - 2020-2021Ануар ТуяковNoch keine Bewertungen

- Allegro QX DataSheetDokument4 SeitenAllegro QX DataSheetProfumo San Martin100% (1)

- La Teoria SintergiaDokument17 SeitenLa Teoria SintergiaCarlos CárdenasNoch keine Bewertungen

- JAMB Physics SyllabusDokument20 SeitenJAMB Physics SyllabusWhinhosaNoch keine Bewertungen

- Sensors: A New Approach For Improving Reliability of Personal Navigation Devices Under Harsh GNSS Signal ConditionsDokument21 SeitenSensors: A New Approach For Improving Reliability of Personal Navigation Devices Under Harsh GNSS Signal ConditionsRuddy EspejoNoch keine Bewertungen

- Vehicle Detection Using Hog and SVMDokument5 SeitenVehicle Detection Using Hog and SVMBaargav BheemaNoch keine Bewertungen

- Rohit Kumar XII B PHYSICSDokument14 SeitenRohit Kumar XII B PHYSICSRKNoch keine Bewertungen

- Separation Science - Chromatography Unit Thomas Wenzel Department of Chemistry Bates College, Lewiston ME 04240 Twenzel@bates - EduDokument69 SeitenSeparation Science - Chromatography Unit Thomas Wenzel Department of Chemistry Bates College, Lewiston ME 04240 Twenzel@bates - EduthecriticNoch keine Bewertungen