Beruflich Dokumente

Kultur Dokumente

Lect17 Seq

Hochgeladen von

orengeneralCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Lect17 Seq

Hochgeladen von

orengeneralCopyright:

Verfügbare Formate

Advanced VLSI Design

Sequential Logic Design

CMPE 640

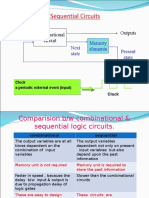

Concepts

In sequential logic, the outputs depend not only on the inputs, but also on the preceding

input values... it has memory.

Memory can be implemented in 2 ways:

Positive feedback or regeneration (static):

One or more output signals are connected back to the inputs via storage elements.

These circuits are called multivibrator.

Bistable elements such as flip-flops are most common but monostable and astable circuits are also used.

Charge storage (dynamic):

As we know, a periodic refresh is necessary here.

The bistable element can be either static or dynamic and is an essential library element

called a register.

An astable multivibrator acts as an oscillator (clock generator) while a monostable multivibrator can be used as a pulse generator.

1

Sequential Logic Design

Advanced VLSI Design

CMPE 640

Static Sequential Circuits

W've already discussed the regenerative property.

out

Vi1

Vo1 = Vi2

Vo2 = Vi1

Vo2

f(Vi1) Metastable

v1

finv(Vi2)

Two stable

operating

points

v2

v0

in

Regenerative

If the gain of the inverter in the transient region is greater than 1, there are only two

stable operating points.

Storing a new value usually involves applying a trigger pulse for a duration equal to the

propagation delay through the two inverters.

The trigger pulse takes either Vi1 or Vi2 temporarily out of the region where the gain,

G, is less than 1 to the unstable region where G > 1.

2

Sequential Logic Design

Advanced VLSI Design

CMPE 640

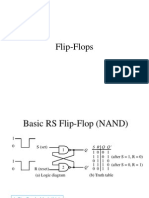

Flip-flop Classification

Q

Positive

logic

NOR

version

The length of the trigger pulse

Set-Reset

Flip-flop applied to S or R has to larger than

the loop delay of the cross-coupled

pair.

NAND

version

Negative

logic

S

0

0

1

1

R

0

1

0

1

Q

Q

0

1

0

Q

Q

1

0

0

Note that this mode is forbidden

since the constraint Q and Q

are not complementary. Also,

the return to 00/11 leaves the FF

in an unpredictable state.

S

0

0

1

1

R

0

1

0

1

Q

1

1

0

Q

Q

1

0

1

Q

Sequential Logic Design

Advanced VLSI Design

CMPE 640

Flip-flop Classification

The ambiguity of having a non-allowed mode caused by trigger pulses going active simultaneously can be avoided by adding two feedback lines:

Jn

0

0

1

1

Kn

0

1

0

1

Qn+1

Qn

0

1

Qn

Note the characteristic table is

similar to SR FF except for

the forbidden mode

Note if both J and K are high, and clock pulses, the output is complemented.

However, doing so enables the other input and the FF oscillates.

This places some stringent constraints on the clock pulse width (e.g. < than the propagation delay through the FF).

Advanced VLSI Design

Sequential Logic Design

CMPE 640

Flip-flop Classification

Synchronous circuit

Changes in the output logic states of all FFs are synchronized with the clock signal, .

Note that:

T FF (toggle FF) is a special case of the JK with J and K tied together.

D FF (delay FF) is a special case with J and K connected with complementary values of

the D input.

It generates a delayed version of the input synchronized with the clock.

These FFs are also called latches.

A FF is a latch if the gate is transparent while the clock is high (low).

Any changes in the input appear in the output after a nominal delay.

The transparent nature can cause race problems:

This circuit oscillates as long

Q

D

as remains high.

D

1

Sequential Logic Design

Advanced VLSI Design

CMPE 640

Master-Slave FFs

One way to avoid the race is to use the master-slave approach.

SI

RI

Master

Slave

The master on the left is active (J and K are enabled) when is high.

The slave on the right is in hold mode, preventing changes on SI and RI from propagating to the output, Q.

When goes low, the state of the master is frozen and the NAND gates in the slave are

enabled.

There is no constraint on the maximum width of for proper operation.

6

Sequential Logic Design

Advanced VLSI Design

CMPE 640

Master-Slave FFs

D

Negative

level-sensitive

latch

QM

1

Clk

Clk

Positive

level-sensitive

latch

Clk

D

QM

Q

Latches are transparent on half of the

clock cycle and subject to race conditions.

Sequential Logic Design

Advanced VLSI Design

Master-Slave Set/Clear Asynchronous FFs

D

CMPE 640

set

reset

Clk

Clk

set

Q

P

Or

reset

Clr

0

QM

Clr

Clk

Set

Clk

Set

8

Advanced VLSI Design

Sequential Logic Design

CMPE 640

Toggle Flip-Flop with Asynchronous Clear:

Sequential Logic Design

Advanced VLSI Design

CMPE 640

T FF

QM

Clr

C

Clk

Out

Clk

Can also use NAND SR FF

and two NANDs.

Divides Clk by 2.

Used in counters.

10

Sequential Logic Design

Advanced VLSI Design

CMPE 640

Edge-triggered FFs

Problem with master-slave approach:

The circuit is sensitive to changes in the input signals as long as is high.

In the case of the JK FF, the inputs MUST stay constant with high.

If FF is reset, it is sensitive to the level of J, e.g., 1 glitches.

The fix is to allow the state of the FF to change only at the rising (falling) edge of the clock.

In (1)

N1

In (0)

Out

N2

0 Pulse

In

Results in a short low-going pulse

at the output of N2 with length

approximately equal to the

propagation delay through N1.

In

Out

11

Sequential Logic Design

Advanced VLSI Design

CMPE 640

Edge-triggered FFs

The modification applied to the JK FF is shown below.

Low-going pulses

are generated on

S and R with the

low going edge

of the clock.

Note that the inputs must be stable for some time before the clock goes low.

This is also true for the master-slave D FF, but the constraints are different.

Let's first define some terms.

12

Advanced VLSI Design

Sequential Logic Design

CMPE 640

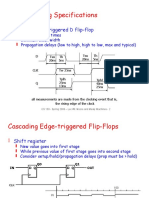

Flip-Flop Timing Definitions

Timing diagram showing the terms defining the proper operation of a FF.

Clock Cycle Time (Tc)

Setup time (Ts) Hold time (Th)

D

Clock-to-Q delay (Tq) (Q is indeterminate in this region)

Q

Tc: Clock Cycle Time.

Ts: The amount of time before the clock edge that the D input has to be stable.

Th: Data has to be held for this period while clock travels to point of storage.

Tq: Clock-to-Q delay: Delay from the positive clock input to new value of Q.

13

Sequential Logic Design

Advanced VLSI Design

CMPE 640

Setup/Hold Time Violations

Depending on the design, one or both of Ts and Th may have to be non-zero.

For example, the master-slave D FF is likely to require a longer setup time than the

edge-triggered D FF.

QM

G1

S1

"Glitches" in

the combo logic.

S2

Y

D

X

Y

Clk

G2

Let's assume a 1 is the "correct" storage value.

Since setup time is violated, a zero will be

"latched" instead.

S1 opens and S2 closes.

The delay through inverters G1 and G2.

Edge triggered FF prevents the "master" from following the D input so the FF's internal

delay does not affect setup time.

14

Sequential Logic Design

Advanced VLSI Design

System Timing

Two possible strategies to implement clocked systems:

inputs

Combinational

Reg

Logic

A

CMPE 640

outputs

Reg

B

clk

inputs

Latch

A

Tq

Combinational

Logic

Td

outputs

Ts

Latch

B

clk

Latches are a more economical implementation strategy but are transparent on half of the

clock cycle, i.e., cannot be used in feedback systems.

Also, the following constraint must be met for latches:

Td < Tc/2 - Tq - Ts

where Td is the worst case propagation delay, Tc is the clock cycle time, Tq is the

Clock-to-Q time of latch A and Ts is the setup time for latch B.

15

Sequential Logic Design

Advanced VLSI Design

CMPE 640

Clock Race Conditions

For edge-triggered FFs, the following time constraint must be met:

Tq + Td + Ts < Tc

Clock races caused by:

Delays in the clock line to Reg B.

New data stored instead of previous data:

D

Q

Combinational

Reg

Logic

A

clk

D

Reg

B

clk

Q

D

previous data

clk

clk

new data

clock delayed to Reg B

new data latched in error

16

Sequential Logic Design

Advanced VLSI Design

CMPE 640

Clock Race Conditions

Delays in the combinational logic that are larger than the clock cycle time.

Data arrives late at Reg B, old data retained instead of latching new data.

D

Q

Reg

A

Reg

B

clk

Q

D

previous data delayed

new data

clk

Old data latched in error.

As you can see, designers have to walk a temporal 'tight-rope', e.g., they have to minimize

clock skew while considering worst and best case delays through combinational logic.

17

Advanced VLSI Design

Sequential Logic Design

CMPE 640

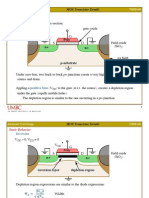

CMOS Static Flip-Flops

Full complementary version of the master-slave FF requires 38 transistors!

SI

RI

Alternatively,

an 18 transistor

version using

M5

Q

this building

block:

M6

M2 Q

M1M3

M4 R

This strategy requires transistor

sizes to be taken into account.

Assume Q is high and R pulsed.

M3 and M4 must "overpower" M2

and reduce Q to < threshold of

M5 and M6.

A variation of this, which combines

and R/S, is the 6 trans. SRAM.

18

Das könnte Ihnen auch gefallen

- DFTDokument14 SeitenDFTRahulNoch keine Bewertungen

- Load Test On DC Compund GeneratorDokument4 SeitenLoad Test On DC Compund Generatorkudupudinagesh50% (12)

- Reed's Basic Electrotechnology For Engineers PDFDokument311 SeitenReed's Basic Electrotechnology For Engineers PDFraovisam100% (2)

- CMOS Sequential Circuit Design Lec.-1Dokument22 SeitenCMOS Sequential Circuit Design Lec.-1Parag ParandkarNoch keine Bewertungen

- Flip FlopsDokument25 SeitenFlip FlopsNagul MeeraNoch keine Bewertungen

- 6 RegistersDokument24 Seiten6 RegistersPiyooshTripathiNoch keine Bewertungen

- CMOS Logic StructuresDokument23 SeitenCMOS Logic StructuressuprabhuNoch keine Bewertungen

- Sequential LogicDokument68 SeitenSequential LogicbabahussainNoch keine Bewertungen

- Experiment No. 3.1Dokument5 SeitenExperiment No. 3.1Harshal AmbatkarNoch keine Bewertungen

- Timing Issues in Digital ASIC DesignDokument101 SeitenTiming Issues in Digital ASIC Designnsai_vs1513Noch keine Bewertungen

- Finite State Machine Implementation: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998Dokument31 SeitenFinite State Machine Implementation: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998Sai PrashanthNoch keine Bewertungen

- Latch and Flip-FlopDokument58 SeitenLatch and Flip-FlopDalila Nadia RazaliNoch keine Bewertungen

- 11 Clock SkewDokument35 Seiten11 Clock SkewMaheshNoch keine Bewertungen

- Chapter #10: Finite State Machine ImplementationDokument32 SeitenChapter #10: Finite State Machine Implementationphani_abkNoch keine Bewertungen

- Working of C MOS (Single Edge Triggered)Dokument4 SeitenWorking of C MOS (Single Edge Triggered)Avinash BaldiNoch keine Bewertungen

- Clock Tree SynthesisDokument27 SeitenClock Tree Synthesispdnoob100% (3)

- Flip FlopsDokument29 SeitenFlip FlopsShweta RoyNoch keine Bewertungen

- Set Up DelayDokument15 SeitenSet Up DelayNathan BrooksNoch keine Bewertungen

- Shift Sins OutDokument11 SeitenShift Sins Outawa buayaNoch keine Bewertungen

- CB 2 CleDokument4 SeitenCB 2 CleJosé Antonio Montanares ZambranoNoch keine Bewertungen

- MOSIS Counter Report Spring 2008Dokument60 SeitenMOSIS Counter Report Spring 2008atom_2334Noch keine Bewertungen

- FlipflopsDokument80 SeitenFlipflopsvikramkolanuNoch keine Bewertungen

- CH 7Dokument69 SeitenCH 7katral-jamerson-9379Noch keine Bewertungen

- Arithmetic and Logic (Cont) : 2.3 Build Sequential Logic CircuitDokument22 SeitenArithmetic and Logic (Cont) : 2.3 Build Sequential Logic CircuitBadrul Afif ImranNoch keine Bewertungen

- Experiment 9 Sequential Circuits Introduction To CountersDokument3 SeitenExperiment 9 Sequential Circuits Introduction To CountersKeshav MusunuriNoch keine Bewertungen

- Timing Issues in FPGA Synchronous Circuit Design: ECE 428 Programmable ASIC DesignDokument33 SeitenTiming Issues in FPGA Synchronous Circuit Design: ECE 428 Programmable ASIC DesignVarun KondagunturiNoch keine Bewertungen

- Lect11 SeqDokument35 SeitenLect11 Seqs.b.v.seshagiri1407Noch keine Bewertungen

- DFF Setup Hold ReviewDokument50 SeitenDFF Setup Hold ReviewAkanksha221291Noch keine Bewertungen

- Lecture #32 Registers, Counters EtcDokument21 SeitenLecture #32 Registers, Counters EtcRajan GoyalNoch keine Bewertungen

- EC 303 Chapter 2Dokument48 SeitenEC 303 Chapter 2PrevenaManiamNoch keine Bewertungen

- Clocking Part 2Dokument4 SeitenClocking Part 2Dmitry LeyzerovichNoch keine Bewertungen

- Selected Design Topics: Logic and Computer Design FundamentalsDokument20 SeitenSelected Design Topics: Logic and Computer Design FundamentalsYawar Abbas KhanNoch keine Bewertungen

- Typical Timing Specifications: Positive Edge-Triggered D Flip-FlopDokument50 SeitenTypical Timing Specifications: Positive Edge-Triggered D Flip-Flopanusha killariNoch keine Bewertungen

- Evolution of Latches and Flip-Flops-1Dokument24 SeitenEvolution of Latches and Flip-Flops-1Ravi ThejaNoch keine Bewertungen

- Flancter App NoteDokument11 SeitenFlancter App NotebigdogguruNoch keine Bewertungen

- Chip Level Timing: ECE124 Digital Circuits and SystemsDokument18 SeitenChip Level Timing: ECE124 Digital Circuits and SystemspdnoobNoch keine Bewertungen

- Chp1 - Latches and Flip-FlopsDokument44 SeitenChp1 - Latches and Flip-FlopsAbnen OngNoch keine Bewertungen

- Sequential Logic - Flip-Flops: 6.1 SR LatchDokument5 SeitenSequential Logic - Flip-Flops: 6.1 SR Latchanon020202Noch keine Bewertungen

- CSE 307: Digital TechniqueDokument33 SeitenCSE 307: Digital TechniquemmlabjpNoch keine Bewertungen

- Lecture27 - Flip Flops: Jagannadha Naidu KDokument0 SeitenLecture27 - Flip Flops: Jagannadha Naidu Khim92Noch keine Bewertungen

- Metastability/Overview: - Metastability of Flip-Flops (FFS) and LatchesDokument19 SeitenMetastability/Overview: - Metastability of Flip-Flops (FFS) and LatchesMani KiranNoch keine Bewertungen

- 6.xi Constraints 1762Dokument187 Seiten6.xi Constraints 1762Khubaib AhmedNoch keine Bewertungen

- Lect11 SeqDokument35 SeitenLect11 Seqkaushik_gupta_4Noch keine Bewertungen

- Two Phase Non-Overlapping Clock DriverDokument9 SeitenTwo Phase Non-Overlapping Clock DriverVictor ChangNoch keine Bewertungen

- Unit 5 DLDDokument189 SeitenUnit 5 DLDGuru VelmathiNoch keine Bewertungen

- dpsd-2 Mark QBDokument14 Seitendpsd-2 Mark QBpriya100% (2)

- Topic 2 - Subtopic 2.3Dokument31 SeitenTopic 2 - Subtopic 2.3Navinaash Chanthra SegaranNoch keine Bewertungen

- Unit-1 - Digital ElectronicsDokument50 SeitenUnit-1 - Digital ElectronicsVignesh VigneshNoch keine Bewertungen

- STA FinalDokument66 SeitenSTA FinalgauravkshriNoch keine Bewertungen

- Synchronous Derived Clock and Synthesis of Low Power Sequential CircuitsDokument7 SeitenSynchronous Derived Clock and Synthesis of Low Power Sequential CircuitsChaitanya ChavaNoch keine Bewertungen

- 80C186 and 80C188 Integrated 16-Bit Microprocessors: Clocking Information Changes Crystal-Driven Clock SourceDokument18 Seiten80C186 and 80C188 Integrated 16-Bit Microprocessors: Clocking Information Changes Crystal-Driven Clock SourceCristian BandilaNoch keine Bewertungen

- 6-Registers and CountersDokument40 Seiten6-Registers and CountersWisdom tabuloNoch keine Bewertungen

- Static Timing Analysis - MaharshiDokument29 SeitenStatic Timing Analysis - MaharshiSatish Yada100% (1)

- ClockGating CtsDokument8 SeitenClockGating CtsSrikanth Reddy SarabudlaNoch keine Bewertungen

- BOCODokument10 SeitenBOCOKarn SenNoch keine Bewertungen

- Simulation of Se Qu Ntial CK TDokument10 SeitenSimulation of Se Qu Ntial CK TSivaprakasam KarthikeyanNoch keine Bewertungen

- Registers: Register Is A Group of Flip-Flops. Its Basic Function Is ToDokument20 SeitenRegisters: Register Is A Group of Flip-Flops. Its Basic Function Is ToUninj XelaNoch keine Bewertungen

- 17 RegistersDokument20 Seiten17 RegistersPawan Kumar KNoch keine Bewertungen

- 17 RegistersDokument20 Seiten17 RegistersNeeraj SinghNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksVon EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksNoch keine Bewertungen

- Lect00 IntroDokument12 SeitenLect00 IntroorengeneralNoch keine Bewertungen

- Lect03 Qual MetricsDokument14 SeitenLect03 Qual MetricsorengeneralNoch keine Bewertungen

- Comlementary CMOS Logic Gates: nMOS Pull-Down Network pMOS Pull-Up Network Static CMOSDokument12 SeitenComlementary CMOS Logic Gates: nMOS Pull-Down Network pMOS Pull-Up Network Static CMOSorengeneralNoch keine Bewertungen

- Mos, Cmos, Transmission GatesDokument17 SeitenMos, Cmos, Transmission GatesSynthiya VinothiniNoch keine Bewertungen

- Directivity: Unidirectional Unchanging InputDokument11 SeitenDirectivity: Unidirectional Unchanging InputChinNoch keine Bewertungen

- Lect05 DiodeDokument18 SeitenLect05 DiodeorengeneralNoch keine Bewertungen

- Static Behavior: Poly N+ N+Dokument14 SeitenStatic Behavior: Poly N+ N+Lan LuoNoch keine Bewertungen

- Lot To Lot Wafer To Wafer Die To Die: Process VariationsDokument8 SeitenLot To Lot Wafer To Wafer Die To Die: Process VariationsMunish JainNoch keine Bewertungen

- Pn-Junction: Excess Minority Carrier Charge Space ChargeDokument28 SeitenPn-Junction: Excess Minority Carrier Charge Space ChargePrashant Kumar SinghNoch keine Bewertungen

- CMOS Processing Technology Silicon: A Semiconductor With Resistance Between That of Conductor and AnDokument18 SeitenCMOS Processing Technology Silicon: A Semiconductor With Resistance Between That of Conductor and AntmdmurthyNoch keine Bewertungen

- Lect12 InverterDokument17 SeitenLect12 InverterVimala PriyaNoch keine Bewertungen

- Isolation: CMOS Processing TechnologyDokument15 SeitenIsolation: CMOS Processing TechnologyAshwani RanaNoch keine Bewertungen

- Lect11 ScalingDokument7 SeitenLect11 ScalingsuprabhuNoch keine Bewertungen

- Lect13 Inverter2Dokument20 SeitenLect13 Inverter2orengeneralNoch keine Bewertungen

- Lect14 ComboDokument12 SeitenLect14 ComboorengeneralNoch keine Bewertungen

- Lect19 MemDokument21 SeitenLect19 MemorengeneralNoch keine Bewertungen

- Pass Gate Logic: Switch NetworkDokument34 SeitenPass Gate Logic: Switch NetworkSunil SharmaNoch keine Bewertungen

- Lect18 Seq2Dokument22 SeitenLect18 Seq2orengeneralNoch keine Bewertungen

- Ratioed Logic: R Resistive Load V 0 Depletion Load V 0 Pmos LoadDokument13 SeitenRatioed Logic: R Resistive Load V 0 Depletion Load V 0 Pmos LoadAmjad WadalaNoch keine Bewertungen

- Sata Moi Tektronix Phy-Tsg-Oob r14 v1 0rcDokument142 SeitenSata Moi Tektronix Phy-Tsg-Oob r14 v1 0rcorengeneralNoch keine Bewertungen

- Image Processing & Computer Vision With MATLAB 2013Dokument71 SeitenImage Processing & Computer Vision With MATLAB 2013orengeneralNoch keine Bewertungen

- Bug Blower Motor Summary-SampleDokument1 SeiteBug Blower Motor Summary-SampleMohammad Reza NajafiNoch keine Bewertungen

- Marshall Bass Amp dbs7200Dokument5 SeitenMarshall Bass Amp dbs7200Dean LombardNoch keine Bewertungen

- 2N1305 CentralSemiconductorDokument5 Seiten2N1305 CentralSemiconductorAirton SousaNoch keine Bewertungen

- EbookDokument2 SeitenEbookAG Gumelar MuktiNoch keine Bewertungen

- C03 - HVSG 11Dokument20 SeitenC03 - HVSG 11princensikan23Noch keine Bewertungen

- E. UnruhThe Second X-DacDokument9 SeitenE. UnruhThe Second X-DacThorsten LoeschNoch keine Bewertungen

- Beryl (Radial Thru-Hole) HW SeriesDokument2 SeitenBeryl (Radial Thru-Hole) HW Seriesester853Noch keine Bewertungen

- A Generic DMM Test and CalibrationDokument11 SeitenA Generic DMM Test and CalibrationrobertNoch keine Bewertungen

- Dual Beam Oscilloscope Dual and Multiple Beam OscilloscopesDokument3 SeitenDual Beam Oscilloscope Dual and Multiple Beam OscilloscopesDebashish PalNoch keine Bewertungen

- Be1-Flex (Uub)Dokument2 SeitenBe1-Flex (Uub)Eliyanto E BudiartoNoch keine Bewertungen

- List STRDokument3 SeitenList STRdineshsoni29685Noch keine Bewertungen

- VdivDokument12 SeitenVdivmehralsmenschNoch keine Bewertungen

- FRS Electrical Panel Spec EOIDokument20 SeitenFRS Electrical Panel Spec EOITravis WoodNoch keine Bewertungen

- Schneider Distribution Transformer1Dokument44 SeitenSchneider Distribution Transformer1STEVE58100% (3)

- Datasheet lf356 PDFDokument23 SeitenDatasheet lf356 PDFAlberto Chica CardenasNoch keine Bewertungen

- Lesson Plan Template: Synchronous MachinesDokument3 SeitenLesson Plan Template: Synchronous MachinesNANDHAKUMAR ANoch keine Bewertungen

- Ixys P-Channel Power Mosfets and Applications Abdus Sattar, Kyoung-Wook Seok, Ixan0064Dokument14 SeitenIxys P-Channel Power Mosfets and Applications Abdus Sattar, Kyoung-Wook Seok, Ixan0064Kikuvi JohnNoch keine Bewertungen

- Dewalt d25481Dokument12 SeitenDewalt d25481Vasilic NikolaNoch keine Bewertungen

- MPR-100 Brochure GB 220930 144329Dokument3 SeitenMPR-100 Brochure GB 220930 144329roy zonthara simbolonNoch keine Bewertungen

- MSE Mono 60 - v3 (270-280)Dokument2 SeitenMSE Mono 60 - v3 (270-280)amitNoch keine Bewertungen

- Rz1 ManualDokument34 SeitenRz1 Manualhaha2012Noch keine Bewertungen

- Asr 44 - Asr Self Hold Thermal CutoutDokument4 SeitenAsr 44 - Asr Self Hold Thermal CutoutHotel WijayaNoch keine Bewertungen

- 0900P Electronic SensorsDokument33 Seiten0900P Electronic SensorseugenNoch keine Bewertungen

- Very Low Dropout 3.0 Amp Regulator With Enable: Power Management Features DescriptionDokument10 SeitenVery Low Dropout 3.0 Amp Regulator With Enable: Power Management Features DescriptionmitusharmaNoch keine Bewertungen

- AEGIS Bearing Protection - Ring CatalogDokument20 SeitenAEGIS Bearing Protection - Ring CatalogJan AbuYildirimNoch keine Bewertungen

- C1 3 - Development of An Arduino Based Identification Diagnostic and Monitoring System - ADokument51 SeitenC1 3 - Development of An Arduino Based Identification Diagnostic and Monitoring System - ALeigh NavalesNoch keine Bewertungen

- Coleman 58032 Owners ManualDokument12 SeitenColeman 58032 Owners Manual21st-Century-Goods.comNoch keine Bewertungen

- Tig Iveco S-Way 2019+ enDokument7 SeitenTig Iveco S-Way 2019+ enandreaviligiardiNoch keine Bewertungen