Beruflich Dokumente

Kultur Dokumente

RealDigital Project 10

Hochgeladen von

Krishnamurthy AnantharamakrishnanCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

RealDigital Project 10

Hochgeladen von

Krishnamurthy AnantharamakrishnanCopyright:

Verfügbare Formate

Lab Project #10: Structural Design of Sequential

Circuits

Revision: August 31, 2009

215 E Main Suite D | Pullman, WA 99163

(509) 334 6306 Voice and Fax

STUDENT

I am submitting my own work, and I understand penalties will

be assessed if I submit work for credit that is not my own.

Print Name

ID Number

Sign Name

Date

Estimated Work Hours

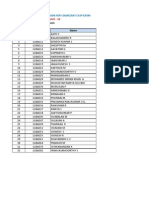

Point Scale

1 2 3

1

0

1 2 3

1

0

Overall Weight

20% will be deducted from scores for each week late

Score = Points awarded (Pts) x Weight (Wt)

LAB ASSISTANT

#

Demonstration

Wt

Circuit demonstration

10

Circuit demonstration

10

Pts

Lat

e

Sco

re

Attachments

Source, simulation, worksheet

Source and simulation

Worksheets, source and simulation files

Source, simulation, and worksheet

Problem 1.

Lab Asst Signature

Date

Total In-Lab

Score

NA

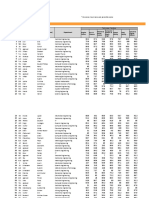

GRADER

#

4: Exemplary

3: Complete

2: Incomplete

1: Minor effort

0: Not submitted

Wt

6

3

10

10

Pt

s

Weeks

late

Score

Total

Grading Score

Total

Score

Total

score is

In-lab

score plus

grading

score

Using the Xilinx CAD tools, create a structural 4-bit counter with CEN and TC functions.

You may use schematic methods and the FDCE flip-flop component from the Xilinx

library, or structural VHDL methods (in which case you can use the flip-flop you

designed in the previous lab). To complete the design, you will need to find next-state

logic circuits for the counter. A state diagram and K-maps have been provided below

for this purpose (or, nothing is keeping you from borrowing a circuit from the Xilinx

schematic library, but you must complete the K-maps regardless). When the counter is

complete, simulate it using a VHDL a test bench file, and be sure to show all

appropriate output states. Print and submit your source and simulation files. (Hint:

Extensive XOR patterns are present in the D next-state maps. You will probably want

to refer to some circuit schematic source to check your K-map looping.)

Contains material Digilent, Inc.

3 pages

Lab Project #10: Structural design of Sequential Circuits

Empty K-maps follow. Note that if you choose to design a counter using DFFs with a CE input,

you can ignore the CEN inputs shown in the state diagram above (i.e., the state diagram

would only show branches to the next state, without any holding conditions). In this case, the

counters CEN input would directly drive the CE inputs on the DFFs (this makes the K-map

loading and looping a fair amount easier but it is your choice!).

CP DP

AP BP

00

01

11

CP DP

AP BP

10

00

00

01

01

11

11

10

10

00

01

11

10

AN

AN = _____________________

CP DP

AP BP

00

01

11

BN

BN = ____________________

CP DP

AP BP

10

00

00

01

01

11

11

10

10

00

01

11

10

CN

DN

CN = ____________________

DN = ____________________

Problem 2.

Create and simulate a behavioral VHDL 4-bit counter, using a VHDL test bench for the

simulation. Print and submit your source and simulation files.

Problem 3.

Design a circuit that increments a digit (0 F) shown on the seven-segment display

device once each second. The circuit has four pushbutton inputs: one button starts the

counter, a second button stops the counter, a third button increments the counter, and

the fourth button asynchronously resets all memory devices in the design. The system

has the block diagram shown below. You must create the 4-bit counter, a clock divider,

Lab Project #10: Structural design of Sequential Circuits

a seven-segment display decoder, and a controller circuit. You may use any design

tools or methods you wish. You must also create and submit a state diagram for the

controller, together with K-maps showing the next-state and output circuits. Have the

lab assistant inspect your completed work, and download your design to the Digilent

board. Demonstrate your circuits function to the lab assistant and print and submit

your source files for credit.

Problem 4.

Modify your circuit so that all four digits on the seven-segment display are driven, and

drive the least-significant digit so that it changes at a rate of once per millisecond (and

so, the most-significant bit will change at a rate of once per second). This circuit

requires a scanning display controller which is discussed in your boards Reference

Manual. When complete, demonstrate your circuit to the lab assistant and print and

submit your source files for credit. Also create and submit a detailed block diagram of

your circuit showing all circuit blocks and signal connections (and make sure to

appropriately label all circuit blocks and signals).

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Follow MeDokument1 SeiteFollow MeKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- Exam InterfaceDokument3 SeitenExam InterfaceKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- GRE Math Review 2 AlgebraDokument86 SeitenGRE Math Review 2 AlgebraJessica AngelinaNoch keine Bewertungen

- Melfsmolp PadDokument8 SeitenMelfsmolp PadKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- KeyDokument3 SeitenKeyKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- TrailblazerBC PD1 EN AgendaDokument3 SeitenTrailblazerBC PD1 EN AgendaKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- Hopfield NetworksDokument23 SeitenHopfield NetworksSanjay NegiNoch keine Bewertungen

- Object Oriented Programming OOPs or C Sample Paper of MSBTE For Third Semester Computer Engineering Diploma 80 MarksDokument4 SeitenObject Oriented Programming OOPs or C Sample Paper of MSBTE For Third Semester Computer Engineering Diploma 80 MarksKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- Cognizant CCS Exam Applied Students ListDokument18 SeitenCognizant CCS Exam Applied Students ListKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- Fuzzy RelationsDokument23 SeitenFuzzy RelationsdinkarbhombeNoch keine Bewertungen

- Antarctica CruiseDokument17 SeitenAntarctica CruiseKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- GRE Quant Concepts FormulaeDokument31 SeitenGRE Quant Concepts Formulaeshaliniark100% (3)

- Object Oriented Programming OOPs or C Sample Paper of MSBTE For Third Semester Computer Engineering Diploma 80 MarksDokument4 SeitenObject Oriented Programming OOPs or C Sample Paper of MSBTE For Third Semester Computer Engineering Diploma 80 MarksKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- Physic eDokument209 SeitenPhysic eKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- Example 2:: To Get Square Wave Mode 3 Is Selected Count Should Be 1 MHZ 1 KHZ 1000Dokument16 SeitenExample 2:: To Get Square Wave Mode 3 Is Selected Count Should Be 1 MHZ 1 KHZ 1000Athul Raj100% (1)

- VLSI DesignDokument116 SeitenVLSI DesignKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- VLSI MayJune 2013Dokument1 SeiteVLSI MayJune 2013Krishnamurthy AnantharamakrishnanNoch keine Bewertungen

- Physic eDokument209 SeitenPhysic eKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- Pressure Sensing TransmitterDokument10 SeitenPressure Sensing TransmitterKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- Readme CCRDokument1 SeiteReadme CCRNirmal DasNoch keine Bewertungen

- Charge AmpsDokument5 SeitenCharge AmpsKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- Controllability and Observability of DTISDokument5 SeitenControllability and Observability of DTISKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- In Gate 2012Dokument24 SeitenIn Gate 2012Anish GoswamiNoch keine Bewertungen

- Vedit TutDokument106 SeitenVedit TutKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- KrisDokument6 SeitenKrisKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- Mato 2Dokument3 SeitenMato 2Krishnamurthy AnantharamakrishnanNoch keine Bewertungen

- CEDokument2 SeitenCEKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- TDP 1Dokument2 SeitenTDP 1Krishnamurthy AnantharamakrishnanNoch keine Bewertungen

- GATE 2014 Instrumentation Engineering - Sample PaperDokument12 SeitenGATE 2014 Instrumentation Engineering - Sample PaperKrishnamurthy AnantharamakrishnanNoch keine Bewertungen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (120)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Procedure To Create The Employee Attendance ProjectDokument30 SeitenProcedure To Create The Employee Attendance ProjectSougata Roy Chowdhury0% (5)

- Qualifications: Stephanie WarringtonDokument3 SeitenQualifications: Stephanie Warringtonapi-268210901Noch keine Bewertungen

- Earth Pressure At-Rest PDFDokument7 SeitenEarth Pressure At-Rest PDFvpb literaturaNoch keine Bewertungen

- Seminar WorkshopDokument3 SeitenSeminar Workshopsir_mhickoNoch keine Bewertungen

- Youtube Poop: Subverting Art OnlineDokument14 SeitenYoutube Poop: Subverting Art OnlineWill KurlinkusNoch keine Bewertungen

- Barthes EiffelTower PDFDokument21 SeitenBarthes EiffelTower PDFegr1971Noch keine Bewertungen

- Advanced Java SlidesDokument134 SeitenAdvanced Java SlidesDeepa SubramanyamNoch keine Bewertungen

- 20 Issues For Businesses Expanding InternationallyDokument24 Seiten20 Issues For Businesses Expanding InternationallySubash RagupathyNoch keine Bewertungen

- RealviewDokument62 SeitenRealviewXaxo PapoNoch keine Bewertungen

- Membrane TypesDokument92 SeitenMembrane TypesVanditaa Kothari100% (1)

- MODBUSDokument19 SeitenMODBUSJosé Luis MartínezNoch keine Bewertungen

- Entity Relationship Diagram: TBL - Students TBL - ProgramsDokument1 SeiteEntity Relationship Diagram: TBL - Students TBL - ProgramsEun Chae KimNoch keine Bewertungen

- 2998 1-Emt Fibre Optic Cable-Cat LRDokument32 Seiten2998 1-Emt Fibre Optic Cable-Cat LRsubramanyaNoch keine Bewertungen

- Philippines Research PaperDokument6 SeitenPhilippines Research Paperhxmchprhf100% (1)

- How To Use The Fos AppDokument8 SeitenHow To Use The Fos AppViral Patangiya100% (1)

- CM6 - Mathematics As A Tool - Dispersion and CorrelationDokument18 SeitenCM6 - Mathematics As A Tool - Dispersion and CorrelationLoeynahcNoch keine Bewertungen

- Internal Audit CharterDokument5 SeitenInternal Audit CharterUrsu BârlogeaNoch keine Bewertungen

- Program - PPEPPD 2019 ConferenceDokument3 SeitenProgram - PPEPPD 2019 ConferenceLuis FollegattiNoch keine Bewertungen

- 2011bibliography Part I (Preparation and Initial Assessment)Dokument188 Seiten2011bibliography Part I (Preparation and Initial Assessment)Espiritu MineralNoch keine Bewertungen

- Innoventure List of Short Listed CandidatesDokument69 SeitenInnoventure List of Short Listed CandidatesgovindmalhotraNoch keine Bewertungen

- Confidence Limits in StatisticsDokument30 SeitenConfidence Limits in StatisticsaassmmrrNoch keine Bewertungen

- Meet and Greet Officer PDFDokument85 SeitenMeet and Greet Officer PDFJoby JoseNoch keine Bewertungen

- Generative Drafting (ISO) : CATIA TrainingDokument148 SeitenGenerative Drafting (ISO) : CATIA TrainingAnonymous 38RNNHWyNoch keine Bewertungen

- BS 5499-1:2002 Graphical Symbols and Signs - Safety Signs, Including Fire Safety SignsDokument1 SeiteBS 5499-1:2002 Graphical Symbols and Signs - Safety Signs, Including Fire Safety SignsKuljinder VirdiNoch keine Bewertungen

- IO Chapter6 FinalDokument10 SeitenIO Chapter6 FinalJulia MoplaNoch keine Bewertungen

- Rigstoreef Impact or Enhancement On Marine Biodiversity 2157 7625 1000187Dokument9 SeitenRigstoreef Impact or Enhancement On Marine Biodiversity 2157 7625 1000187tavis80Noch keine Bewertungen

- Associate Cloud Engineer - Study NotesDokument14 SeitenAssociate Cloud Engineer - Study Notesabhi16101Noch keine Bewertungen

- UCO 359 Key & Solution 05Dokument3 SeitenUCO 359 Key & Solution 05Anwesha SatpathyNoch keine Bewertungen

- Sasi EnriquezDokument9 SeitenSasi EnriquezEman NolascoNoch keine Bewertungen

- Manual de Servicio CX 350B 84355067-Dmc Site OnlyDokument127 SeitenManual de Servicio CX 350B 84355067-Dmc Site Onlyabel jairo santos cabello100% (2)