Beruflich Dokumente

Kultur Dokumente

Dynamic Scheduling Using Tomasulo's Approach

Hochgeladen von

Jiju_Joseph_1288Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Dynamic Scheduling Using Tomasulo's Approach

Hochgeladen von

Jiju_Joseph_1288Copyright:

Verfügbare Formate

ASAN MEMORIAL COLLEGE OF ENGINEERING & TECHNOLOGY

Explain the Tomasulos approach used in dynamic scheduling for overcoming data hazards.

Or

Briefly explain how to overcome data hazards with dynamic scheduling using Tomasulos approach

Or

What is dynamic scheduling? Explain how it is used to reduce data hazards

Or

Explain the function of Tomasulos approach

Dynamic Scheduling

The Dynamic Scheduling is a technique in which the hardware rearranges the

instruction execution to reduce the stalls while maintaining data flow and exception

behaviour.

Advantages

It enables handling some cases when dependences are unknown at compile time

It simplifies the compiler

It allows code that was compiled with one pipeline in mind to run efficiently on a

different pipeline

Uses speculation technique to improve performance

Overcoming Data Hazards with Dynamic Scheduling:

Although a dynamically scheduled processor cannot change the data flow, it tries to

avoid stalling when dependences, which could generate hazards, are present.

A major limitation of the simple pipelining techniques is that they all use in-order

instruction issue and execution: Instructions are issued in program order and if an instruction

is stalled in the pipeline, no later instructions can proceed. Thus, if there is dependence

between two closely spaced instructions in the pipeline, this will lead to a hazard and a stall.

If there are multiple functional units, these units could lie idle. If instruction j depends on a

long-running instruction i, currently in execution in the pipeline, then all instructions after j

must be stalled until i is finished and j can execute. For example, consider this code:

DIV.D

F0,F2,F4

ADD.D

F10,F0,F8

SUB.D

F12,F8,F14

Out-of-order execution introduces the possibility of WAR and WAW hazards, which

do not exist in the five-stage integer pipeline and its logical extension to an in-order floatingpoint pipeline.

Out-of-order completion also creates major complications in handling exceptions.

Dynamic scheduling with out-of-order completion must preserve exception behaviour in the

sense that exactly those exceptions that would arise if the program were executed in strict

program order actually do arise.

Imprecise exceptions can occur because of two possibilities:

1. The pipeline may have already completed instructions that are later in program order than

the instruction causing the exception, and

JIJU K JOSEPH, Lecturer/CSE

ASAN MEMORIAL COLLEGE OF ENGINEERING & TECHNOLOGY

2. The pipeline may have not yet completed some instructions that are earlier in program

order than the instruction causing the exception.

To allow out-of-order execution, we essentially split the ID pipe stage of our simple fivestage pipeline into two stages:

1 IssueDecode instructions, check for structural hazards.

2 Read operandsWait until no data hazards, then read operands.

In a dynamically scheduled pipeline, all instructions pass through the issue stage in

order (inorder issue); however, they can be stalled or bypass each other in the second stage

(read operands) and thus enter execution out of order. Score-boarding is a technique for

allowing instructions to execute out-of-order when there are sufficient resources and no data

dependences. We focus on a more sophisticated technique, called Tomasulos algorithm, that

has several major enhancements over score-boarding.

Dynamic Scheduling Using Tomasulos Approach :

The IBM 360/91 floating point unit used a sophisticated scheme to allow out-of-order

execution. This scheme, invented by RobertTomasulo, tracks when operands for instructions

are available, to minimize RAW hazards, and introduces register renaming, to minimize

WAW and WAR hazards.

To better understand how register renaming eliminates WAR and WAW hazards,

consider the following example code sequence that includes both a potential WAR and WAW

hazard:

DIV.D

F0,F2,F4

ADD.D

F6,F0,F8

S.D

F6,0(R1)

SUB.D

F8,F10,F14

MUL.D

F6,F10,F8

There is an anti dependence between the ADD.D and the SUB.D and an output

dependence between the ADD.D and the MUL.D, leading to two possible hazards: a WAR

hazard on the use of F8 by ADD.D and a WAW hazard since the ADD.D may finish later than

the MUL.D. There are also three true data dependences: between the DIV.D and the ADD.D,

between the SUB.D and the MUL.D, and between the ADD.D and the S.D. These two name

dependences can both be eliminated by register renaming. For simplicity, assume the

existence of two temporary registers, S and T. Using S and T, the sequence can be rewritten

without any dependences as

DIV.D

F0,F2,F4

ADD.D

S,F0,F8

S.D

S,0(R1)

SUB.D

T,F10,F14

MUL.D

F6,F10,T

Tomasulo's algorithm implements register renaming through the use of what are called

reservation stations. Reservation stations. They fetch and buffer an operand as soon as it is

JIJU K JOSEPH, Lecturer/CSE

ASAN MEMORIAL COLLEGE OF ENGINEERING & TECHNOLOGY

available, eliminating the need to get the operand from a register. In addition, pending

instructions designate the reservation station that will provide their input. Finally, when

successive writes to a register overlap in execution, only the last one is actually used to

update the register. As instructions are issued, the register specifies for pending operands are

renamed to the names of the reservation station, which provides register renaming.

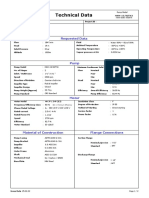

The following diagram shows the basic structure of a Tomasulo-based MIPS processor,

including both the floating-point unit and the load/store unit.

The Basic structure of a MIPS floating-point unit using Tomasulos algorithm

Instructions are sent from the instruction unit into the instruction queue from which

they are issued in FIFO order.

The reservation stations include the operation and the actual operands, as well as

information used for detecting and resolving hazards. Load buffers have three functions: hold

the components of the effective address until it is computed, track outstanding loads that are

waiting on the memory, and hold the results of completed loads that are waiting for the CDB.

Similarly, store buffers have three functions: hold the components of the effective address

until it is computed, hold the destination memory addresses of outstanding stores that are

waiting for the data value to store, and hold the address and value to store until the memory

unit is available.

JIJU K JOSEPH, Lecturer/CSE

ASAN MEMORIAL COLLEGE OF ENGINEERING & TECHNOLOGY

All results from either the FP units or the load unit are put on the CDB, which goes to

the FP register file as well as to the reservation stations and store buffers. The FP adders

implement addition and subtraction, and the FP multipliers do multiplication and division.

There are only three steps in Tomasulos Aprroach :

1. IssueGet the next instruction from the head of the instruction queue. If there is a

matching reservation station that is empty, issue the instruction to the station with the

operand values (renames registers)

2. Execute(EX) When all the operands are available, place into the corresponding

reservation stations for execution. If operands are not yet available, monitor the

common data bus (CDB) while waiting for it to be computed.

3. Write result (WB)When the result is available, write it on the CDB and from there

into the registers and into any reservation stations (including store buffers) waiting for

this result. Stores also write data to memory during this step: When both the address

and data value are available, they are sent to the memory unit and the store completes.

Each reservation station has six fields:

OpThe operation to perform on source operands S1 and S2.

Qj, QkThe reservation stations that will produce the corresponding source operand; a

value of zero indicates that the source operand is already available in Vj or Vk, or is

unnecessary.

Vj, VkThe value of the source operands. Note that only one of the V field or the Q field is

valid for each operand. For loads, the Vk field is used to the offset from the instruction.

Aused to hold information for the memory address calculation for a load or store.

BusyIndicates that this reservation station and its accompanying functional unit are

occupied.

JIJU K JOSEPH, Lecturer/CSE

Das könnte Ihnen auch gefallen

- ParaphraseDokument51 SeitenParaphrasevincent tekeyNoch keine Bewertungen

- Unit - IiiDokument41 SeitenUnit - IiiJit Agg0% (1)

- Interview Questions for IBM Mainframe DevelopersVon EverandInterview Questions for IBM Mainframe DevelopersBewertung: 1 von 5 Sternen1/5 (1)

- Dual-Pot Sand Filter Type B (DSF-B)Dokument2 SeitenDual-Pot Sand Filter Type B (DSF-B)kanchanabalajiNoch keine Bewertungen

- Instruction-Level Parallelism 2Dokument77 SeitenInstruction-Level Parallelism 2AnonimusNoch keine Bewertungen

- CA Classes-126-130Dokument5 SeitenCA Classes-126-130SrinivasaRaoNoch keine Bewertungen

- Dpco Unit 4Dokument21 SeitenDpco Unit 4pl.babyshalini palanisamyNoch keine Bewertungen

- Techopedia Explains: Amdahl's LawDokument19 SeitenTechopedia Explains: Amdahl's LawSandip PaulNoch keine Bewertungen

- Pipeline HazardsDokument39 SeitenPipeline HazardsPranidhi RajvanshiNoch keine Bewertungen

- Lec18 Tomasulo AlgorithmDokument40 SeitenLec18 Tomasulo Algorithmmayank pNoch keine Bewertungen

- CA Classes-131-135Dokument5 SeitenCA Classes-131-135SrinivasaRaoNoch keine Bewertungen

- Instruction PipelineDokument16 SeitenInstruction PipelineRamya RamasubramanianNoch keine Bewertungen

- ACA Question BankDokument19 SeitenACA Question BankVanitha VivekNoch keine Bewertungen

- CA Classes-86-90Dokument5 SeitenCA Classes-86-90SrinivasaRaoNoch keine Bewertungen

- OLP NotesDokument11 SeitenOLP NotesSathish NarayananNoch keine Bewertungen

- Dynamic Scheduling:-: If An Instruction Is Stalled in The Pipeline, No Later Instructions Can ProceedDokument4 SeitenDynamic Scheduling:-: If An Instruction Is Stalled in The Pipeline, No Later Instructions Can ProceednaveedzamanNoch keine Bewertungen

- CA Classes-91-95Dokument5 SeitenCA Classes-91-95SrinivasaRaoNoch keine Bewertungen

- EC6009 Unit 2 IQDokument3 SeitenEC6009 Unit 2 IQshahul hameedNoch keine Bewertungen

- ACA Unit 3Dokument17 SeitenACA Unit 3Fak Profi LesNoch keine Bewertungen

- System On Chip: Inside Processor Pipeline StallsDokument12 SeitenSystem On Chip: Inside Processor Pipeline StallsPinagani SurajNoch keine Bewertungen

- RISC Instruction Set:: I) Data Manipulation InstructionsDokument8 SeitenRISC Instruction Set:: I) Data Manipulation InstructionsSwarup BharNoch keine Bewertungen

- Ee/Ce 6370 Spring 2015: Design Assignment: Utd Pipelined MicroprocessorDokument7 SeitenEe/Ce 6370 Spring 2015: Design Assignment: Utd Pipelined MicroprocessorRohit YedidaNoch keine Bewertungen

- Unit 3: Machine InstructionsDokument16 SeitenUnit 3: Machine Instructionsshreya ChauhanNoch keine Bewertungen

- 03ILP Speculation and Advanced TopicsDokument48 Seiten03ILP Speculation and Advanced TopicsUzair AliNoch keine Bewertungen

- MPI Lab ManualDokument103 SeitenMPI Lab ManualVeerayya JavvajiNoch keine Bewertungen

- Microprocessor: Viva QuestionsDokument6 SeitenMicroprocessor: Viva QuestionshrrameshhrNoch keine Bewertungen

- Hold and Setup Violation and SDFDokument2 SeitenHold and Setup Violation and SDFIlaiyaveni IyanduraiNoch keine Bewertungen

- MPMC Final QBDokument194 SeitenMPMC Final QBSYEDNoch keine Bewertungen

- Instruction Pipeline Design, Arithmetic Pipeline Deign - Super Scalar Pipeline DesignDokument34 SeitenInstruction Pipeline Design, Arithmetic Pipeline Deign - Super Scalar Pipeline DesignMarlon TugweteNoch keine Bewertungen

- Pipeline Hazards - Computer ArchitectureDokument5 SeitenPipeline Hazards - Computer ArchitectureBalu vakaNoch keine Bewertungen

- Hyderabad HTMLDokument16 SeitenHyderabad HTMLrithika14Noch keine Bewertungen

- System On Chip: Inside Processor Pipeline StallsDokument12 SeitenSystem On Chip: Inside Processor Pipeline StallsPinagani SurajNoch keine Bewertungen

- Tuesday, October 31, 2023 10:53 PM: Discuss, The Schemes For Dealing With The Pipeline Stalls Caused by Branch HazardsDokument7 SeitenTuesday, October 31, 2023 10:53 PM: Discuss, The Schemes For Dealing With The Pipeline Stalls Caused by Branch Hazardskrahul74714Noch keine Bewertungen

- VIMP Micro QuestionsDokument68 SeitenVIMP Micro QuestionsayushnaleNoch keine Bewertungen

- PIC Architecture and Assembler Programming: (Including Software Time Delay Subroutine)Dokument16 SeitenPIC Architecture and Assembler Programming: (Including Software Time Delay Subroutine)Ashim KumarNoch keine Bewertungen

- Instruction-Level Parallelism (ILP), Since TheDokument57 SeitenInstruction-Level Parallelism (ILP), Since TheRam SudeepNoch keine Bewertungen

- HW2 Operating SystemsDokument9 SeitenHW2 Operating SystemsSainadh GodenaNoch keine Bewertungen

- MPI Lab ManualDokument68 SeitenMPI Lab Manualsansure100% (1)

- Sections 3.2 and 3.3 Dynamic Scheduling - Tomasulo's AlgorithmDokument53 SeitenSections 3.2 and 3.3 Dynamic Scheduling - Tomasulo's AlgorithmvpsampathNoch keine Bewertungen

- Artifact FLO1 2 ELab Learning ToolsDokument31 SeitenArtifact FLO1 2 ELab Learning ToolsMurali KrishnaNoch keine Bewertungen

- Instruction Level Parallelism-Concepts N ChallengesDokument4 SeitenInstruction Level Parallelism-Concepts N ChallengesJiju_Joseph_1288100% (1)

- ACA Unit 3 - Part - Hardware Based Speculation Notes - Unit 8Dokument5 SeitenACA Unit 3 - Part - Hardware Based Speculation Notes - Unit 8Ashwini BangeraNoch keine Bewertungen

- Draw The Block Diagram of Von Neumann Architecture and Explain About Its Parts in Brief AnswerDokument7 SeitenDraw The Block Diagram of Von Neumann Architecture and Explain About Its Parts in Brief AnswerhayerpaNoch keine Bewertungen

- ACA - Two MarksDokument17 SeitenACA - Two MarksAarthy Sekar DNoch keine Bewertungen

- OS - IAT3 Two Marks QB PDFDokument4 SeitenOS - IAT3 Two Marks QB PDF21ITA10 KANNATHALNoch keine Bewertungen

- CA Classes-136-140Dokument5 SeitenCA Classes-136-140SrinivasaRaoNoch keine Bewertungen

- Comparch Comparch-002 Exams Midterm A8Xj46NCRoDokument9 SeitenComparch Comparch-002 Exams Midterm A8Xj46NCRoMattia LeNoch keine Bewertungen

- Chapter 2 ProposedDokument62 SeitenChapter 2 Proposedvincent tekeyNoch keine Bewertungen

- Intel MP Architecture & Assembly ProgrammingDokument16 SeitenIntel MP Architecture & Assembly ProgrammingDaisuke SSNoch keine Bewertungen

- Very Large Instruction Word (Vliw) Processors: What Is Good and What Is Bad With Superscalars ?Dokument11 SeitenVery Large Instruction Word (Vliw) Processors: What Is Good and What Is Bad With Superscalars ?Avinash KumarNoch keine Bewertungen

- Mod 5 Book 2 Computers Fiber Optics, Esds Flight InstrumentsDokument99 SeitenMod 5 Book 2 Computers Fiber Optics, Esds Flight Instrumentsranjit prasadNoch keine Bewertungen

- Cad For Vlsi 2 Pro Ject - Superscalar Processor ImplementationDokument10 SeitenCad For Vlsi 2 Pro Ject - Superscalar Processor ImplementationkbkkrNoch keine Bewertungen

- The Software of The KDF9Dokument25 SeitenThe Software of The KDF9nomen nescioNoch keine Bewertungen

- Exp 2Dokument10 SeitenExp 2NAFISA ISLAM 1808006Noch keine Bewertungen

- Assignment 4: Course Instructor / Lab EngineerDokument8 SeitenAssignment 4: Course Instructor / Lab EngineerNitasha HumaNoch keine Bewertungen

- Order By: 5. UnionDokument20 SeitenOrder By: 5. UnionRaunak RoyNoch keine Bewertungen

- Embedded System Design-NPTEL-NOTESDokument38 SeitenEmbedded System Design-NPTEL-NOTESGulshan Upreti100% (1)

- Minimizes Data HazardsDokument10 SeitenMinimizes Data HazardsJagadish BabuNoch keine Bewertungen

- MCSE-103 by Mohd AbdullahDokument9 SeitenMCSE-103 by Mohd AbdullahabhayNoch keine Bewertungen

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationVon EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNoch keine Bewertungen

- Resume 1622554790Dokument1 SeiteResume 1622554790Jiju_Joseph_1288Noch keine Bewertungen

- Installation of Virtual Box and VAGRANT On Cent OS 7Dokument1 SeiteInstallation of Virtual Box and VAGRANT On Cent OS 7Jiju_Joseph_1288Noch keine Bewertungen

- Dbms Ut II Answer KeyDokument3 SeitenDbms Ut II Answer KeyJiju_Joseph_1288Noch keine Bewertungen

- Operating System 2 MarksDokument2 SeitenOperating System 2 MarksJiju_Joseph_12880% (1)

- Dbms UT I Answer KeyDokument4 SeitenDbms UT I Answer KeyJiju_Joseph_1288Noch keine Bewertungen

- CS 2354 - 2 MarksDokument2 SeitenCS 2354 - 2 MarksJiju_Joseph_1288Noch keine Bewertungen

- Instruction Level Parallelism-Concepts N ChallengesDokument4 SeitenInstruction Level Parallelism-Concepts N ChallengesJiju_Joseph_1288100% (1)

- Learning Activity 3 / Actividad de Aprendizaje 3 Evidence: Cell Phones For Sale / Evidencia: Celulares A La VentaDokument3 SeitenLearning Activity 3 / Actividad de Aprendizaje 3 Evidence: Cell Phones For Sale / Evidencia: Celulares A La VentaKaventinas SASNoch keine Bewertungen

- Principles of Management Assignment by 20191bbl0061 Mohammed RohinDokument4 SeitenPrinciples of Management Assignment by 20191bbl0061 Mohammed RohinRohin Bin RafiNoch keine Bewertungen

- Association RulesDokument20 SeitenAssociation RulesAnik1005Noch keine Bewertungen

- Jannatul Bakia Afrida (1910117) - GSG 303 (Sec: 01) - Date: March 7, 2021Dokument4 SeitenJannatul Bakia Afrida (1910117) - GSG 303 (Sec: 01) - Date: March 7, 2021Ara AdibaNoch keine Bewertungen

- Self-Learning Modules - EEnglish-7-Q3-M1Dokument7 SeitenSelf-Learning Modules - EEnglish-7-Q3-M1bom ybanezNoch keine Bewertungen

- Coiled-Tubing Services: Transforming Your InterventionDokument8 SeitenCoiled-Tubing Services: Transforming Your Interventionoswaldo58Noch keine Bewertungen

- DD 1 2 Practice Ryder CookDokument3 SeitenDD 1 2 Practice Ryder CookJessica IreneNoch keine Bewertungen

- AD-330 AD-320 Parts Manual PN 450239 (Rev-1) 042803Dokument46 SeitenAD-330 AD-320 Parts Manual PN 450239 (Rev-1) 042803naokito AkemiNoch keine Bewertungen

- Robotics Unit4 SlidesDokument72 SeitenRobotics Unit4 SlidesJanarthanan BalakrishnasamyNoch keine Bewertungen

- Revision Q (Answer)Dokument6 SeitenRevision Q (Answer)Johan ZafriNoch keine Bewertungen

- PF ProjectDokument16 SeitenPF Projectsunnia munsifNoch keine Bewertungen

- API RP 96 - Deepwater Well Design and Construction. Annex C - Inflow Test ExamplesDokument5 SeitenAPI RP 96 - Deepwater Well Design and Construction. Annex C - Inflow Test ExamplesjuanNoch keine Bewertungen

- Ventura Highway Tab GuitarDokument3 SeitenVentura Highway Tab GuitarRodolfo Fiorina100% (1)

- ASHRAE Journal - VAV System Duct Main DesignDokument5 SeitenASHRAE Journal - VAV System Duct Main DesignJhoNoch keine Bewertungen

- Zeiss AI EbookDokument56 SeitenZeiss AI EbookRaylson De SÁ Melo UFCNoch keine Bewertungen

- CT Scanner Asteion Super 4 PDFDokument16 SeitenCT Scanner Asteion Super 4 PDFYusef ManasrahNoch keine Bewertungen

- Understanding Security Capability of Information System1Dokument6 SeitenUnderstanding Security Capability of Information System1upadhyay kulbhushanNoch keine Bewertungen

- CAL-00-E-0004 Rev-1 ELECTRICAL CABLE SIZINGDokument5 SeitenCAL-00-E-0004 Rev-1 ELECTRICAL CABLE SIZINGtceterexNoch keine Bewertungen

- Heating Product 2019 CatalogueDokument10 SeitenHeating Product 2019 Catalogueapi-404330673Noch keine Bewertungen

- Woodward Governor Actuator Groups SELD0134-08Dokument7 SeitenWoodward Governor Actuator Groups SELD0134-08reng1994Noch keine Bewertungen

- Oracle Process ExecutionDokument552 SeitenOracle Process ExecutionVineethNoch keine Bewertungen

- DR - Sri.Sri - Sri.Shivakumara Mahaswamy College of Engineering Department of Civil Engineering I InternalDokument2 SeitenDR - Sri.Sri - Sri.Shivakumara Mahaswamy College of Engineering Department of Civil Engineering I InternalCivil EngineeringNoch keine Bewertungen

- Horquillas CascadeDokument56 SeitenHorquillas CascadeBeatriz Miranda Mellado100% (1)

- Wafer 5825&6Dokument1 SeiteWafer 5825&6RB STNoch keine Bewertungen

- BS 5446-2Dokument34 SeitenBS 5446-21limonataNoch keine Bewertungen

- Acclarix LX9 Series Datasheet-V2.2Dokument27 SeitenAcclarix LX9 Series Datasheet-V2.2Marcos CharmeloNoch keine Bewertungen

- PMP-901 & 902 - 2. DSGN-SP-0005 Glycol Pump - MHN-12-02TN - DatasheetDokument2 SeitenPMP-901 & 902 - 2. DSGN-SP-0005 Glycol Pump - MHN-12-02TN - DatasheetfarhaNoch keine Bewertungen

- Input Devices of A ComputerDokument9 SeitenInput Devices of A ComputerJerick Enrique FegaridoNoch keine Bewertungen

- B01000 - CAT - EN - A4 - V53 INEREX eDokument32 SeitenB01000 - CAT - EN - A4 - V53 INEREX eGUDANG KARAOKE KITANoch keine Bewertungen