Beruflich Dokumente

Kultur Dokumente

Design and Implementation of 64 Bit Multiplier by Using Carry Save Adder

Hochgeladen von

Ravikanth Gella0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

140 Ansichten5 SeitenDesign and Implementation of 64 Bit Multiplier by Using Carry Save Adder

Copyright

© © All Rights Reserved

Verfügbare Formate

DOCX, PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenDesign and Implementation of 64 Bit Multiplier by Using Carry Save Adder

Copyright:

© All Rights Reserved

Verfügbare Formate

Als DOCX, PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

140 Ansichten5 SeitenDesign and Implementation of 64 Bit Multiplier by Using Carry Save Adder

Hochgeladen von

Ravikanth GellaDesign and Implementation of 64 Bit Multiplier by Using Carry Save Adder

Copyright:

© All Rights Reserved

Verfügbare Formate

Als DOCX, PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 5

Design And Implementation Of 64 Bit

Multiplier By Using Carry Save Adder

MOHAMMAD JAVEED, GELLA RAVIKANTH

Project Lead, Associate Professor

Javeed.mohammad417@gmail.com, gellaravikanth@gmail.com

which are used basically for the storage and

AbstractIn this paper we have shown the

design and implementation of 64 bit multiplier

by using multi bit flip flop shift register and

carry save adder . In arithmetic operations

addition and multiplication are having a major

role. When the number of bits increases, the

complexity of adder circuits increases and

speed performance decreases. Our proposed

system uses two 64 bit numbers and multiply

to form a 128 bit number, which is for larger

applications. Proposed carry save adder based

multiplier, On comparing with the carry look

ahead adder based 64 bit multiplier, the results

showing time (speed) decreased by 93.5%

approximately and when comparing with the

carry select adder based 64 bit multiplier time

(speed) decreased up to 88%. The code is

written in VHDL and synthesized the design in

Xilinx

ISE

10.1

Version

and

hardware

implementation is in Spartan 3E FPGA family.

Key words Shift register, Single bit flip

flop, Multi bit flip flop, Carry look ahead adder,

carry select adder, carry save adder, vlsi, VHDL,

spartan.

I.

INRODUCTION

A digital designer has to concentrate on

many criteria like Circuit speed, power

consumption, area and cost. While designing

the digital circuits, the fundamental arithmetic

operations like addition and multiplication are

the

main

optimizations.

Our

design

concentrates on multiplication of binary

numbers for larger applications.

For the multiplication operation, adding as

well as shifting of bits is necessary. Considering

these two operations, we have designed a 64

bit multiplier by using carry save adder for

addition and multi bit flip flop based shift

register for shifting of bits.

In this paper we have shown the comparison

among the adders for multiplication based on

the time. On comparison with carry look ahead

adder (CLAA) and carry select adder (CSLA),

carry save adder (CSA) based multiplier is less

complex and results have shown that CSA

based multiplier is very faster than the other

two multipliers.

A shift register is very important digital

building block. It has a large amount of

applications. Registers are often used to

momentarily store binary information appearing

at the output. Shift registers are the logic types

transfer of digital data. The basic storage

elements are the flip flops. The most of the

registers use D flip flops due to its simplicity [1].

Basically a flip flop stores a single bit data. In

our proposed design the flip flop stores a multi

bit data. By using the multi bit flip flops, we

have shown a shift register which is serial in

serial out (SISO). Finally we have designed a 64

bit multiplier by using carry save adder and

multi bit flip flop shift register.

This paper is scheduled as first it discusses

and compares the about the different adders in

sections II, III and IV. After that in section V it

shows the multiplication algorithm with multi bit

flip flop shift register. Section VI illustrates the

simulation results and section VII concludes the

paper.

II.

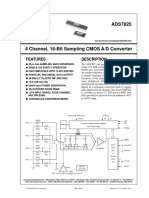

CARRY LOOK AHEAD ADDER

Carry look ahead adder generates carries

parallel at a time. For this we should have the

extra circuitry. Because of these extra circuits

and storage elements Carry Look Ahead adder

needs more area and the power using by the

whole circuit is high. The below equations

describes the pattern how a carry look ahead

generates the carries [2]. Figure 1 shows the

block diagram for carry look ahead adder.

B63

A63B2

A2 B1A1 B0

A0

F F F F

.

Cout

AC3. AC2 AC1 A

S63 . S2

.

S1

C0

S0

Figure 1. Carry look ahead adder

Let Gi be the generating the function and P i

be the propagating function then we can write

the carries as

Ci+1=A.B+ (A xor B).Ci, Where

(1)

Gi = A.B

Pi= (A xor B).Ci

(2)

(3)

From the equations (1) (2) (3), we can

understand that the sum of adder circuit does

not depend on the carry generation so we can

generate all the carries at a time as

need not to wait for the previous stage carry.

So, the time taken to perform the addition

operation decreases. We can see a significant

improvement in time.

C1= A0.B0 + (A0 xor B0). C0

C2=A1.B1 + (A1 xor B1). C1

C3=A2.B2 + (A2 xor B2). C2 ..

C64=A63.B63 + (A63 xor B63).C63

The sum of the adder is written as

IV.

The carry save addition further can decrease

the timing performance of the addition. In this

carry save addition the carry is neglected first

and only sum will be considered [4]. Let us see

one example for the carry save addition with

two numbers A and B

SUM= A xor B xor C

III.

CARRY SELECT ADDER

Carry select adder is a different from the

carry look ahead adder, in which we select the

carry as 0 once and again select the carry as 1.

After that, we perform the addition operation for

the both cases and give these outputs to the

2:1 multiplexer. Finally we receive the single

output. So, we do not need to wait for previous

addition result to the next step [3]. The figure 2

represents the carry select adder. The

multiplexer output equations for sum and

carries are

Sum function is as follows

If carry =1 then,

SUM0= A0 xor B0 xor Carry

If carry =0 then,

SUM0=A0 xor B0

B63

A1

A0

F

A3

A2

F B2

FB1

FB0

0

0

0

Cout 1 . 1 1 01

A A A A

CARRY SAVE ADDER

A:

3456

B:

4365

Sum:

7711

The carries generated by the addition are

neglected here are 0 0 1 1. Now these carries

can be shifted to the left and add to the sum, as

Shifted Carries: 0 1 1

Sum: 7 7 1 1

Total sum: 7 8 2 1

Carry save adder does not have more

complexity as carry select adder and carry look

ahead adder. So, we have implemented 64 bit

multiplier by using the carry save adder. Even

though it needs large amount of registers to

store the carries separately, this can be

advantageous in its speed performance. The

main advantage of carry save addition is it can

add three bits at a time. But in our design we

are not considering multi operand redundant

addition. The third bit is considering as zero.

Figure 3 represents the carry save adder block

diagram.

2:1 MUX

2:1 MUX

2:1 MUX

2:1 MUX

S63 S2 S1 S0

.

.

.

.

Figure 2. Carry select adder

These two SUMs will be given to the

multiplexer. Here, to perform the operation

Figure 3. Carry save adder

V.

MULTIPLICATION ALGORITHM

Let the product size be 128. Multiplier and

multiplicand are 64 bit. Clear the most

significant half of the product register. Store the

multiplier in the least significant half of the

product register. The repeat the following steps

64 times.

If the least significant bit of the

product register is 1 then add the

multiplicand to the most significant

half of the product register.

Shift the content of the product

register one bit to the right (ignore

the shifted-out bit.)

Shift-in the carry bit into the most

significant bit of the product register

[5]

[6]

[7].

The

multiplication

algorithm shows in figure 4.

S

N

HI

BI

F

T

T

M

M

MULTIPLICAND

A 10a

MMn-2

D

n

n A

A10 d QQ10

CAAn-2D

QQn-2

- E MULTIPLIER

A

n R

nD

1

-D

MB

FF

D1

D2

CLK

MB

FF

Q1

Q2

Figure 5. Multi bit flip flop shift register

CLK

D1

Q1

D2

Q2

Figure 6. Timing diagram for multi bit flip flop

Figure 4. Multiplication algorithm

Here the important issue is to shift the bits.

We are proposing a shift register by using the

multi bit flip flops. Generally for the storage of

bits the memory elements are latches and flip

flops. The flip flop casually stores a single bit

value. Here in our proposed system the flip flop

stores the multi bits. Finally we designed a shift

register by using the multi bit two flip flops. The

diagram for the shift register, serial in serial out

is shown in the figure 5. The edge triggering D

flip flop output takes the input value when clock

goes high in positive edge triggering and takes

the input value when clock goes low in negative

edge triggering. The multi bit flip flop works

under the technique of merging the clock pulses

[8]. The timing diagram for multi bit flip flop is

shown in figure 6 which is having the operation

for negative edge triggering D flip flop as

Initially Q1 and Q2 are assumed to be

high, D1 and D2 are low, and clock (CLK)

is low.

At the negative going edge of the first

clock pulse, D1 and D2 are low, so, Q1

and Q2 are also low.

At the second negative going pulse of

clock, D1 and D2 are high, so, Q1 and Q2

are also high.

At the negative transition edge of the

second clock pulse, D is high and Q1 and

Q2 are high.

And the same will continue

VI.

SIMULATION RESULTS

The analysis of 64 bit multiplier designed

based on carry save adder by using multi bit flip

flop shift register. The design is simulated in

Xilinx ISE 10.1 version. The results are shown in

the following figures. Fig. 7, Fig., 8, Fig 9 are the

timing details of the multiplier based on CLAA,

CSLA and CSA respectively by using multi bit

flip flop shift register. Table 1 shows the clear

timing details for the multiplier. Fig 10, Fig 11,

Fig 12 shows the wave forms generated for the

three different multipliers. Fig 13 (a) and (b)

shows the RTL schematics for the carry save

adder based 64 bit multiplier by using multi bit

flip flop shift register. Proposed design

implemented on Spartan 3e tool.

Figure 7. Timing performance of carry look

ahead adder based multiplier

Figure 12. Wave form generation for carry

save adder based multiplier

Figure 8. Timing performance of carry select

adder based multiplier

(a)

(b)

Figure 13. RTL views for carry save adder

based multiplier

Figure 9. Timing performance of carry save

adder based multiplier

TABLE I TIMING ANALYSIS

TIME (ns)

CLAA

37.271

CSLA

20.804

CSA

2.379

Figure 10. Wave form generation for carry

look ahead adder based multiplier

VII.

CONCLUSION

A design and implementation of 64 bit

multiplier with different adders have shown in

this paper. VHDL language is used to simulate

and synthesize the multiplier. By using the carry

save adder improved the overall speed of the

design. We have shown that proposed multiplier

increased its speed by 93.5 % when compared

with the CLAA and 88% when compared with

CSLA. A fast adder can significantly improve the

performance of the multiplier. Over all the

speed performance of the multiplier based on

carry save adder is high. Even though the area

increases by using the carry save adder, it is

negligible when compared to the speed

performance.

REFERENCES

[1] Anand kumar Fundamentals of digital circuits

Prentice hall India publications, 2004.

[2] Jagannath Samanta, Mousam Halder, Bishnu

Prasad De Performance Analysis of High Speed

Low Power Carry Look-Ahead Adder Using

Different Logic Styles International Journal of Soft

Computing and Engineering (IJSCE) ISSN: 22312307, Volume-2, Issue-6, Jan- 2013

Figure 11. Wave form generation for carry

select adder based multiplier

[3] Deepthi Obul Reddy, P.Ramesh Yadav Carry

Select Adder with Low Power and Area

Efficiency. International Journal of Engineering

Research and Development, Volume 3, Issue 3

(August 2012), PP. 29-35.

[4] D.R Lutz, D.N. JayaSimha, The power of carry

save addition, Department of computer and

Information Science, The Ohio State University,

1991.

[5] Hasan Krad* and Aws Yousif** Design and

Implementation of a Fast Unsigned 32-bit

Multiplier

Using

VHDL

Qatar

University/Department of Computer Science &

Engineering, Doha, Qatar.

[6] W.

Stallings,

Computer

Organization

and

Architecture Designing for Peljormance, 71h ed.,

Prentice Hall, Pearson Education International,

USA, 2006, ISBN: 0-13-185644-8.

[7] V.Vijayalakshmil, R.Seshadd, Dr.S.Ramakrishnan3

Design and Implementation of 32 Bit Unsigned

Multiplier Using CLAA and CSLA IEEE 2013.

[8] G. Prakash, K.Sathishkumar, B. Sakthibharathi S.

Saravanan, R. Vijaysai Achieveing reduced area

by multi-bit flip flop design International

Conference on Computer Communication and

Informatics (ICCCI -2013), Jan. 04 06, 2013,

Coimbatore, INDIA, 2013

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- VSICM7 M08 Resource Manage MonitorDokument78 SeitenVSICM7 M08 Resource Manage Monitorhacker_05Noch keine Bewertungen

- M01 Opnet MM1Dokument35 SeitenM01 Opnet MM1Engr. Sohaib JamalNoch keine Bewertungen

- 3500/40M Proximitor Monitor Module: Operation and Maintenance ManualDokument245 Seiten3500/40M Proximitor Monitor Module: Operation and Maintenance Manualnabil160874Noch keine Bewertungen

- Vsphere 5.5 Command Line Documentation Vsphere Command-Line Interface Documentation Vsphere Command-Line Interface ReferenceDokument23 SeitenVsphere 5.5 Command Line Documentation Vsphere Command-Line Interface Documentation Vsphere Command-Line Interface ReferenceJohn PrincipioNoch keine Bewertungen

- Learn Azure Fundamentals and Provision SQL DatabaseDokument21 SeitenLearn Azure Fundamentals and Provision SQL Databaseekta agarwalNoch keine Bewertungen

- Access Level 2Dokument277 SeitenAccess Level 2Bathina Srinivasa RaoNoch keine Bewertungen

- HRMS Implementation Setup Process in Oracle AppsDokument5 SeitenHRMS Implementation Setup Process in Oracle AppsFerasHamdanNoch keine Bewertungen

- CCNA Lab Topology 100406Dokument34 SeitenCCNA Lab Topology 100406api-3748256100% (2)

- Atmel 6430 32 Bit Cortex M3 Microcontroller SAM3U4 SAM3U2 SAM3U1 - Datasheet PDFDokument1.163 SeitenAtmel 6430 32 Bit Cortex M3 Microcontroller SAM3U4 SAM3U2 SAM3U1 - Datasheet PDFsamuel moraNoch keine Bewertungen

- How To Use Dlink 2750u As RepeaterDokument3 SeitenHow To Use Dlink 2750u As RepeaterAbhinav SrivastavaNoch keine Bewertungen

- Ea Virtual DocumentsDokument5 SeitenEa Virtual DocumentsArturo GarciaNoch keine Bewertungen

- Dice Resume CV Nuvraj DhanjalDokument1 SeiteDice Resume CV Nuvraj Dhanjalvamsi chinniNoch keine Bewertungen

- Report AutocadDokument38 SeitenReport AutocadRISHAV RAUSHANNoch keine Bewertungen

- BIT2117 Accounting Information SystemsDokument85 SeitenBIT2117 Accounting Information SystemsJames MuthuriNoch keine Bewertungen

- M3 Service BlueprintingDokument12 SeitenM3 Service BlueprintingGhiffariNoch keine Bewertungen

- Excel Template Saves Time Configuring RedPrairie WMS ReplenishmentsDokument9 SeitenExcel Template Saves Time Configuring RedPrairie WMS ReplenishmentsChristian RNNoch keine Bewertungen

- Nonlinear Model Predictive Control Based On Existing Mechanistic Models of Polymerisation ReactorsDokument27 SeitenNonlinear Model Predictive Control Based On Existing Mechanistic Models of Polymerisation Reactorsfadatamo2Noch keine Bewertungen

- Image Captioning Generator Using Deep Machine LearningDokument3 SeitenImage Captioning Generator Using Deep Machine LearningEditor IJTSRDNoch keine Bewertungen

- Lab practical 7 - Monthly rainfall analysis and sales commission calculatorDokument4 SeitenLab practical 7 - Monthly rainfall analysis and sales commission calculatorYaniNoch keine Bewertungen

- Exception Handling Interview QuestionsDokument9 SeitenException Handling Interview Questionsmangala rNoch keine Bewertungen

- Features Description: 1996 Burr-Brown Corporation PDS-1304B Printed in U.S.A. October, 1997Dokument16 SeitenFeatures Description: 1996 Burr-Brown Corporation PDS-1304B Printed in U.S.A. October, 1997Hector Jose Murillo CordobaNoch keine Bewertungen

- Ashish SoftwareDokument2 SeitenAshish SoftwareKumar RajputNoch keine Bewertungen

- BI Apps 11.1.1.8.1 Configuration GuideDokument476 SeitenBI Apps 11.1.1.8.1 Configuration Guidemsujankumar100% (1)

- MemoCam Application User Guide V01 PDFDokument173 SeitenMemoCam Application User Guide V01 PDFJorge HuangNoch keine Bewertungen

- Verbose logging startedDokument35 SeitenVerbose logging startedemartemm1503Noch keine Bewertungen

- GG 244001Dokument200 SeitenGG 244001Yeshwanth G SomasundaramNoch keine Bewertungen

- Numerical Lab Assignment2Dokument11 SeitenNumerical Lab Assignment2Ramo comNoch keine Bewertungen

- ComboDokument390 SeitenComboValvolt NovaNoch keine Bewertungen

- Curriculum Vitae Ramya-1Dokument4 SeitenCurriculum Vitae Ramya-1meghaNoch keine Bewertungen

- 5th Lecture - 8085 Timing DiagramDokument18 Seiten5th Lecture - 8085 Timing Diagramcgupta1be21Noch keine Bewertungen