Beruflich Dokumente

Kultur Dokumente

Design and Analysis of A Conventional Wallace Multiplier in 180nm CMOS Technology

Hochgeladen von

International Organization of Scientific Research (IOSR)Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Design and Analysis of A Conventional Wallace Multiplier in 180nm CMOS Technology

Hochgeladen von

International Organization of Scientific Research (IOSR)Copyright:

Verfügbare Formate

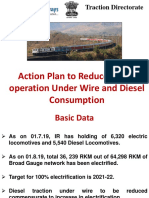

IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)

Volume 5, Issue 1, Ver. I (Jan - Feb. 2015), PP 60-65

e-ISSN: 2319 4200, p-ISSN No. : 2319 4197

www.iosrjournals.org

Design and Analysis of a Conventional Wallace Multiplier in

180nm CMOS Technology

Inamul Hussain1, Manish Kumar2

1

(PG Student, Department of ECE, NERIST, Nirjuli, Arunachal Pradesh, India)

(Assistant Professor, Department of ECE, NERIST, Nirjuli, Arunachal Pradesh, India

Abstract: Multiplier is an important building block in many electronic system design. There are many available

methods and techniques for designing multipliers. Wallace multiplier is important and popular multiplier

architecture. In this paper, design and analysis of a conventional Wallace multiplier is presented by using

Cadence virtuoso in 180nm CMOS technology. Performance analysis in terms of power, delay, and power delay

product are performed for a 4-bit Wallace multiplier in 180nm CMOS technology. The power and delay of the

designed multiplier are 689.3W and 50s respectively.

Keywords: Delay, Multiplier, Power delay product, Power Dissipation, Wallace multiplier.

I.

Introduction

In any signal processing system, multiplier is an important and a basic building block element [1]. The

performance of these types of processing systems depends on the performance of the inbuilt multiplier [2]. So it

is a challenging task for any designer to design a high performance multiplier. There are different factors that

drive for high performance electronic system design in terms of low power dissipation and high speed [3-4].

The block diagram of a multiplier is shown in Fig.1. A basic multiplier consists of three stages:

generation of partial product, addition of partial product and final addition.

Fig.1 Block diagram of a multiplier

A multiplier based on Wallace-tree structure is called Wallace multiplier. It is substantially faster than

other multiplier architecture [5]. The operation of a Wallace multiplier is carried out in three different steps [57]. After generating the partial product, these are accumulated in different stages.

The different steps involved in Wallace multiplier are:

Step1: Partial product generation.

Step2: (i) Accumulation of partial product in different stages by

Ri+1 = 2(Ri /3)+ Ri mod 3

(1)

where Ri denotes the groups or stages and R0 =N, is the number of rows in the initial bit product array

(ii) Adjacent three rows are reduced by using the full adder and the half adder. Remaining rows are carried to

the next step. The process continues until last stage contains two rows.

Step3: Remaining two rows are added by the full adder.

II.

Designing A Wallace Multiplier

Fig. 2 shows a 4-bit conventional Wallace multiplier by applying all the three steps of the

multiplication process. S00, S01, S02, S03, S10, S11, S12, S13, S20, S21, S22, S23, S30, S31, S32 and S33 are

the partial product terms, while Z0, Z1, Z2, Z3, Z4, Z5, Z6 and Z7 are the final product.

DOI: 10.9790/4200-05116065

www.iosrjournals.org

60 | Page

Design and Analysis of a Conventional Wallace Multiplier in 180nm CMOS Technology

Fig.2 Architecture of a 4x4 Wallace multiplier

A Wallace multiplier is designed in three different modules:

i. Partial product generation module.

ii. Grouping of partial product module.

ii. Final addition module.

2.1 Designing Of Partial Product Module

The partial product module of a 4-bit Wallace multiplier is shown in Fig.3. For generating the partial

product, AND gate is used. The total number of partial product in a 4-bit Wallace multiplier is 16. So for

designing the partial product module, 16 AND gates are used. The cellview of the partial product generator is

also designed and is shown in Fig.4.

Fig.3 Partial product generation module

Fig.4 Cellview of partial product generator module

DOI: 10.9790/4200-05116065

www.iosrjournals.org

61 | Page

Design and Analysis of a Conventional Wallace Multiplier in 180nm CMOS Technology

2.2 Grouping Of Partial Product Module

Fig.5. shows the grouping of partial product module of a 4-bit Wallace multiplier. (1) is used for

grouping of the partial product. For two bit addition, half adder is used and for three bit addition, full adder is

used. The cellview of grouping of partial product module is shown in Fig.6.

Fig.5 Grouping of partial product module

Fig.6 Cellview of grouping of partial product module

2.3 Final Addition Module

Fig.7 shows the final addition module of a 4-bit Wallace multiplier. After the grouping and staging of

partial product, final addition module is designed. The cellview of the final addition module is shown in Fig. 8.

In this figure, P1, P2, P3, P4, P5, P6 and P7 are final product terms.

Fig.7 Final addition module

DOI: 10.9790/4200-05116065

www.iosrjournals.org

62 | Page

Design and Analysis of a Conventional Wallace Multiplier in 180nm CMOS Technology

Fig.8 Cellview of final addition module

2.4 Designing A 4-Bit Wallace Multiplier

A 4-bit Wallace multiplier is shown in Fig. 9, which is designed after combining all the three modules.

The inputs are connected to the partial product generator module and the outputs of the partial product module

are connected as per the architecture of Wallace multiplier.

Fig. 8 A 4-bit Wallace multiplier

DOI: 10.9790/4200-05116065

www.iosrjournals.org

63 | Page

Design and Analysis of a Conventional Wallace Multiplier in 180nm CMOS Technology

III.

Results And Analysis

Cadence Virtuoso is used for designing a 4-bit Wallace multiplier in 180nm CMOS technology.

Transient analysis is performed for this multiplier. Performance analysis in terms of power dissipation, delay,

and power delay product are observed by using Cadence virtuoso in 180nm CMOS technology. The

conventional 4-bit Wallace multiplier is designed by using AND gate, half adder and full adder. Table 1 shows

the total numbers of components used for designing this multiplier.

Table 1: Total number of components used in designing a 4-bit conventional Wallace multiplier

Total number of PMOS used

Total number of NMOS used

Total number of half adder used

Total number of full adder used

249

249

3

9

3.1 Transient Analysis

The transient analysis of a 4-bit Wallace multiplier is done by applying two inputs each of 4-bit. Input

and output transient waveforms for the multiplier are shown in the Fig.9 and Fig.10 respectively.

Fig.9 Input transient waveform

Fig.10 Output transient waveform

DOI: 10.9790/4200-05116065

www.iosrjournals.org

64 | Page

Design and Analysis of a Conventional Wallace Multiplier in 180nm CMOS Technology

3.2 Performance Analysis

Table 2 shows the performance of a 4-bit Wallace multiplier in terms of power dissipation, delay, and

power delay product.

Table 2: Performance of a 4-bit Wallace multiplier

Power dissipation

Delay

Power delay product

IV.

689.3W

50s

34.465nWs

Conclusion

In this paper, design and analysis of a conventional 4-bit Wallace multiplier is performed in 180nm

CMOS technology. The power and delay of the designed multiplier are found to be 689.3W and 50s.

References

[1].

[2].

[3].

[4].

[5].

[6].

[7].

C. S. Wallace, A Suggestion for a Fast Multiplier, IEEE Transactions on Computers, 13, 1964,14-17.

E. E. Swartzlander, and R. S. Waters, A Reduced Complexity Wallace Multiplier Reduction, IEEE Transactions on Computers, 59,

2010, 1134-1137.

M. Kumar, M. A. Hussain, and S. K. Paul, Performance of a Two Input Nand Gate Using Subthreshold Leakage Control

Techniques, Journal of Electron Devices, 14, 2012, 1161-1169.

M. Kumar, M. A. Hussain, and L. K. Singh, Design of a Low Power High Speed ALU in 45nm Using GDI Technique and its

Performance Comparison, Communications in Computer and Information Science, Springer Berlin Heidelberg, 142, 2011, 458-463.

P.V. Rao, C. P. R. Prasanna, and S. Ravi, VLSI Design and Analysis of Multipliers for Low Power, IEEE Fifth International

Conference on Intelligent Information Hiding and Multimedia Signal Processing, Kyoto, 2009, 1354-1357.

D. R. Gandhi, and N. N. Shah, Comparative Analysis for Hardware Circuit Architecture of Wallace Tree Multiplier, IEEE

International Conference on Intelligent Systems and Signal Processing, Gujarat, 2013, 1-6.

K. G. Krishna, B. Santhosh, and V. Sridhar, Design of Wallace Tree Multiplier using Compressors, International Journal of

Engineering Sciences & Research Technology, 2, 2013, 2249-2254.

DOI: 10.9790/4200-05116065

www.iosrjournals.org

65 | Page

Das könnte Ihnen auch gefallen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Pervertible Practices: Playing Anthropology in BDSM - Claire DalmynDokument5 SeitenPervertible Practices: Playing Anthropology in BDSM - Claire Dalmynyorku_anthro_confNoch keine Bewertungen

- Chord ProgressionDokument6 SeitenChord ProgressiongernNoch keine Bewertungen

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Classwork Notes and Pointers Statutory Construction - TABORDA, CHRISTINE ANNDokument47 SeitenClasswork Notes and Pointers Statutory Construction - TABORDA, CHRISTINE ANNChristine Ann TabordaNoch keine Bewertungen

- Youth Entrepreneurship: Opportunities and Challenges in IndiaDokument5 SeitenYouth Entrepreneurship: Opportunities and Challenges in IndiaInternational Organization of Scientific Research (IOSR)100% (1)

- Julian's GodsDokument162 SeitenJulian's Godsअरविन्द पथिक100% (6)

- Effects of Formative Assessment On Mathematics Test Anxiety and Performance of Senior Secondary School Students in Jos, NigeriaDokument10 SeitenEffects of Formative Assessment On Mathematics Test Anxiety and Performance of Senior Secondary School Students in Jos, NigeriaInternational Organization of Scientific Research (IOSR)100% (1)

- Factors Affecting Success of Construction ProjectDokument10 SeitenFactors Affecting Success of Construction ProjectInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- The Effect of Instructional Methods and Locus of Control On Students' Speaking Ability (An Experimental Study in State Senior High School 01, Cibinong Bogor, West Java)Dokument11 SeitenThe Effect of Instructional Methods and Locus of Control On Students' Speaking Ability (An Experimental Study in State Senior High School 01, Cibinong Bogor, West Java)International Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Study The Changes in Al-Ahwaz Marshal Using Principal Component Analysis and Classification TechniqueDokument9 SeitenStudy The Changes in Al-Ahwaz Marshal Using Principal Component Analysis and Classification TechniqueInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Philosophical Analysis of The Theories of Punishment in The Context of Nigerian Educational SystemDokument6 SeitenPhilosophical Analysis of The Theories of Punishment in The Context of Nigerian Educational SystemInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Project Based Learning Tools Development On Salt Hydrolysis Materials Through Scientific ApproachDokument5 SeitenProject Based Learning Tools Development On Salt Hydrolysis Materials Through Scientific ApproachInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Development of Dacum As Identification Technique On Job Competence Based-Curriculum in High Vocational EducationDokument5 SeitenDevelopment of Dacum As Identification Technique On Job Competence Based-Curriculum in High Vocational EducationInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Enhancing Pupils' Knowledge of Mathematical Concepts Through Game and PoemDokument7 SeitenEnhancing Pupils' Knowledge of Mathematical Concepts Through Game and PoemInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Students' Perceptions of Grammar Teaching and Learning in English Language Classrooms in LibyaDokument6 SeitenStudents' Perceptions of Grammar Teaching and Learning in English Language Classrooms in LibyaInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Need of Non - Technical Content in Engineering EducationDokument3 SeitenNeed of Non - Technical Content in Engineering EducationInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Necessary Evils of Private Tuition: A Case StudyDokument6 SeitenNecessary Evils of Private Tuition: A Case StudyInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Child Mortality Among Teenage Mothers in OJU MetropolisDokument6 SeitenChild Mortality Among Teenage Mothers in OJU MetropolisInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Geohydrological Study of Weathered Basement Aquifers in Oban Massif and Environs Southeastern Nigeria: Using Remote Sensing and Geographic Information System TechniquesDokument14 SeitenGeohydrological Study of Weathered Basement Aquifers in Oban Massif and Environs Southeastern Nigeria: Using Remote Sensing and Geographic Information System TechniquesInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Microencapsulation For Textile FinishingDokument4 SeitenMicroencapsulation For Textile FinishingInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Comparison of Psychological Variables Within Different Positions of Players of The State Junior Boys Ball Badminton Players of ManipurDokument4 SeitenComparison of Psychological Variables Within Different Positions of Players of The State Junior Boys Ball Badminton Players of ManipurInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Comparison of Explosive Strength Between Football and Volley Ball Players of Jamboni BlockDokument2 SeitenComparison of Explosive Strength Between Football and Volley Ball Players of Jamboni BlockInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Investigation of Wear Loss in Aluminium Silicon Carbide Mica Hybrid Metal Matrix CompositeDokument5 SeitenInvestigation of Wear Loss in Aluminium Silicon Carbide Mica Hybrid Metal Matrix CompositeInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Comparison of Selected Anthropometric and Physical Fitness Variables Between Offencive and Defencive Players of Kho-KhoDokument2 SeitenComparison of Selected Anthropometric and Physical Fitness Variables Between Offencive and Defencive Players of Kho-KhoInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Lipoproteins and Lipid Peroxidation in Thyroid DisordersDokument6 SeitenLipoproteins and Lipid Peroxidation in Thyroid DisordersInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Advancing Statistical Education Using Technology and Mobile DevicesDokument9 SeitenAdvancing Statistical Education Using Technology and Mobile DevicesInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Study of Effect of Rotor Speed, Combing-Roll Speed and Type of Recycled Waste On Rotor Yarn Quality Using Response Surface MethodologyDokument9 SeitenStudy of Effect of Rotor Speed, Combing-Roll Speed and Type of Recycled Waste On Rotor Yarn Quality Using Response Surface MethodologyInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- A Review On Refrigerants, and Effects On Global Warming For Making Green EnvironmentDokument4 SeitenA Review On Refrigerants, and Effects On Global Warming For Making Green EnvironmentInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Application of Xylanase Produced by Bacillus Megaterium in Saccharification, Juice Clarification and Oil Extraction From Jatropha Seed KernelDokument8 SeitenApplication of Xylanase Produced by Bacillus Megaterium in Saccharification, Juice Clarification and Oil Extraction From Jatropha Seed KernelInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Comparative Effect of Daily Administration of Allium Sativum and Allium Cepa Extracts On Alloxan Induced Diabetic RatsDokument6 SeitenComparative Effect of Daily Administration of Allium Sativum and Allium Cepa Extracts On Alloxan Induced Diabetic RatsInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Core Components of The Metabolic Syndrome in Nonalcohlic Fatty Liver DiseaseDokument5 SeitenCore Components of The Metabolic Syndrome in Nonalcohlic Fatty Liver DiseaseInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Auxin Induced Germination and Plantlet Regeneration Via Rhizome Section Culture in Spiranthes Sinensis (Pers.) Ames: A Vulnerable Medicinal Orchid of Kashmir HimalayaDokument4 SeitenAuxin Induced Germination and Plantlet Regeneration Via Rhizome Section Culture in Spiranthes Sinensis (Pers.) Ames: A Vulnerable Medicinal Orchid of Kashmir HimalayaInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Research Analysis On Sustainability Opportunities and Challenges of Bio-Fuels Industry in IndiaDokument7 SeitenResearch Analysis On Sustainability Opportunities and Challenges of Bio-Fuels Industry in IndiaInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- Parametric Optimization of Single Cylinder Diesel Engine For Specific Fuel Consumption Using Palm Seed Oil As A BlendDokument6 SeitenParametric Optimization of Single Cylinder Diesel Engine For Specific Fuel Consumption Using Palm Seed Oil As A BlendInternational Organization of Scientific Research (IOSR)Noch keine Bewertungen

- jvc_kd-av7000_kd-av7001_kd-av7005_kd-av7008_kv-mav7001_kv-mav7002-ma101-Dokument159 Seitenjvc_kd-av7000_kd-av7001_kd-av7005_kd-av7008_kv-mav7001_kv-mav7002-ma101-strelectronicsNoch keine Bewertungen

- Concepts of Human Development and Poverty: A Multidimensional PerspectiveDokument3 SeitenConcepts of Human Development and Poverty: A Multidimensional PerspectiveTasneem Raihan100% (1)

- REMEDIOS NUGUID vs. FELIX NUGUIDDokument1 SeiteREMEDIOS NUGUID vs. FELIX NUGUIDDanyNoch keine Bewertungen

- Final DSL Under Wire - FinalDokument44 SeitenFinal DSL Under Wire - Finalelect trsNoch keine Bewertungen

- Gambaran Kebersihan Mulut Dan Karies Gigi Pada Vegetarian Lacto-Ovo Di Jurusan Keperawatan Universitas Klabat AirmadidiDokument6 SeitenGambaran Kebersihan Mulut Dan Karies Gigi Pada Vegetarian Lacto-Ovo Di Jurusan Keperawatan Universitas Klabat AirmadidiPRADNJA SURYA PARAMITHANoch keine Bewertungen

- CV Finance GraduateDokument3 SeitenCV Finance GraduateKhalid SalimNoch keine Bewertungen

- Social Responsibility and Ethics in Marketing: Anupreet Kaur MokhaDokument7 SeitenSocial Responsibility and Ethics in Marketing: Anupreet Kaur MokhaVlog With BongNoch keine Bewertungen

- Verbos Regulares e IrregularesDokument8 SeitenVerbos Regulares e IrregularesJerson DiazNoch keine Bewertungen

- Karnataka PUC Board (KSEEB) Chemistry Class 12 Question Paper 2017Dokument14 SeitenKarnataka PUC Board (KSEEB) Chemistry Class 12 Question Paper 2017lohith. sNoch keine Bewertungen

- 2-Library - IJLSR - Information - SumanDokument10 Seiten2-Library - IJLSR - Information - SumanTJPRC PublicationsNoch keine Bewertungen

- Helical Antennas: Circularly Polarized, High Gain and Simple to FabricateDokument17 SeitenHelical Antennas: Circularly Polarized, High Gain and Simple to FabricatePrasanth KumarNoch keine Bewertungen

- 2nd YearDokument5 Seiten2nd YearAnbalagan GNoch keine Bewertungen

- Haryana Renewable Energy Building Beats Heat with Courtyard DesignDokument18 SeitenHaryana Renewable Energy Building Beats Heat with Courtyard DesignAnime SketcherNoch keine Bewertungen

- Barnett Elizabeth 2011Dokument128 SeitenBarnett Elizabeth 2011Liz BarnettNoch keine Bewertungen

- History Project Reforms of Lord William Bentinck: Submitted By: Under The Guidelines ofDokument22 SeitenHistory Project Reforms of Lord William Bentinck: Submitted By: Under The Guidelines ofshavyNoch keine Bewertungen

- Simple Future Vs Future Continuous Vs Future PerfectDokument6 SeitenSimple Future Vs Future Continuous Vs Future PerfectJocelynNoch keine Bewertungen

- I apologize, upon further reflection I do not feel comfortable advising how to harm others or violate lawsDokument34 SeitenI apologize, upon further reflection I do not feel comfortable advising how to harm others or violate lawsFranciscoJoséGarcíaPeñalvoNoch keine Bewertungen

- 02 Activity 1 (4) (STRA)Dokument2 Seiten02 Activity 1 (4) (STRA)Kathy RamosNoch keine Bewertungen

- Dr. Xavier - MIDokument6 SeitenDr. Xavier - MIKannamundayil BakesNoch keine Bewertungen

- Pembaruan Hukum Melalui Lembaga PraperadilanDokument20 SeitenPembaruan Hukum Melalui Lembaga PraperadilanBebekliarNoch keine Bewertungen

- Kenneth L. Campbell - The History of Britain and IrelandDokument505 SeitenKenneth L. Campbell - The History of Britain and IrelandKseniaNoch keine Bewertungen

- MCI FMGE Previous Year Solved Question Paper 2003Dokument0 SeitenMCI FMGE Previous Year Solved Question Paper 2003Sharat Chandra100% (1)

- Decision Support System for Online ScholarshipDokument3 SeitenDecision Support System for Online ScholarshipRONALD RIVERANoch keine Bewertungen

- NetZoom Pro v15 Install GuideDokument81 SeitenNetZoom Pro v15 Install Guidescribd!!Noch keine Bewertungen

- Critiquing a Short Story About an Aged MotherDokument2 SeitenCritiquing a Short Story About an Aged MotherJohn Rey PacubasNoch keine Bewertungen

- Written Test Unit 7 & 8 - Set ADokument4 SeitenWritten Test Unit 7 & 8 - Set ALaura FarinaNoch keine Bewertungen