Beruflich Dokumente

Kultur Dokumente

Adc

Hochgeladen von

Alexander VargasOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Adc

Hochgeladen von

Alexander VargasCopyright:

Verfügbare Formate

Design

&

Implementation of

Low Power 3-bit

Flash

ADC

in

0.18m CMOS

ADC.Flash analog-to-digital converters, also

known as

parallel ADCs, are the fastest way to convert an

analog signal

to a digital signal. Flash ADCs are ideal for

applications

requiring very large bandwidth; however, they

typically

consume more power than other ADC

architectures and are

generally limited to 8-bits resolution.

Pradeep Kumar, Amit Kolhe

AbstractThis paper describes the design and

implementation

of a Low Power 3-bit flash Analog to Digital

converter (ADC). It

includes 7 comparators and one thermometer to

binary encoder.

It is implemented in 0.18um CMOS Technology.

The

pre-simulation of ADC is done in T-Spice and post

layout

simulation is done in Microwind3.1. The response

time of the

comparator equal to 6.82ns and for Flash ADC as

18.77ns.The

Simulated result shows the power consumption in

Flash ADC as

is 36.273mw .The chip area is for Flash ADC is

1044um2 .

II. ARCHITECTURE

Fig.2. shows a typical flash ADC block

diagram. For an

"N" bit converter, the circuit employs 2N-1

comparators. A

resistive divider with 2N resistors provides the

reference

voltage. The reference voltage for each

comparator is one

least significant bit (LSB) greater than the

reference voltage

for the comparator immediately below it. Each

comparator

produces a "1" when its analog input voltage is

higher than the

reference voltage applied to it. Otherwise, the

comparator in

Fig.3.output is "0". Comparatator design

specification is

shown in Table I. As shown in Fig. 2, the flash

ADC is

composed of three major components: resistors

string,

Index Terms CMOS, Comparator , Flash ADC,

T-Spice

I. INTRODUCTION

Applications such as wireless communications

and digital

audio and video have created need for costeffective data

converters that will achieve higher speed and

resolution. The

needs required by digital signal processors [1]

continually

challenge analog designers to improve and

develop new ADC

and DAC architectures. There are many

different types of

architectures, each with unique characteristics

and different

limitations[2]. Figure.1. shows the general block

diagram of

Fig. 1. Block for 3-Bit Flash ADC

comparators and encoder. The analog input

voltage is

concurrently compared to the reference voltage

levels

generated from resistors string and the speed of

A/D

conversion is therefore maximized. The outputs

of

comparators form a thermometer code (TC)

which is a

combination of a series of zeros and a series of

ones, e.g.,

000011111. Because binary code is

usually needed for

digital signal processing, a thermometer code is

then

transformed to a binary code through a (2k-1)to-k TC-to-BC

encoder, where k is the resolution (bits) of

ADCs. The cost of

such

a

traditional

encoder

increases

exponentially with the

resolution. Optimizations on area cost, circuit

latencies an

power consumptions are greatly expected. In

this paper we

have low power Comparator used in the design

throughout.

Fig. 2. Circuit for a 3 Bit Flash ADC

V. CONCLUSIONS AND FUTUREWORKS

In this paper, a 3 Bit flash ADC architecture

with low

hardware complexity and low latency is

proposed.This 3bit

flash type Analog to digital converter have

limitations such as

this device is accurate for the conversion of

analog voltage to

digital form from 0 to 3 voltage in amplitude

and for accurate

result the input voltage should be greater or

lesser than the

reference voltage of the comparator about

0.05 volt.

Moreover, this architecture can be extended to

medium-to-high resolution applications because

this

simplicity of the circuit.

Das könnte Ihnen auch gefallen

- Flash ADCDokument3 SeitenFlash ADCKiran SomayajiNoch keine Bewertungen

- B10410782S219Dokument4 SeitenB10410782S219mayurpoojary1703Noch keine Bewertungen

- Design Implementation and Analysis of Flash Adc Architecture WitDokument7 SeitenDesign Implementation and Analysis of Flash Adc Architecture WitsayemeeceNoch keine Bewertungen

- 12EC62R20 Ramesh SynopsisDokument9 Seiten12EC62R20 Ramesh Synopsisprasad72207Noch keine Bewertungen

- IET Circuits Devices Syst - 2018 - Gupta - Highly Digital Voltage Scalable 4 Bit Flash ADCDokument7 SeitenIET Circuits Devices Syst - 2018 - Gupta - Highly Digital Voltage Scalable 4 Bit Flash ADCmayurpoojary1703Noch keine Bewertungen

- Design and Simulation of 4-Bit Flash Analog To Digital Converter (ADC) For High Speed ApplicationsDokument7 SeitenDesign and Simulation of 4-Bit Flash Analog To Digital Converter (ADC) For High Speed ApplicationsAlisha KshetriNoch keine Bewertungen

- FTADCDokument6 SeitenFTADCsaravanany5kNoch keine Bewertungen

- P109 113 PDFDokument5 SeitenP109 113 PDFSuraj Kumar PrustyNoch keine Bewertungen

- Analog To Digital (ADC) and Digital To Analog (DAC) ConvertersDokument12 SeitenAnalog To Digital (ADC) and Digital To Analog (DAC) ConvertersIoana IoanaNoch keine Bewertungen

- REPORTFINALDokument21 SeitenREPORTFINALReal HumanityNoch keine Bewertungen

- A Review: High Speed Low Power Flash ADC: Rahul D. Marotkar, Dr. Manoj S. NagmodeDokument4 SeitenA Review: High Speed Low Power Flash ADC: Rahul D. Marotkar, Dr. Manoj S. NagmodeSunil PandeyNoch keine Bewertungen

- Review On Different Types of Binary Code PDFDokument3 SeitenReview On Different Types of Binary Code PDFSento IsuzuNoch keine Bewertungen

- A 10-Bit 5 Msample/s ADC: Two-Step FlashDokument9 SeitenA 10-Bit 5 Msample/s ADC: Two-Step FlashRaghav ChaudharyNoch keine Bewertungen

- Low-Power Heterogeneous Encoder Based 4-Bit Flash ADC Using TIQ-1893Dokument8 SeitenLow-Power Heterogeneous Encoder Based 4-Bit Flash ADC Using TIQ-1893mayurpoojary1703Noch keine Bewertungen

- Electronics: A Low-Power Column-Parallel Gain-Adaptive Single-Slope ADC For CMOS Image SensorsDokument21 SeitenElectronics: A Low-Power Column-Parallel Gain-Adaptive Single-Slope ADC For CMOS Image SensorsShehab BahaaNoch keine Bewertungen

- Design of 16 Bit 180nm CMOS Fully Segmented DACDokument3 SeitenDesign of 16 Bit 180nm CMOS Fully Segmented DACInternational Journal of Application or Innovation in Engineering & ManagementNoch keine Bewertungen

- PXC 3884802Dokument5 SeitenPXC 3884802Nhi NguyễnNoch keine Bewertungen

- Precise Kilometer Calculation by Underground Cable Fault DetectorDokument27 SeitenPrecise Kilometer Calculation by Underground Cable Fault DetectorAbhinavNoch keine Bewertungen

- Thesis On Flash AdcDokument7 SeitenThesis On Flash Adcafbtnbmuw100% (1)

- Design of A New 3 Bit Flash Analog To DiDokument11 SeitenDesign of A New 3 Bit Flash Analog To DisayemeeceNoch keine Bewertungen

- D A A C: Igitally Ssisted Nalog IrcuitsDokument10 SeitenD A A C: Igitally Ssisted Nalog Ircuitsjofinjv3194Noch keine Bewertungen

- DLC Lab - 10Dokument7 SeitenDLC Lab - 10Didarul Alam AlifNoch keine Bewertungen

- Bits AbstractDokument1 SeiteBits AbstractSrinath SanthanamNoch keine Bewertungen

- AN12217 - S32K1xx ADC Guidelines, Spec andDokument26 SeitenAN12217 - S32K1xx ADC Guidelines, Spec andNguyễn Mỹ KiênNoch keine Bewertungen

- Camera Ready Reconfigurable ADCDokument20 SeitenCamera Ready Reconfigurable ADCjayamala adsulNoch keine Bewertungen

- Cadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyDokument6 SeitenCadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyUtsavNoch keine Bewertungen

- How Do Adcs Work?: Back PrintDokument5 SeitenHow Do Adcs Work?: Back Printmilostar6Noch keine Bewertungen

- A Novel and Systematic Implementation of Thermometer-Coded Current-Mode DACDokument4 SeitenA Novel and Systematic Implementation of Thermometer-Coded Current-Mode DACRodrigo SantosNoch keine Bewertungen

- An Analysis and Design of High Performance Power Consumption Double Tail Comparator Using Gated Clock and Power Gating TechniquesDokument7 SeitenAn Analysis and Design of High Performance Power Consumption Double Tail Comparator Using Gated Clock and Power Gating TechniquesIJIRSTNoch keine Bewertungen

- Design and Implementation of A 10 Bit SAR ADCDokument4 SeitenDesign and Implementation of A 10 Bit SAR ADCVipul ChauhanNoch keine Bewertungen

- Dada Acquisition HRISDokument4 SeitenDada Acquisition HRISDiponkerSahaNoch keine Bewertungen

- Design and Simulation of 1-Bit Sigma-Delta ADC Using Ngspice ToolDokument5 SeitenDesign and Simulation of 1-Bit Sigma-Delta ADC Using Ngspice ToolIjarcsee JournalNoch keine Bewertungen

- 09 Chapter1Dokument20 Seiten09 Chapter1SriramNoch keine Bewertungen

- Analog To Digital Converter - Block Diagram, Types Its ApplicationsDokument10 SeitenAnalog To Digital Converter - Block Diagram, Types Its ApplicationsNikka Hernandez FloresNoch keine Bewertungen

- A 8-Bit Hybrid Architecture Current-Steering DAC: International Research Journal of Engineering and Technology (IRJET)Dokument5 SeitenA 8-Bit Hybrid Architecture Current-Steering DAC: International Research Journal of Engineering and Technology (IRJET)upendra450Noch keine Bewertungen

- A 1-V 1-GSs 6-Bit Low-Power Flash ADC in 90nm CMOSDokument4 SeitenA 1-V 1-GSs 6-Bit Low-Power Flash ADC in 90nm CMOSThanos van RamNoch keine Bewertungen

- Design of Low Power 4-Bit Flash ADC Based On Standard Cells: Marcel Siadjine Njinowa, Hung Tien Bui François-Raymond BoyerDokument4 SeitenDesign of Low Power 4-Bit Flash ADC Based On Standard Cells: Marcel Siadjine Njinowa, Hung Tien Bui François-Raymond BoyerSunil PandeyNoch keine Bewertungen

- Modeling of Sigma Delta Modulator Non Idealities With Two Step Quantization in MATLAB SIMULINK PDFDokument6 SeitenModeling of Sigma Delta Modulator Non Idealities With Two Step Quantization in MATLAB SIMULINK PDFeditor_ijcatNoch keine Bewertungen

- 0710ijcnc04 PDFDokument10 Seiten0710ijcnc04 PDFJam 234Noch keine Bewertungen

- Icaet2017073 PDFDokument5 SeitenIcaet2017073 PDFKaushik YadiyalNoch keine Bewertungen

- A Low Power A - D Converter 05613669Dokument4 SeitenA Low Power A - D Converter 05613669Romualdo Begale PrudêncioNoch keine Bewertungen

- Optimizing The Number of Bits/Stage in 10-Bit, 50Ms/Sec Pipelined A/D Converter Considering Area, Speed, Power and LinearityDokument7 SeitenOptimizing The Number of Bits/Stage in 10-Bit, 50Ms/Sec Pipelined A/D Converter Considering Area, Speed, Power and LinearityronaldomponteNoch keine Bewertungen

- DP - 26 DocumentationDokument64 SeitenDP - 26 DocumentationViplav SangvaiNoch keine Bewertungen

- Flash ADC Design in ElectricDokument22 SeitenFlash ADC Design in ElectricNagaraj HegdeNoch keine Bewertungen

- Title: Design of A Flash Analog To Digital ConverterDokument4 SeitenTitle: Design of A Flash Analog To Digital Converteranon_776365175Noch keine Bewertungen

- A 1-GS/s CMOS 6-Bit Flash ADC With An Offset Calibrating MethodDokument4 SeitenA 1-GS/s CMOS 6-Bit Flash ADC With An Offset Calibrating MethodSunil PandeyNoch keine Bewertungen

- Design of Comparator and Comparative Study of Encoders in A 4-Bit Flash ADC Using VerilogDokument3 SeitenDesign of Comparator and Comparative Study of Encoders in A 4-Bit Flash ADC Using VerilogjestinmaryNoch keine Bewertungen

- Low Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron TechnologyDokument5 SeitenLow Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron Technologyeditor_ijtel100% (1)

- Pipelined AdcDokument26 SeitenPipelined AdcKausar Fathima100% (1)

- Dual Slope ADC DesignDokument10 SeitenDual Slope ADC DesignMoHaMMeD HaLaByNoch keine Bewertungen

- Project ReportDokument34 SeitenProject Reportkeerti hattiNoch keine Bewertungen

- Digital Techniques/Electronic Instrument Systems: Basic Training CenterDokument21 SeitenDigital Techniques/Electronic Instrument Systems: Basic Training Centermevlüt said çalgınNoch keine Bewertungen

- Lab 10Dokument6 SeitenLab 10Nouroj AminNoch keine Bewertungen

- Dec Exp 6 Student ManualDokument5 SeitenDec Exp 6 Student ManualSakib MahmudNoch keine Bewertungen

- ADC TrendsDokument8 SeitenADC TrendsscribeFzNoch keine Bewertungen

- Adc 0808Dokument6 SeitenAdc 0808src e-solutionsNoch keine Bewertungen

- Simulink Behavioral Modeling of A 10-Bit Pipelined ADCDokument9 SeitenSimulink Behavioral Modeling of A 10-Bit Pipelined ADCbhasin_hemantNoch keine Bewertungen

- Flash Adc PHD ThesisDokument8 SeitenFlash Adc PHD Thesisanniehansonmadison100% (2)

- MyLabGamma 160000024MAK V06 0518 HRDokument8 SeitenMyLabGamma 160000024MAK V06 0518 HRAlexander VargasNoch keine Bewertungen

- MyLabAlpha eHD CL 160000013MAK4 0518 HR PDFDokument12 SeitenMyLabAlpha eHD CL 160000013MAK4 0518 HR PDFAlexander VargasNoch keine Bewertungen

- MyLabGamma 160000024MAK V06 0518 HRDokument8 SeitenMyLabGamma 160000024MAK V06 0518 HRAlexander VargasNoch keine Bewertungen

- Brochure Mylab SigmaDokument2 SeitenBrochure Mylab SigmaAlexander VargasNoch keine Bewertungen

- RAMPS 1 4manualDokument3 SeitenRAMPS 1 4manualgustavo3148146Noch keine Bewertungen

- Brochure Mylab OmegaDokument4 SeitenBrochure Mylab OmegaAlexander VargasNoch keine Bewertungen

- Description: Quick Start Guide For Demonstration Circuit Dc512B LTC4100Dokument6 SeitenDescription: Quick Start Guide For Demonstration Circuit Dc512B LTC4100Alexander VargasNoch keine Bewertungen

- 17HS4401 MotionKing PDFDokument1 Seite17HS4401 MotionKing PDFAlberto Aduvire RafaelNoch keine Bewertungen

- A4988 Datasheet PDFDokument20 SeitenA4988 Datasheet PDFJulio Cesar Romano100% (1)

- Description Features: Ltc4100 Smart Battery Charger ControllerDokument30 SeitenDescription Features: Ltc4100 Smart Battery Charger ControllerAlexander VargasNoch keine Bewertungen

- MyLabOmega 160000164MA Ver.03maskDokument12 SeitenMyLabOmega 160000164MA Ver.03maskAlexander VargasNoch keine Bewertungen

- The Meaning of EntropyDokument29 SeitenThe Meaning of EntropyAlexander VargasNoch keine Bewertungen

- 17HS4401 MotionKing PDFDokument1 Seite17HS4401 MotionKing PDFAlberto Aduvire RafaelNoch keine Bewertungen

- Infet Dcin VDD: Technology Technology TechnologyDokument1 SeiteInfet Dcin VDD: Technology Technology TechnologyAlexander VargasNoch keine Bewertungen

- Chap05 (7 5 06)Dokument60 SeitenChap05 (7 5 06)Amar NathNoch keine Bewertungen

- 17HS4401 MotionKing PDFDokument1 Seite17HS4401 MotionKing PDFAlberto Aduvire RafaelNoch keine Bewertungen

- Samsung PL42C91HPDokument89 SeitenSamsung PL42C91HPAlexander Vargas50% (2)

- Chapter 8 PDFDokument93 SeitenChapter 8 PDF김민성Noch keine Bewertungen

- FRA5310 TechDokument2 SeitenFRA5310 TechBash MatNoch keine Bewertungen

- Crow Proximity Reader ManualDokument8 SeitenCrow Proximity Reader ManualMichael GiannakNoch keine Bewertungen

- 9365Dokument69 Seiten9365Kivanc NEROGLUNoch keine Bewertungen

- 3.re Situation in Suez Canal - M.V EVER GIVEN SUCCESSFULLY REFLOATEDDokument9 Seiten3.re Situation in Suez Canal - M.V EVER GIVEN SUCCESSFULLY REFLOATEDaungyinmoeNoch keine Bewertungen

- Iso 5294 1989Dokument9 SeitenIso 5294 1989a.mursadinNoch keine Bewertungen

- 33003788K01000 PDFDokument472 Seiten33003788K01000 PDFAji SukumaNoch keine Bewertungen

- Chapter 1 Vapor Power Cycles - CompleteDokument97 SeitenChapter 1 Vapor Power Cycles - CompleteAdnan NimachwalaNoch keine Bewertungen

- Control Lab ReportDokument11 SeitenControl Lab ReportMariamMunirAhmad100% (1)

- MTK 1023-Material and ConsumableDokument13 SeitenMTK 1023-Material and ConsumableGraceLamNoch keine Bewertungen

- Orca Share Media1541759628568 PDFDokument12 SeitenOrca Share Media1541759628568 PDFJuneNeilBalacuitNoch keine Bewertungen

- ITC Guide For Thesis PreparationDokument26 SeitenITC Guide For Thesis PreparationPanha MenhNoch keine Bewertungen

- CH 16Dokument20 SeitenCH 16Engr. Talha Riaz PersotaNoch keine Bewertungen

- (52621001078) DM - DM Half Inch Flex Jumper Spec SheetDokument2 Seiten(52621001078) DM - DM Half Inch Flex Jumper Spec SheetmicroqualNoch keine Bewertungen

- Basics of CT and PTDokument15 SeitenBasics of CT and PTanamika1690% (1)

- DataDokument194 SeitenDataddlaluNoch keine Bewertungen

- 5e17f Toshiba Satellite l40 Compal La9862p Compal La9862p r10 Laptop SchematicsDokument46 Seiten5e17f Toshiba Satellite l40 Compal La9862p Compal La9862p r10 Laptop Schematicsamier jrs100% (1)

- Technical Delivery Condition of S500MCDokument4 SeitenTechnical Delivery Condition of S500MCdcevipin100% (1)

- Rashid Ch10 ImagesDokument47 SeitenRashid Ch10 ImagesAtiq Ur RehmanNoch keine Bewertungen

- Base Plate and Anchor Rod DesignDokument2 SeitenBase Plate and Anchor Rod DesignKannan MurugesanNoch keine Bewertungen

- Spare Parts List: Riders R214 TC, 967325902, 2017-01Dokument49 SeitenSpare Parts List: Riders R214 TC, 967325902, 2017-01aliuta aliutaNoch keine Bewertungen

- Power Tool Switches: Catalog 1308650 Issued 1-01Dokument18 SeitenPower Tool Switches: Catalog 1308650 Issued 1-01Gamal AhmadNoch keine Bewertungen

- Tabl Navegacion Aqua SignalDokument4 SeitenTabl Navegacion Aqua SignalNelson Aguirre BravoNoch keine Bewertungen

- Asteion MultiDokument59 SeitenAsteion MultiIng. Arturo PreciadoNoch keine Bewertungen

- Technical Reference Options and Adapters Volume 1 Apr84Dokument501 SeitenTechnical Reference Options and Adapters Volume 1 Apr84kgrhoadsNoch keine Bewertungen

- E2186 Certif Conformidad - TomasDokument6 SeitenE2186 Certif Conformidad - TomasFRANCISCONoch keine Bewertungen

- Delphi Informant Magazine Issue 3 Volume 6 2000Dokument36 SeitenDelphi Informant Magazine Issue 3 Volume 6 2000Raimo JankaNoch keine Bewertungen

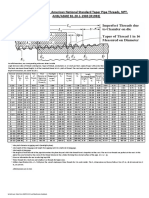

- NPT Thread Dimensions PDFDokument1 SeiteNPT Thread Dimensions PDFRamnandan MahtoNoch keine Bewertungen

- Til 1213 R1Dokument6 SeitenTil 1213 R1Hernan GirautNoch keine Bewertungen

- Unlock Any Roku Device: Watch Shows, TV, & Download AppsVon EverandUnlock Any Roku Device: Watch Shows, TV, & Download AppsNoch keine Bewertungen

- Chip War: The Quest to Dominate the World's Most Critical TechnologyVon EverandChip War: The Quest to Dominate the World's Most Critical TechnologyBewertung: 4.5 von 5 Sternen4.5/5 (227)

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Von EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Bewertung: 5 von 5 Sternen5/5 (1)

- Computer Science: A Concise IntroductionVon EverandComputer Science: A Concise IntroductionBewertung: 4.5 von 5 Sternen4.5/5 (14)

- Chip War: The Fight for the World's Most Critical TechnologyVon EverandChip War: The Fight for the World's Most Critical TechnologyBewertung: 4.5 von 5 Sternen4.5/5 (82)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XVon EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XBewertung: 3 von 5 Sternen3/5 (2)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Von EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Bewertung: 5 von 5 Sternen5/5 (2)

- CompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Von EverandCompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Noch keine Bewertungen

- Amazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesVon EverandAmazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesNoch keine Bewertungen

- Amazon Web Services (AWS) Interview Questions and AnswersVon EverandAmazon Web Services (AWS) Interview Questions and AnswersBewertung: 4.5 von 5 Sternen4.5/5 (3)

- Mastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFVon EverandMastering IoT For Industrial Environments: Unlock the IoT Landscape for Industrial Environments with Industry 4.0, Covering Architecture, Protocols like MQTT, and Advancements with ESP-IDFNoch keine Bewertungen

- Programming with STM32: Getting Started with the Nucleo Board and C/C++Von EverandProgramming with STM32: Getting Started with the Nucleo Board and C/C++Bewertung: 3.5 von 5 Sternen3.5/5 (3)

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxVon EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxNoch keine Bewertungen

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertVon EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertBewertung: 3.5 von 5 Sternen3.5/5 (6)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsVon EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsBewertung: 5 von 5 Sternen5/5 (2)

- Raspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesVon EverandRaspberry Pi Retro Gaming: Build Consoles and Arcade Cabinets to Play Your Favorite Classic GamesNoch keine Bewertungen

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideVon EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideBewertung: 1 von 5 Sternen1/5 (1)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Von EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Bewertung: 5 von 5 Sternen5/5 (1)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Von EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Bewertung: 5 von 5 Sternen5/5 (2)

- Real-Time UML Workshop for Embedded SystemsVon EverandReal-Time UML Workshop for Embedded SystemsBewertung: 3.5 von 5 Sternen3.5/5 (2)

- Raspberry Pi for Python Programmers Cookbook - Second EditionVon EverandRaspberry Pi for Python Programmers Cookbook - Second EditionNoch keine Bewertungen

- How To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsVon EverandHow To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsNoch keine Bewertungen

- Essential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XVon EverandEssential iPhone X iOS 12 Edition: The Illustrated Guide to Using iPhone XBewertung: 5 von 5 Sternen5/5 (1)

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714829744?v=1)