Beruflich Dokumente

Kultur Dokumente

Idt TN-08 Apn 20060731

Hochgeladen von

santoshkrishna12Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Idt TN-08 Apn 20060731

Hochgeladen von

santoshkrishna12Copyright:

Verfügbare Formate

Operating FIFOs On Full and

Empty Boundary Conditions

TECHNICAL NOTE

TN-08

by Suneel Rajpal and Frank Schapfel

be scrambled or may be garbage. The Empty Flag and Full Flag counters may

also be upset by the internal glitch, which upsets FIFO memory usage. The

only way to recover from this violation is to do a master reset.

A similar situation arises at the full FIFO boundary condition. When the FIFO

is one word from being full, the falling edge of W causes the FF to be asserted.

After the write cycle is completed ( W goes HIGH again), FF will remain asserted

and the internal write counter is not affected by subsequent write cycles. The

FF flag is deasserted by the next rising edge of R , as shown in Figure 3, after

which another write pulse can be applied to do a write operation.

When the FIFO is full and W is being clocked, data sent to the FIFO will be

ignored and the write pointer will not incre-ment. Here, as in the earlier case,

if these write cycles are asynchronous during a read operation, a possible

violation of the write pulse width minimum can occur, as shown in Figure 4. Here,

FF is deasserted but a sufficient write pulse minimum width is not met. To prevent

the problem, initiate a write operation only after FF is HIGH, or guarantee a long

enough write pulse width minimum time. A violation of the timing causes an

internal glitch on the FIFO write line. This can cause the write pointers to be out

of sync where the data inside the FIFO may be scrambled or may be garbage.

The Empty Flag and Full Flag counters may also be upset by the internal glitch.

Again, the only way to recover from this condition is to do a master reset.

In summary, these FIFOs are designed to transfer only valid data from input

to output. To ensure that valid data is written into and read from, empty and full

FIFOs handshake through the flag mechanism. When there is no output data

available, the reading side must wait until the end of a write. In a full FIFO, the

writing side must wait for the reading side to create an empty location.

Incomplete read and write cycles can not only invalidate data, but can cause

the pointers to be out of synchronization, requiring a master reset to renew data

transfer.

The IDT7201, IDT7202, IDT7203 and IDT7204 (512 x 9, 1,024 x 9, 2,048

x 9 and 4,096 x 9) FIFOs have only four control lines: Read, Write, Reset and

Retransmit. The focus of this tech note is the relation of the Read ( R ) and Write

( W ) lines to the FIFOs empty and full conditions.

These high-speed FIFOs can perform asynchronous and simultaneous

read and write operations. R and W assert and deassert the Empty Flag

( EF ) and Full Flag ( FF ).Therefore, special conditions exist when a full FIFO

continues to be written to and a read operation takes place. Also, special timings

occur when an empty FIFO continues to be read to and a write operation takes

place. These operations are called the FIFO boundary conditions.

Read and Write increment the read and write pointers on their respective

rising clock edges.The read and write pointers affect the Empty Flag and Full

Flag counters.The Empty Flag timings are shown in Figure 1. When the FIFO

has only one word in it, the falling edge of R causes EF to be asserted. After

the clock cycle is completed ( R goes HIGH again), EF will remain asserted

and the internal read counter is not affected by subsequent read cycles. EF is

deasserted by the next rising edge of W , after which another read pulse can

be applied to do a read operation. In asynchronous systems, read and write

operations take place at any time; EF is set by one signal and deasserted by

another asynchronous signal.

When R is being clocked on an empty FIFO, the outputs will be in highimpedance. If a write operation is performed during asynchronous read cycles,

a possible violation of the read pulse width minimum can occur, as shown in

Figure 2. EF is deasserted, but there is an insufficient read pulse minimum width.

To prevent the minimum read pulse width violation, initiate a read operation only

after EF is HIGH, or guarantee a long enough read pulse width minimum time.

A violation of the timing causes an internal glitch on the FIFO Read which can

cause the read pointer to be out of sync. Then the data inside the FIFO may

This read pulse is ignored by the FIFO

t REF

t WEF

EF

Figure 1. Empty Flag from Last Read to First Write

The IDT logo is a trademark of Integrated Device Technology, Inc.

FAST is a trademark of Fairchild Semiconductor Co.

MARCH 1999

1

1999

Integrated Device Technology, Inc.

DSC-4307/1

IDT Technical Note TN-08

This read pulse is ignored by the FIFO

W

EF

External

to FIFO

t1

R

INTERNAL READ(1)

EF

R (Internal

)

EF (Internal)

NOTES:

1. Pulse within the FIFO used to clock the write pointer and the Empty and Full Flag counters.

2. If t1 < tRPW (minimum read pulse width low), then the read pointer, Empty Flag and Full Flag counters may be out of sync. See Figure 15 of IDT7201/7202LA

data sheet.

Figure 2. Violation of tRPW During Boundary Conditions

This write pulse is ignored by the FIFO

t WFF

t RFF

FF

Figure 3. Full Flag from Last Write to First Read

This write pulse is ignored by the FIFO

R

FF

t1

W

W (Internal)

INTERNAL WRITE (1)

FF

FF (Internal)

External

to FIFO

NOTES:

1. Pulse within the FIFO used to clock the read pointer and the Empty and Full Flag counters.

2. If t1 < tWPW (minimum write pulse width low), then the write pointer, Empty Flag and Full Flag counters may be out of sync. See Figure 16 of IDT7201/7202LA data sheet.

Figure 4. Violation of tWPW During Boundary Conditions

CORPORATE HEADQUARTERS

6024 Silver Creek Valley Road

San Jose, CA 95138

for SALES:

800-345-7015 or 408-284-8200

fax: 408-284-2775

www.idt.com

3

for Tech Support:

408-360-1753

email: FIFOhelp@idt.com

Das könnte Ihnen auch gefallen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5795)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Financial Management - Risk and Return Assignment 2 - Abdullah Bin Amir - Section ADokument3 SeitenFinancial Management - Risk and Return Assignment 2 - Abdullah Bin Amir - Section AAbdullah AmirNoch keine Bewertungen

- Reading Activity - A Lost DogDokument3 SeitenReading Activity - A Lost DogGigsFloripaNoch keine Bewertungen

- Skills For Developing Yourself As A LeaderDokument26 SeitenSkills For Developing Yourself As A LeaderhIgh QuaLIty SVTNoch keine Bewertungen

- Heat Transfer OperationsDokument10 SeitenHeat Transfer OperationsShafique AhmedNoch keine Bewertungen

- Audio Scripts B1 Student'S Book: CD 4 Track 38Dokument2 SeitenAudio Scripts B1 Student'S Book: CD 4 Track 38Priscila De La Rosa0% (1)

- Movie Review TemplateDokument9 SeitenMovie Review Templatehimanshu shuklaNoch keine Bewertungen

- Credit Transactions Case Digestpdf PDFDokument241 SeitenCredit Transactions Case Digestpdf PDFLexa L. DotyalNoch keine Bewertungen

- The Utopia of The Zero-OptionDokument25 SeitenThe Utopia of The Zero-Optiontamarapro50% (2)

- DaybreaksDokument14 SeitenDaybreaksKYLE FRANCIS EVANoch keine Bewertungen

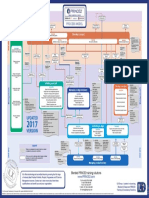

- p2 Process Model 2017Dokument1 Seitep2 Process Model 2017Miguel Fernandes0% (1)

- Macguffin: History and UseDokument5 SeitenMacguffin: History and UseGeraldo CostaNoch keine Bewertungen

- IndexDokument3 SeitenIndexBrunaJ.MellerNoch keine Bewertungen

- Sanjay Seth - Once Was Blind But Now Can See Modernity and The Social SciencesDokument16 SeitenSanjay Seth - Once Was Blind But Now Can See Modernity and The Social SciencesQuelen GuedesNoch keine Bewertungen

- Concept Paper For Business ResearchDokument4 SeitenConcept Paper For Business ResearchRobertchristian RagaNoch keine Bewertungen

- Delta Robot KinematicsDokument11 SeitenDelta Robot KinematicssekinNoch keine Bewertungen

- (154 Marks) : (1 Mark)Dokument40 Seiten(154 Marks) : (1 Mark)Manav NairNoch keine Bewertungen

- Lecture - 4 - 28june2023Dokument18 SeitenLecture - 4 - 28june2023vanshikaNoch keine Bewertungen

- Types of CounsellingDokument5 SeitenTypes of CounsellingAnkita ShettyNoch keine Bewertungen

- DLL - English 4 - Q2 - W8Dokument4 SeitenDLL - English 4 - Q2 - W8BenjNoch keine Bewertungen

- YCAP 7 Steps PosterDokument1 SeiteYCAP 7 Steps PosterSohila AmrNoch keine Bewertungen

- Approaching Checklist Final PDFDokument15 SeitenApproaching Checklist Final PDFCohort Partnerships100% (1)

- Extreme Risk FinanceDokument322 SeitenExtreme Risk FinanceThomas Thomas100% (2)

- Redemption and The Relief Work RevisedDokument234 SeitenRedemption and The Relief Work RevisedYewo Humphrey MhangoNoch keine Bewertungen

- Kosem SultanDokument2 SeitenKosem SultanAmaliaNoch keine Bewertungen

- Learning Objectives: Understanding The Self Module 1 - Sexual SelfDokument11 SeitenLearning Objectives: Understanding The Self Module 1 - Sexual SelfMiss MegzzNoch keine Bewertungen

- Xenophanes' ScepticismDokument22 SeitenXenophanes' Scepticismvince34Noch keine Bewertungen

- Study On Perfromance Appraisal System in HPCLDokument12 SeitenStudy On Perfromance Appraisal System in HPCLomkinggNoch keine Bewertungen

- SCHEEL, Bernd - Egyptian Metalworking and ToolsDokument36 SeitenSCHEEL, Bernd - Egyptian Metalworking and ToolsSamara Dyva86% (7)

- Teacher LOA & TermsDokument3 SeitenTeacher LOA & TermsMike SchmoronoffNoch keine Bewertungen

- TARA FrameworkDokument2 SeitenTARA Frameworkdominic100% (1)