Beruflich Dokumente

Kultur Dokumente

CS M151B / EE M116C: Computer Systems Architecture

Hochgeladen von

tinhtrilacOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

CS M151B / EE M116C: Computer Systems Architecture

Hochgeladen von

tinhtrilacCopyright:

Verfügbare Formate

CS M151B / EE M116C

Computer Systems Architecture

ALU Design Part II

Instructor: Prof. Lei He

<LHE@ee.ucla.edu>

Some notes adopted from Glenn Reinman

Outline

Review of ALU and CLA

Signed multiplication and division

Break

FP representation and operation

Building blocks

a.

CarryOut

Binvert

Binvert

Operation

CarryIn

Operation

CarryIn

1

Result

1

b

Result

b

2

Less

3

Set

Less

3

Overflow

detection

CarryOut

All but MSB

b.

Most Significant Bit

Overflow

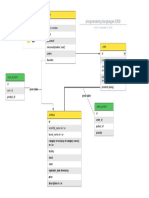

Final Full ALU

You should feel

comfortable

identifying what

signals

accomplish:

add

sub

and

or

beq

slt

Bnegate

Operation

a0

b0

CarryIn

ALU0

Less

CarryOut

Result0

a1

b1

0

CarryIn

ALU1

Less

CarryOut

Result1

a2

b2

0

CarryIn

ALU2

Less

CarryOut

Result2

a31

b31

0

CarryIn

ALU31

Less

Zero

Result31

Set

Overflow

Carry Look Ahead

c0 = Cin

A0

B0

G

P

S

c1 = g0 + c0 p0

A1

B1

G

P

A

0

0

1

1

B

0

1

0

1

C-out

0

C-in

C-in

1

kill

propagate

propagate

generate

g = A and B

p = A xor B

c2 = g1 + g0 p1 + c0 p0 p1

A2

B2

G

P

S

c3 = g2 + g1 p2 + g0 p1 p2 + c0 p0 p1 p2

A3

B3

G

P

For hierarchical CLA

G0=g3+g2p3+

P0=p3p2p1p0

c4 = . . .

Hierarchical CLA

C

L

A

4-bit

Adder

C0

G0= g3+g2p3+

P0= p3p2p1p0

C1 = G0 + C0 P0

G1= g7+g6p7+

P0= p7p6p5p4

C2 = G1 + G0 P1 + C0 P0 P1

4-bit

Adder

C3 = G2 + G1 P2 + G0 P1 P2 + C0 P0 P1 P2

G

P

4-bit

Adder

C4 = . . .

Signed Multiplication?

First, convert both to positive numbers

remember whether to complement product when

done

Then, apply definition of 2s complement

need to sign-extend partial products at the end

Booths Algorithm

elegant way to multiply signed numbers

using same hardware as before and save cycles

Motivation for Booths Algorithm

Example 2 x 6 = 0010 x 0110:

0010

x

0110

+

0000

shift (0 in multiplier)

+

0010

add (1 in multiplier)

+

0010

add (1 in multiplier)

+

0000

shift (0 in multiplier)

00001100

ALU with add or subtract gets same result in more than one way:

6

= 2 + 8

0110 = 00010 + 01000 = 11110 + 01000

For example

0010

x

0110

0000 shift (0 in multiplier)

0010 sub (first 1 in multpl.) .

0000

shift (mid string of 1s) .

+

0010

add (prior step had last 1)

00001100

Booths Algorithm

end of run

middle of run

011110

beginning of run

Current Bit Bit to the Right Explanation

Example

Op

1

0

Begins run of 1s

0001111000 sub

1

1

Middle of run of 1s 0001111000 none

0

1

End of run of 1s

0001111000 add

0

0

Middle of run of 0s 0001111000 none

Originally for Speed (when shift was faster than add)

Replace a string of 1s in multiplier with an initial subtract when we first see a

one and then later add for the bit after the last one

1

+ 10000

01111

Booths Example (2 x 7)

Operation

Multiplicand

Product

next?

0. initial value

0010

0000 0111 0

10 -> sub

1a. P = P - m

1110

+ 1110

1110 0111 0

1b.

0010

1111 0011 1

11 -> nop, shift

2.

0010

1111 1001 1

11 -> nop, shift

3.

0010

1111 1100 1

01 -> add

4a.

0010

+ 0010

0001 1100 1

4b.

0010

0000 1110 0

shift P (sign ext)

shift

done

Booths Example (2 x -3)

Operation

Multiplicand

0. initial value

1a. P = P - m

0010

1110

0000 1101 0

+ 1110

1110 1101 0

10 -> sub

1b.

0010

1111 0110 1

+ 0010

01 -> add

2a.

Product

0001 0110 1

next?

shift P (sign ext)

shift P

2b.

0010

0000 1011 0

+ 1110

10 -> sub

3a.

0010

1110 1011 0

shift

3b.

4a

0010

1111 0101 1

1111 0101 1

11 -> nop

shift

4b.

0010

1111 1010 1

done

Quick example

Division

Divisor

Assumptions:

1101 Quotient

1000 1101010 Dividend

-1000

1010

-1000

0010

0101

-0000

1010

-1000

10 Remainder

dividend, divisor, quotient, and remainder are all 32-bit

positive values

Divide Version 1

32-bit divisor starts in left half of divisor register

Remainder register is initialized with dividend

Divisor

Shift right

64 bits

Quotient

Shift left

64-bit ALU

32 bits

Remainder

Write

64 bits

Control

test

Divide Version 1

n+1 steps for n-bit operands

Book shows 7 / 2

Lets try 7 / 3 (4-bit operands)

Q

D

R

0000

0011 0000

0000 0111

0000

0011 0000

1101 0111

0000

0011 0000

0000 0111

0000

0001 1000

0000 0111

0000

0001 1000

1110 1111

0000

0001 1000

0000 0111

0000

0000 1100

0000 0111

0000

0000 1100

1111 1011

0000

0000 1100

0000 0111

0000

0000 0110

0000 0111

0000

0000 0110

0000 0001

0001

0000 0110

0000 0001

0001

0000 0011

0000 0001

0000

0000 0011

1111 1110

0010

0000 0011

0000 0001

0010

0000 0001

0000 0001

2

1

S tart

1. Subtract the Divisor register from the

Remainder register and place t he

result in the Remainder register

Remainder > 0

Test Remainder

2a. Shift the Quotient register to the left,

setting the new rightmost bit to 1

Remainder < 0

2b. Restore the original value by adding

the Divisor register to the Remainder

register and place the sum in the

Remainder register. Also shift the

Quotient register to the left, setting the

new least significant bit to 0

3. Shift the Divisor register right 1 bit

33rd repetition?

No: < 33 repetitions

Yes: 33 repet itions

Done

Divide Version 2

At most half the divisor has useful information

cut divisor and ALU in half

Divisor

32 bits

Quotient

Shift left

32-bit ALU

32 bits

Remainder

64 bits

Shift left

Write

Control

test

Divide Version 3

Start

Divisor

32 bits

1. Shift the Remainder register left 1 bit

2. Subtract the Divisor register from the

left half of the Remainder register and

place the result in the left half of the

Remainder register

32- bit ALU

Rema inder

Shift right

Shift lef t

Wr i te

C on trol

te s t

Remainder >

0

Test Remainder

Remainder < 0

64 bit s

3a. Shift the Remainder register to the

left, setting the new rightmost bit to 1

Can we eliminate the

quotient register?

3b. Restore the original value by adding

the Divisor register to the left half of the

Remainder register and place the sum

in the left half of the Remainder register.

Also shift the Remainder register to the

left, setting the new rightmost bit to 0

32nd repetition?

No: < 32 repetitions

Yes: 32 repetitions

Done. Shift left half of Remainder right 1 bit

Multiply vs. Divide

Divisor

Multiplicand

32 bits

32 bits

32- bit ALU

32-bit ALU

Remainder

Shift right

Shift left

Write

64 bits

Divide/multiply

C ontrol

test

Product

Shift right

Write

Control

test

64 bits

Multiply

Signed Division

Just make both operands positive and remember the sign

Must set the sign of the remainder though!

In MIPS

HI and LOW registers used for 64-bit register

Floating Point (FP)

Binary fractions:

10112 = 1x23 + 0x22 + 1x21 + 1x20

AND:

101.012 = 1x22 + 0x21 + 1x20 + 0x2-1 + 1x2-2

Example:

.75 = 3/4 = 1/2 + 1/4 = .112

Recall Scientific Notation

exponent

decimal point

sign

+6.02 x 10

Mantissa

23

radix (base)

Issues:

Arithmetic (+, -, *, / )

Representation, Normal form

Range and Precision

Rounding

Exceptions (e.g., divide by zero, overflow, underflow)

Errors

Properties ( negation, inversion, if A = B then A - B = 0 )

IEEE 754 FP Numbers

Single precision

representation of

(-1)S 2E-127 (1.M)

sign

bit

23

exponent:

excess 127

binary integer

(actual exponent

is e = E - 127)

mantissa:

sign + magnitude, normalized

binary significand with hidden

integer bit: 1.M

0 = 0 00000000 00 . . . 0

-1.5 = 1 01111111 10 . . . 0

325 = 101000101 = 1.01000101 x 28

= 0 10000111 01000101000000000000000

.02 = .0011001101100... = 1.1001101100... x 2-3

= 0 01111100 1001101100...

range of about 2 X 10-38 to 2 X 1038

always normalized (so always leading 1, never shown)

special representation of 0 (E = 00000000)

can do integer compare for greater-than, sign

Double Precision FP (IEEE 754)

sign

11

20

32

exponent:

excess 1023

binary integer

actual exponent is e = E - 1023

N = (-1)S 2 E-1023(1.M)

52 (+1) bit mantissa

range of about 2 X 10-308 to 2 X 10308

mantissa:

sign + magnitude, normalized

binary significand with hidden

integer bit: 1.M

Range of FP Numbers

Exponent

Fraction

Object

Denormalized Number

1 to 254

any

Normalized Number

(regular floating point number)

255

255

NaN

Range of the floating point number:

Single precision: 2126~2127 (1038~1038)

Double Precision: 21022~21023 (10308~10308)

FP Addition

How do you add in scientific notation?

9.962 x 104 + 5.231 x 102

Basic Algorithm

1. Align

2. Add

3. Normalize

4. Round

Not exact

Usually, rounding throws away bits at the end.

Subtracting two nearly-equal numbers doesnt lose

bits, but answer doesnt have as many significant

bits.

FP Addition

S ig n

Exponent

Significand

Sign

E xponent

Significa nd

S tart

Compare

exponents

Small ALU

1. Compare the exponents of the two numbers.

Shift the smaller number to the right until its

exponent would match the larger exponent

Exponent

difference

0

2. Add the significands

Control

Shift smaller

number right

S h if t r ig h t

3. Normalize the sum, either shifting right and

incrementing the exponent or shifting left

and decrementing the exponent

Big ALU

Overflow or

underflow?

Add

Yes

No

0

Exception

Increm ent or

decrement

Shift left or right

Normalize

4. Round the significand to the appropriate

number of bits

Rounding hardware

No

Still normalized?

Yes

Done

Sign

Exponent

Significand

Round

FP Multiplication

Multiply in scientific notation?

(9.9 x

104)(5.2

102)

Basic Algorithm

1. Add exponents

2. Multiply

3. Normalize

4. Round

5. Set Sign

= 5.148 x

107

S ta rt

1 . A d d t h e b i a s e d e x p o n e n t s o f t h e tw o

n u m be rs , s ub tra ct in g t he bia s fr o m th e su m

to g e t th e n e w b i a s e d e x p o n e n t

2 . M u l ti p l y t h e s i g n i f i c a n d s

3 . N o rm a liz e the p ro d uc t i f n e c e ss ar y, sh if tin g

i t r i g h t a n d i n c r e m e n ti n g th e e x p o n e n t

O v e rf l o w o r

u n d e rf l o w ?

Yes

No

4 . R o u n d t he s ig nif ic an d to th e a p p rop ria te

n u m b e r o f b it s

No

S ti l l n o r m a l i z e d ?

Yes

5 . S et th e s ig n o f t h e p r o d uc t t o p os it iv e if t he

si gn s of the o rig in al op er an ds a re t he s am e ;

if th e y d if fe r m a k e t h e s ig n n e g at iv e

D o ne

E x ce p t io n

Floating Point Accuracy

Extremely important in scientific calculations

Very tiny errors can accumulate over time

IEEE 754 has four rounding modes

always round up (toward +)

always round down (toward -)

truncate (i.e. round towards zero)

round to nearest

=> in case of tie, round to nearest even

Requires extra bits in intermediate

representations

Extra Bits for FP Accuracy

Guard bits -- bits to the right of the least

significant bit of the significand computed for

use in normalization (could become significant

at that point) and rounding.

IEEE 754 has three extra bits and calls them

guard, round, and sticky.

Key Points

Multiplication and Division take much longer

than Addition and Subtraction

Floating Point extends the range of numbers

that can be represented, but at the expense of

precision

FP operations are very similar to integer

operations, but have pre- and post- processing

Rounding implementation is critical to accuracy

over time

Key Terms and Problems

Floating point, single/double precision,

normalized, scientific notation, biased

notation

Interprets of word (instruction, integer,

floating point)

Ripple carry adder versus carry lookahead

adder

Three versions of multiply/divide algorithms,

Booths algorithm

Das könnte Ihnen auch gefallen

- Arithmetic & Logic UnitDokument58 SeitenArithmetic & Logic Unitakbisoi1Noch keine Bewertungen

- PPTDokument9 SeitenPPTsindhuvindhya100% (1)

- Computer Science 37 Lecture 9Dokument17 SeitenComputer Science 37 Lecture 9Alexander TaylorNoch keine Bewertungen

- Review: MIPS Organization: Processor MemoryDokument13 SeitenReview: MIPS Organization: Processor MemorytyfnpkrNoch keine Bewertungen

- Review Multiple Hardware AlgorithmsDokument6 SeitenReview Multiple Hardware AlgorithmsNarender KumarNoch keine Bewertungen

- ECE4680 Computer Organization & Architecture Divide, Floating Point, Pentium BugDokument17 SeitenECE4680 Computer Organization & Architecture Divide, Floating Point, Pentium BugNarender KumarNoch keine Bewertungen

- Computer Organization and Architecture Computer ArithmeticDokument78 SeitenComputer Organization and Architecture Computer ArithmeticTirusew AbereNoch keine Bewertungen

- 10-Floating Point Representation With IEEE Standards and Algorithms For Common Arithmetic operations-30-Jul-2019Material - IDokument34 Seiten10-Floating Point Representation With IEEE Standards and Algorithms For Common Arithmetic operations-30-Jul-2019Material - Ividhi agarwalNoch keine Bewertungen

- FALLSEM2019-20 CSE2001 TH VL2019201000585 Reference Material I 13-Aug-2019 Data Representation and Computer Arithmetic 2019 2010Dokument34 SeitenFALLSEM2019-20 CSE2001 TH VL2019201000585 Reference Material I 13-Aug-2019 Data Representation and Computer Arithmetic 2019 2010Puneeth SaiNoch keine Bewertungen

- Basic Arithmetic OperationsDokument34 SeitenBasic Arithmetic OperationsGeorge ChalhoubNoch keine Bewertungen

- 09 ArithmeticDokument41 Seiten09 ArithmeticEva WilizNoch keine Bewertungen

- CH 8 StallingsDokument38 SeitenCH 8 StallingsRifah TasniaNoch keine Bewertungen

- CH 8 StallingsDokument38 SeitenCH 8 StallingsRifah TasniaNoch keine Bewertungen

- How To Represent Real Numbers: - in Decimal Scientific NotationDokument16 SeitenHow To Represent Real Numbers: - in Decimal Scientific NotationJulie AlicosNoch keine Bewertungen

- Approximation and Error Concepts in Numerical MethodsDokument553 SeitenApproximation and Error Concepts in Numerical Methodsfuwad84100% (1)

- 198:211 Computer Architecture: TopicsDokument35 Seiten198:211 Computer Architecture: TopicsJaswant SinghNoch keine Bewertungen

- Chapter 8Dokument39 SeitenChapter 8arif muttaqinNoch keine Bewertungen

- MMW111 - Group 6: Topics: Integers in Computer Logic and Computer AdditionDokument45 SeitenMMW111 - Group 6: Topics: Integers in Computer Logic and Computer AdditionCham RosarioNoch keine Bewertungen

- Float Point MultiplierDokument6 SeitenFloat Point MultiplierDang NguyenNoch keine Bewertungen

- Module 6 DldcaDokument45 SeitenModule 6 Dldcasneha chauhanNoch keine Bewertungen

- Computer Organization and Architecture: Central Processing Unit Computer ArithmeticDokument30 SeitenComputer Organization and Architecture: Central Processing Unit Computer ArithmeticZersh EthioNoch keine Bewertungen

- CS205-Assignment1-solutionDokument7 SeitenCS205-Assignment1-solutionjohnnybyzhangNoch keine Bewertungen

- CSC 258 Numerical Representation and ArithmeticDokument51 SeitenCSC 258 Numerical Representation and ArithmeticApurva SinghNoch keine Bewertungen

- Lecture 8: Binary Multiplication & DivisionDokument20 SeitenLecture 8: Binary Multiplication & DivisionTahir KhanNoch keine Bewertungen

- Computer Arithmetic: ALU, Integer Representation, Floating PointDokument37 SeitenComputer Arithmetic: ALU, Integer Representation, Floating PointreinaldoopusNoch keine Bewertungen

- Booth's Algorithm ExplainedDokument14 SeitenBooth's Algorithm ExplainedFarhat VooDooNoch keine Bewertungen

- Lecture 8: Binary Multiplication & DivisionDokument20 SeitenLecture 8: Binary Multiplication & DivisionAfnanNoch keine Bewertungen

- Chapter IV Computer ArithmeticDokument133 SeitenChapter IV Computer ArithmeticjohnsamvlbNoch keine Bewertungen

- BOOTHDokument3 SeitenBOOTHBharath VijaiNoch keine Bewertungen

- Unit 3Dokument49 SeitenUnit 3zccoffin007Noch keine Bewertungen

- CS37 Lecture 7 Floating Point NumbersDokument39 SeitenCS37 Lecture 7 Floating Point NumbersdvfgdfggdfNoch keine Bewertungen

- Ch2 - Lec1 - Computer ArithmeticDokument36 SeitenCh2 - Lec1 - Computer ArithmeticMagarsaa Qana'iiNoch keine Bewertungen

- This Unit: Arithmetic and ALU Design ShiftsDokument8 SeitenThis Unit: Arithmetic and ALU Design ShiftsBhagya RajuNoch keine Bewertungen

- ArithmeticDokument37 SeitenArithmeticArnav SharmaNoch keine Bewertungen

- CS M151B / EE M116C: Computer Systems ArchitectureDokument33 SeitenCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacNoch keine Bewertungen

- Computer Organization - Data Representation On CPUDokument67 SeitenComputer Organization - Data Representation On CPUBadrulshahputra BashaNoch keine Bewertungen

- Lecture 4 Computer Arithmetic Part I IntegersDokument19 SeitenLecture 4 Computer Arithmetic Part I IntegerstesfuNoch keine Bewertungen

- Register Transfer and MicrooperationsDokument35 SeitenRegister Transfer and MicrooperationsPerfectamente EstupendoNoch keine Bewertungen

- Affan Telek - F23 Lab01 Algorithms 3Dokument8 SeitenAffan Telek - F23 Lab01 Algorithms 3Affan TelekNoch keine Bewertungen

- Computer Arithmetic Chapter 9Dokument12 SeitenComputer Arithmetic Chapter 9Mohammed BilalNoch keine Bewertungen

- Logic Circuits and Switching TheoryDokument57 SeitenLogic Circuits and Switching TheoryBruce Lamb100% (1)

- Computer Arithmetic Part I: IntegersDokument19 SeitenComputer Arithmetic Part I: IntegerstesfuNoch keine Bewertungen

- EE201: Digital Circuits and Systems: Section 3 - Arithmetic Logic UnitDokument27 SeitenEE201: Digital Circuits and Systems: Section 3 - Arithmetic Logic UnitMahmoud KamelNoch keine Bewertungen

- Contact Session 2Dokument35 SeitenContact Session 2api-3724082Noch keine Bewertungen

- Digital Arithmetic: Operations and Circuits: Chapter-6Dokument44 SeitenDigital Arithmetic: Operations and Circuits: Chapter-6Samina TohfaNoch keine Bewertungen

- Binary Numbers and ArithmeticDokument50 SeitenBinary Numbers and ArithmeticRohit MaheshwariNoch keine Bewertungen

- Digital Integrated Circuits: Traian Tulbure NII13Dokument55 SeitenDigital Integrated Circuits: Traian Tulbure NII13boymatterNoch keine Bewertungen

- Processor Design 5Z032: Arithmetic For ComputersDokument57 SeitenProcessor Design 5Z032: Arithmetic For ComputersdishatiwariNoch keine Bewertungen

- Running Addition ON Partial-Products (Multiplication)Dokument16 SeitenRunning Addition ON Partial-Products (Multiplication)Niel Roel VelascoNoch keine Bewertungen

- Division Algorithms ExplainedDokument19 SeitenDivision Algorithms ExplainedKomal SwamiNoch keine Bewertungen

- Binary SlidesDokument26 SeitenBinary Slidesdjenkins12318Noch keine Bewertungen

- Floatpoint IntroDokument20 SeitenFloatpoint IntroItishree PatiNoch keine Bewertungen

- Computer Architecture and Organization: The Central Processing UnitDokument126 SeitenComputer Architecture and Organization: The Central Processing Unitcudarun100% (1)

- Blick Propeller Clock: Ònoblinkó Main Program OverviewDokument9 SeitenBlick Propeller Clock: Ònoblinkó Main Program OverviewOpLight TranNoch keine Bewertungen

- Digital Electronics For Engineering and Diploma CoursesVon EverandDigital Electronics For Engineering and Diploma CoursesNoch keine Bewertungen

- Python Programming for Beginners Crash Course with Hands-On Exercises, Including NumPy, Pandas and MatplotlibVon EverandPython Programming for Beginners Crash Course with Hands-On Exercises, Including NumPy, Pandas and MatplotlibNoch keine Bewertungen

- GCSE Maths Revision: Cheeky Revision ShortcutsVon EverandGCSE Maths Revision: Cheeky Revision ShortcutsBewertung: 3.5 von 5 Sternen3.5/5 (2)

- Fundamentals of Electronics 3: Discrete-time Signals and Systems, and Quantized Level SystemsVon EverandFundamentals of Electronics 3: Discrete-time Signals and Systems, and Quantized Level SystemsNoch keine Bewertungen

- CS M151B / EE M116C: Computer Systems ArchitectureDokument29 SeitenCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacNoch keine Bewertungen

- M116C 1 M116C 1 Lect02-PerformanceDokument23 SeitenM116C 1 M116C 1 Lect02-PerformancetinhtrilacNoch keine Bewertungen

- CS151B/EE116C - Solutions To Homework #2: ProblemDokument6 SeitenCS151B/EE116C - Solutions To Homework #2: ProblemtinhtrilacNoch keine Bewertungen

- CS M151B / EE M116C: Computer Systems ArchitectureDokument50 SeitenCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacNoch keine Bewertungen

- CS M151B / EE M116C: Computer Systems ArchitectureDokument33 SeitenCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacNoch keine Bewertungen

- HW 2Dokument1 SeiteHW 2tinhtrilacNoch keine Bewertungen

- CS151B/EE116C - Solutions To Homework #1Dokument3 SeitenCS151B/EE116C - Solutions To Homework #1tinhtrilacNoch keine Bewertungen

- 7fff FffaDokument4 Seiten7fff FffatinhtrilacNoch keine Bewertungen

- CS M151B / EE M116C: Computer Systems ArchitectureDokument36 SeitenCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacNoch keine Bewertungen

- M116C 1 M116C 1 Lec10-Pipeline-IIDokument18 SeitenM116C 1 M116C 1 Lec10-Pipeline-IItinhtrilacNoch keine Bewertungen

- CS M151B / EE M116C: Computer Systems ArchitectureDokument38 SeitenCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacNoch keine Bewertungen

- Interfacing Processors and Peripherals: CS151B/EE M116C Computer Systems ArchitectureDokument31 SeitenInterfacing Processors and Peripherals: CS151B/EE M116C Computer Systems ArchitecturetinhtrilacNoch keine Bewertungen

- CS M151B / EE M116C: Computer Systems ArchitectureDokument34 SeitenCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacNoch keine Bewertungen

- M116C 1 EE116C-Midterm2-w15 SolutionDokument8 SeitenM116C 1 EE116C-Midterm2-w15 Solutiontinhtrilac100% (1)

- HW7Dokument2 SeitenHW7tinhtrilacNoch keine Bewertungen

- Revision Questions Solution-2Dokument3 SeitenRevision Questions Solution-2tinhtrilacNoch keine Bewertungen

- Virtual Memory: CS151B/EE M116C Computer Systems ArchitectureDokument16 SeitenVirtual Memory: CS151B/EE M116C Computer Systems ArchitecturetinhtrilacNoch keine Bewertungen

- Revision Questions 2Dokument4 SeitenRevision Questions 2tinhtrilacNoch keine Bewertungen

- HW6 SolutionDokument2 SeitenHW6 SolutiontinhtrilacNoch keine Bewertungen

- Homework Set 4: Class CPI On P1 CPI On P2Dokument2 SeitenHomework Set 4: Class CPI On P1 CPI On P2tinhtrilacNoch keine Bewertungen

- Homework Set - 5Dokument2 SeitenHomework Set - 5tinhtrilacNoch keine Bewertungen

- CS151B/EE116C Homework 6Dokument2 SeitenCS151B/EE116C Homework 6tinhtrilacNoch keine Bewertungen

- Solution To Homework #5Dokument3 SeitenSolution To Homework #5tinhtrilacNoch keine Bewertungen

- Multiprocessors and Multithreading: CS151B/EE M116C Computer Systems ArchitectureDokument13 SeitenMultiprocessors and Multithreading: CS151B/EE M116C Computer Systems ArchitecturetinhtrilacNoch keine Bewertungen

- EEM116C Midterm1 Winter 2015 s2 SolutionDokument5 SeitenEEM116C Midterm1 Winter 2015 s2 SolutiontinhtrilacNoch keine Bewertungen

- Introductory Handbook On Microprocessor Controlled Electric Locomotives PDFDokument35 SeitenIntroductory Handbook On Microprocessor Controlled Electric Locomotives PDFDinesh Mehta100% (1)

- MusicalDokument4 SeitenMusicalGwynbleiddNoch keine Bewertungen

- E17040 ZenWiFi AX XT8 UM PDFDokument151 SeitenE17040 ZenWiFi AX XT8 UM PDFEP TANNoch keine Bewertungen

- Manual Drilling OperationDokument13 SeitenManual Drilling OperationnaninoNoch keine Bewertungen

- Programming Languages ERDDokument1 SeiteProgramming Languages ERDkosaialbonniNoch keine Bewertungen

- NWDISystemDokument16 SeitenNWDISystemYvette CamposNoch keine Bewertungen

- Transformation CarteDokument5.774 SeitenTransformation CartePeter BoulasNoch keine Bewertungen

- 1162-1619624546635-Unit 16 - Cloud-Computing - Reworded - 2021Dokument49 Seiten1162-1619624546635-Unit 16 - Cloud-Computing - Reworded - 2021Vivekan VivekNoch keine Bewertungen

- Schedule Review ChecklistDokument1 SeiteSchedule Review ChecklistErwin ObenzaNoch keine Bewertungen

- Android Ranch ProgrammingDokument69 SeitenAndroid Ranch ProgrammingReg Nullify100% (2)

- Android LayoutsDokument51 SeitenAndroid LayoutsLona Jean AberillaNoch keine Bewertungen

- Design, Prototyping and Construction: by Anupa Mogili Arun MuralidharanDokument51 SeitenDesign, Prototyping and Construction: by Anupa Mogili Arun MuralidharanTobi MMNoch keine Bewertungen

- FortiClient EMS 6.2 Course Description-OnlineDokument2 SeitenFortiClient EMS 6.2 Course Description-OnlineyoubpNoch keine Bewertungen

- Build an Automated Airsoft Gun TurretDokument19 SeitenBuild an Automated Airsoft Gun TurretWeb devNoch keine Bewertungen

- PowerPoint TemplateDokument20 SeitenPowerPoint Templatehuynhducquoc0122100% (3)

- Novakovic Srbi I TurciDokument415 SeitenNovakovic Srbi I TurciBorisSubNoch keine Bewertungen

- Company Profile-Human Resource ServicesDokument16 SeitenCompany Profile-Human Resource Servicessyed pashaNoch keine Bewertungen

- Datasheet MX 880Dokument3 SeitenDatasheet MX 880jorge_chavez01Noch keine Bewertungen

- Galileo Reservation ManualDokument47 SeitenGalileo Reservation Manualatelelellelelele ateNoch keine Bewertungen

- Basic Overview of Ms Dos CommandsDokument6 SeitenBasic Overview of Ms Dos CommandsAjay ChandranNoch keine Bewertungen

- Sybase 12 Install InstructionsDokument29 SeitenSybase 12 Install InstructionsJohn ThorntonNoch keine Bewertungen

- Oce Arizona 350XT BrochureDokument2 SeitenOce Arizona 350XT BrochuremarcelcoopersNoch keine Bewertungen

- Advanced Geometrical Optics by P D Lin Scope TextbDokument3 SeitenAdvanced Geometrical Optics by P D Lin Scope TextbShrey badoniNoch keine Bewertungen

- Programmable Switching DC Power SupplyDokument6 SeitenProgrammable Switching DC Power SupplyPaolo CristianiNoch keine Bewertungen

- PhoneGap API DocumentationDokument1 SeitePhoneGap API DocumentationCAMILA CARMONA SALAZARNoch keine Bewertungen

- Test Suite Siprotec 5Dokument27 SeitenTest Suite Siprotec 5Guillermo BetancourtNoch keine Bewertungen

- Find optimal sums of three numbers using greedy and backtrackingDokument8 SeitenFind optimal sums of three numbers using greedy and backtrackingAida VoicuNoch keine Bewertungen

- Smart Battery Data Specification Revision 1.1 ErrataDokument5 SeitenSmart Battery Data Specification Revision 1.1 ErrataredmsbatteryNoch keine Bewertungen

- Hyperion Strategy and RoadmapDokument48 SeitenHyperion Strategy and RoadmapSamrat MitraNoch keine Bewertungen

- Software Validation TemplateDokument8 SeitenSoftware Validation TemplateHouser_BRNoch keine Bewertungen