Beruflich Dokumente

Kultur Dokumente

Gal PDF

Hochgeladen von

hansolosnahOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Gal PDF

Hochgeladen von

hansolosnahCopyright:

Verfügbare Formate

Introduction to GAL

Device Architectures

Base Products - Aimed at providing superior design

alternatives to bipolar PLDs, these five architectures

replace over 98% of all bipolar PAL devices. The GAL16V8

and GAL20V8 replace forty-two different PAL devices.

The GAL22V10, GAL20RA10, and GAL20XV10 round

out the base products. These GAL devices meet and, in

most cases, beat bipolar PAL performance specifications while consuming significantly lower power and

offering higher quality and reliability via Lattices electrically reprogrammable E2CMOS technology. High-speed

erase times (<100ms) allow the devices to be reprogrammed quickly and efficiently.

Overview

In 1985, Lattice Semiconductor introduced a new type of

programmable logic device (PLD) that transformed the

PLD market: the Generic Array Logic (GAL) device. The

E2CMOS technology of the GAL devices gave them

significant advantages over their bipolar PAL counterparts; not only could GAL devices be programmed quickly

and efficiently, but they could also be erased and reprogrammed. Today, Lattice is the leading supplier,

worldwide, of low-density PLDs. Industry leading performance, low power E2CMOS technology, 100% testability

and 100% programming yields make the GAL family the

preferred choice among system designers.

Extension Products - These products build upon the

Base GAL product features to provide enhanced functionality including innovative architectures (GAL18V10,

GAL26CV12, GAL6001/6002), 64mA high output drive

(GAL16VP8 & GAL20VP8), Zero power operation

(GAL16V8Z/ZD & GAL20V8Z/ZD) and In-System Programmability (ispGAL22V10).

The GAL family includes fourteen distinct product architectures, with a variety of performance levels specified

across commercial, industrial, and military (MIL-STD883) operating ranges, to meet the demands of any

system logic design.

A Product for any System Design Need

These GAL products can be segmented into two broad

categories:

Lattice GAL products have the performance, architectural features, low power, and high quality to meet the

needs of the most demanding system designs.

Lattice offers the broadest line of high-performance PLDs.

introgal_02

1996 ISP Encyclopedia

Introduction to GAL Device Architectures

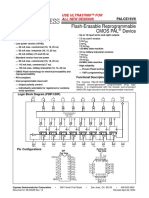

The GAL16V8 and GAL20V8

The GAL16V8 (20-pin) and GAL20V8 (24-pin) provide

the highest speed performance available in the PLD

market at 3.5 ns and 5.0 ns respectively. CMOS circuitry

allows the GAL16V8 and GAL20V8 low power devices to

consume just 75mA typical Icc, which represents a 50%

savings in power when compared to bipolar counterparts. Quarter power versions save even more at 45mA

Icc.

vices are capable of emulating virtually all PAL architectures with full function/fuse map/parametric compatibility.

Output Logic Macrocell

There are three OLMC configuration modes possible in

GAL16V8 and GAL20V8 devices: registered, complex,

and simple. These are illustrated in the diagrams on the

following pages. You cannot mix modes; all OLMCs are

either simple, complex, or registered (in registered mode,

the output can be combinational or registered).

The GAL16V8 is a 20-pin device which contains eight

dedicated input pins and eight I/O pins. The GAL20V8 is

a 24-pin version of the 16V8 device with 12 dedicated

input pins and eight I/O pins. Their generic architecture

provides maximum design flexibility by allowing the Output Logic Macrocell (OLMC) to be configured by the user.

An important subset of the many architecture configurations possible with the GAL16V8 and GAL20V8 are the

standard PAL architectures. Providing eight OLMCs with

eight product terms each, GAL16V8 and GAL20V8 de-

The outputs of the AND array are fed into an OLMC,

where each output can be individually set to active high

or active low, with either combinational (asynchronous)

or registered (synchronous) configurations. A common

output enable is connected to all registered outputs, or a

product term can be used to provide individual output

I/CLK

GAL20V8 Only

I

IMUX

CLK

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

OLMC

E CMOS Programmable

AND Array

I

IMUX

I/OE

GAL20V8 Only

GAL20V8 Only

GAL16V8 and GAL20V8 Block Diagram

1996 ISP Encyclopedia

Introduction to GAL Device Architectures

enable control for combinational outputs in the registered

mode or combinational outputs in the complex mode.

ibility in matching signal requirements, thus providing

more functionality than possible with standard PAL devices.

There is no output enable control in the simple mode. The

OLMC provides the designer with maximum output flexRegistered Configuration for Registered Mode

Combinatorial Output with Feedback

Configuration for Simple Mode

CLK

Vcc

Q

Q

XOR

XOR

OE

Combinatorial Configuration for Registered Mode

Combinatorial Output Configuration for Simple

Mode

Vcc

XOR

XOR

Combinatorial Output Configuration for Complex

Mode

Dedicated Input Configuration for Simple Mode

XOR

1996 ISP Encyclopedia

Introduction to GAL Device Architectures

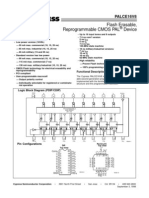

The GAL22V10, GAL18V10 and GAL26CV12

Three devices are offered in the high-speed, E2CMOS

GAL22V10 family: the GAL22V10 (24-pin), GAL18V10

(20-pin), and GAL26CV12 (28-pin). Each of these devices uses the industry standard 22V10 universal

architecture, which provides maximum design flexibility

by allowing the OLMC to be configured by the user. The

GAL22V10 family low power devices consume just 90mA

typical Icc, with quarter power versions consuming only

45mA Icc. The devices differ in the number of I/Os, pins,

and product terms offered.

The GAL26CV12 is a 28-pin version of the 22V10 device.

It features more inputs and outputs in order to provide

greater functionality and increased I/O. The GAL26CV12

contains fourteen dedicated input pins and twelve

macrocells and I/O pins.

Output Logic Macrocell

The GAL22V10, 18V10, and 26CV12 each have a variable number of product terms per OLMC. Of the ten

OLMCs available in the GAL22V10, two have access to

eight product terms, two have ten product terms, two

have 12 product terms, two have 14 product terms, and

two have 16 product terms. Of the ten OLMCs available

in the GAL18V10, eight have access to eight product

terms, and two have ten product terms. Of the 12 OLMCs

available in the GAL26CV12, eight have access to eight

product terms, two have ten product terms, and two have

12 product terms.

The 24-pin GAL22V10 contains twelve dedicated input

pins and ten macrocells and I/O pins. The device has a

variable number of product terms per OLMC, ranging

from eight to sixteen per output.

The GAL18V10 is a 20-pin version of the popular 22V10

device. It provides a smaller footprint and lower cost

alternative to the 22V10 device. The GAL18V10 contains

eight dedicated input pins and ten macrocells and I/O

pins.

ASYNC.

RESET

SYNC.

PRESET

I/CLK

I

I

I

I

I

I

I

OLMC

I/O/Q

I/O/Q

I/O/Q

1

2

I/O/Q

3

I/O/Q

4

I/O/Q

5

I/O/Q

6

I/O/Q

7

I/O/Q

8

I/O/Q

9

I/O/Q

10

GAL26CV12

GAL18V10 and

GAL22V10

PROGRAMMABLE

AND-ARRAY

GAL18V10

GAL22V10

GAL26CV12

I/O/Q

11

12

GAL22V10, GAL18V10 and GAL26CV12 Block Diagram

1996 ISP Encyclopedia

Introduction to GAL Device Architectures

The output polarity of each OLMC can be individually

programmed to be true or inverting, in either combinational or registered mode. This allows the user to reduce

the overall number of product terms required in a design

and/or to invert the output signal.

GAL22V10 family devices have a product term for Asynchronous Reset (AR) and a product term for Synchronous

Preset (SP). These two product terms are common to all

registered OLMCs.

GAL22V10, GAL18V10 and GAL26CV12 Output Logic Macrocell

A R

D

Q

CLK

4 TO 1

MUX

Q

SP

2 TO 1

MUX

Output Logic Macrocell Configuration (Registered Mode)

AR

AR

CLK

CLK

SP

Q

SP

Active Low

Active High

Output Logic Macrocell Configuration (Combinatorial Mode)

Active Low

Active High

1996 ISP Encyclopedia

Introduction to GAL Device Architectures

The GAL20RA10

The GAL20RA10 (24-pin) supports high performance,

asynchronous logic. It is a direct parametric compatible

CMOS replacement for the PAL20RA10 device. However, Lattices E2CMOS circuitry achieves power levels

as low as 75mA typical Icc, which represents a substantial savings in power when compared to bipolar

counterparts like the PAL20RA10.

the state of the programmable polarity bit. The ability to

program the active polarity of the D-inputs can be used to

reduce the total number of product terms used, by allowing the DeMorganization of the logic functions. This logic

reduction is accomplished by the logic compiler, and

does not require the designer to define the polarity.

PL

The GAL20RA10 contains ten dedicated input pins and

ten I/O pins. As with other GAL devices, it has userconfigurable OLMCs.

Output Logic Macrocell

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

The GAL20RA10 OLMC consists of ten D flip-flops with

individual asynchronous programmable reset, preset,

and clock product terms. The four product terms and an

Exclusive-OR gate provide a programmable polarity Dinput to each flip-flop. An output enable term, combined

with a dedicated output enable pin, provide tri-state

control of each output. Each OLMC has a flip-flop bypass, allowing any combination of registered or

combinational outputs.

An independent clock control product term is provided for

each GAL20RA10 macrocell. Data is clocked into the

flip-flop on the active edge of the clock product term. The

use of individual clock control product terms allows up to

ten separate clocks. These clocks can be derived from

any pin or combination of pins and/or feedback from

other flip-flops. Multiple clock sources allow a number of

asynchronous register functions to be combined into a

single GAL20RA10. This allows the designer to combine

discrete logic functions into a single device.

PROGRAMMABLE

AND-ARRAY

(80X40)

The polarity of the D-input to each macrocell flip-flop is

individually programmable to be active high or low. This

is accomplished with a programmable Exclusive-OR

gate on the D-input of each flip-flop. While any one of the

four logic function product terms are active, the D-input

to the flip-flop will be low if the Exclusive-OR bit is set to

zero, and high if the Exclusive-OR bit is set to one. It

should be noted that the programmable polarity only

affects the data latched into the flip-flop on the active

edge of the clock product term. The reset, preset, and

preload will alter the state of the flip-flop independent of

OE

GAL20RA10 Block Diagram

1996 ISP Encyclopedia

Introduction to GAL Device Architectures

GAL20RA10 Output Logic Macrocell Diagram

PL

OE

PL

AR

PD

D

AP

0

1

X O R (n )

Output Logic Macrocell Configuration (Registered with Polarity)

PL

OE

PL

AR

PD

Q

AP

X O R (n )

Output Logic Macrocell Configuration (Combinatorial with Polarity)

OE

XOR (n)

1996 ISP Encyclopedia

Introduction to GAL Device Architectures

The GAL20XV10

The GAL20XV10 (24-pin) provides the highest speed,

low-density Exclusive-OR PLD available in the market,

making it perfect for the fast counters, decoders, or

comparators common in video, multimedia, and graphics

applications. At 75mA typical Icc, the E2 CMOS

GAL20XV10 reduces power by over 50% from bipolar

XOR architectures.

When the macrocell is set to the Exclusive-OR Registered configuration, the four product terms are segmented

into two OR-sums of two product terms each, which are

then combined by an Exclusive-OR gate and fed into a Dtype register that is clocked by the low-to-high transition

of the I/CLK pin.

When the macrocell is set to Registered configuration,

three of the four product terms are used as sum-ofproduct terms for the D input of the register. The inverting

output buffer is enabled by the fourth product term. The

output is enabled while this product term is true. The XOR

bit controls the polarity of the output.

The GAL20XV10 is a 24-pin device which contains ten

dedicated input pins and ten I/O pins. Its generic architecture provides maximum design flexibility by allowing the

Output Logic Macrocell (OLMC) to be configured by the

user. An important subset of the many architecture configurations possible with the GAL20XV10 are the standard

PAL architectures. Providing ten OLMCs with four product terms each, the GAL20XV10 is capable of emulating

the PAL12L10, PAL20L10, PAL20X10, PAL20X8, and

PAL20X4 devices.

When the macrocell is set to the Exclusive-OR combinatorial configuration, the four product terms are segmented

into two OR-sums of two product terms each, which are

then combined by an Exclusive-OR gate and fed to an

output buffer.

Output Logic Macrocell

I/CLK

Each OLMC has an Exclusive-OR gate capability with

programmable polarity. This minimizes product term

usage.

4

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

The GAL20XV10 has two global OLMC architecture

configurations that allow it to emulate PAL architectures.

Input mode emulates combinatorial PAL devices, whereas

Feedback mode emulates registered PAL devices.

I

4

Each OLMC has four possible logic function configurations: XOR Registered, Registered, XOR Combinatorial,

and Combinatorial. Four product terms are fed into each

macrocell.

PROGRAMMABLE

AND-ARRAY

(40 X 40)

I

4

I/OE

GAL20XV10 Block Diagram

1996 ISP Encyclopedia

Introduction to GAL Device Architectures

GAL20XV10 OLMC Configurations

XOR Registered Configuration

Registered Configuration

OE

XOR

Q

Q

CLK

CLK

XOR Combinatorial Configuration

Combinatorial Configuration

OE

XOR

1996 ISP Encyclopedia

Introduction to GAL Device Architectures

The GAL16VP8 and GAL20VP8

The GAL16VP8 (20-pin) and 20VP8 (24-pin), with 64 mA

drive capability, are ideal for bus and memory control

applications. System bus and memory interfaces require

control logic before driving the bus or memory interface

signals. The GAL16VP8 and 20VP8 combine the familiar

GAL16V8 and 20V8 architectures (refer to the GAL16V8

and GAL20V8 section in this article) with bus drivers at

their outputs. Programmable open-drain or totem pole

outputs and 64mA output drive eliminate the need for

additional devices to provide bus-driving capability. Also,

Schmitt trigger inputs are provided to screen out noise.

GAL16VP8 Block Diagram

GAL20VP8 Block Diagram

I/CLK

I/CLK

I

I

I

CLK

IMUX

8

CLK

I/O/Q

OLMC

1

I

8

I/O/Q

OLMC

3

I/O/Q

OLMC

4

I/O/Q

OLMC

5

I/O/Q

OLMC

6

I

8

I

8

OE

OLMC

2

I/O/Q

OLMC

3

I/O/Q

OLMC

4

I/O/Q

OLMC

5

I/O/Q

OLMC

6

I/O/Q

OLMC

7

I/O/Q

OLMC

8

I/O/Q

I/O/Q

OLMC

8

I/O/Q

OLMC

7

I/O/Q

PROGRAMMABLE

AND-ARRAY

(64 X 40)

PROGRAMMABLE

AND-ARRAY

(64 X 32)

OLMC

1

I/O/Q

OLMC

2

I/OE

OE

10

IMUX

I

I/OE

1996 ISP Encyclopedia

Introduction to GAL Device Architectures

The GAL16V8Z/ZD and GAL20V8Z/ZD

GAL16V8 and 20V8 respectively (refer to the GAL16V8

and GAL20V8 section in this article). The GAL16V8ZD

and 20V8ZD utilize a dedicated power-down pin (DPP) to

put the device in standby mode.

The GAL16V8Z/ZD (20-pin) and GAL20V8Z/ZD (24pin), at 100uA standby current, provide the highest speed

and lowest power combination PLDs available in the

market. These devices are ideal for battery powered

systems.

The GAL16V8ZD has 15 inputs available to the AND

array, whereas the GAL20V8ZD has 19 inputs available

to the AND array.

The GAL16V8Z and 20V8Z use Input Transition Detection (ITD) to put the device in standby mode and are

capable of emulating the full functionality of the standard

GAL16V8Z/ZD Block Diagram

GAL20V8Z/ZD Block Diagram

I/CLK

I/CLK

CLK

OLMC

1

I/O/Q

OLMC

2

I/O/Q

IMUX

CLK

I

8

I/O/Q

OLMC

4

I/O/Q

OLMC

5

I/O/Q

8 OLMC

2

I/O/Q

8 OLMC

3

I/O/Q

8 OLMC

4

I/O/Q

8 OLMC

5

I/O/Q

8 OLMC

6

I/O/Q

8 OLMC

7

I/O/Q

OLMC

8

I/O/Q

I/DPP

OLMC

3

OLMC

6

I/O/Q

PROGRAMMABLE

AND-ARRAY

(64 X 40)

PROGRAMMABLE

AND-ARRAY

(64 X 32)

I/DPP

I/O/Q

I

8

8 OLMC

1

OLMC

7

I/O/Q

OLMC

8

I/O/Q

I

I

8

I

OE

I/OE

OE

I

IMUX

I/OE

11

1996 ISP Encyclopedia

Introduction to GAL Device Architectures

The GAL6001 and GAL6002

Offering an FPLA architecture and superior flexibility in

state machine design, the GAL6001 (24-pin) and

GAL6002 (24-pin) provide a high degree of functional

integration and flexibility in a 24-pin device.

Input Logic Macrocell (ILMC) and I/O Logic

Macrocell (IOLMC)

The GAL6001 and 6002 feature two configurable input

sections. The ILMC section corresponds to the dedicated

input pins, and the IOLMC section corresponds to the

I/O pins. On the GAL6001, each input section is

configurable as a block for asynchronous, latched, or

registered inputs. On the GAL6002, however, each input

section is individually configurable as asynchronous,

latched, or registered inputs. ICLK is used as an enable

input for latched macrocells or as a clock input for

registered macrocells. Configurable input blocks provide

system designers with unparalleled design flexibility.

With the GAL6001 and 6002, external input registers and

latches are not necessary.

The GAL6001 and GAL6002 have ten programmable

Output Logic Macrocells (OLMCs) and eight programmable Buried Logic Macrocells (BLMCs). In addition,

there are ten Input Logic Macrocells (ILMCs) and ten I/O

Logic Macrocells (IOLMCs). Two clock inputs are provided for independent control of the input and output

macrocells.

The GAL6001 and 6002 contain two E2 reprogrammable

arrays, an AND array and an OR array. The AND array is

organized as 78 inputs by 75 product term outputs. Ten

ILMCs, ten IOLMCs, eight BLMC feedbacks, ten OLMC

feedbacks, and ICLK comprise the 39 inputs into this

array. The OR array is organized as 64 inputs by 36 sum

term outputs. 64 product terms from the AND array serve

as the inputs to the OR array.

For the GAL6001, both the ILMC and the IOLMC are

block configurable; however, the ILMC can be configured

independently of the IOLMC. For the GAL6002, both the

ILMC and the IOLMC are individually configurable, and

the ILMC can be configured independently of the IOLMC.

ICLK

INPUT

CLOCK

14

11

23

ILMC

IOLMC

RESET

2

INPUTS

2-11

AND

OUTPUT

ENABLE

14

23

OLMC

E

OR

BLMC

{ OUTPUTS

14 - 23

OCLK

OUTPUT

CLOCK

GAL6001 and GAL6002 Block Diagram

12

1996 ISP Encyclopedia

Introduction to GAL Device Architectures

with directional control provided by the ten output enable

(OE) product terms. Additionally, the polarity of each

OLMC output is selected through the D XOR. Polarity

selection is available for BLMCs, since both the true and

complemented forms of their outputs are available in the

AND array. Polarity of all E sum terms is selected

through the E XOR.

Output Logic Macrocell (OLMC) and Buried

Logic Macrocell (BLMC)

The outputs of the OR array feed two groups of macrocells.

One group of eight macrocells is buried; its outputs feed

back directly into the AND array rather than to device

pins. These cells are called the Buried Logic Macrocells

(BLMCs), and are useful for building state machines. The

second group of macrocells consists of ten cells whose

outputs, in addition to feeding back into the AND array,

are available at the device pins. Cells in this group are

known as Output Logic Macrocells (OLMCs).

Registers in both the OLMCs and BLMCs feature a

common RESET product term. This active high product

term allows the registers to be asynchronously reset.

Registers are reset to a logic zero. If connected to an

output pin, a logic one will occur because of the inverting

output buffer.

The Output and Buried Logic Macrocells are configurable

on a macrocell by macrocell basis. They may be set to

one of three configurations: combinatorial, D-type register with sum term (asynchronous) clock, or D/E-type

register. Output macrocells always have I/O capability,

13

1996 ISP Encyclopedia

Introduction to GAL Device Architectures

The ispGAL22V10

The ispGAL22V10 (28-pin) provides the industrys first

in-system programmable 22V10 device. It is fully function/fuse map/parametric compatible with standard bipolar

and CMOS 22V10 devices (refer to the GAL22V10,

GAL18V10, and GAL26CV12 section in this article). The

standard 28-pin PLCC package provides the same functional pinout at the standard 22V10 PLCC package with

the four No-Connect pins being used for ISP interface

signals. For space constrained designs, Lattice offers

the 28-pin SSOP package.

RESET

I/CLK

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

OLMC

I/O/Q

12

PROGRAMMABLE

AND-ARRAY

(132X44)

I/O/Q

I/O/Q

Vcc

SCLK

I/CLK

OLMC

14

16

16

14

12

I/O/Q

10

The in-system programming capability of the

ispGAL22V10 allows designers to define and develop

systems with capabilities previously unattainable. ISP

provides the ability to program and reprogram logic

devices while attached to the printed circuit board (PCB).

No other logic technology is better for reducing time to

market, while assuring the highest system quality and

lowest overall cost. With ISP technology, hardware as

flexible and easy to modify as software becomes a reality:

hardware functions can be programmed and modified in

real time to expand product features, shorten system

design and debug time, enhance product

manufacturability and simplify field upgrades.

OLMC

10

I

8

4

I

28

26

25

I

I

23

PRESET

Programming

Logic

I/O/Q

SDO

SDI

MODE

SCLK

SDO

9

21

ispGAL22V10 Block Diagram

I/O/Q

I/O/Q

11

I/O/Q

I/O/Q

SCLK

I/CLK

I

I

I

I

I

MODE

I

I

I

I

I

GND

I/O/Q

19

18

16

SDI

14

12

GND

I/O/Q

MODE

I

I/O/Q

ispGAL22V10 28-Pin PLCC Pinout Diagram

28

22

14

15

Vcc

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

SDO

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I

SDI

ispGAL22V10 28-Pin SSOP Pinout Diagram

14

1996 ISP Encyclopedia

Copyright 1996 Lattice Semiconductor Corporation.

E2CMOS, GAL, ispGAL, ispLSI, pLSI, pDS, Silicon Forest, UltraMOS, Lattice Logo, L with Lattice Semiconductor Corp. and L

(Stylized) are registered trademarks of Lattice Semiconductor Corporation (LSC). The LSC Logo, Generic Array Logic, InSystem Programmability, In-System Programmable, ISP, ispATE, ispCODE, ispDOWNLOAD, ispGDS, ispStarter,

ispSTREAM, ispTEST, ispTURBO, Latch-Lock, pDS+, RFT, Total ISP and Twin GLB are trademarks of Lattice Semiconductor

Corporation. ISP is a service mark of Lattice Semiconductor Corporation. All brand names or product names mentioned are

trademarks or registered trademarks of their respective holders.

Lattice Semiconductor Corporation (LSC) products are made under one or more of the following U.S. and international

patents: 4,761,768 US, 4,766,569 US, 4,833,646 US, 4,852,044 US, 4,855,954 US, 4,879,688 US, 4,887,239 US, 4,896,296

US, 5,130,574 US, 5,138,198 US, 5,162,679 US, 5,191,243 US, 5,204,556 US, 5,231,315 US, 5,231,316 US, 5,237,218 US,

5,245,226 US, 5,251,169 US, 5,272,666 US, 5,281,906 US, 5,295,095 US, 5,329,179 US, 5,331,590 US, 5,336,951 US,

5,353,246 US, 5,357,156 US, 5,359,573 US, 5,394,033 US, 5,394,037 US, 5,404,055 US, 5,418,390 US, 5,493,205 US,

0194091 EP, 0196771B1 EP, 0267271 EP, 0196771 UK, 0194091 GB, 0196771 WG, P3686070.0-08 WG. LSC does not

represent that products described herein are free from patent infringement or from any third-party right.

The specifications and information herein are subject to change without notice. Lattice Semiconductor Corporation (LSC)

reserves the right to discontinue any product or service without notice and assumes no obligation to correct any errors

contained herein or to advise any user of this document of any correction if such be made. LSC recommends its customers

obtain the latest version of the relevant information to establish, before ordering, that the information being relied upon is

current.

LSC warrants performance of its products to current and applicable specifications in accordance with LSCs standard

warranty. Testing and other quality control procedures are performed to the extent LSC deems necessary. Specific testing of

all parameters of each product is not necessarily performed, unless mandated by government requirements.

LSC assumes no liability for applications assistance, customers product design, software performance, or infringements of

patents or services arising from the use of the products and services described herein.

LSC products are not authorized for use in life-support applications, devices or systems. Inclusion of LSC products in such

applications is prohibited.

LATTICE SEMICONDUCTOR CORPORATION

5555 Northeast Moore Court

Hillsboro, Oregon 97124 U.S.A.

Tel.: (503) 681-0118

FAX: (503) 681-3037

http://www.latticesemi.com

November 1996

Das könnte Ihnen auch gefallen

- GAL16V8: Features Functional Block DiagramDokument23 SeitenGAL16V8: Features Functional Block DiagramWilmar Diaz RodriguezNoch keine Bewertungen

- Intro GalDokument15 SeitenIntro GalFilozófus ÖnjelöltNoch keine Bewertungen

- GAL16V8: Features Functional Block DiagramDokument22 SeitenGAL16V8: Features Functional Block DiagramLharchichi AnissNoch keine Bewertungen

- GAL16V8: Features Functional Block DiagramDokument22 SeitenGAL16V8: Features Functional Block Diagramsgio_4Noch keine Bewertungen

- DSDokument23 SeitenDSGuillermo JiménezNoch keine Bewertungen

- Data Sheet VBDokument23 SeitenData Sheet VBVicky AchmadNoch keine Bewertungen

- Hoja de Datos Gal22v10 PDFDokument27 SeitenHoja de Datos Gal22v10 PDFCadHomeNoch keine Bewertungen

- DataSheet 16v8Dokument23 SeitenDataSheet 16v8Sergio Alberto Olivas LoredoNoch keine Bewertungen

- GAL20V8Dokument27 SeitenGAL20V8Ivan Perez ONoch keine Bewertungen

- All Devices Discontinued!: GAL 22V10 Device DatasheetDokument23 SeitenAll Devices Discontinued!: GAL 22V10 Device DatasheetDavid CruzNoch keine Bewertungen

- GAL16LV8: Features Functional Block DiagramDokument22 SeitenGAL16LV8: Features Functional Block Diagramjoaobatistasilva45Noch keine Bewertungen

- Pal 22 V 10Dokument20 SeitenPal 22 V 10mawaisehsan100% (1)

- PLDTUTORDokument13 SeitenPLDTUTORAjay Nath S ANoch keine Bewertungen

- P 22 V 10Dokument34 SeitenP 22 V 10roozbehxoxNoch keine Bewertungen

- Pca9536 Pca9554 Pca9554a Pca9555Dokument2 SeitenPca9536 Pca9554 Pca9554a Pca9555YuvarajaNoch keine Bewertungen

- Peel 20V8 - 15/-25 CMOS Programmable Electrically Erasable Logic DeviceDokument10 SeitenPeel 20V8 - 15/-25 CMOS Programmable Electrically Erasable Logic Devicenadeem hameedNoch keine Bewertungen

- PAL16R8 Family 20-Pin TTL Programmable Array LogicDokument33 SeitenPAL16R8 Family 20-Pin TTL Programmable Array LogicsolomonicbdmNoch keine Bewertungen

- Use Gal Devices For New Designs: PALCE16V8 and PALCE16V8Z FamiliesDokument32 SeitenUse Gal Devices For New Designs: PALCE16V8 and PALCE16V8Z FamiliesGeorge SimmonsNoch keine Bewertungen

- Xilinx XC2C128-6VQG100C - 5G Technology - Cloud ComputingDokument4 SeitenXilinx XC2C128-6VQG100C - 5G Technology - Cloud ComputingjackNoch keine Bewertungen

- PeelDokument4 SeitenPeelSaurabh Bansal100% (1)

- GAL Databook 1991 PDFDokument251 SeitenGAL Databook 1991 PDFbkaplan452Noch keine Bewertungen

- Ispmach 4000V/B/C/Z Family: FeaturesDokument74 SeitenIspmach 4000V/B/C/Z Family: Featurescatsoithahuong84Noch keine Bewertungen

- PALCE16V8H 15 AdvancedMicroDevicesDokument54 SeitenPALCE16V8H 15 AdvancedMicroDevicesMelek yılmazNoch keine Bewertungen

- 80 C 535Dokument56 Seiten80 C 535MÜhammadFIkriNoch keine Bewertungen

- XC9500Dokument17 SeitenXC9500Anonymous xTGQYFrNoch keine Bewertungen

- MORE PLC APPLICATIONS in TRAFFIC SIGNAL OPERATIONSDokument9 SeitenMORE PLC APPLICATIONS in TRAFFIC SIGNAL OPERATIONSapi-3770306100% (3)

- Assignment - Muhammad Ali Asad - 014Dokument39 SeitenAssignment - Muhammad Ali Asad - 014mumtazNoch keine Bewertungen

- Modulo TSXDokument19 SeitenModulo TSXRonald Victor Galarza Hermitaño100% (1)

- Xilinx XC2C128-7VQG100C - 5G Technology - Wireless TechnologyDokument5 SeitenXilinx XC2C128-7VQG100C - 5G Technology - Wireless TechnologyjackNoch keine Bewertungen

- Pal22V10 Family, Ampal22V10/A: Advanced Micro Devices 24-Pin TTL Versatile Pal DeviceDokument20 SeitenPal22V10 Family, Ampal22V10/A: Advanced Micro Devices 24-Pin TTL Versatile Pal Deviceha-manNoch keine Bewertungen

- Xilinx XC2C256-7VQG100I - Medical Equipment - Industrial ControlDokument5 SeitenXilinx XC2C256-7VQG100I - Medical Equipment - Industrial ControljackNoch keine Bewertungen

- Xilinx XC2C128-7VQG100I - Medical Equipment - 5G TechnologyDokument4 SeitenXilinx XC2C128-7VQG100I - Medical Equipment - 5G TechnologyjackNoch keine Bewertungen

- Flash-Erasable Reprogrammable Cmos Pal Device: Use Ultra37000™ For All New DesignsDokument13 SeitenFlash-Erasable Reprogrammable Cmos Pal Device: Use Ultra37000™ For All New DesignsUlises RojasNoch keine Bewertungen

- Xilinx XC2C256-7VQ100I - Consumer Electronics - Wireless TechnologyDokument5 SeitenXilinx XC2C256-7VQ100I - Consumer Electronics - Wireless TechnologyjackNoch keine Bewertungen

- 18CV8 EtcDokument10 Seiten18CV8 EtcAdriancito ZavalaNoch keine Bewertungen

- Isplsi 1024ea: In-System Programmable High Density PLDDokument14 SeitenIsplsi 1024ea: In-System Programmable High Density PLDCristiano BruschiniNoch keine Bewertungen

- Xilinx XC2C128-7VQ100C - Artificial Intelligence - Cloud ComputingDokument4 SeitenXilinx XC2C128-7VQ100C - Artificial Intelligence - Cloud ComputingjackNoch keine Bewertungen

- DGPMANDokument168 SeitenDGPMANnabil160874Noch keine Bewertungen

- Palce 16 V 8Dokument12 SeitenPalce 16 V 81webdomainNoch keine Bewertungen

- Cypress CPLDDokument65 SeitenCypress CPLDavireddy1Noch keine Bewertungen

- Ee128 Lecture9Dokument22 SeitenEe128 Lecture9KarthikeyanNoch keine Bewertungen

- XC9500 In-System Programmable CPLD Family: Product SpecificationDokument16 SeitenXC9500 In-System Programmable CPLD Family: Product SpecificationMohamed MohNoch keine Bewertungen

- Xilinx XC2C256-6VQ100C - 5G Technology - Wireless TechnologyDokument5 SeitenXilinx XC2C256-6VQ100C - 5G Technology - Wireless TechnologyjackNoch keine Bewertungen

- PLD Architectures and TestingDokument37 SeitenPLD Architectures and TestingParesh SawantNoch keine Bewertungen

- Anachip 18CV8P 25 DatasheetDokument11 SeitenAnachip 18CV8P 25 DatasheetMarcelo PerezNoch keine Bewertungen

- Data Sheet: CAN Serial Linked I/O Device (SLIO) With Digital and Analog Port FunctionsDokument36 SeitenData Sheet: CAN Serial Linked I/O Device (SLIO) With Digital and Analog Port FunctionsalexNoch keine Bewertungen

- 8255 ReportDokument12 Seiten8255 Reportapi-26100966Noch keine Bewertungen

- Xilinx XC2C256-6FT256C - Consumer Electronics - Medical EquipmentDokument5 SeitenXilinx XC2C256-6FT256C - Consumer Electronics - Medical EquipmentjackNoch keine Bewertungen

- 22cv10a Peel LogicDokument11 Seiten22cv10a Peel LogicnevdullNoch keine Bewertungen

- All About PEELDokument10 SeitenAll About PEELRizwanNoch keine Bewertungen

- GE Fanuc Quick Panel Datashee-649204568tDokument4 SeitenGE Fanuc Quick Panel Datashee-649204568tDavid AldanaNoch keine Bewertungen

- Freescale's S08 Ultra-Low-Power MCU With LCD DriverDokument6 SeitenFreescale's S08 Ultra-Low-Power MCU With LCD DriverIonela100% (1)

- Realtek Single Chip Fast Ethernet Controller With Power Management RTL8139C (L)Dokument60 SeitenRealtek Single Chip Fast Ethernet Controller With Power Management RTL8139C (L)vinh_electronicsNoch keine Bewertungen

- Basic PLCDokument32 SeitenBasic PLCRizwanhussain RazviNoch keine Bewertungen

- Zibani - PLD NotesDokument5 SeitenZibani - PLD NotesIshmael ZibaniNoch keine Bewertungen

- Infineon C165 DS v02 - 00 en PDFDokument77 SeitenInfineon C165 DS v02 - 00 en PDFRomi KabelNoch keine Bewertungen

- PLC Programming Using RSLogix 500 & Industrial Applications: Learn ladder logic step by step with real-world applicationsVon EverandPLC Programming Using RSLogix 500 & Industrial Applications: Learn ladder logic step by step with real-world applicationsBewertung: 5 von 5 Sternen5/5 (1)

- Anais Do Workshop De Micro-ondasVon EverandAnais Do Workshop De Micro-ondasNoch keine Bewertungen

- Gammascout Datasheet May2011Dokument1 SeiteGammascout Datasheet May2011hansolosnahNoch keine Bewertungen

- ThinkPad T430s PDFDokument15 SeitenThinkPad T430s PDFSepaleng BaeNoch keine Bewertungen

- ThinkPad T430Dokument19 SeitenThinkPad T430Alexjohn2009Noch keine Bewertungen

- Workstation Precision m6400 Technicke Specifikace enDokument2 SeitenWorkstation Precision m6400 Technicke Specifikace enModesteNoch keine Bewertungen

- Programming in MathrmaticaDokument15 SeitenProgramming in MathrmaticahansolosnahNoch keine Bewertungen

- Arduino Fungsi SyntaxDokument36 SeitenArduino Fungsi Syntaxmul21Noch keine Bewertungen

- Functional Programming in MathematicaDokument39 SeitenFunctional Programming in Mathematicahansolosnah100% (1)

- Algebraic Programming Mathematica (Paper)Dokument13 SeitenAlgebraic Programming Mathematica (Paper)carmo-netoNoch keine Bewertungen

- The Zx97 ComputerDokument13 SeitenThe Zx97 ComputerhansolosnahNoch keine Bewertungen

- RS232 CommunicationDokument30 SeitenRS232 CommunicationhansolosnahNoch keine Bewertungen

- Gal PDFDokument15 SeitenGal PDFhansolosnahNoch keine Bewertungen

- Zenith PDFDokument9 SeitenZenith PDFhansolosnahNoch keine Bewertungen

- Making Moldings With Hollows and Rounds (And A Few Other Planes)Dokument4 SeitenMaking Moldings With Hollows and Rounds (And A Few Other Planes)hansolosnahNoch keine Bewertungen

- An Enhanced RFID-Based Authentication Protocol Using PUF For Vehicular Cloud ComputingDokument18 SeitenAn Enhanced RFID-Based Authentication Protocol Using PUF For Vehicular Cloud Computing0dayNoch keine Bewertungen

- Th-Sunday Magazine 6 - 2Dokument8 SeitenTh-Sunday Magazine 6 - 2NianotinoNoch keine Bewertungen

- Epson EcoTank ITS Printer L4150 DatasheetDokument2 SeitenEpson EcoTank ITS Printer L4150 DatasheetWebAntics.com Online Shopping StoreNoch keine Bewertungen

- Nursing Care Plan For AIDS HIVDokument3 SeitenNursing Care Plan For AIDS HIVFARAH MAE MEDINA100% (2)

- Limited Alembic: Employee Related DataDokument4 SeitenLimited Alembic: Employee Related DataTp EarningsNoch keine Bewertungen

- Curry PowderDokument8 SeitenCurry PowderMahendar Vanam100% (1)

- Probset 3 KeyDokument7 SeitenProbset 3 KeyhoneyschuNoch keine Bewertungen

- Substitution Reactions - PMDokument64 SeitenSubstitution Reactions - PMprasoon jhaNoch keine Bewertungen

- EVS (Yuva)Dokument88 SeitenEVS (Yuva)dasbaldev73Noch keine Bewertungen

- Pathophysiology: DR - Wasfi Dhahir Abid AliDokument9 SeitenPathophysiology: DR - Wasfi Dhahir Abid AliSheryl Ann PedinesNoch keine Bewertungen

- Chapter 4 PDFDokument26 SeitenChapter 4 PDFMeloy ApiladoNoch keine Bewertungen

- The Politics of GenreDokument21 SeitenThe Politics of GenreArunabha ChaudhuriNoch keine Bewertungen

- English 9 Week 5 Q4Dokument4 SeitenEnglish 9 Week 5 Q4Angel EjeNoch keine Bewertungen

- Centric WhitepaperDokument25 SeitenCentric WhitepaperFadhil ArsadNoch keine Bewertungen

- Jmac TempDokument5 SeitenJmac TempDan GerNoch keine Bewertungen

- Tablet Time - Student GuideDokument5 SeitenTablet Time - Student GuideAyesha BaigNoch keine Bewertungen

- Topic - Temperature SensorDokument9 SeitenTopic - Temperature SensorSaloni ChaudharyNoch keine Bewertungen

- MICRF230Dokument20 SeitenMICRF230Amador Garcia IIINoch keine Bewertungen

- Title - Dating Virtual To Coffee Table Keywords - Dating, Application BlogDokument3 SeitenTitle - Dating Virtual To Coffee Table Keywords - Dating, Application BlogRajni DhimanNoch keine Bewertungen

- Operator Training ManualDokument195 SeitenOperator Training ManualIgnacio MuñozNoch keine Bewertungen

- Subtotal Gastrectomy For Gastric CancerDokument15 SeitenSubtotal Gastrectomy For Gastric CancerRUBEN DARIO AGRESOTTNoch keine Bewertungen

- RL78 L1B UsermanualDokument1.062 SeitenRL78 L1B UsermanualHANUMANTHA RAO GORAKANoch keine Bewertungen

- Development and Growth of Teeth: Dr. Madhusudhan ReddyDokument48 SeitenDevelopment and Growth of Teeth: Dr. Madhusudhan ReddysiyaNoch keine Bewertungen

- Industrial Automation Using PLCDokument29 SeitenIndustrial Automation Using PLCAditya JagannathanNoch keine Bewertungen

- STIHL TS410, TS420 Spare PartsDokument11 SeitenSTIHL TS410, TS420 Spare PartsMarinko PetrovićNoch keine Bewertungen

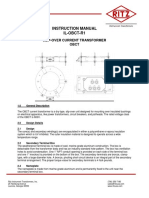

- Instruction Manual Il-Obct-R1: Slip-Over Current Transformer ObctDokument2 SeitenInstruction Manual Il-Obct-R1: Slip-Over Current Transformer Obctبوحميدة كمالNoch keine Bewertungen

- Project 2 Analysis of Florida WaterDokument8 SeitenProject 2 Analysis of Florida WaterBeau Beauchamp100% (1)

- An Overview of Marketing - Week 1Dokument7 SeitenAn Overview of Marketing - Week 1Jowjie TVNoch keine Bewertungen

- LANY Lyrics: "Thru These Tears" LyricsDokument2 SeitenLANY Lyrics: "Thru These Tears" LyricsAnneNoch keine Bewertungen

- Guide For Sustainable Design of NEOM CityDokument76 SeitenGuide For Sustainable Design of NEOM Cityxiaowei tuNoch keine Bewertungen