Beruflich Dokumente

Kultur Dokumente

Gate-Induced Barrier Field Effect Transistor (GBFET) - A New Thin Film Transistor For Active Matrix Liquid Crystal Display Systems

Hochgeladen von

Mamidala Jagadesh KumarOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Gate-Induced Barrier Field Effect Transistor (GBFET) - A New Thin Film Transistor For Active Matrix Liquid Crystal Display Systems

Hochgeladen von

Mamidala Jagadesh KumarCopyright:

Verfügbare Formate

Gate-induced Barrier Field Effect Transistor (GBFET) – A New Thin Film

Transistor for Active Matrix Liquid Crystal Display Systems

M. Jagadesh Kumar1 and Ali A. Orouji2

1

Department of Electrical Engineering, Indian Institute of Technology, New Delhi 110016, India

2

Department of Electrical Engineering, Semnan University, Semnan, Iran

E-mail: mamidala@ieee.org aliorouji@ee.iitd.ac.in

Abstract leakage current of the poly-Si TFTs is very critical. A

number of device structures have been reported in

Using two-dimensional simulation, we report a new literature to circumvent the undesirable leakage current

Gate-induced Barrier Field Effect Transistor (GBFET) in poly-Si TFTs [4-8]. One of the useful techniques is

which exhibits at least three orders of magnitude less to reduce the number of grains in the channel using

OFF state leakage current when compared to a excimer laser annealing [4,5]. Since the grain size

conventional poly-Si TFT. We demonstrate that the increases and the number of grain boundaries

GBFET is completely free of pseudo-subthreshold decreases with annealing, the carrier mobility increases

conduction making it a very attractive device for active improving the device switching characteristics.

matrix liquid crystal display systems. However, all these novel structures are still based on

polysilicon in which the channel conduction is due to

the control of the grain boundary potential barrier in

1. Introduction the channel by the applied gate voltage.

For high-speed low power display applications, it is

Polycrystalline thin film transistors (TFTs) are very critical to reduce the OFF state leakage current of

extensively used in active matrix liquid crystal displays the TFTs. In conventional poly-Si TFTs, the potential

(AMLCDs) [1] because polysilicon can be easily barrier around the grain boundaries in the undoped

deposited on large area substrates using low channel controls the channel conduction. However,

temperature chemical vapor deposition methods. grain boundaries are also the reason for causing the

Unlike in the case of amorphous silicon with low field- pseudo-subthreshold conduction resulting in a large

effect mobility, poly-Si TFTs due to their larger carrier OFF state leakage current. An ideal TFT, therefore,

mobility can be easily incorporated in the driving should have no grain boundaries. The absence of grain

circuitry on the same substrate used for AMLCDs boundaries will cause the grain-boundary potential

resulting in a drastic reduction in the assembly barriers to disappear and the TFT becomes

complexity, cost and size of the display [1]. It is also uncontrollable. In this paper, we demonstrate that even

important to build polysilicon TFTs with channel if the entire polysilicon film is converted into single

lengths less than 1 micron for high density, high crystal silicon using, for example, pulsed wave laser

resolution AMLCDs [2,3]. annealing, we can still induce large potential barriers

In polycrystalline silicon thin film transistors, grain in the channel using a modified gate consisting of two

boundaries and intragranular defects play a major role p+ poly side gates and one n+poly main gate. Using

in degrading the carrier transport and influencing the two-dimensional simulation, we show that the

poly-Si TFT characteristics. Compared to the proposed Gate-induced Barrier Field Effect Transistor

MOSFETs fabricated on single crystal silicon, poly-Si (GBFET) will exhibit at least three orders of

TFTs exhibit poor device characteristics in terms of magnitude less OFF state leakage current when

threshold voltage, subthreshold swing, leakage current, compared to a conventional poly-Si TFT. We

mobility and transconductance. The major drawback of demonstrate that the GBFET is completely free of

poly-Si TFTs is their large OFF state leakage current. pseudo-subthreshold conduction making it a very

For applications as pixel switching elements for flat attractive device for active matrix liquid crystal display

panel liquid crystal displays, reducing the OFF state systems.

Proceedings of the 19th International Conference on VLSI Design (VLSID’06)

1063-9667/06 $20.00 © 2006 IEEE

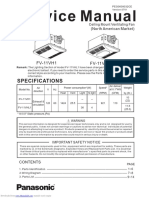

Table 1: Simulation parameters used in MEDICI 2. Effect of grain boundaries

Parameter Value Using excimer laser annealing, it is now possible to

+

Doping of n source/drain 10 cm-3

19 have just one or two grain boundaries in the center of

Trap density at the grain boundary 1013 cm-2 the channel [4,5]. As an example, a conventional poly-

Electron trap energy relative to the 0.51 eV Si TFT (C-TFT) with a single grain boundary in the

conduction band undoped channel is shown Fig. 1(a). The potential

Hole trap energy relative to the 0.51 eV distribution in the channel of the C-TFT, simulated by

valence band us using the two-dimensional simulator MEDICI [9], is

Capture rate for electrons and holes 10-8 cm3/sec shown in Fig. 1(b). The simulation parameters used in

Width of the grain boundary (GB) 10 nm MEDICI are given in Table 1. It clearly shows the

Polysilicon channel layer thickness 50 nm formation of a potential barrier at the grain boundary

due to carrier trapping. The C-TFT can be turned ON

Gate oxide thickness 10 nm

or OFF by controlling the height of the potential

Channel length L 0.4 µm

barrier by applying a gate voltage. Unlike in the case

p+-poly gate work function 5.25 eV of single crystal silicon MOSFETs, channel

n+-poly gate work function 4.17 eV conduction in a poly-Si TFT is not controlled by the

accumulation charge density modulation by the gate.

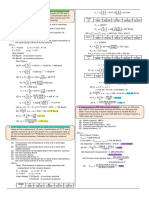

Gate As a result, a pseudo- subthreshold region appears in

the transfer characteristics of the poly-Si TFT resulting

n+ Poly-Si in an unacceptable OFF state leakage current [10].

Source SiO2 Drain Using MEDICI, in order to examine the pseudo-

subthreshold region, we have simulated the transfer

N+ N+ characteristics of a conventional polysilicon TFT (C-

TFT) having a single grain boundary in the center of

Grain Boundary the channel and a conventional single crystal silicon

(a)

SOI MOSFET (C-SOI) whose cross-section and

channel potential distribution are shown in Fig. 2. In

our simulations, for both the structures, we have

chosen identical dopings, silicon film thickness,

Central Barrier channel length, gate oxide thickness and gate work

functions as given in Table 1.

3. Pseudo-subthreshold region

From the transfer characteristics of C-TFT

and C-SOI shown in Fig. 3, the pseudo-subthreshold

region is clearly visible in the polysilicon TFT with a

central grain boundary. However, in the case of C-SOI,

the transfer characteristic is very steep but due to the

undoped channel, its threshold voltage is negative and

the device conducts a large current even at zero gate

voltage. An ideal TFT for AMLCDs application would

(b) have been one with a positive threshold voltage and an

Drain

undoped single crystal silicon channel for achieving

large carrier mobility and steep subthrehold slope. But

Source unfortunately, single crystal silicon cannot be

deposited on large area glass substrates using low

deposition temperatures. However, it has been

Fig. 1 (a) Schematic cross-section of a conventional poly-Si

TFT (C-TFT) with a single grain boundary in the center of recently demonstrated experimentally that using

the undoped channel and (b) The simulated potential continuous wave laser annealing [11], it is possible to

distribution in the channel for VGS = 0 V and VDS = 0 V. convert the entire poly-Si thin film layer into single

crystal silicon even on large area substrates. After

Proceedings of the 19th International Conference on VLSI Design (VLSID’06)

1063-9667/06 $20.00 © 2006 IEEE

Gate annealing, all the grain boundaries in the channel will

disappear as shown in Fig. 2 (a) and there will be no

n+ Poly-Si potential barriers to control the channel conduction as

Source SiO2 Drain shown in Fig. 2 (b). With no grain boundary induced

potential barriers in the channel, the TFT will conduct

N+ Undoped N+ even at zero gate bias. In this paper, using two

dimensional simulation, we demonstrate for the first

time that using gate engineering, one can induce

artificial potential barriers in the single crystal silicon

(a) channel whose height can then controlled by the gate

voltage allowing the TFT to be switched ON and OFF.

4. Gate induced barrier field effect tran-

sistor (GBFET)

The cross-section of the proposed gate induced

barrier field effect transistor (GBFET) is shown in Fig.

4(a). This structure can be fabricated using

conventional poly-Si TFT fabrication procedures.

However, before the source/drain implantation is

carried out, the polysilicon can be converted into

single crystal silicon using continuous wave laser

irradiation [11]. In GBFET, there are two p+

polysilicon side gates (LS) on either side of the n+

(b) polysilicon main gate (LM). Due to the work function

difference between the p+ polysilicon and n+

polysilicon gates, as indicated by MEDICI simulations,

two side potential barriers are induced in the channel

Fig. 2 (a) Schematic cross-section of a single crystal silicon TFT region as shown in Fig. 4(b). In the absence of a gate

(C-SOI) with no grains in the channel and (b) Simulated channel voltage, these large potential barriers, larger and wider

potential distribution for VGS = 0 V and VDS = 0 V.

than the grain boundary induced potential barrier

shown in Fig. 1(b), do not permit any current to flow

from the drain to the source. If a positive gate voltage

is applied, the height of the induced potential barrier

will decrease allowing the current to flow through the

channel.

In other words, the channel conduction is controlled

by the accumulation charge density modulation by

manipulating the gate induced side barriers in the

single crystal silicon channel. However, we need to

examine whether the GBFET will exhibit (i) a positive

threshold voltage and (ii) a pseudo- subthreshold free

transfer characteristic.

In Fig. 5, the simulated transfer characteristics of

the GBFET are compared with that of the conventional

crystalline silicon SOI MOSFET (C-SOI). It is clearly

seen that the GBFET exhibits a steep subthreshold

Fig. 3 Transfer characteristics of a conventional poly-Si slope without any pseudo-subthreshold region. When

TFT (C-TFT) with a single grain boundary in the center compared to the transfer characteristic of the

channel compared with that of a single crystal silicon TFT conventional poly-Si TFT (C-TFT) shown in Fig. 3,

(C-SOI) with no grains. the OFF state leakage current of GBFET is at least few

Proceedings of the 19th International Conference on VLSI Design (VLSID’06)

1063-9667/06 $20.00 © 2006 IEEE

Gate

p+ poly n+ poly p+ poly

Source SiO2 Drain

N+ Undoped N+

(a)

Fig. 6 Simulated potential distribution of GBFET

showing the induced side potential barriers in the

undoped channel for VGS = 0 V and VDS = 1 V.

orders of magnitude smaller. In many techniques

(b) reported in literature, a reduction in the OFF state

leakage current also leads to a reduction in the ON

state current [4-8]. This is detrimental for the device

operation. However, in the GBFET, we observe that

the ON state current is unaffected even while the OFF

state current reduces by three orders of magnitude. The

presence of the gate induced potential barriers in the

Fig. 4 (a) Schematic cross-section of GBFET and (b) Simulated channel also cause the threshold voltage to be positive.

potential distribution showing the induced side potential barriers The simulated potential distribution of the GBFET for

in the undoped channel for VGS = 0 V and VDS = 0 V. VDS = 1 V is shown in Fig. 6. Even in the presence of

increased drain voltage, the side potentials are clearly

present in the channel of the GBFET demonstrating its

improved performance at higher drain voltages.

5. GBFET with single grain boundary

It is also important to see what would be the

transfer characteristic of the proposed GBFET if a

grain boundary is introduced in the middle of the

channel. To investigate this, we have compared in Fig.

7, the transfer characteristic of the GBFET and the

conventional polysilicon TFT both having a single

grain in the channel. It is very clear that if a grain

boundary is present in the channel of the GBFET, the

Fig. 5 Comparison of the transfer characteristics of GBFET transfer characteristic will again show a diminished

with that of a single crystal silicon TFT (C-SOI) with no grains subthreshold slope similar to that of the conventional

in the undoped channel. TFT indicating that the presence of grains in the

5. Simulation results channel is detrimental to the operation of the device.

Proceedings of the 19th International Conference on VLSI Design (VLSID’06)

1063-9667/06 $20.00 © 2006 IEEE

[4] C. W. Lin, C. H. Tseng, T. K. Chang, C. W. Lin, W. T.

Wang, and H. C. Cheng, “A novel laser-processed self-

aligned gate-overlapped LDD poly-Si TFT,” IEEE Electron

Device Lett. Vol. 23, pp. 133-135, 2002.

[5] H. J. Kim and J. S. Im, “New excimer-laser-

crystallization method for producing large-grained and grain

boundary-location-controlled Si films for thin film

transistors,” Appl. Phys. Lett. vol. 68, pp. 1513-1515, 1996.

[6] K. Tanaka, H. Arai, and S. Kohda, “Characteristics of

offset-structure polycrystalline-silicon thin-film transistors,”

IEEE Electron Device Lett. Vol. 9, pp. 23-25, 1988.

[7] K. W. Kim, K. S. Cho, and J. Jang, “Performance

improvement of polycrystalline thin-film transistor by

adopting a very thin amorphous silicon buffer,” J. Non-Cryst.

Sol., Vol. 266-269, pp. 1265-1269, 2000.

Fig. 7 Comparison of the transfer characteristics of

GBFET and a conventional polysilicon TFT both having [8] J.-H. Jeon, M.-C. Lee, K.-C. Park, and M.-K. Han, “A

a single grain boundary in the middle of the channel. The new polycrystalline silicon TFT with a single grain boundary

transfer characteristic of a single crystal silicon TFT (C- in the channel,” IEEE Electron Device Lett., vol.22, pp. 429-

SOI) with no grains in the undoped channel is also 431, 2001.

shown.

[9] MEDICI 4.0, Technology Modeling Associates, Palo

Alto, CA, 1997.

6. Conclusions

[10] T.-S. Li and P.-S. Lin, “On the pseudo-subthreshold

In conclusion, using two-dimensional simulation, we characteristics of polycrystalline-silicon thin-film transistors

have reported for the first time, a new gate-induced with large grain size,” IEEE Electron Device Lett., vol. 14,

barrier field effect transistor (GBFET) whose leakage pp. 240-242, 1993.

current is several orders of magnitude smaller than that

of the conventional polysilicon TFTs and the proposed [11] A. Hara, K. Yoshino, F. Takeuchi and N. Sasaki,

“Selective Single-Crystalline-Silicon Growth at the Pre-

device is completely devoid of the pseudo-

defined Active Region of a Thin Film Transistor on Glass by

subthreshold region. The GBFET, with its ideal Using Continuous Wave Laser Irradiation,” Jpn. J. Appl.

characteristics is a perfect candidate in many Phys. Vol. 42, pp.23-27, 2003.

applications such as active matrix liquid crystal

displays (AMLCDs), random access memories, read [12] T. Yamanaka et al., “Advanced TFT SRAM cell

only memories, linear image sensors, thermal printer technology using a phase-shift lithography,” IEEE Trans.

heads and photodetector amplifiers [12-15]. Electron Devices, vol. 42, pp. 1305-1313, 1995.

[13] S. Koyama, “A novel cell structure for giga-bit

7. References EPROMs and flash memories using polysilicon thin film

transistors,” Sym. VLSI Technology Digest of Technical

[1] T. Tanaka, H. Asuma, K. Ogawa, Y. Shinagawa, and N. Papers, pp. 44-45, 1992.

Konishi, “An LCD addressed by a-Si:H TFTs with peripheral

poly-Si TFT circuits,” IEDM Tech. Dig., pp. 389-392, 1993. [14] Y. Hayashi, H. Hayashi, M. Negishi, and T. Matsushita,

“A thermal printer head with CMOS thin-film transistors and

[2] T. Zhao, M. Cao, K. C. Saraswat, and J. D. Plummer, “A heating elements integrated on a chip,” IEEE Solid-State

vertical submicron polysilicon thin-film transistor using a Circuits Conference (ISSCC), p. 266, 1998.

low temperature process,” IEEE Electron Device Lett. Vol.

15, pp. 415-417, 1994. [15] A. A. Orouji and M. J. Kumar, "A New Poly-Si Triple-

Gate Thin Film Transistor (TG-TFT) with Diminished

[3] P. M. Walker, H. Mizuta, S. Uno, Y. Furuta and D. G. Pseudo-Subthreshold Region: Theoretical Investigation and

Hasko, “Improved off-current and subthreshold slope in Analysis," IEEE Trans. Electron Devices, Vol.52, pp.1815-

aggressively scaled poly-Si TFTs with a single grain 1820, Aug.2005.

boundary in the channel,” IEEE Trans. Electron Devices,

vol.51, pp. 212-219, 2004.

Proceedings of the 19th International Conference on VLSI Design (VLSID’06)

1063-9667/06 $20.00 © 2006 IEEE

Das könnte Ihnen auch gefallen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Label Free BiosensorDokument6 SeitenLabel Free BiosensorMamidala Jagadesh KumarNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Impact of Gate Leakage Considerations in Tunnel Field Effect Transistor DesignDokument21 SeitenImpact of Gate Leakage Considerations in Tunnel Field Effect Transistor DesignMamidala Jagadesh KumarNoch keine Bewertungen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- How Does The Power of "Suggestion" Influence Students' Performance?"Dokument8 SeitenHow Does The Power of "Suggestion" Influence Students' Performance?"Mamidala Jagadesh KumarNoch keine Bewertungen

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Quantum Computing in India: An Opportunity That Should Not Be MissedDokument3 SeitenQuantum Computing in India: An Opportunity That Should Not Be MissedMamidala Jagadesh KumarNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Making Your Research Paper Discoverable: Title Plays The Winning TrickDokument7 SeitenMaking Your Research Paper Discoverable: Title Plays The Winning TrickMamidala Jagadesh KumarNoch keine Bewertungen

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Compact Analytical Model of Dual Material Gate Tunneling Field Effect Transistor Using Interband Tunneling and Channel TransportDokument6 SeitenCompact Analytical Model of Dual Material Gate Tunneling Field Effect Transistor Using Interband Tunneling and Channel TransportMamidala Jagadesh KumarNoch keine Bewertungen

- Dielectric-Modulated Impact-Ionization MOS (DIMOS) Transistor As A Label-Free BiosensorDokument3 SeitenDielectric-Modulated Impact-Ionization MOS (DIMOS) Transistor As A Label-Free BiosensorMamidala Jagadesh KumarNoch keine Bewertungen

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- An Academician's Reminiscences On Giving Interesting and Effective Public LecturesDokument3 SeitenAn Academician's Reminiscences On Giving Interesting and Effective Public LecturesMamidala Jagadesh KumarNoch keine Bewertungen

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Doping-Less Tunnel Field Effect Transistor: Design and InvestigationDokument6 SeitenDoping-Less Tunnel Field Effect Transistor: Design and InvestigationMamidala Jagadesh KumarNoch keine Bewertungen

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- "Schottky Collector Bipolar Transistor Without Impurity Doped Emitter and Base: Design and PerformanceDokument3 Seiten"Schottky Collector Bipolar Transistor Without Impurity Doped Emitter and Base: Design and PerformanceMamidala Jagadesh KumarNoch keine Bewertungen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Malady of Technology in Our Lives: Is Anyone ListeningDokument3 SeitenThe Malady of Technology in Our Lives: Is Anyone ListeningMamidala Jagadesh KumarNoch keine Bewertungen

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- InGaAs LDMOS Power TransistorsDokument13 SeitenInGaAs LDMOS Power TransistorsMamidala Jagadesh KumarNoch keine Bewertungen

- Back To Basics: Why Every Student and Professor Should Ride A Bicycle On A University Campus?Dokument6 SeitenBack To Basics: Why Every Student and Professor Should Ride A Bicycle On A University Campus?Mamidala Jagadesh KumarNoch keine Bewertungen

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Bipolar Charge-Plasma Transistor: A Novel Three Terminal DeviceDokument6 SeitenBipolar Charge-Plasma Transistor: A Novel Three Terminal DeviceMamidala Jagadesh KumarNoch keine Bewertungen

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Sharing of Best Practices or Plagiarism?Dokument2 SeitenSharing of Best Practices or Plagiarism?Mamidala Jagadesh KumarNoch keine Bewertungen

- Reflections On Teaching A Large ClassDokument6 SeitenReflections On Teaching A Large ClassMamidala Jagadesh KumarNoch keine Bewertungen

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Can A Bipolar Junction Transistor Be Made Without Doping?Dokument1 SeiteCan A Bipolar Junction Transistor Be Made Without Doping?Mamidala Jagadesh KumarNoch keine Bewertungen

- Novel Attributes of A Dual Material Gate Nanoscale Tunnel Field Effect TransistorDokument27 SeitenNovel Attributes of A Dual Material Gate Nanoscale Tunnel Field Effect TransistorMamidala Jagadesh KumarNoch keine Bewertungen

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Bipolar Charge Plasma Transistor: A Novel Three Terminal DeviceDokument7 SeitenBipolar Charge Plasma Transistor: A Novel Three Terminal DeviceMamidala Jagadesh KumarNoch keine Bewertungen

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Compact Modeling of Partially Depleted Silicon-on-Insulator Drain-Extended MOSFET (DEMOS) Including High-Voltage and Floating Body EffectsDokument11 SeitenCompact Modeling of Partially Depleted Silicon-on-Insulator Drain-Extended MOSFET (DEMOS) Including High-Voltage and Floating Body EffectsMamidala Jagadesh KumarNoch keine Bewertungen

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Approaches To Nanoscale MOSFET Compact Modeling Using Surface Potential Based ModelsDokument6 SeitenApproaches To Nanoscale MOSFET Compact Modeling Using Surface Potential Based ModelsMamidala Jagadesh KumarNoch keine Bewertungen

- Electrochemical Doulbe-Layer Capacitors Featuring Carbon NanotubesDokument10 SeitenElectrochemical Doulbe-Layer Capacitors Featuring Carbon NanotubesMamidala Jagadesh KumarNoch keine Bewertungen

- Analytical Drain Current Model of Nanoscale Strained-Si/SiGe MOSFETs For Circuit SimulationDokument6 SeitenAnalytical Drain Current Model of Nanoscale Strained-Si/SiGe MOSFETs For Circuit SimulationMamidala Jagadesh KumarNoch keine Bewertungen

- Estimation and Compensation of Process Induced Variations in Nanoscale Tunnel Field Effect Transistors (TFETs) For Improved ReliabilityDokument22 SeitenEstimation and Compensation of Process Induced Variations in Nanoscale Tunnel Field Effect Transistors (TFETs) For Improved ReliabilityMamidala Jagadesh KumarNoch keine Bewertungen

- IETE Technical Review March 2010 IssueDokument2 SeitenIETE Technical Review March 2010 IssueMamidala Jagadesh KumarNoch keine Bewertungen

- A New SiC-emitter Lateral NPM Schottky Collector Bipolar Transistor On SOI For VLSI ApplicationsDokument8 SeitenA New SiC-emitter Lateral NPM Schottky Collector Bipolar Transistor On SOI For VLSI ApplicationsMamidala Jagadesh KumarNoch keine Bewertungen

- New Silicon Carbide (SiC) Hetero-Junction Darlington TransistorDokument3 SeitenNew Silicon Carbide (SiC) Hetero-Junction Darlington TransistorMamidala Jagadesh KumarNoch keine Bewertungen

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (120)

- Schottky-Gate Effect Transistor Without Junction: New Silicon Carbide Bipolar Mode FieldDokument3 SeitenSchottky-Gate Effect Transistor Without Junction: New Silicon Carbide Bipolar Mode FieldMamidala Jagadesh KumarNoch keine Bewertungen

- A High Current Gain Horizontal Current Bipolar Transistor (HCBT) Technology For The BiCMOS Integration With FinFETsDokument4 SeitenA High Current Gain Horizontal Current Bipolar Transistor (HCBT) Technology For The BiCMOS Integration With FinFETsMamidala Jagadesh KumarNoch keine Bewertungen

- Example2 Two Equal Spans Option1 FinalDokument94 SeitenExample2 Two Equal Spans Option1 FinalTakács AttilaNoch keine Bewertungen

- A Brief History of Turbine-Driven GeneratorsDokument15 SeitenA Brief History of Turbine-Driven GeneratorsGilbert PinedaNoch keine Bewertungen

- Data Sheets - Closed Circuit Television System For Lewpp-3ProjectDokument21 SeitenData Sheets - Closed Circuit Television System For Lewpp-3ProjectCaptainNoch keine Bewertungen

- Cepe BomDokument8 SeitenCepe BomRomeo AtienzaNoch keine Bewertungen

- Fmindds3 InstructionsDokument8 SeitenFmindds3 InstructionsAnonymous ttDqU6zNoch keine Bewertungen

- 0 - College Status Report Volume I Mar 2016Dokument84 Seiten0 - College Status Report Volume I Mar 2016Hossam Eldin TalaatNoch keine Bewertungen

- Quality ManualDokument30 SeitenQuality ManualCarl WilliamsNoch keine Bewertungen

- Manual de Compressores Por Modelos para Compras (Bendix)Dokument14 SeitenManual de Compressores Por Modelos para Compras (Bendix)Luis Emilio Santana DiazNoch keine Bewertungen

- Net CrackerDokument10 SeitenNet Crackermr1977Noch keine Bewertungen

- tc80-120 Brochure 10-19 WebDokument2 Seitentc80-120 Brochure 10-19 Webvitor rodriguesNoch keine Bewertungen

- Interbond 600 PDFDokument4 SeitenInterbond 600 PDFTrịnh Minh KhoaNoch keine Bewertungen

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- DE08 Engine ManualDokument80 SeitenDE08 Engine ManualRonaldi motter100% (6)

- Insualtion ClassDokument10 SeitenInsualtion ClassgoyalmanojNoch keine Bewertungen

- Design and Construction of A Manipulator Type ScaraDokument9 SeitenDesign and Construction of A Manipulator Type ScaraHari Kirupakar100% (1)

- SOAL LATIHAN-1 - Spring Loaded Safety ValveDokument3 SeitenSOAL LATIHAN-1 - Spring Loaded Safety ValveRahmat AgungNoch keine Bewertungen

- Brosur Penangkal Petir LPI GuardianDokument6 SeitenBrosur Penangkal Petir LPI GuardianKoen Arifvanda Prayoga100% (1)

- CTC TransformerDokument14 SeitenCTC Transformerkunjan2165Noch keine Bewertungen

- Brocade PurseDokument5 SeitenBrocade PursemachimayzNoch keine Bewertungen

- Zoning and Designing For Affordability Using Modular Housing PDFDokument123 SeitenZoning and Designing For Affordability Using Modular Housing PDFJuhi ParyaniNoch keine Bewertungen

- A&S: Nov/Dec 10Dokument68 SeitenA&S: Nov/Dec 10promechmagsNoch keine Bewertungen

- Panasonic Bathroom Fan Heater Combo Service ManualDokument15 SeitenPanasonic Bathroom Fan Heater Combo Service ManualddNoch keine Bewertungen

- Double Walled Storage TankDokument4 SeitenDouble Walled Storage Tankrkgt67% (3)

- Kyoritsu Insulation TesterDokument3 SeitenKyoritsu Insulation Testeranon_702895956Noch keine Bewertungen

- SR Piping Designer/checkerDokument4 SeitenSR Piping Designer/checkerapi-78715367Noch keine Bewertungen

- Membrane LG BW 4040RDokument1 SeiteMembrane LG BW 4040RPT Deltapuro Indonesia100% (1)

- HEMM Drill02Dokument644 SeitenHEMM Drill02miningnova2Noch keine Bewertungen

- Introduction To Internal Combustion EnginesDokument19 SeitenIntroduction To Internal Combustion EnginesAkhilesh ChoudharyNoch keine Bewertungen

- SMC/TSMC 100 MK 4 LL Reciprocating Compressor Units: Spare Parts ManualDokument58 SeitenSMC/TSMC 100 MK 4 LL Reciprocating Compressor Units: Spare Parts ManualHamza HafidiNoch keine Bewertungen

- USA Gas Cycles Diesel DualDokument4 SeitenUSA Gas Cycles Diesel DualRaymartNoch keine Bewertungen

- CamDokument52 SeitenCamGaurav DabhekarNoch keine Bewertungen

- RV Living Collection: RV living for beginners, RV travel for the whole family, RV repair and RV mobile solar power: Experience Freedom on the roads alone or with your family with this collection. Learn how to repair your motorhome while using renewable energy!Von EverandRV Living Collection: RV living for beginners, RV travel for the whole family, RV repair and RV mobile solar power: Experience Freedom on the roads alone or with your family with this collection. Learn how to repair your motorhome while using renewable energy!Noch keine Bewertungen

- Introduction to Power System ProtectionVon EverandIntroduction to Power System ProtectionBewertung: 5 von 5 Sternen5/5 (1)

- Fire on the Horizon: The Untold Story of the Gulf Oil DisasterVon EverandFire on the Horizon: The Untold Story of the Gulf Oil DisasterNoch keine Bewertungen

- Power of Habit: The Ultimate Guide to Forming Positive Daily Habits, Learn How to Effectively Break Your Bad Habits For Good and Start Creating Good OnesVon EverandPower of Habit: The Ultimate Guide to Forming Positive Daily Habits, Learn How to Effectively Break Your Bad Habits For Good and Start Creating Good OnesBewertung: 4.5 von 5 Sternen4.5/5 (21)

- Shorting the Grid: The Hidden Fragility of Our Electric GridVon EverandShorting the Grid: The Hidden Fragility of Our Electric GridBewertung: 4.5 von 5 Sternen4.5/5 (2)

- The Permaculture City: Regenerative Design for Urban, Suburban, and Town ResilienceVon EverandThe Permaculture City: Regenerative Design for Urban, Suburban, and Town ResilienceNoch keine Bewertungen