Beruflich Dokumente

Kultur Dokumente

Memorias Digitales

Hochgeladen von

Herberth CórdobaOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Memorias Digitales

Hochgeladen von

Herberth CórdobaCopyright:

Verfügbare Formate

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

ELECTRNICA DIGITAL

Tema 13

UNIDADES DE MEMORIA DIGITALES (PARTE 2)

Enrique Mandado Prez

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

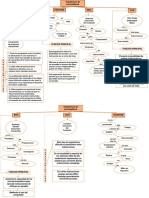

MEMORIAS DE ACCESO DIRECTO Y

ESTRUCTURA INTERNA ALEATORIA

MEMORIAS DE ACCESO ALEATORIO

Voltiles

Activas

Clasificacin

de las

memorias

de acceso

aleatorio

No voltiles

Segn la volatilidad

Pasivas

Escritura y lectura simultneas

Segn la forma de realizar las

operaciones de escritura y lectura

Escritura y lectura no simultneas

Acceso mltiple

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

ACTIVAS (READ/WRITE)

El tiempo que tarda en realizarse una operacin de

escritura y una de lectura es del mismo orden de magnitud.

Pueden ser voltiles o no voltiles.

PASIVAS (READ ONLY)

Tardan mucho ms en ser escritas que en ser ledas. No son

voltiles.

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS ACTIVAS

Se suelen denominar memorias de escritura/lectura

(Read/Write) y se les llama RAM cuando son de escritura y

lectura no simultneas.

Se pueden implementar:

- Con biestables activados por niveles

Se denominan estticas (SRAM)

- Con condensadores

Se denominan dinmicas (DRAM)

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS DE ACCESO ALEATORIO ACTIVAS

DE ESCRITURA Y LECTURA NO SIMULTANEAS (RAM)

Estticas

Asncronas (ASRAM)

Sncronas (SSRAM)

Voltiles

Clasificacin

segn la volatilidad

de las memorias

de acceso aleatorio

activas de escritura y

lectura no simultneas

Asncronas (DRAM)

FPMDRAM

Dinmicas

EDODRAM

Sncronas

BEDODRAM

SDRAM

SLDRAM

RDRAM

NVRAM

No voltiles

FRAM

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS RAM ACTIVAS ESTTICAS DE

ESCRITURA Y LECTURA NO SIMULTNEAS (SRAM)

Se caracterizan porque solo se puede seleccionar en cada

instante una posicin para escribir en ella o leer la

informacin que contiene. Se pueden clasificar en dos

grandes tipos:

- Memorias SRAM asncronas (ASRAM).

- Memorias SRAM sncronas (SSRAM).

Variables

de direccin

Seales

de control

n2

MEMORIA DE

ACCESO ALEATORIO

DE ESCRITURA Y

LECTURA NO

SIMULTNEAS

n1

Entrada/Salida

de informacin

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS RAM ACTIVAS ESTTICAS

DE ESCRITURA Y LECTURA NO SIMULTNEAS (SRAM)

n2

Variables de direccin

WE

Impulso escritura

Desinhibicin escritura/lectura

Desinhibicin de salida

CE

OE

RAM

A n2

2 -1

C

G

&

EN

A

Smbolo lgico de

una memoria SRAM

Terminales de

entrada/salida

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA SRAMt

lectura

Variables de direccin

(Address variables)

Desinhibicin de

escritura/lectura (CE)

(Chip enable)

Cronograma de las seales

de una memoria SRAM

durante un ciclo de lectura

Desinhibicin de

salida (OE)

(Output enable)

Nivel uno

Impulso de escritura (WE)

(Writing pulse)

Nivel cero

Terminales de

entrada/salida

(Input/Output pins)

t desinh. salida

t salida indefinida

t acceso

(Access time)

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

t escritura

MEMORIA SRAM

Variables de direccin

(Address variables)

Cronograma de las seales

de una memoria SRAM

durante un ciclo de escritura

Desinhibicin de

escritura/lectura (CE)

(Chip enable)

Nivel uno

Desinhibicin de

salida (OE)

Nivel cero

(Output enable)

te

(t setup)

tm

(t hold)

Impulso de escritura (WE)

(Writing pulse)

Terminales de

entrada/salida

(Input/Output pins)

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA SRAM

+VDD

T3

T5

T4

CELDA MOS

Q

T1

T6

ESTTICA

T2

I

Lnea de

seleccin

Lnea de

seleccin

Esquema y bloque funcional de una memoria SRAM

de tecnologa MOS de canal N

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

I

MEMORIA SRAM

X/Y

MOS

ESTTICA

X1

A1

X2

X3

CELDA

MOS

ESTTICA

Memoria SRAM de

16x1 posiciones de

organizacin 3D

MOS

ESTTICA

CELDA

MOS

ESTTICA

CELDA

MOS

T7

CELDA

MOS

ESTTICA

ESTTICA

X/Y

CELDA

CELDA

MOS

ESTTICA

CELDA

MOS

ESTTICA

CELDA

MOS

Y1

A3

Y2

Y3

Entrada de

informacin

T7

MOS

CELDA

MOS

ESTTICA

CELDA

MOS

CELDA

MOS

ESTTICA

T8

T7

EN

&

EN

WE

&

EN

Salida de

informacin

CELDA

MOS

ESTTICA

ESTTICA

1

&

OE

ESTTICA

ESTTICA

T8

CELDA

Y0

A2

CE

X0

A0

CELDA

CELDA

MOS

ESTTICA

CELDA

MOS

ESTTICA

T8

T7

T8

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

Variables de

direccin

(A 0 a A (n 2 / 2) 1 )

X/Y

n2/2

MEMORIA SRAM

2n 2 / 2

G

CONJUNTO DE

CE

CELDAS MOS

WE

ESTTICAS Y

OE

AMPLIFICADORES

Variables de

direccin

(A n 2 / 2 a A n 2 1 )

X/Y

n2/2

2n 2 / 2

G

Esquema de bloques de una memoria de acceso aleatorio

esttica de 2n2 posiciones de un bit

Salida de

Informacin

Entrada de

Informacin

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA SRAM

Variables de

direccin

(A 0 a A (n 2 / 2) 1 )

X/Y

n2/2

2n2 / 2

G

CONJUNTO DE

CONJUNTO DE

CE

CELDAS MOS

CELDAS MOS

WE

ESTTICAS Y

ESTTICAS Y

OE

AMPLIFICADORES

AMPLIFICADORES

Variables de

direccin

(A n 2 / 2 a A n 2 1 )

X/Y

n2/2

2n2 / 2

G

Entrada de

Informacin

Salida de

Informacin

Esquema de bloques de una memoria activa de acceso aleatorio esttica

de 2n2 posiciones de dos bits cada una, con organizacin 3D

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA SRAM

Memoria activa esttica

de escritura y lectura

no simultneas

APLICACIONES

Barra de direccin

MICROPROCESADOR

RAM

n1

A

0

n1

2 -1

Seales de control

Barra de datos

Memoria activa de acceso aleatorio esttica

de escritura y lectura no simultneas (SRAM )

utilizada como unidad de memoria de un

procesador digital programable.

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

Registro de

direccin

MEMORIA SSRAM

Reloj del

C1

sistema

Variables

de direccin

n2

1D

n2

Esquema de bloques

CE

de una memoria

de acceso aleatorio

activa esttica sncrona

(SSRAM) de escritura

y lectura no simultneas

(Synchronous SRAM )

Terminales

de entrada

Q

1D

0

2

GENERADOR

DEL IMPULSO

WE

C1

DE ESCRITURA

CE

n2

SRAM

Registro de

salida

-1

EN

C

C1

Registro de

entrada

n1

1A

C1

n1

n1

1D

Q

OE

1D

C1

n1

Terminales

de salida

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA SSRAM

n2

CE

OE

Smbolo lgico

de una memoria

de acceso aleatorio

activa esttica sncrona

(SSRAM) de escritura

y lectura no simultneas

Terminales

de entrada

SSRAM

A n2

2 -1

G

EN

C1

n1

n1

1A

Terminales

de salida

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

n2-3

A3 A 2n 2 1 1

MEMORIA BSSRAM

Esquema de bloques

de una memoria

de acceso aleatorio

activa esttica sncrona

de rfagas (BSSRAM)

de escritura y lectura

no simultneas

A2

Variables

de direccin

n2

=1

A2

=1

A1

=1

A0

A1

A0

Control de

rfagas

CTR

G2

C1,2+

Q0

(Burst Synchronous

SRAM )

Q1

Q2

n2

CE

OE

Reloj del

sistema

Terminales

de entrada

SSRAM

A n02

2 -1

G

EN

C1

n1

n1

1A

Terminales

de salida

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA DE ACCESO ALEATORIO DINMICA

DE LECTURA Y ESCRITURA NO SIMULTNEAS (DRAM)

Decodificador

de filas

X/Y

Lnea de entrada/salida

de informacin

Direccin

de filas

n2/2

Lnea de

seleccin

(Word line)

Lnea de

lectura BL

(Bit line)

Lnea BL

CELDA

T

Lnea de seleccin

C

C BL

C BL

SENSE

AMPLIFIER

Celda de memoria

CIRCUITO

DE

LECTURA

Seal de reescritura

Esquema de bloques del circuito

de lectura y regrabado.

Terminal

de salida

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA DRAM

n2

Direccin o seleccin

de fila (Row)

Direccin o seleccin

de columna (Column)

Seales

de control

n2/2

n2/2

CONJUNTO

DE CELDAS

DINMICAS

Bloque funcional bsico de una memoria de acceso aleatorio dinmica

de escritura y lectura no simultneas (DRAM)

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

Registro de

direccin de filas

MEMORIA DRAM

RAS

Esquema de bloques de una

memoria de acceso aleatorio

dinmica de escritura y lectura

no simultneas con

registros temporales

de memorizacin de la direccin

Variables

de direccin

C1

n2 /2

1D

Registro de direccin

de columnas

CAS

C1

n2/2

n2 /2

n2/2

1D

DE CELDAS

m

CIRCUITO

DE

R/W

CONJUNTO

CONTROL

Seales

de control

DINMICAS

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA DRAM

Variables

de direccin

RAS

CAS

n2 /2

RAM

DINMICA

2 n 2 x n1

n1

n1

R/W

Smbolo lgico de una

memoria de acceso aleatorio

dinmica de escritura y lectura

no simultneas con

registros temporales

de memorizacin de la direccin

A8

D

R/W

RAS

A0

A2

A1

VDD

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

VSS

CAS

Q

A6

A3

A4

A5

A7

Encapsulado de la memoria

DRAM TMS 4256 de 256K1

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA DRAM

Direccin

de fila (Row)

Direccin de

Columna (Column)

Direccin

de fila

Direccin

(Address)

t Ciclo de lectura (t RC)

(t RAS)

RAS

CAS

t RCS

R/W

(t RAC)

Informacin

de salida

Entrada/Salida

Cronograma de las seales de una memoria de acceso aleatorio dinmica

de escritura y lectura no simultneas durante un ciclo de lectura

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA DRAM

Direccin

de fila (Row)

Direccin de

Columna (Column)

Direccin

de fila

Direccin

(Address)

t Ciclo de escritura (t WC)

(t RAS)

RAS

CAS

t RCS

R/W

(t RAC)

Informacin

de entrada

Entrada/Salida

Cronograma de las seales de una memoria de acceso aleatorio dinmica

de escritura y lectura no simultneas durante un ciclo de escritura

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA DRAM

Variables de

direccin

Variables de

direccin

Seales

de control

n2 /2

n2

CONTROLADOR

RAS

DE MEMORIA

CAS

DINMICA

R/W

RAM

DINMICA

2 n 2 x n1

n1

n1

Memoria de acceso aleatorio dinmica de escritura y lectura no simultneas

(DRAM) con circuito controlador de regrabado (Refreshing)

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA DRAM

CAS

CAS

RAS

CTR

R

Esquema de bloques bsico

de un controlador de una Seales

memoria de acceso aleatoriode control

dinmica de escritura y lectura

no simultneas (DRAM)

sin generador de seales de control

(Timing controller)

RAS

G 3

n2 /2

0

n2 /2

1

2

3

Registro

C

n2 /2

Variables

de direccin

MUX

n2

n2 /2

n2 /2

Variables

de direccin

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA DRAM

Peticin de ciclo

de memoria

Seal de ciclo de

regrabado en ejecucin

UNIDAD DE MEMORIA DINMICA

Variables de direccin

CONTROLADOR DE MEMORIA DINMICA

n2 /2

GEN ERADOR

DE S EALES

DE CONTROL

MICROPROCES ADOR

Barra de direccin

n2

CIRCUITO

RAS

CONTROLADOR

CAS

R/W

RAM

DINMICA

2 n 2 x n1

R/W

Barra de datos

Unidad de memoria de acceso aleatorio dinmica

de escritura y lectura no simultneas (DRAM) acoplada a un microprocesador

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA DRAM AVANZADAS

Estticas

Asncronas (ASRAM)

Sncronas (SSRAM)

Voltiles

Clasificacin

segn la volatilidad

de las memorias

de acceso aleatorio

activas de escritura y

lectura no simultneas

Asncronas (DRAM)

FPMDRAM

Dinmicas

EDODRAM

Sncronas

BEDODRAM

SDRAM

SLDRAM

RDRAM

NVRAM

No voltiles

FRAM

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA DRAM AVANZADAS FPMDRAM

Se basan en que la mayora de los programas que se ejecutan en los computadores de

aplicacin general acceden a direcciones de la memoria que estn en la misma pgina

y la parte alta de la direccin permanece constante. Si dicha parte se aplica a la direccin

de las filas se puede mantener la entrada en un nivel constante y aplicar flancos de bajada

sucesivos a la entrada . De esa forma la precarga, descrita anteriormente, se hace una sola

vez y se disminuye el tiempo de acceso.

Direccin

de fila

Direccin de

columna

Direccin de

columna

Direccin de

columna

Direccin

(Address)

RAS

CAS

R/W

Informacin

de salida

Informacin

de salida

Informacin

de salida

Entrada/Salida

Cronograma de las seales de una memoria FPMDRAM

(Fast Page Mode DRAM) durante un ciclo de lectura

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

VCC

CAS

DQ1

A0

A1

DQ2

A2

A3

VSS

DQ3

A4

A5

DQ4

A6

A7

DQ5

A8

A9

A10

DQ6

W

VSS

DQ7

NC

DQ8

NC

RAS

NC

NC

VCC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

MEMORIA DRAM

Mdulo SIMM (Single-In Line Module)

de una memoria DRAM

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA ACTIVA RAM DE ESCRITURA

Y LECTURA SIMULTNEAS

INTERFAZ

MEMORIA ACTIVA

PROCESADOR

DE ES CRITURA

PERIFRICO

DIGITAL

Y LECTURA

DE SALIDA

SIMULTNEAS

Memoria de acceso aleatorio activa de escritura y lectura simultneas

como interfaz entre un procesador y un perifrico de salida

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA ACTIVA RAM DE ESCRITURA

Y LECTURA SIMULTNEAS

Direccin de escritura

Direccin de lectura

Impulso de escritura

Control o desinhibicin de salida

Terminales

de entrada

n2

n2

1A

RAM

2 n 2 -1

0

2A n 2

2 -1

C3

EN4

1A,3D

2A,4

Terminales

de salida

Smbolo lgico de una memoria de acceso aleatorio activa esttica

de escritura y lectura simultneas

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA ACTIVA RAM DE ESCRITURA Y LECTURA SIMULTNEAS

CONJUNTO DE CELDAS DE MEMORIA

(MEMORY CELLS)

POSICIN 0

DEC 1

Direccin

de escritura

X/Y

n2

0

1

Bit

n1

n1

POSICIN 1

2n2 -1

X/Y

n2

n1

DEC 2

Control

de salida

Bit

n1

Impulso

de escritura

Direccin

de lectura

Bit

EN

Bit

Bit

Bit

n1

0

1

n1

n1

n1

n1

EN

G

Esquema de bloques

de una memoria

RAM de escritura y

lectura simultneas

en posiciones diferentes

con organizacin 2D

2n2 -1

POSICIN 2 n 2 - 1

Bit

Bit

Bit

n1

n1

n1

n1

n1

Terminales de entrada

EN

Terminales

de salida

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA ACTIVA RAM DE ESCRITURA

Y LECTURA SIMULTNEAS

INTERFAZ (INTERFACE)

RAM

Direccin de escritura

2A

PROCESADOR

DIGITAL

1A

Impulso de escritura

C3

SINCRONO

Informacin

1A,3D

2A

Direccin

de lectura

Esquema de bloques del circuito

de acoplamiento de un procesador

digital y un perifrico de salida

realizado con una memoria

de acceso aleatorio activa de escritura

y lectura simultneas

UNIDAD

DE

PERIFRICO

Impulso de transferencia

CONTROL

Seal de transferencia aceptada

G

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA ACTIVA RAM DE ESCRITURA Y LECTURA SIMULTNEAS

VISUALIZADOR ESTTICO

UNIDAD DE CONTROL

2

Direccin de escritura

PROCESADOR

Impulso de escritura

DIGITAL

RAM

0

1A 3

0

2A 3

C3

SINCRONO

VISUALIZADOR DINMICO

Informacin (Dgito ASCII)

Circuito de conversin

de un visualizador

dinmico en esttico

mediante una memoria

de acceso aleatorio activa

esttica de escritura

y lectura simultneas

6

1A,3D

CONVERTIDOR

2A

DE CDIGO

17

G

CTR

C

X/Y

2

I1

I2

I3

Direccin

de lectura

I4

+V

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA RAM DE ACCESO MLTIPLE

(MULTIPORT MEMORIES)

Direccin de

escritura/lectura

n2

n2

Direccin de lectura

RAM

1A

2A

0

2n 2 -1

0

2 n 2 -1

Seales de control

n1

Terminales

de entrada

Smbolo lgico

normalizado de una memoria RAM

activa de acceso doble en lectura y

escritura simultneas

1A

n1

1A

n1

2A

Terminales

de salida

Terminales

de salida

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA RAM DE ACCESO MLTIPLE

Variables de direccin

Variables de direccin

Canal

1A

Seales de control

CIRCUITO DIGITAL

Seales de control

Seal de memoria

ocupada (Busy)

DE ARBITRAJE

Seal de memoria

ocupada (Busy)

Esquema de bloques

de una memoria activa

de acceso aleatorio doble

en escritura y lectura

(Dualport Static RAM)

(DPRAM)

Impulso de escritura

X/Y

X/Y

CONJUNTO

DE CELDAS

DE MEMORIA

Terminales de

entrada/salida

CIRCUITOS DE

Terminales de

entrada/salida

del canal 1A

SELECCIN Y CONTROL

DE ENTRADA/SALIDA

Terminales de

entrada/salida

del canal 2A

Canal

2A

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA RAM DE ACCESO MLTIPLE

n2

Variables de direccin

RAM

1A

0

2 n 2 -1

2A

0

2 n 2 -1

n2

Variables de direccin

Seales de control

Seales de control

Memoria ocupada

Memoria ocupada

Terminales

del canal 1A

1A

2A

Terminales

del canal 2A

Smbolo lgico de una memoria DPRAM

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA RAM DE ACCESO MLTIPLE

Barra de direccin n2

PROCESADOR

DIGITAL

RAM

1A

0

2 n 2 -1

2A

0

2n 2 -1

Seales de control

Seales de control

Seal de memoria

ocupada

Barra de datos

n2 Barra de direccin

Seal de memoria

ocupada

1A

2A

Barra de datos

Utilizacin de una memoria DPRAM

para acoplar dos procesadores digitales

PROCESADOR

DIGITAL

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA RAM DE ACCESO MLTIPLE

APLICACIONES

Al sistema

electrnico

de control

RAM

de acceso

doble

Interfaz de

comunicaciones AS-i

Al cable AS-i

Bus interno

Unidad

central de

proceso

E2PROM

Interfaz de

configuracin

Al usuario

Esquema de bloques del procesador de comunicaciones

principal de una red de comunicaciones AS-i que utiliza una memoria DPRAM

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA RAM DE ACCESO MLTIPLE

Sistema electrnico

de control

Procesador de comunicaciones

principal (AS-i master)

APLICACIONES

Fuente de alimentacin

AS-i

Sensor con procesador de

comunicaciones subordinado

(AS-i slave)

Distribuidor

Columna de

sealizacin

con proc. de

comunicaciones

subordinado

Cable de

comunicaciones

AS-i

Mdulo de E/S

con procesador de

comunicaciones

subordinado

Fuente de

alimentacin

auxiliar

Arrancador de motor

con procesador de

comunicaciones

subordinado

Sensores y actuadores

convencionales

Ejemplo real de red AS-i (Cortesa de Siemens).

Botonera con

procesador de

comunicaciones

subordinado

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIA RAM DE ACCESO MLTIPLE

APLICACIONES

a)

b)

Circuito integrado AS-i A2SI: a) Diagrama de bloques. b)

Placa de circuito impreso para el diseo de subordinados ASi. (Cortesa de ZMD y Bihl&Wiedemann) []

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS RAM ACTIVAS NO VOLTILES (NVRAM)

NVRAM

Variables

Esquema de bloques de de direccin

WE

una memoria NVRAM

CE

OE

implementada con un

circuito de alimentacin

ininterrumpida

VCC

n2

n2

SISTEMA DE ALIMENTACIN

ININTERRUMPIDA (SAI)

MUX

FUENTE

DE

ALIMENTACIN

RAM (CMOS)

A n02

2 -1

C

G

EN

X 1

0

CIRCUITO

DE

CONTROL

CARGADOR

DE

BATERAS

n1

+

-

Entrada/salida

de informacin

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS RAM ACTIVAS NO VOLTILES

Registro de

direccin

C

Registro de

salida

FRAM

Variables

de direccin

Esquema de bloques

de una memoria RAM

ferroelctrica (FRAM)

CE

CIRCUITO

WE

DE

CONTROL

OE

CIRCUITO

DE

VDD

LVL

MONITOR

DE VDD

INHIBICIN

Terminales de

entrada/salida

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS

Memorias de acceso aleatorio que estn implementadas con

elementos de memoria no voltiles cuyo tiempo de lectura es

mucho menor que el de escritura. Reciben la denominacin

general de memorias ROM (Read Only Memories) y se

caracterizan por:

- Tienen tiempos de escritura y lectura muy diferentes que dependen del

principio fsico en el que se basa el elemento de memoria utilizado.

- No son voltiles lo que las hace idneas para el almacenamiento de una

parte o de todas las instrucciones de los procesadores digitales

secuenciales sncronos programables conocidos como computadores

- Su celda bsica es sencilla porque slo contiene uno o dos elementos

dispositivos semiconductores.

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS

Totalmente pasivas: ROM

Clasificacin

de las memorias

de acceso aleatorio

pasivas

Pasivas programables

PROM

OTP EPROM

Borrables mediante rayos ultravioleta (EPROM)

Pasivas reprogramables

Borrables elctricamente por efecto tnel (EEPROM)

FLASH

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS

APLICACIONES

- Implementacin de generadores de caracteres

(Character generators) que son convertidores de cdigo,

como por ejemplo del cdigo ASCII al de 5 por 7 puntos

- Implementacin del circuito combinacional de los

sistemas secuenciales sncronos programables.

- Almacenamiento de todas las instrucciones, o de una parte de

ellas, de los computadores de arquitectura Princeton

(Von Neumann) o Harvard.

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS TOTALMENTE PASIVAS (ROM)

Son conocidas simplemente como ROM (acrnimo de

Read Only Memories). Son memorias de acceso aleatorio

que nunca pueden ser escritas por el usuario. Al colocarlas

en un sistema digital slo pueden ser ledas.

La grabacin o escritura la realiza el fabricante durante el

proceso de fabricacin. Debido a que dicho proceso se lleva

acabo mediante la utilizacin de una secuencia de

mscaras, estas memorias suelen recibir la denominacin

de memorias programables por mscara (Mask

Programmable ROM)

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS TOTALMENTE PASIVAS (ROM)

+VDD

Memoria totalmente pasiva (ROM)

de organizacin 3D implementada

con transistores MOS de canal N

enriquecidos

T

Salida de

Informacin

TC

X/Y

TC

TC

TL

TL

TL

TL

TL

TL

TL

TL

TL

X0

X1

n/2

(A 0 a A (n / 2)1 )

X 2n 2 -1

Variables de

direccin

X/Y

(A n / 2 a A n 1 )

Y0

Y1

n/2

Y2n 2 -1

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS TOTALMENTE PASIVAS (ROM)

Variables de

direccin

n2

MEMORIA

n1

PASIVA

Terminales

de salida

Variables de

direccin

n2

ROM

A

0

2

n2

-1

n1

A

Inhibicin

de salida

No normalizado

Variables de

direccin

Desinhibicin

de salida

Smbolos lgicos

de una memoria ROM

n2

Desinhibicin

de salida

ROM

EN

2 n 2 -1

EN

Normalizado

n1

A

Normalizado

Terminales

de salida

Terminales

de salida

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS PROGRAMABLES (PROM)

Son memorias de acceso aleatorio cuyo contenido puede ser escrito por

el usuario una sola vez. Por ello se llaman PROM (Programmable

Read Only Memories)

Las de uso ms extendido se implementaron en tecnologa TTL y

utilizaron la celda de memoria formada por un transistor bipolar y un

diodo.

Han dejado de utilizarse porque han sido sustituidas con ventaja por

las memorias reprogramables implementadas con transistores MOS.

Tambin se pueden considerar PROM las memorias OTP EPROM.

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS PROGRAMABLES (PROM)

Variables de

direccin

n2

PROM

A

0

2 n 2 -1

n1

A

E1

E2

Terminales de

salida/programacin

&

EN

E3

Smbolo lgico de una memoria PROM con salida de tres estados

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES (RPROM)

Son memorias de acceso aleatorio cuyo contenido puede

ser escrito por el usuario varias veces. Se diferencian de

las memorias de acceso aleatorio activas en que el tiempo

de escritura es en general mayor que el de lectura.

Hay tres tipos de memorias RPROM:

- EPROM

- EEPROM

- FLASH

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EPROM

Las memorias pasivas reprogramables, conocidas como EPROM (Erasable

Programmable Read Only Memories) se graban mediante impulsos

elctricos cuyo nivel de tensin es mayor que el utilizado durante la operacin

del circuito.

Utilizan en su implementacin los transistores MOS de puerta flotante borrables

con rayos ultravioleta La grabacin consiste en inyectar portadores de carga en

dicha puerta, mediante impulsos elctricos. El borrado se realiza mediante rayos

ultravioleta, para lo cual el circuito se encapsula de forma que queda situado

debajo de una zona (ventana) transparente que permite el paso de los citados

rayos, y por ello algunos fabricantes las denominan UVEPROM.

Las memorias EPROM que carecen de la citada ventana solo se pueden

programar una vez y por ello se denominan OTP (One Time Programmable)

EPROM.

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EPROM

Variables de

direccin

n2

EPROM

A

0

2

n2

-1

n1

Vpp

Seales

de control

G/PWR DWN

OE

Terminales de

salida/programacin

&

EN

CE

Smbolo lgico de una memoria de acceso aleatorio pasiva reprogramable EPROM

con terminal independiente para la tensin de grabacin (VPP)

e impulso de grabacin a travs del terminal de desinhibicin CE).

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EPROM

EPROM

n2

Variables de direccin

Vpp

Seales

de control

PGM

(Program Enable)

OE

0

2 n 2 -1

n1

G/PWR DWN

Terminales de

salida/programacin

PGM

&

EN

CE

Smbolo lgico de una memoria de acceso aleatorio pasiva reprogramable EPROM

con terminal independiente para la tensin de grabacin (VPP)

y para el impulso de grabacin PGM

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EPROM

Variables de

direccin

n2

EPROM

A

0

2

n2

-1

n1

Seales

de control

G/PWR DWN

CE

Terminales de

salida/programacin

&

EN

OE/Vpp

Smbolo lgico de una memoria de acceso aleatorio pasiva reprogramable EPROM

con terminal nico de desinhibicin de salida y tensin de grabacin (OE/ Vpp)

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EPROM

Seales de

control

Modo de operacin

Lectura (Read)

Inhibicin de salida (Output enable)

Mnimo consumo (Standby)

Programacin (Programming)

Verificacin (Test)

Inhibicin de programacin

(Programming enable)

Identificacin inteligente

(Electronic signature)

- Fabricante (Manufacturer code)

- Dispositivo (Device code)

Variables

de

direccin

CE OE / V PP A k

Tensin de

alimentacin

Terminales

salida/programacin

Ai

VCC

Dn1 1 D0

0

0

1

0

0

0

1

X

VPP

0

X

X

X

X

X

X

X

X

X

X

5V

5V

5V

VProg.

VProg.

Informacin memoria

Tercer estado

Tercer estado

Informacin externa

Informacin memoria

VPP

VProg.

Tercer estado

0

0

0

0

Vid

Vid

0

1

5V

5V

Cod. Fabricante

Cod. Circuito

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EPROM

Variables

de direccin

Variables

de direccin

Informacin

externa

CE

VProg

VCC

OE/Vpp

5V

Vpp

OE/Vpp

Terminales

de salida

t acceso

Ciclo de lectura

CE

te

tg

tm

tr

Ciclo de lectura

Cronograma de las seales aplicadas a la memoria pasiva reprogramable EPROM

de la diapositiva 54

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

INICIO

DIRECCIN =

MEMORIAS DE

ACCESO ALEATORIO

Aplicar VCC = Vgrab1

y Vpp = Vgrab2

I=0

PONER DATO A GRABAR Y

APLICAR IMPULSO I

I = I+1

I = 25

SI

NO

MEMORIAS PASIVAS

REPROGRAMABLES EPROM

NO

COMPARAR EL CONTENIDO

DE LA MEMORIA CON LA

INFORMACIN ORIGINAL

COMPARAR EL CONTENIDO

DE LA MEMORIA CON LA

INFORMACIN ORIGINAL

COINCIDENCIA

COINCIDENCIA

SI

NO

SI

LTIMA

DIRECCIN

SI

INCREMENTAR

DIRECCIN

VCC = Vpp = Vnormal

COMPARAR EL CONTENIDO

DE LA MEMORIA CON LA

INFORMACIN ORIGINAL

Algoritmo rpido de grabacin

de una memoria pasiva reprogramable EPROM

ALGUNA

POSICIN NO

COINCIDE

SI

NO

GRABACIN

REALIZADA

CIRCUITO

DEFECTUOSO

NO

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EPROM

GRABADOR

Zcalo de fuerza

de insercin nula

COMPUTADOR

INTERFAZ

PERSONAL

FUENTE DE

ALIMENTACIN

Esquema de bloques de un grabador de memorias pasivas

reprogramables EPROM

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EPROM

APLICACIONES

MICROCONTROLADOR

RAM

A

EPROM

A

Barra de

direccin

UNIDAD

Barra de datos

CENTRAL DE

PROCESO

Seales

de control

INTERFAZ

PERIFRICO

Aplicacin de las memorias pasivas reprogramables EPROM

al almacenamiento de las instrucciones de un microcomputador

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EEPROM

Variables de

direccin

MUX

WE

+21V

+5V

CE

X 1

0

1

EEPROM

n2

A

Vpp

0

2 -1

n2

n1

A

G/PWR DWN

Terminales de

salida/programacin

&

EN

OE

Smbolo lgico de una memoria pasiva reprogramable EEPROM

con terminal de impulsos de grabacin (VPP)

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EEPROM

Variables de

direccin

EEPROM

n2

MUX

0

WE

+5V

CONVERTIDO R

5 a 21V

CE

X 1

0

1

CONJUNTO DE C ELDAS

DE MEMO RIA

A

Vpp

0

2 -1

n2

n1

A

G/PWR DWN

Terminales de

entrada/salida

&

EN

OE

Esquema de bloques de una memoria pasiva reprogramable EEPROM

con tensin de alimentacin nica

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EEPROM

Variables de

direccin

WE

EEPROM

n2

A

0

2 -1

n2

n1

C

G/PWR DWN

CE

Terminales de

entrada/salida

&

EN

OE

Smbolo lgico de una memoria pasiva reprogramable EEPROM

con tensin de alimentacin nica

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EEPROM

Puesta en estado

inicial del sistema

Barra de direccin

1

&

N1

&

EEPROM

n2

A

WE

0

2 -1

n2

n1

C

G/PWR DWN

PROCESADOR

DIGITAL

CE

Seal de

seleccin de

EEPROM

N2

&

OE

&

EN

&

Seal de lectura/escritura (R/W)

Barra de datos

Circuito de conexin de la memoria pasiva reprogramable EEPROM

con tensin de alimentacin nica a un procesador digital

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EEPROM

RUTINA DE

BORRADO/ GRAB ACIN

Algoritmo de grabacin

de la memoria de acceso

SELECCIONAR DIRECCIN

PONER CE = 0 Y OE = 1

ACTIVAR WE

aleatorio pasiva reprogramable

EEPROM

BORRADO

TIPO DE

OPERACIN

PONER BARRA

DE DATOS EN

TERCER ES TADO

GRABACIN

PONER

INFORMACIN

EN BARRA DE DATOS

RETARDO

DESACTIVAR WE

FIN

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EEPROM

Variables de

direccin

WE

Grabacin

realizada (Ready)

+VCC (5V)

CE

TEMPO RIZADOR

DE ESC RITURA

CONVERTIDO R

5 a 21V

n2

MUX

0

X 1

0

1

Vpp

CONJUNTO DE CELDAS

DE MEMO RIA

A n02

2 -1

n1

A

G/PWR DWN

Terminales de

entrada/salida

&

EN

OE

Esquema de bloques de una memoria pasiva reprogramable EEPROM

con temporizador de escritura incorporado

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EEPROM

Memoria EEPROM

con temporizador de

escritura incorporado

Variables de

direccin

EEPROM

n2

A

0

2 -1

n2

n1

WE

G/PWR DWN

Smbolo lgico

CE

Terminales de

entrada/salida

A

n

&

Deteccin de

escritura realizada

EN

OE

n2

Barra de direccin

EEPROM

0

2 n 2 -1

WE

n1

G/PWR DWN

Conexin a un

microprocesador

CE

MICROPROCESADOR

OE

Barra de datos

&

EN

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EEPROM

APLICACIONES

DATOS Y

RESULTADOS

MEMORIA

ACTIVA

(RAM)

PROGRAMA

TABLAS

MEMORIA

MEMORIA

PASIVA

REPROGRAMABLE

(EPROM)

PASIVA

REPROGRAMABLE

(EEPROM)

MICROPROCESADOR

INTERFAZ

INTERFAZ

DE RED

PERIFRICO

COMPUTADOR

Aplicacin de las memorias EEPROM al almacenamiento de tablas

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES EEPROM

MICROCONTROLADOR

RAM

EPROM

MICROPROCESADOR

INTERFAZ

INTERFAZ

Canal de

comunicacin serie

MEMORIA EEPROM

DE ESCRITURA Y

LECTURA EN SERIE

A los Perifricos

Conexin de un microcontrolador y una memoria

EEPROM de lectura y escritura en serie (Serial EEPROM)

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES FLASH

FLASH

18

Variables de direccin

Vpp

0

2 -1

18

WE

G/PWR DWN

OE

Terminales de

entrada/salida

&

EN

CE

Smbolo lgico de una memoria FLASH

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

Registro de

direcciones

C

MEMORIAS

PASIVAS

REPROGRAMABLES

FLASH

n2

Variables

de direccin

n1

CONJUNTO

DE

Vpp

CELDAS

SEALES DE

BORRADO

Y GRABADO

Z1

OE

Esquema de bloques

simplificado de una

memoria FLASH

&

WE

Registro de

rdenes

UNIDAD

Z2

DE

CONTROL

CE

Registro de

datos

Z2

Z1

n1

n1

n1

EN

Barra

de datos

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS PASIVAS REPROGRAMABLES FLASH

APLICACIONES

DATOS Y

RESULTADOS

MEMORIA

ACTIVA

(RAM)

PROGRAMA DE CARGA

DE LA MEMORIA FLASH

PROGRAMA

DE CONTROL

MEMORIA

PASIVA

REPROGRAMABLE

MEMORIA

PASIVA

REPROGRAMABLE

(EPROM)

(FLASH)

MICROPROCESADOR

INTERFAZ

PROCESADOR DE

COMUNICACIONES

PERIFRICO

Canal de

comunicacin serie

COMPUTADOR

Aplicacin de las memorias FLASH al almacenamiento

de programas en un sistema de control distribuido

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS DE ACCESO ALEATORIO

DE COMUNICACIN SERIE

MEMORIA DE ACCESO ALEATORIO SERIE

Bus de

comunicacin

serie

PROCESADOR

DE

MEMORIA DE

ACCESO

COMUNICACIONES

ALEATORIO

Esquema de bloques de una memoria de acceso aleatorio

de lectura y escritura en serie

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS EEPROM DE COMUNICACIN SERIE

MEMORIA EEPROM SERIE

n2

EEPROM

A n02

2 -1

WE

Canal de

comunicacin

serie

PROCESADOR

DE

GR

CE

COMUNICACIONES

OE

n

A

G/PWR DWN

&

EN

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS EEPROM DE COMUNICACIN SERIE

MICROCONTROLADOR

CS

PROCESADOR DE

COMUNICACIONES

(MICROWIRE)

EEPROM

SERIE

CLK

DO

Ejemplo de

MICROPROCESADOR

DI

conexin

de una EEPROM

serie a un

Conexin a travs de un puerto serie del microcontrolador

microcontrolador

MICROCONTROLADOR

CS

MICROPROCESADOR

PUERTO DE

ENTRADA/SALIDA

EN PARALELO

CLK

EEPROM

SERIE

DO

DI

Conexin a travs de un puerto paralelo del microcontrolador

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS EEPROM CON COMUNICACIN SERIE

CLK

CS

DI

Cdigo de operacin

Direccin de lectura

DO

Bit de

inicio

Informacin leda

Cronograma del ciclo de lectura de las seales de una memoria EEPROM

que utiliza el protocolo Microwire

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS DE ACCESO ALEATORIO

CON COMUNICACIN SERIE

CLK

CS

DI

Cdigo de operacin

Direccin de escritura

Informacin a escribir

DO

Ciclo de escritura

en memo ria

Fin del

ciclo de

escritura

Cronograma del ciclo de escritura de las seales de una memoria EEPROM

que utiliza el protocolo Microwire

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS DE ACCESO ALEATORIO

CON COMUNICACIN SERIE

APLICACIONES

MEMORIA EXTERNA (PEN DRIVE)

USB

PROCESADOR DE

COMUNICACIONES

USB

Esquema de bloques

MEMORIA

FLASH

Fotografa

Memoria externa (Pen Drive) conectable a un computador

mediante el protocolo de comunicaciones USB

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

MEMORIAS DE ACCESO ALEATORIO

CON COMUNICACIN SERIE

APLICACIONES

MICROCONTROLADOR CON MEMORIA FLASH

MEMORIA

FLASH

---------------

PROCESADOR DE

COMUNICACIONES

UNIDAD

CENTRAL DE

PUERTO

PROCESO

PARALELO

PUERTO

SERIE

Microcontrolador que almacena las instrucciones

en una memoria FLASH

PROCESADOR

EXTERNO

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

UNIDADES DE MEMORIA MODULARES

n2

Variables de direccin

WE

Impulso escritura

Desinhibicin escritura/lectura

Desinhibicin de salida

CE

OE

RAM

0

A n2

2 -1

C1

G2

&

EN3

n1

2,A,1D/ 2,A,1,3

Smbolo lgico de una memoria de acceso aleatorio activa, esttica

y de escritura y lectura no simultneas

con terminales de entrada y salida comunes

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

BF1

n2

Variables de direccin

Impulso escritura

MEMORIAS

DE ACCESO ALEATORIO

Desinhibicin escritura/lectura

Desinhibicin de salida

WE

CE

RAM

A n02

2 -1

C1

G2

&

EN3

OE

n1

2,A,1D/2,A,1,3

UNIDADES DE MEMORIA

MODULARES

BF2

n2

WE

CE

RAM

0

A n2

2 -1

C1

G2

&

EN3

OE

Unidad de memoria

de acceso aleatorio activa

de 2n2 posiciones de n'1bits

implementada con n' bloques

n1

2,A,1D/2,A,1,3

funcionales idnticos

BFm

n2

WE

CE

OE

RAM

A n02

2 -1

C1

G2

&

EN3

n1

2,A,1D/2,A,1,3

Terminales de

entrada/salida

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

BF1

MEMORIAS

DE ACCESO ALEATORIO

n2

Variables de direccin

(bits menos significativos)

Impulso escritura

WE

Z1

CE

RAM

0

A n2

2 -1

C1

G2

&

EN3

OE

Desinhibicin de salida

n1

2,A,1D/2,A,1,3

BF2

UNIDADES DE MEMORIA

MODULARES

n2

WE

Z2

CE

RAM

0

A n2

2 -1

C1

G2

&

EN3

OE

Unidad de memoria

de acceso aleatorio activa

de m posiciones de n1 bits

implementada con 2n2

bloques funcionales idnticos

Variables de

direccin

(bits ms

significativos)

1

2

n '2

X/Y

1

2

2n'2

n1

Z1

Z2

2,A,1D/2,A,1,3

n1

Zp

BFm

n2

WE

Zp

CE

OE

RAM

0

A n2

2 -1

C1

G2

&

EN3

n1

2,A,1D/2,A,1,3

Terminales de

entrada/salida

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

UNIDADES DE MEMORIA MODULARES

8

WE

CE

RAM (256x4)

0

A 255

C1

G2

&

EN3

OE

4

2,A,1D/ 2,A,1,3

Smbolo lgico de una memoria de acceso aleatorio activa esttica

de escritura y lectura no simultneas de 256 posiciones de 4 bits

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO ALEATORIO

UNIDADES DE MEMORIA MODULARES

8

RAM (256x4)

0

A 255

C1

G2

&

&

EN3

RAM (256x4)

0

A 255

C1

G2

&

EN3

RAM (256x4)

0

A 255

C1

G2

RAM (256x4)

0

A 255

C1

G2

&

EN3

EN3

Variables de direccin (A 0 a A 7)

Impulso escritura

Desinhibicin de salida

A8

Variables de

direccin

A9

X/Y

1

2

2,A,1D/2,A,1,3

2,A,1D/2,A,1,3

2,A,1D/2,A,1,3

2,A,1D/2,A,1,3

0

1

Barra de

entrada/salida

2

Desinhibicin

EN

Unidad de memoria

1K8 implementada

con el bloque funcional

de la diapositiva

anterior

RAM (256x4)

0

A 255

C1

G2

&

&

EN3

RAM (256x4)

0

A 255

C1

G2

&

EN3

4

2,A,1D/2,A,1,3

RAM (256x4)

0

A 255

C1

G2

&

EN3

4

2,A,1D/2,A,1,3

RAM (256x4)

0

A 255

C1

G2

EN3

4

2,A,1D/2,A,1,3

4

2,A,1D/2,A,1,3

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO DIRECTO

MEMORIAS DE ACCESO DIRECTO Y ESTRUCTURA INTERNA SERIE

SRG

DINMICO

G

Esquema bsico de un

1J

C1

1K

Q

&

&

C1

registro de desplazamiento

1D

dinmico utilizado como

memoria de acceso directo

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO DIRECTO

MEMORIAS DE ACCESO DIRECTO Y ESTRUCTURA INTERNA SERIE

SRG

DINMICO

1

1J

C1

1K

Q

&

&

C1

CTR

C+

n1

1D

n2

Q n1

Esquema bsico de una memoria de acceso directo implementada

mediante un registro de desplazamiento dinmico y un contador

y organizada en posiciones de n1 bits

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO DIRECTO

MEMORIAS DE ACCESO DIRECTO Y ESTRUCTURA INTERNA SERIE

SRG

DINMICO

G

1J

C1

1K

Q

&

&

C1

CONTADOR

DE BITS

CONTADOR DE

POSICIONES

CTR DIV n1

CTR

G1

C+

C2/1+

1

1D

n2

Q 1

COMP

CT = 0

Direccin externa

Esquema bsico de una memoria de acceso directo implementada

mediante un registro de desplazamiento dinmico y un contador

y organizada en serie bit a bit

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO DIRECTO

MEMORIAS DE ACCESO DIRECTO Y ESTRUCTURA INTERNA SERIE

SRG

DINMICO

G

1J

C1

1K

Q

&

&

C1

CONTADOR

DE BITS

CONTADOR DE

POSICIONES

CTR DIV n1

CTR

G1

C+

C2/1+

Orden de

lectura

1D

n2

Q 1

CT = 0

Direccin de lectura

Esquema del circuito de lectura

de una memoria de acceso directo

implementada con un registro

de desplazamiento dinmico

y organizada en serie bit a bit

SRG

G2

C1

1,2D

n1

Informacin

de salida

COMP

&

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO DIRECTO

MEMORIAS DE ACCESO DIRECTO Y ESTRUCTURA INTERNA SERIE

SRG

DINMICO

G

SRG

G2

M3

C1

MUX

1,3,2D

Entrada de

informacin

n1

1J

C1

1K

Q

&

&

C1

CONTADOR

DE BITS

CONTADOR DE

POSICIONES

CTR DIV n1

CTR

G1

C+

C2/1+

1

1D

0

1

1,3,2D

0

Q 1

CT = 0

Orden de

escritura

n2

&

COMP

Direccin de escritura

Esquema del circuito de escritura de una memoria de acceso directo implementada

con un registro de desplazamiento dinmico y organizada en serie bit a bit

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO DIRECTO

MEMORIAS DE ACCESO DIRECTO Y ESTRUCTURA INTERNA SERIE

UNIDAD DE

Orden de

lectura

CONTROL

SRG

DINMICO

G

SRG

G2

M3

C1

MUX

1,3,2D

Entrada de

informacin

1J

C1

1K

Q

&

&

C1

CONTADOR

DE BITS

CONTADOR DE

POSICIONES

CTR DIV n1

CTR

G1

C+

C2/1+

1

1D

0

1

1,3,2D

n2

0

Q 1

CT = 0

CT = 0

Esquema del circuito de escritura secuencial de una memoria de acceso directo

implementada con un registro de desplazamiento dinmico

y organizada en serie bit a bit

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

CARACTERISTICAS GENERALES

Memorias que se caracterizan por carecer de variables de direccin.

En ellas no se especifica la direccin sino que en la operacin de

escritura la informacin se introduce en la posicin de la memoria

conectada a los terminales de entrada y en la de lectura se lee la

situada en la posicin unida a los terminales de salida.

Este tipo de memorias tiene como objetivo facilitar el tratamiento

de la informacin proporcionada en secuencia por un sistema digital.

Segn la forma en la que se accede a la informacin almacenada

se pueden clasificar en tres grandes clases:

- Registros de desplazamiento.

- Memorias cola o tubo.

- Memorias pila

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

REGISTROS DE DESPLAZAMIENTO ESTTICOS

SRG n

Entrada de puesta a cero

Impulsos de desplazamiento

Entrada de informacin en serie

R

C1/

1D

Q n-1

Salida de informacin en serie

Smbolo lgico de un registro de desplazamiento esttico

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

PROCESADOR DE

COMUNICACIONES

REGISTROS DE

DESPLAZAMIENTO

ESTTICOS

APLICACIONES

PROCESADOR

TRANSMISOR

SRG

DIGITAL

Salida serie

Utilizacin de los registros

de desplazamiento estticos

en la implementacin de

un procesador de comunicaciones

RECEPTOR

SRG

A otros

procesadores

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

REGISTROS DE DESPLAZAMIENTO DINMICOS

Se caracterizan porque los impulsos de desplazamiento no se

pueden anular por tiempo indefinido dado que en dicho caso

desaparece la informacin contenida en su interior.

Se han realizado especialmente en tecnologas MOS y estn

formados por celdas bsicas de memoria que almacenan la

informacin en forma de carga del condensador existente

entre la puerta y el surtidor de un transistor MOS.

Se utilizan para implementar Memorias circulares.

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

MEMORIAS COLA (FIFO)

Son memorias de acceso secuencial en las que la informacin que

entra al darle una orden de escritura sale antes que todas las que

entran en posteriores ordenes de escritura.

FIFO

Seales

de control

Entrada de

informacin

Smbolo lgico

de una memoria FIFO

n1

n1

Salida de

informacin

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

POS. 2n 2

POS. 3 POS. 2 POS. 1

Entrada de

informacin

Salida de

informacin

MEMORIA VACA

MEMORIAS

PILA (FIFO)

I1

I1

PRIMERA OPERACIN DE ESCRITURA

Forma en que se escribe y se

lee una memoria cola (FIFO)

en sucesivas operaciones

de escritura y lectura

I2

I2

I1

SEGUNDA OPERACIN DE ESCRITURA

I3

I3

I2

I1

TERCERA OPERACIN DE ESCRITURA

I3

PRIMERA OPERACIN DE LECTURA

I2

I1

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

MEMORIAS COLA (FIFO)

FIFO

C1/

n1

Entrada de

informacin

1D

G0

G1

Orden

externa

R/W

UNIDAD DE

n2

G2

CONTROL

n1

G n 2 1

Salida de

informacin

Memoria cola (FIFO) implementada mediante un conjunto de biestables

conectados en serie con entradas de inhibicin independientes

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

MEMORIAS COLA (FIFO) IMPLEMENTADAS CON UNA

MEMORIA DE ESTRUCTURA INTERNA SERIE

Poseen las siguientes caractersticas que limitan su operatividad:

-En ellas la informacin se desplaza fsicamente lo cual hace que su

escritura necesite tantos impulsos del reloj como posiciones vacas posea la

memoria.

-La elevacin de su nmero de posiciones disminuye su velocidad

porque aumenta el tiempo medio de escritura.

-No es posible realizar en operaciones de lectura y escritura simultneas.

-No es posible realizar dos lecturas sucesivas de la misma posicin.

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

MEMORIAS COLA (FIFO) IMPLEMENTADAS CON UNA RAM

MEMORIA TUBO (FIFO)

UNIDAD DE CONTROL

CONTADOR

DE LECTURA

Puesta en estado inicial

Orden de lectura

Orden de escritura

Orden de retransmisin

Seal de memoria vaca

PROCES ADOR

DIGITAL

SECUENCIAL

SINCRONO

CONTADOR

DE ES CRITURA

RAM

0

1A n 2

2 -1

2A

C3

Seal de memoria llena

Entrada de

datos

1A,3D

2A

Salida de

datos

Esquema de bloques de una memoria cola (FIFO) implementada mediante

una memoria de acceso aleatorio de lectura y escritura simultneas.

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

MEMORIAS COLA (FIFO) IMPLEMENTADAS CON UNA RAM

Poseen las siguientes caractersticas:

Todas las operaciones de escritura tienen idntica duracin.

Es posible realizar la operacin de escritura y la de lectura

simultneamente.

Se puede ampliar la capacidad de la memoria sin disminuir la

velocidad.

Es posible realizar varias operaciones de lectura sucesivas de una o

ms posiciones de la memoria consecutivas. Para ello se dota a la

memoria de un terminal que hace que el contenido del contador de

lectura disminuya en una unidad. Dicho terminal suele

denominarse orden de retransmisin porque su principal utilidad

es hacer que se vuelva a enviar la informacin contenida en la

memoria cuando la misma forma parte de un procesador de

comunicaciones en la aplicacin descrita a continuacin.

Existen mltiples alternativas que se diferencian por las seales de

control que la acoplan con los sistemas externos

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

MEMORIAS COLA (FIFO)

FIFO

R

Puesta a cero

Orden de retransmisin (Retransmit)

Orden de lectura (Read Clock)

LDCK

Orden de escritura (Write Clock)

UNCK

OE

Desinhibicin de la salida (Output Enable)

EN

n1

Entrada de informacin

QF

Seal de memoria

llena (Full)

QE

Seal de memoria

vaca (Empty)

n1

Salida de informacin

Smbolo lgico de una memoria cola (FIFO) implementada mediante

una memoria de acceso aleatorio de lectura y escritura simultneas..

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

MEMORIAS COLA (FIFO)

INTERFAZ

APLICACIONES

FIFO

PROCESADOR

PROCESADOR

DIGITAL

DIGITAL

SECUENCIAL

SECUENCIAL

SINCRONO

SINCRONO

Esquema bsico del acoplamiento entre dos procesadores digitales sncronos

implementado mediante una memoria cola

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

MEMORIAS COLA (FIFO)

APLICACIONES

PROCESADOR DE COMUNICACIONES

CON MEMORIA FIFO

FIFO

PROCESADOR

DIGITAL

SECUENCIAL

SINCRONO

UNIDAD

DE

Lnea o red de

comunicaciones

COMUNICACIONES

Esquema de bloques bsico del acoplamiento de un procesador digital

secuencial sncrono a una lnea o red de comunicaciones por

medio de un procesador de comunicaciones que posee una memoria cola (FIFO)

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

MEMORIAS COLA (FIFO)

APLICACIONES

PROCESADOR DE COMUNICACIONES

CON MEMORIA FIFO

FIFO

QF

R

LDCK

UNCK

EN

PROCESADOR

DIGITAL

QE

SECUENCIAL

SINCRONO

UNIDAD

n1

n1

DE

COMUNICACIONES

Esquema de bloques de un procesador de comunicaciones

implementado con una memoria cola

Lnea o red de

comunicaciones

Escuelas Tcnicas de Ingenieros

Universidad de Vigo

Departamento de Tecnologa Electrnica

Electrnica Digital: Unidades de memoria digitales

MEMORIAS DE ACCESO SECUENCIAL

Entrada

MEMORIAS PILA (LIFO)

Salida

Las memorias pila (Stack)

conocidas como LIFO

Entrada

(acrnimo de Last In-First Out) Salida

son memorias de acceso secuencial

en las que la informacin que entra

en la ltima operacin de escritura Entrada

es la que sale en la primera operacinSalida

de lectura que se realice.