Beruflich Dokumente

Kultur Dokumente

Area Delay Power Efficient and Implementation of Modified Square-Root Carry Select Adder Architecture

Hochgeladen von

ijtetjournalCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Area Delay Power Efficient and Implementation of Modified Square-Root Carry Select Adder Architecture

Hochgeladen von

ijtetjournalCopyright:

Verfügbare Formate

INTERNATIONAL JOURNAL FOR TRENDS IN ENGINEERING & TECHNOLOGY

VOLUME 4 ISSUE 2 APRIL 2015 - ISSN: 2349 - 9303

Area Delay Power Efficient and Implementation

of Modified Square-Root Carry Select Adder

Architecture

Ms.S.Banu priya1

Mr.G.Lingeswaran2

Pg scholar

Assistant professor

Erode Sengunthar engineering college, Thudupathi

Erode Sengunthar engineering college, Thudupathi

banusubramaniam92@gmanil.com1

lingesgk1879@gmail.com2

Abstract: In VLSI Technology, Carry Propagation Delay is the most important concern for the Adders. Adder is the

most unavoidable component for the arithmetic performances. This paper is Modified Square Root-Carry Select

Adder (SQRT-CSLA) design reduces the delay with 16 bit adder. Carry select adder have two units for Carry

Generation (CG) and Carry Selection (CS). The modified SQRT-CSLA design can gives parallel path for carry

propagation. So the overall adder delay has reduced. Modified design is obtained using Ripple Carry Adder (RCA)

with Boolean Excess-1 Converter (BEC). BEC produces an output i.e., is an excess one result for given input bits.

Then input bits and BEC output is given to multiplexer for carry selection. Use of BEC instead of dual RCA gives

efficient carry propagation delay and it consumes the lower power and overall gates using in design is reduced with

compared to carry select adder with dual RCA. The final sum is calculated using final sum generation.

Index Terms: RCA, BEC with MUX and Modified SQRT-CSLA

I.INTRODUCTION

II.RIPPLE CARRY ADDER

A ripple carry (RCA) adder is a digital circuit that gives

the two binary values while performing arithmetic

summation. It can be builds with two full adder blocks

connected in parallel form and it produces carry output

from each full adder blocks connected to the next full

adder block to gives the carry input. RCA is one of the

types of adder to use of arithmetic functions and it used

in first stage of this paper.

In the VLSI technology, the low power adder circuits

are widely used due to their fast and increase of

convenient electronics component. A speedy operation

of a digital system is generally influenced by the tenant

adders. The most important and widely accepted metrics

for measuring the quality of adder designs are power,

delay and area. Optimizing the area, delay has always

been considered an important for VLSI design

stipulation. Then the reduction of power dissipation has

come to for as a major design goal aspect. Here digital

adders, the speed of addition are limited by the time

required to propagate a carry through the adder. Highspeed addition and multiplication has always been a

fundamental requirement of high- performance

processors and systems.

A.2-Bit Ripple Carry Adders

In this project, uses a two-bit ripple carry adder and

RCA consists of two full adders (FA) block in it. 2-bit

RCA structure is shown in figure 1. After that, 2-bit

binary inputs and Cin=1 are given to the two full adders.

Then, the sum and carry are generated by first full adder

block. This carry is propagates through the next full

adder block, after only starts to addition process and it

will also generates the sum and carry. These results are

given to the new modified Square Root-Carry Select

adder (SQRT-CSLA).

The sum for each bit position in an elementary adder

is generated sequentially only after the previous bit

position has been summed and carries propagated into

the next block. The major problem of main speed

limitation in several adders is in generation of carries.

This speed limitation can be conquering by using carry

select adder (CSLA) and this CSLA is a fastest adder

among all other adders. Then CSLA has mainly two

types i.e., square-root and linear. Here uses a CSLA

with square-root type and it are an efficient and fast

adder.

Fig 1:

Construction of Two-bit full adder

12

INTERNATIONAL JOURNAL FOR TRENDS IN ENGINEERING & TECHNOLOGY

VOLUME 4 ISSUE 2 APRIL 2015 - ISSN: 2349 - 9303

B.BEC with Mux

The BEC is constructed with Multiplexer (MUX)

circuit and here shows a BEC with 8:4 MUX in figure 3.

One input of the 8:4 MUX gets as it input (B3, B2, B1,

and B0) and another input of the MUX is the BEC

output. This structure can possibly generate parallel two

results and the MUX is selecting either the BEC output

or straight input based on the control signal cin. The

significance of the BEC logic is from the large area

reduction when designing of CSLA with large binary

numbers.

III. FULL ADDER

A full adder is a adder circuits and it contains two half

adders. FA can perform the addition of three input bits

and gives the result of sum and carry. The three input

bits are A, B and Cin and the output of Sum and Cout.

The full adder is shown in following figure 2.

Fig 2: Structure of full adder

IV.BINARY EXCESS-1 CONVERTER

The use of binary to excess-1 code converter is to

converts binary value into excess one form of binary

representation. In this project, dual pair RCA is replaced

by BEC in the new modified SQRT-CSLA architecture

to get lower area and improved speed of performance

than RCA. Because of high propagation delay was

produced when generating partial sum and carry due to

the use of dual RCA pair. The gate counts are used in

this modified CSLA gets reduced.

Fig 3: BEC logic with MUX

V.REGULAR CSLA

In this method n-bit input are given to the first Ripple

carry adder (RCA) block with Cin of 0 and it produces a

sum and carry. After getting carry only, the second RCA

block will start to process on Cin of 1. Until, this second

RCA get carry from previous block, it will wait to get.

So those, the problem were increased in delay and

power. And after that, the right sum and carry is selected

in the selection unit. This regular CSLA method is

shows in figure 4.

A. Binary Excess Code

The modified Square root Carry select adder has a

single ripple carry adder with Binary to Excess-I

converter, which replace the ripple carry adder with

Cin=l, in order to reduce the area and power

consumption of the regular CSLA. Here n+1 BEC is

used instead of n-bit RCA. Table I shows the 4-bit BEC.

Table I: Binary to Binary excess-1 code conversion

Fig 4: Regular CSLA structure

13

INTERNATIONAL JOURNAL FOR TRENDS IN ENGINEERING & TECHNOLOGY

VOLUME 4 ISSUE 2 APRIL 2015 - ISSN: 2349 - 9303

VI.NEW MODIFIED SQRT-CSLA

design and less power consumption compares to the regular

CSLA.

The Binary to excess one Converter (BEC) used instead of the

RCA with signal input cin=1 because of reduce the area and

power utilization of the regular CSLA. The new modified 16bit SQRT-CSLA using BEC is shown in figure 4. Then the

structure is further divided into five major blocks with RCA

and BEC.

VII. SIMULATION RESULTS AND

IMPLEMENTATION

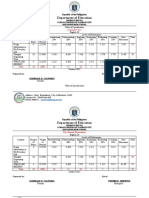

The regular SQRT-CSLA and new modified 16-bit SQRTCSLA experimental results are given in following below

fiure 5 and figure 6. Comparison results of the regular

SQRT-CSLA and new modified 16-bit SQRT-CSLA is

given in table II.

One input to the MUX goes from the RCA with Cin=0 and

other input from the BEC. Clearly gives best result about the

BEC structure reduces the number of gate counts used in the

Fig 5: New modified 16-bit SQRT-CSLA

Fig 6: Simulation result of regular CSLA

14

INTERNATIONAL JOURNAL FOR TRENDS IN ENGINEERING & TECHNOLOGY

VOLUME 4 ISSUE 2 APRIL 2015 - ISSN: 2349 - 9303

Fig 7: simulation result of new modified SQRT-CSLA

Table II: Area, delay results compared with conventional method

VIII. CONCLUSION

Special Issue on National Conference on

Information and Communication (NCIC'13).

Volume III.

In this paper, the new 16-bit modified square root carry

select adder designed replacement of ripple carry adder by

binary to excess one converter (BEC) in existing method.

VHSIC Hardware Description Language (VHDL) codes

are done by use of Xilinx ISE 8.1i/ Modelsim SE 6.5 and

simulation waveform and design reports are clearly

indicating this design is an efficient to lesser delay and

power. Modified SQRT-CSLA design gives an efficient

and fast carry select adder than the existing adder because

of this design produced overall delay of 25.209 ns, power

of 72 ns and the total logic gates are used in design to 248

gate counts.

[2].Chan Gagandeep Singh Gill and Chakshu Goel

(March 2014), Carry Select Adder-review,

International Journal of

Emerging

Trends in Engineering and Development Issue 4,

Vol.2.

[3]. Ishita Banerjee (Nov-Dec 2013), High Speed, Low

Power, Area Efficient Mux-Add and Based

Implementation of Carry Select Adder. Ishita

Banerjeeet al Int. Journal of Engineering Research

and Applications .ISSN : 2248-9622, Vol. 3, Issue 6

pp.75-78.

REFERENCES

[1]. Anand Selvakumar.P and Hemalatha. K. L (August

2013)., An Efficient Logic

Test Structure for

Low Power Testing, International Journal of

Computer Applications in Engineering Sciences

[4]. Itamar Levi, Alexander Belenky, and Alexander

Fish (may 2014), Logical Effort for CMOS-Based

Dual Mode Logic Gates, IEEE transactions on

15

INTERNATIONAL JOURNAL FOR TRENDS IN ENGINEERING & TECHNOLOGY

VOLUME 4 ISSUE 2 APRIL 2015 - ISSN: 2349 - 9303

very large scale integration (VLSI) systems, vol. 22,

no. 5.

Communication technology, IJRCCT, ISSN 22785841, Vol 1, Issue 6.

[5]. Negowda.C, and Dr. Aswatha A. R (July 2013),

Power Optimized Full Adder Architecture.

International Journal of Emerging Technology and

Advanced Engineering, ISSN 2250-2459, ISO

9001:2008 Certified Journal, Volume 3, Issue 7.

[11]. Sreenivasulu.P, Dr. Srinivasa Rao.K, Malla Reddy

and Dr.Vinay Babu.A (Mar-Apr 2012), Energy and

Area efficient Carry Select Adder on a reconfigurable

hardware. International Journal of Engineering

Research and Applications (IJERA) ISSN: 2248-9622.

www.ijera.com Vol. 2, Issue 2, pp.436-440.

[6]. Daniel R. Llamocca-Obregon, A core design to

obtain square root based on a non-restoring

algorithm, Av. Universitararia S/N Cdra.18-Lima

32,Peru.

[12]. Senthilkumar.A and Kousalya devi.A (April 2013),

VLSI Implementation of an efficient Carry Select

Adder Architecture, International Journal Of

Advance

Research

In

Science

And

Engineering,IJARSE, Vol. No.2, Issue No.4 .

[7]. Pravin adlin.J and Palaniappan.C (Mar. - Apr. 2013),

An Area and Delay Efficient Csla Architecture,

IOSR Journal of Electronics and Communication

Engineering (IOSR-JECE) e-ISSN: 2278-2834,pISSN: 2278-8735. Volume 5, Issue 3, PP 20-25.

[13]. Saranya.K (January 2013), Low Power and AreaEfficient Carry Select Adder, International Journal of

Soft Computing and Engineering (IJSCE), ISSN:

2231-2307, Volume-2, Issue-6.

[8]. Pallavi.CH, swathi.V(June 2013), An Efficient Carry

Select Adder with Reduced Area Application,

International Journal of Computer Engineering

Science (IJCES) Volume 3, Issue 6 , ISSN :

2250:3439.

[14]. Subha.R and Durga.G (2013), Design of Digital

Filter using Low Power and Area Efficient SQRT

CSLA.

International Journal

of

Computer

Applications (0975 8887) National conference on

VSLI and Embedded systems.

[9]. Rongali Aneel Kumar, Srinivasa Rao.B.N, Prasad Rao.R

(September 2012)., Design and analysis of 16-bit

Full Adder using Spartan-3 FPGA, International

Journal of Advanced Research in Computer

Engineering & Technology (IJARCET) Volume 1,

Issue 7.

[15]. Yogayata, Shrivastava, Tarun verma and rita jain

(April 2014), Design and implementation of low

power high speed 32-bit hcsa. International Journal

of VLSI and Embedded Systems-IJVES, Vol 05,

Article 04292; ISSN: 2249 6556.

[16]. Zhanfeng Zhang (December

Theory Based on Half Adder

CMOS Gates. I.J. Image,

Processing, 2010, 2, 11-17

MECS.

[10]. RatnaMala.T, Vinay Kumar.R and Chandra Kala.T

(November 2012), Design and Verification of Area

Efficient High-Speed Carry Select Adder.

International Journal of Research in Computer and

16

2010), A New Adder

and Implementation in

Graphics and Signal

Published Online in

Das könnte Ihnen auch gefallen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- A Secure Cloud Storage System With Data Forwarding Using Proxy Re-Encryption SchemeDokument4 SeitenA Secure Cloud Storage System With Data Forwarding Using Proxy Re-Encryption SchemeijtetjournalNoch keine Bewertungen

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Service Level Grade Using Web Ranking Framework For Web Services in Cloud ComputingDokument5 SeitenService Level Grade Using Web Ranking Framework For Web Services in Cloud ComputingijtetjournalNoch keine Bewertungen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- Segmentation and Classification of Lung Nodule in Chest Radiograph ImageDokument4 SeitenSegmentation and Classification of Lung Nodule in Chest Radiograph ImageijtetjournalNoch keine Bewertungen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- An Efficient System of Electrocardiogram Data Acquisition and Analysis Using LABVIEWDokument5 SeitenAn Efficient System of Electrocardiogram Data Acquisition and Analysis Using LABVIEWijtetjournalNoch keine Bewertungen

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Improving Efficiency of Security in Multi-CloudDokument4 SeitenImproving Efficiency of Security in Multi-CloudijtetjournalNoch keine Bewertungen

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Analysis of Leakage Current Calculation For Nanoscale MOSFET and FinFETDokument3 SeitenAnalysis of Leakage Current Calculation For Nanoscale MOSFET and FinFETijtetjournalNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Fingerprint Based Smart Pay and Accident Alert SystemDokument4 SeitenFingerprint Based Smart Pay and Accident Alert SystemijtetjournalNoch keine Bewertungen

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Certain Investigations On Security Issues in Smart Grid Over Wireless CommunicationDokument4 SeitenCertain Investigations On Security Issues in Smart Grid Over Wireless CommunicationijtetjournalNoch keine Bewertungen

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Space Vector of Three Phase Three Level Neutral Point Clamped Quasi Z Source InverterDokument7 SeitenSpace Vector of Three Phase Three Level Neutral Point Clamped Quasi Z Source InverterijtetjournalNoch keine Bewertungen

- Effectiveness of Increased and Efficient Sine Wave in PWM ArchitectureDokument4 SeitenEffectiveness of Increased and Efficient Sine Wave in PWM ArchitectureijtetjournalNoch keine Bewertungen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Surveillance Robot For Military Application Using ARMDokument6 SeitenSurveillance Robot For Military Application Using ARMijtetjournalNoch keine Bewertungen

- Enhancing The Privacy Protection of The User Personalized Web Search Using RDFDokument5 SeitenEnhancing The Privacy Protection of The User Personalized Web Search Using RDFijtetjournalNoch keine Bewertungen

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Quality Prediction in Fingerprint CompressionDokument5 SeitenQuality Prediction in Fingerprint CompressionijtetjournalNoch keine Bewertungen

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- ARM Based Climate Controlled Wearable JacketDokument4 SeitenARM Based Climate Controlled Wearable JacketijtetjournalNoch keine Bewertungen

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- Robust Human Emotion Analysis Using LBP, GLCM and PNN ClassifierDokument6 SeitenRobust Human Emotion Analysis Using LBP, GLCM and PNN ClassifierijtetjournalNoch keine Bewertungen

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Text Categorization Using Improved K Nearest Neighbor AlgorithmDokument4 SeitenText Categorization Using Improved K Nearest Neighbor AlgorithmijtetjournalNoch keine Bewertungen

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Dual - MPPT Control of A Photovoltaic SystemDokument6 SeitenDual - MPPT Control of A Photovoltaic SystemijtetjournalNoch keine Bewertungen

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- Two Step Design For Personal Authentication Using Finger Vein Recognition and GSM TechnologyDokument5 SeitenTwo Step Design For Personal Authentication Using Finger Vein Recognition and GSM TechnologyijtetjournalNoch keine Bewertungen

- Dual - MPPT Control of A Photovoltaic SystemDokument6 SeitenDual - MPPT Control of A Photovoltaic SystemijtetjournalNoch keine Bewertungen

- Weibull Distribution Based Channel Prototype For Decrease of Rain Attenuation in Satellite Communication Links Beyond 10GHzDokument4 SeitenWeibull Distribution Based Channel Prototype For Decrease of Rain Attenuation in Satellite Communication Links Beyond 10GHzijtetjournalNoch keine Bewertungen

- Text Categorization Using Improved K Nearest Neighbor AlgorithmDokument4 SeitenText Categorization Using Improved K Nearest Neighbor AlgorithmijtetjournalNoch keine Bewertungen

- Two Step Design For Personal Authentication Using Finger Vein Recognition and GSM TechnologyDokument5 SeitenTwo Step Design For Personal Authentication Using Finger Vein Recognition and GSM TechnologyijtetjournalNoch keine Bewertungen

- Secure Transmission of Patient Physiological Information in Point of Care SystemDokument6 SeitenSecure Transmission of Patient Physiological Information in Point of Care SystemijtetjournalNoch keine Bewertungen

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Smart Sensor Configuration For Security System Automation Using FPGADokument4 SeitenSmart Sensor Configuration For Security System Automation Using FPGAijtetjournalNoch keine Bewertungen

- Efficient Utility Based Infrequent Weighted Item-Set MiningDokument5 SeitenEfficient Utility Based Infrequent Weighted Item-Set MiningijtetjournalNoch keine Bewertungen

- EETA: Enhancing and Estimating The Transformation of Attacks in Android ApplicationDokument4 SeitenEETA: Enhancing and Estimating The Transformation of Attacks in Android ApplicationijtetjournalNoch keine Bewertungen

- A New Visual Cryptography Technique For Color ImagesDokument5 SeitenA New Visual Cryptography Technique For Color ImagesijtetjournalNoch keine Bewertungen

- NAVMC 3500.35A (Food Services)Dokument88 SeitenNAVMC 3500.35A (Food Services)Alexander HawkNoch keine Bewertungen

- I&C Engineer or Automation EngineerDokument3 SeitenI&C Engineer or Automation Engineerapi-79304330Noch keine Bewertungen

- STAR Worksheet Interviewing SkillsDokument1 SeiteSTAR Worksheet Interviewing SkillsCharity WacekeNoch keine Bewertungen

- HTTP - WWW - Aphref.aph - Gov.au - House - Committee - Pjcis - nsl2012 - Additional - Discussion Paper PDFDokument61 SeitenHTTP - WWW - Aphref.aph - Gov.au - House - Committee - Pjcis - nsl2012 - Additional - Discussion Paper PDFZainul Fikri ZulfikarNoch keine Bewertungen

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Configuring Nagios On Client For OSSIMDokument10 SeitenConfiguring Nagios On Client For OSSIMMaixender NganareNoch keine Bewertungen

- Table of Specification ENGLISHDokument2 SeitenTable of Specification ENGLISHDonn Abel Aguilar IsturisNoch keine Bewertungen

- Db2 Compatibility PDFDokument23 SeitenDb2 Compatibility PDFMuhammed Abdul QaderNoch keine Bewertungen

- Moment Baseplate DesignDokument10 SeitenMoment Baseplate DesignNeil JonesNoch keine Bewertungen

- Key Note Units 3-4Dokument4 SeitenKey Note Units 3-4Javier BahenaNoch keine Bewertungen

- Career DevelopmentDokument23 SeitenCareer DevelopmentHaris Khan100% (1)

- Excellence Range DatasheetDokument2 SeitenExcellence Range DatasheetMohamedYaser100% (1)

- Science 10 3.1 The CrustDokument14 SeitenScience 10 3.1 The CrustマシロIzykNoch keine Bewertungen

- GR 5 Unit Plan 18-19 Art Warli ArtDokument4 SeitenGR 5 Unit Plan 18-19 Art Warli ArtSanjay RautNoch keine Bewertungen

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Energy Efficient Solar-Powered Street Lights Using Sun-Tracking Solar Panel With Traffic Density Monitoring and Wireless Control SystemDokument9 SeitenEnergy Efficient Solar-Powered Street Lights Using Sun-Tracking Solar Panel With Traffic Density Monitoring and Wireless Control SystemIJRASETPublicationsNoch keine Bewertungen

- DELA PENA - Transcultural Nursing Title ProposalDokument20 SeitenDELA PENA - Transcultural Nursing Title Proposalrnrmmanphd0% (1)

- Failure Reporting, Analysis, and Corrective Action SystemDokument46 SeitenFailure Reporting, Analysis, and Corrective Action Systemjwpaprk1100% (1)

- The Effect of Reward Practices on Employee Performance in Ethio TelecomDokument29 SeitenThe Effect of Reward Practices on Employee Performance in Ethio TelecomZakki Hersi AbdiNoch keine Bewertungen

- Lenovo IdeaPad U350 UserGuide V1.0Dokument138 SeitenLenovo IdeaPad U350 UserGuide V1.0Marc BengtssonNoch keine Bewertungen

- Group 7 Scope StatementDokument17 SeitenGroup 7 Scope Statementapi-335995226100% (4)

- Remapping The Small Things PDFDokument101 SeitenRemapping The Small Things PDFAme RaNoch keine Bewertungen

- Liberal Theory: Key Aspects of Idealism in International RelationsDokument11 SeitenLiberal Theory: Key Aspects of Idealism in International RelationsArpit JainNoch keine Bewertungen

- McCann MIA CredentialsDokument20 SeitenMcCann MIA CredentialsgbertainaNoch keine Bewertungen

- The Stolen Bacillus - HG WellsDokument6 SeitenThe Stolen Bacillus - HG Wells1mad.cheshire.cat1Noch keine Bewertungen

- Roman Questions II PDFDokument738 SeitenRoman Questions II PDFjlinderski100% (3)

- SiargaoDokument11 SeitenSiargaomalouNoch keine Bewertungen

- Phase Domain Modelling of Frequency Dependent Transmission Lines by Means of An Arma ModelDokument11 SeitenPhase Domain Modelling of Frequency Dependent Transmission Lines by Means of An Arma ModelMadhusudhan SrinivasanNoch keine Bewertungen

- Dompet Digital Di Kota SemarangDokument10 SeitenDompet Digital Di Kota SemarangRikson TandelilinNoch keine Bewertungen

- Neptune Sign House AspectDokument80 SeitenNeptune Sign House Aspectmesagirl94% (53)

- Tiger Facts: Physical Characteristics of the Largest CatDokument14 SeitenTiger Facts: Physical Characteristics of the Largest CatNagina ChawlaNoch keine Bewertungen

- Date ValidationDokument9 SeitenDate ValidationAnonymous 9B0VdTWiNoch keine Bewertungen

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeVon EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeBewertung: 5 von 5 Sternen5/5 (8)

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionVon EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionBewertung: 4.5 von 5 Sternen4.5/5 (542)

- High Performance Loudspeakers: Optimising High Fidelity Loudspeaker SystemsVon EverandHigh Performance Loudspeakers: Optimising High Fidelity Loudspeaker SystemsBewertung: 4 von 5 Sternen4/5 (1)

- The Rare Metals War: the dark side of clean energy and digital technologiesVon EverandThe Rare Metals War: the dark side of clean energy and digital technologiesBewertung: 5 von 5 Sternen5/5 (2)

- C++ Programming Language: Simple, Short, and Straightforward Way of Learning C++ ProgrammingVon EverandC++ Programming Language: Simple, Short, and Straightforward Way of Learning C++ ProgrammingBewertung: 4 von 5 Sternen4/5 (1)

- Off-Grid Projects: Step-by-Step Guide to Building Your Own Off-Grid SystemVon EverandOff-Grid Projects: Step-by-Step Guide to Building Your Own Off-Grid SystemNoch keine Bewertungen

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionVon EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionBewertung: 4 von 5 Sternen4/5 (331)