Beruflich Dokumente

Kultur Dokumente

Dynamic Partial Reconfiguration

Hochgeladen von

Jinesh KbOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Dynamic Partial Reconfiguration

Hochgeladen von

Jinesh KbCopyright:

Verfügbare Formate

i

Department of Electronics & Communication Engineering

National Institute of Technology Calicut

CERTIFICATE

This is to certify that this seminar report entitled Partial Dynamic Reconfiguration in FPGA is a bonafide record of the seminar presented by Jinesh K.B ,

Roll No. M130121EC, during Winter 2014 in partial fulfilment of the requirement

for the award of Degree of Master of Technology in Microelectronics and VLSI

Design by the National Institute of Technology Calicut, India.

Faculty In-Charge of Seminar

Department of Electronics &

Communication Engineering

N.I.T Calicut

Date:

Partial Dynamic Reconfiguration in FPGA

ii

Abstract

Partial dynamic reconfiguration is the capability to modify the functionality configured on the FPGA while the chip is running. This will reduce the configuration

time and save memory as the partial configuration files are smaller than the entire

device bit stream. There are two styles of partial reconfiguration of FPGA: module

based and difference based. The difference based partial reconfiguration can be

used when a small change is to be made to the design, like in case of changing

the look up table equations or dedicated memory blocks contents. Module based

partial reconfiguration permits to reconfigure distinct modular parts of the design

while rest of the device remains in active mode. These modules are referred as

reconfigurable modules and bus macros are used for the communication between

the reconfigurable and static modules. Early Access Partial Reconfiguration is the

latest design flow used for partial reconfiguration .In this the bus macro used is

based on slice rather than tri-buffer as used in former designs and also here the

partial reconfiguration unit can be of any rectangular size.

Department of Electronics and Communication, National Institute of Technology Calicut

iii

Partial Dynamic Reconfiguration in FPGA

Contents

1

Introduction

Different styles of DPR

2.1 Difference based DPR . . . . . . . . . . . . . . . . . . . . . . .

2.2 Module based DPR . . . . . . . . . . . . . . . . . . . . . . . . .

2

2

3

Reconfiguration Modes

Architectural developments

4.1 Bus macro replace TBUFs . . . . . . . . . . . . . . . . . . . . .

4.2 Unit of reconfiguration granularity . . . . . . . . . . . . . . . . .

4.3 Upgraded ICAP . . . . . . . . . . . . . . . . . . . . . . . . . . .

7

7

8

8

Early Access PR design flow

5.1 Design phase 1: Design partitioning . . . . .

5.2 Design phase 2: Floorplanning and Budgeting

5.3 Design phase 3: Top level implementation . .

5.4 Design phase 4: Static implementation . . . .

5.5 Design phase 5: PRM implementation . . . .

5.6 Design phase 6: Merge . . . . . . . . . . . .

. .

.

. .

. .

. .

. .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

9

10

10

11

11

11

11

Benefits

12

Conclusion

13

Bibliography

14

Department of Electronics and Communication, National Institute of Technology Calicut

Partial Dynamic Reconfiguration in FPGA

iv

List of Figures

2.1

Module based DPR . . . . . . . . . . . . . . . . . . . . . . . . .

3.1

Reconfiguration modes . . . . . . . . . . . . . . . . . . . . . . .

4.1

4.2

Bus macro implemented by a pair of CLB . . . . . . . . . . . . .

Reconfigurable region in old FPGAs . . . . . . . . . . . . . . . .

7

8

5.1

EAPR design flow . . . . . . . . . . . . . . . . . . . . . . . . . .

Department of Electronics and Communication, National Institute of Technology Calicut

Partial Dynamic Reconfiguration in FPGA

Chapter 1

Introduction

Partial reconfigurability refers to the ability of a programmable device such as

FPGA to change the customized design of selected areas by loading different configurations. According to the way this reconfiguration is done, the reconfiguration

can be classified as static and dynamic. The former is the most common and simplest reconfiguration also reffered as compile time reconfiguration.In this approach

there will be separe bit stream for each operation and the device stops during the

reconfiguration time and starts again with the new design when all the partial modules are loaded.Dynamic Partial Reconfiguration allows the modification of an operating FPGA design by loading a partial configuration file, usually a partial BIT

file. After a full BIT file configures the FPGA, partial BIT files can be downloaded

to modify reconfigurable regions in the FPGA without compromising the integrity

of the applications running on those parts of the device that are not being reconfigured. When compared to one bit stream of a non partial reconfiguration implementation,smaller modules resulting in smaller bit stream files allow an FPGA to

implement many more hardware configurations with greater speed under similar

storage requirements.

As long as the system designed meets one of the following questions,it can be

resolved through Dynamic PR:

Systems resource requirement is greater than FPGAs available resourses

System designed has multiple mutually exclusive tasks

Reduce system energy consumption

System has temporarily no need to hardware resources.

Department of Electronics and Communication, National Institute of Technology Calicut

Partial Dynamic Reconfiguration in FPGA

Chapter 2

Different styles of DPR

Xilinx suggests two basic styles of dynamic reconfiguration in a single FPGA :

Difference based and Module based.

2.1

Difference based DPR

Difference based DPR is very efficient for small designs.The basic idea behind this

method is ,suppose if we have two designs A and B.Then instead of creating full

configuration for the two designs,here it will make a full configuration for one design A and compare its configuration frame by frame and will create a partial bit

stream which will represent the difference between the the two designs.So instead

of saving and reconfiguring a full design now we have a small partial reconfiguration bit stream.This will reduce the storage space required and also the speed of

reconfigurability also increases significantly.Using this methos we can modify

LUTs equations

BRAM contents and BRAM write modes

I/O standards and pull-ups or pull-downs on external pins

Muxes

Flip flop initialization and reset values

The main problem with this method is that this cannot ne automated.We have

to manualy analyse and find which LUT,BRAM or MUX have to be modified and

make changes in the FPGA editor.Once this is done the BITGen program is run to

generate a partial bit stream representing the difference between the initial and new

Department of Electronics and Communication, National Institute of Technology Calicut

Partial Dynamic Reconfiguration in FPGA

designs.Next this partial bit stream will be downloaded to FPGA to implement the

new design.These bit streams being smaller can be loaded quickly and easily by

the software.All that is required is an understanding of how to make logic changes

using the FPGA editor.

2.2

Module based DPR

Module based partial reconfiguration is used to make large changes in the implemented design.Unlike difference based method here the entire design is devided

into a static logic and one or more dynamic logics.These dynamic logic will be

representing different mutually exclusive functions and thus by implementing a

time shared multiplexing of hardware.This will save the silicon area by allowing

multiple configuration to be swapped in or out of the device.

Figure 2.1: Module based DPR

The reconfigurable parts A1,A2,A3 etc are independent parts of the design

which need not be active all the time.This is besed on the assumption thal these

doesnt need to be operated in parallel.To ensure the communication across the dynamic module boundaries special bus macros has to be prepared.These will work as

a fixed communication interface port between the modules.They are implemented

using Configurable logic blocks(CLB) of FPGA.Module based partial reconfiguration requires to perform it in a step by step process.First the static module should

be isolated from the dynamic modules,so that static design functionality will not

be effected during the process of reconfiguration.The static logic must be designed

Department of Electronics and Communication, National Institute of Technology Calicut

Partial Dynamic Reconfiguration in FPGA

so that the device will work in some mode even when no dynamic logics are implemented.Then reconfiguration have to be made in the dynamic part.And again

the communication port (Bus macro)have to be enabled.Now the FPGA will work

based on the new design.

Department of Electronics and Communication, National Institute of Technology Calicut

Partial Dynamic Reconfiguration in FPGA

Chapter 3

Reconfiguration Modes

Reconfiguration mode is an important parameter for dynamic reconfiguration since

it have direct impact on the speed of reconfiguration.Depending on method it is

classified as external or internal.

Figure 3.1: Reconfiguration modes

Department of Electronics and Communication, National Institute of Technology Calicut

Partial Dynamic Reconfiguration in FPGA

Externaly

External reconfiguration can be done using

Serial configuration port

JTAG

Select map port

In this both serial configuration port and JTAG will support a data width of 1

bit and select map supports a data width of 32 bits.

Internaly

Internal reconfiguration can be done using internal configuration access port(ICAP).

ICAP is an internal select map port which supports a data width of 32 bits.Not all

devices supports internal reconfiguration.Internal reconfiguration was made available from Virtex II devices.For internal reconfigurable FPGA there will be an inbuilt microprocessor which enables a user to write software programs for an embedded processor that modifies the circuit structure and functionality during the

circuits operation.With this feature the process of dynamic reconfiguration can be

automated by storing the bit stream files in a memory accesible to the proccessor.So

it is also called as self reconfigurable FPGAs.

The speed of configuration is directly related to the size of the partial BIT file

and the bandwidth of the configuration port. The different configuration ports in

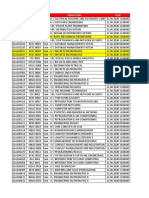

Virtex devices and maximum bandwidths are shown in Table 3.1.

Table 3.1: Maximum Bandwidths for Configuration Ports in Virtex Architectures

Department of Electronics and Communication, National Institute of Technology Calicut

Partial Dynamic Reconfiguration in FPGA

Chapter 4

Architectural developments

4.1

Bus macro replace TBUFs

TBUFs(Tri-state buffers) were used as a communication interface port between

a dynamic module and a static module.These TBUFs were in built FPGA resource available in the older FPGA.And due to its predetermined location and

since it is dispersed across the architecture its use is discouraged in the newer

FPGAs.Bus macro comes as an alterative to the TBUFs.These are implemented

using CLBs.Each CLB consist of four slices and a single slice can implement two

unidirectional connections.Hence a pair of CLB can implement 8 unidirectional

connections succesfully.Since CLBs are the basic elements of FPGA it is available

in abundent and gives maximum freedom to place it.

Figure 4.1: Bus macro implemented by a pair of CLB

Department of Electronics and Communication, National Institute of Technology Calicut

Partial Dynamic Reconfiguration in FPGA

4.2

Unit of reconfiguration granularity

In the older FPGAs the smallest reconfigurable region was 1 CLB wide and the full

device column.So even though our design is small we cant utilise the resource in

the recongigurable region for any other purpose.

Figure 4.2: Reconfigurable region in old FPGAs

In the newer FPGAs this restriction of full device height has been removed and

now devices support different granularities.Smallest reconfigurable unit of some of

the device is given below

Base regions in 7 series FPGAs are 50 CLBs high by 1 CLB wide.

Base regions in Virtex-6 FPGAs are 40 CLBs high by 1 CLB wide.

Base regions in Virtex-5 FPGAs are 20 CLBs high by 1 CLB wide.

Base regions in Virtex-4 FPGAs are 16 CLBs high by 1 CLB wide

4.3

Upgraded ICAP

Internal configuration access port(ICAP) was first introduced in the Virtex II and

Virtex II pro devices.These ports then provided 8 bit data bus for input and output.In the new FPGAs,seven series and from Virtex 4 it supports a data bus of

32 bit wide for both input and output and runs at a speed of 100 Mhz.This will

significantly increase the speed of reconfiguration.

Department of Electronics and Communication, National Institute of Technology Calicut

Partial Dynamic Reconfiguration in FPGA

Chapter 5

Early Access PR design flow

Early access partial reconfiguration(EAPR) was introduced by Xilinx in March

2006 along with the introduction os slice based bus macros.Implementing a dynamically reconfigurable system on an FPGA introduces several additional steps

in the design process.The normal FPGA flow involves a single pass through the

implementation tools (NGDBuild, MAP and Route), while the PR design flow involves implementing the base design and each PRM separately, followed by a final

merge step. A complete design flow is shown in figure 1.

Figure 5.1: EAPR design flow

Department of Electronics and Communication, National Institute of Technology Calicut

Partial Dynamic Reconfiguration in FPGA

10

There are two main difference between the module based PR and EAPR .First

one is the removel of restrictions on devices to be reconfigured in whole column

only.And the second major change is that it allows the signals in static design to

cross the dynamic region without the use of bus macro.This dramaticallyimproves

the timing performance and simplifies the process of creating PR.

5.1

Design phase 1: Design partitioning

The designer have to first devide his entire design into a static part and one or

more dynamic part.Each dynamic part will be implementing mutually exclusive

functions.At the end of this phase a series of HDL files will be generated,

1. A TOP level file:which contains

All global logic such as clock primitives

IO port instantiations

Bus macro instantiations

Signal declarations

Base design instantiations and

PR module instantiations

2. HDL file for the static portion of the design

3. HDL file for each of the PR module

5.2

Design phase 2: Floorplanning and Budgeting

The purpose of this phase is to determine the lacation and size of PR module and

to lock down the placement of bus macros.This can be done manualy but is complex and time consuming.There are automated tools available for this like PlanAhead.PlanAhead is a Xilinx tool for the design and analysis of circuits.PlanAhead

uses the concepr of physical blocks.Each PRmodule will be assigned as a physical

block.And it provides the resource utilised when its size is varied or on changing

location.From this the best case would be selected and finalize the position and

size of PR module.Once the PR location is fixed the bus macro will be placed in

between the PR module and neighbouring modules.

Department of Electronics and Communication, National Institute of Technology Calicut

Partial Dynamic Reconfiguration in FPGA

5.3

11

Design phase 3: Top level implementation

From the first phase the HDL and user constraint file of the top level module is

available and in this phase that have to be converted to a native Xilinx format.This

is done by running the tool NGD Build.This will create a TOP level context file

which contains information on

IO placement

Clock resources

Bus macro placement

Static and dynamic module placement

5.4

Design phase 4: Static implementation

From the preceding stages the HDL and user constraint file for the static logic is

available, and in this phase it has to perform place and route of the design.This is

done by running NGDbuild program referencing to the TOP level context file.Finaly

MAP and PAR(place and route) are run to get a placed and routed file for the static

design.

5.5

Design phase 5: PRM implementation

This stage is very similar to the previous static implementation phase.Here all the

PR modules will be implemented seperately and kept in different files.

5.6

Design phase 6: Merge

The final implementation phase is the merge phase.In this phase a complete design is made from the static design and each PR designs.Corresponding to each PR

module a complete design will be made by combining with the static design.There

are tools available in the EAPR,they are PR varify and PR assemble.PR varify

will generate a merged full bit stream and partial bit stream for each PR module.PR assemble is ued in case where there are multiple PR modules and this will

also generate a blanking bit streams for the PR regions which will be used when

no PR module is required and this will reduce the power consumption.

Department of Electronics and Communication, National Institute of Technology Calicut

Partial Dynamic Reconfiguration in FPGA

Chapter 6

Benefits

Reduce Cost and Board Space.

Increase Deployed System Flexibility.

Reduce Power Consumption.

Improves FPGA fault tolerance.

Accelerates configurable computing.

Reduces bitstream storage requirements.

Department of Electronics and Communication, National Institute of Technology Calicut

12

Partial Dynamic Reconfiguration in FPGA

13

Chapter 7

Conclusion

Dynamic partial reconfiguration offers new possibilities for designs with FPGAs

with reduced size,power consumption.The communication between reconfiguration and static module is realized by slice based on bus macro, it is better than the

traditional TBUF-based bus macro there by incresing communication efficiency

and signal control. And the ICAP enables to design intelligent automated DPR

systems which implements the time-sharing multiplexing of hardware resources,

and improve the system resource utilization effectively.

Department of Electronics and Communication, National Institute of Technology Calicut

Partial Dynamic Reconfiguration in FPGA

14

Bibliography

[1] Patrick Lysaght, Brandon Blodget, Jeff Mason, Jay Young, Brendan Bridgford Invited paper: Enhanced architectures, design methodologies and cad

tools for dynamic reconfiguration of xilinx fpgas International Conference

on Field Programmable Logic and Applications, 2006. FPL 06.

[2] Partial ReconfigurationUser Guide, Xilinx user guide UG702,April

26,2013

[3] Two Flows for Partial Reconfiguration: Module Based orDifference Based,

Xilinx Application Note XAPP290, December 3, 2007

[4] David Dye Partial Reconfiguration of Xilinx FPGAs Using ISE Design

Suite , Xilinx White paper WP374 (v1.2).May 30,2012.

[5] Xie Di, Shi Fazhuang, Deng Zhantao, He Wei A Design Flow for FPGA

Partial Dynamic Reconfiguration 2012 Second International Conference on

Instrumentation & Measurement, Computer, Communication and Control.

[6] Wang Lie,Wu Feng-yan.Dynamic Partial Reconfiguration in FPGAs, Third

International Symposium on Intelligent Information Technology Application,2009.

[7] Trailokya Nath Sasamal, Rajendra Prasad, Module Based and Difference

Based Implementation of Partial Reconfiguration on FPGA: A Review International Journal of Engineering Research and Applications (IJERA), Vol.

1, Issue 4, pp.1898-1903

Department of Electronics and Communication, National Institute of Technology Calicut

Das könnte Ihnen auch gefallen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Dense NetDokument28 SeitenDense NetFahad RazaNoch keine Bewertungen

- Grand Vitara 2005Dokument35 SeitenGrand Vitara 2005PattyaaNoch keine Bewertungen

- CJR Fisika Umum IDokument17 SeitenCJR Fisika Umum IveronikaNoch keine Bewertungen

- Naskah Soal PeroranganDokument16 SeitenNaskah Soal PeroranganRiza FatimahNoch keine Bewertungen

- Tas 5731Dokument60 SeitenTas 5731charly36Noch keine Bewertungen

- Website Catalog MOTORS v2 PDFDokument8 SeitenWebsite Catalog MOTORS v2 PDFИгорь КернякевичNoch keine Bewertungen

- Latest Research Papers On Manet SecurityDokument7 SeitenLatest Research Papers On Manet Securitygz9g97haNoch keine Bewertungen

- Ground PlaneDokument1 SeiteGround Planeaeronautical rajasNoch keine Bewertungen

- Proposal Form NagDokument1 SeiteProposal Form Nagnitheesh kumarNoch keine Bewertungen

- Ec210b Pub20021241-I PDFDokument1.046 SeitenEc210b Pub20021241-I PDFCholif 'oliph' Fadhilah100% (16)

- Squares and Square Roots Chapter Class ViiiDokument24 SeitenSquares and Square Roots Chapter Class ViiiManas Hooda100% (1)

- Construction Companies in AlbaniaDokument17 SeitenConstruction Companies in AlbaniaPacific HRNoch keine Bewertungen

- Pre-Test First QTR 2022-2023Dokument3 SeitenPre-Test First QTR 2022-2023anna marie mangulabnanNoch keine Bewertungen

- OKM 54MP FlyerDokument1 SeiteOKM 54MP FlyerJohnsonNoch keine Bewertungen

- Stock+List 6ct8.3g2 Esn#30549237 Cpl#2218 GeneradorDokument34 SeitenStock+List 6ct8.3g2 Esn#30549237 Cpl#2218 GeneradorAlexis SanchezNoch keine Bewertungen

- Pigging Training Course Mod 7 Rev 1Dokument26 SeitenPigging Training Course Mod 7 Rev 1Suparerk Sirivedin100% (1)

- Infineon IRFZ44N DataSheet v01 - 01 ENDokument9 SeitenInfineon IRFZ44N DataSheet v01 - 01 ENIkram RidhoNoch keine Bewertungen

- ENEE 222 Signals and Systems: Spring 2021 - Problem Set 7 - Due 4/13/2021Dokument2 SeitenENEE 222 Signals and Systems: Spring 2021 - Problem Set 7 - Due 4/13/2021Tiana JohnsonNoch keine Bewertungen

- Lecture2 v1Dokument69 SeitenLecture2 v1c.ronaldo2012777Noch keine Bewertungen

- Chemical Resistance TableDokument6 SeitenChemical Resistance TableEdgarDavidDiazCamposNoch keine Bewertungen

- Iron FistDokument2 SeitenIron FistVictor PileggiNoch keine Bewertungen

- Science BiologyDokument76 SeitenScience BiologynaninanyeshNoch keine Bewertungen

- DysphagiaDokument4 SeitenDysphagiaMicaNoch keine Bewertungen

- Staff Code Subject Code Subject Data FromDokument36 SeitenStaff Code Subject Code Subject Data FromPooja PathakNoch keine Bewertungen

- PricelistDokument4 SeitenPricelistMAYMART CASABANoch keine Bewertungen

- DLP MonsoonDokument2 SeitenDLP MonsoonjennifertariaoNoch keine Bewertungen

- 7MBR75VB120-50: IGBT MODULE (V Series) 1200V / 75A / PIMDokument8 Seiten7MBR75VB120-50: IGBT MODULE (V Series) 1200V / 75A / PIMDanielle ButlerNoch keine Bewertungen

- Traffic Cases in GSMDokument18 SeitenTraffic Cases in GSMkamal100% (1)

- Motion of A Simple Pendulum in A FluidDokument16 SeitenMotion of A Simple Pendulum in A FluidGokul JeevaNoch keine Bewertungen