Beruflich Dokumente

Kultur Dokumente

HDLCoderInterface WhitePaper Final

Hochgeladen von

Adelmo Henrique SantanaCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

HDLCoderInterface WhitePaper Final

Hochgeladen von

Adelmo Henrique SantanaCopyright:

Verfügbare Formate

Model-Based Design for Altera

FPGAs Using Simulink, HDL Coder,

and Altera DSP Builder Advanced

Blockset

By Kiran Kintali and Yongfeng Gu

W h i t e Pa p e r

Model-Based Design for Altera FPGAs Using Simulink, HDL Coder, and Altera DSP Builder Advanced Blockset

Summary

This document describes how HDL Coder from MathWorks can be used with Altera DSP Builder in

an integrated FPGA workflow. We use an example to show how designers can integrate models built

with DSP Builder Advanced Blockset into a Simulink model, and how HDL Coder can generate HDL

code for the complete design. This capability allows designers to reuse existing DSP Builder models

when using HDL Coder to create new designs, or to incorporate target-optimized Altera IP blocks

created for use with HDL Coder within Simulink models.

Introduction

MATLAB and Simulink for Model-Based Design provide signal, image, and video processing engineers with a development platform that spans design, modeling, simulation, code generation, and

implementation. Engineers who use Model-Based Design to target FPGAs or ASICs can design and

simulate systems with MATLAB, Simulink, and Stateflow and then generate bit-true, cycle-accurate,

synthesizable Verilog and VHDL code using HDL Coder.

Alternatively, engineers who specifically target Altera FPGAs can use DSP Builder, a plug-in to

Simulink code generation software, to generate synthesizable hardware description language (HDL)

code mapped to pre-optimized Altera implementations. DSP Builder includes the DSP Builder

Advanced Blockset, a high-level synthesis technology that optimizes the high-level, untimed netlists

into low-level, pipelined hardware for the target Altera FPGA device and desired clock rate.

Some projects benefit from implementing a workflow that combines the native Simulink workflow,

device-independent code, and code readability offered by HDL Coder, with Altera-specific features

and optimizations offered by DSP Builder Advanced Blockset.1

This paper describes a new workflow for designs that are created with blocks from both Simulink and

DSP Builder Advanced Blockset.2 Prior experience with MATLAB, Simulink, and DSP Builder will

help you make the most of the examples in this paper.

Required Software

The models described in this paper are from the example included with HDL Coder, Using Altera

DSP Builder Advanced Blockset with HDL Coder. Simulation and code generation from the model

have been tested with the following versions of the software:

MATLAB (R2013b or later)3

Simulink

HDL Coder (requires MATLAB Coder and Fixed-Point Designer)

Altera DSP Builder (version 13.0sp1 or later)

1

2

For a summary of the features of HDL Coder and Altera DSP Builder Advanced Blockset, see appendix.

This integrated workflow is limited to models built with the DSP Builder Advanced Blockset. Models built using the Standard Blockset

of Altera DSP Builder are not supported in this workflow. All subsequent references to DSP Builder (DSPB) subsystems describe

models built from the DSP Builder Advanced Blockset.

W h i t e Pa p e r

For the latest information, consult HDL Coder documentation, Create an Altera DSP Builder Subsystem.

Model-Based Design for Altera FPGAs Using Simulink, HDL Coder, and Altera DSP Builder Advanced Blockset

To simulate, synthesize, and implement HDL code generated from the model, the following software is

also required:

Altera Quartus II (version 13.0sp1 or later)

Setting Up the MATLAB Environment for HDL Code Generation and DSP

Builder Advanced Blockset Integration

Before you can begin working on your model, you need to ensure that the MATLAB environment is

aware of DSP Builder and that DSP Builder is configured to work with MATLAB.

To start DSP Builder, follow one of these steps (see DSP Builder Handbook Volume 1: Introduction to

DSP Builder for more details):

From Microsoft Windows, click Start, point to All Programs, click Altera<version>, click DSP

Builder, and click Start in MATLAB<version>.

If you have multiple versions of MATLAB installed, you can start DSP Builder in your

desired version from this menu.

On Linux OS, use the following command, which automatically finds MATLAB: <path to the

Quartus II software>/dsp _ builder/dsp _ builder.sh>

You can use the following options after the dsp _ builder.sh command:

m <path to MATLAB> to specify another MATLAB path

glnx86 to run 32-bit DSP Builder

Your MATLAB environment also needs to be made aware of the Quartus II installation. This is

accomplished through the hdlsetuptoolpath command in MATLAB. The command below shows

the typical path for a Windows PC Quartus II installation.

>> hdlsetuptoolpath(ToolName, Altera Quartus II, ToolPath,

C:\altera\13.0sp1\quartus\bin64\quartus.exe);

Note that hdlsetuptoolpath changes the system path and system environment variables for the

current MATLAB session only. To execute the hdlsetuptoolpath command automatically when

MATLAB starts, add it to your startup.m script.

Example: Design with Blocks from Simulink and DSP Builder Advanced

Blockset

The example model (hdlcoder _ sldspba.slx) performs FIR filtering. The top level of the design

contains two subsystems, one implemented with blocks from the DSP Builder Advanced Blockset,

and the other with native Simulink blocks (Figure 1). Because they are designed for synthesis on

Altera devices, Altera blocks will yield an optimized implementation of this FIR filter on an Altera

FPGA. The Simulink subsystem contains a Stateflow block and a MATLAB function block, which

provide flexibility in modeling complex control algorithms. Users can also explore various optimizations on the Simulink subsystem through HDL Coder.

W h i t e Pa p e r

Model-Based Design for Altera FPGAs Using Simulink, HDL Coder, and Altera DSP Builder Advanced Blockset

Figure 1. Simulink model of an FIR system (hdlcoder_sldspba.slx).

W h i t e Pa p e r

Model-Based Design for Altera FPGAs Using Simulink, HDL Coder, and Altera DSP Builder Advanced Blockset

Preparing a Model for HDL Code Generation

In a typical development workflow, engineers model and simulate a design in Simulink, completing

multiple iterations to identify and eliminate design problems in preparation for implementation.

Before using HDL Coder and DSP Builder Advanced Blockset to generate code, you must prepare the

model by:

Creating a DSP Builder (DSPB) subsystem

Setting code generation options for DSPB subsystems

Setting code generation options for HDL Coder

Creating a DSPB Subsystem

To create a DSPB subsystem:

1. Put all the Altera blocks in one subsystem. (Note: In general, HDL Coder supports the use of multiple DSPB subsystems provided that all Altera blocks must be contained in DSPB subsystems; this

example, however, demonstrates use of a single DSPB subsystem.)

2. Ensure the subsystems Architecture parameter is set to Module (the default value). See the Code

Generation Options for HDL Coder section (page 8) for more on this setting.

3. Place a Device block at the top level of the subsystem. You can have subsystem hierarchy in a DSPB

subsystem, but there must be a Device block at the top level of the hierarchy.

4. Place a Control block and a Signals block at the top level of the model.

You can use the following MATLAB command to open the DSPB subsystem in the example model

(Figure 2).

>> open _ system(hdlcoder _ sldspba/SLandDSPBA/DSPBA Subsystem);

W h i t e Pa p e r

Model-Based Design for Altera FPGAs Using Simulink, HDL Coder, and Altera DSP Builder Advanced Blockset

Figure 2. The image processing systems DSPB subsystem.

Setting Code Generation Options for DSP Builder

HDL Coder supports DSP Builder code generation with the following settings only:

Device block (Figure 3):

The same Device must be chosen by all Device blocks and by HDL Coder if applicable.

Control block (Figure 4):

Generate Hardware must be checked.

Create Automatic Testbenches must be unchecked.

Signals block (Figure 5):

Reset Active must be same the setting in HDL Coder.

You do not need to configure these settings yourself. HDL Coder will modify and restore these settings

on the DSP Builder blocks during code generation.

W h i t e Pa p e r

Model-Based Design for Altera FPGAs Using Simulink, HDL Coder, and Altera DSP Builder Advanced Blockset

Figure 3. Options for the DSPB Device block.

Figure 4. Options for the DSPB Control block.

Figure 5. Options for the DSPB Signals block.

W h i t e Pa p e r

Model-Based Design for Altera FPGAs Using Simulink, HDL Coder, and Altera DSP Builder Advanced Blockset

Setting Code Generation Options for HDL Coder

In addition to the settings described above for HDL code generation, HDL Coder requires the

Architecture parameter of DSPB subsystems to be set to Module (Figure 6). If code generation is

performed with HDL Workflow Advisor, the device settings for Workflow Advisor and DSPB Device

blocks must be identical, as shown in Figures 3 and 7.

Figure 6. DSPB subsystem implementation parameters in HDL Coder.

Figure 7. Tool and device options in HDL Workflow Advisor.

Generating HDL

You can generate HDL code from the configured model with the command line interface or with the

GUI, as with any other model. For this example model, the command to generate code is:

>> makehdl(hdlcoder _ sldspba/SLandDSPBA)

W h i t e Pa p e r

Model-Based Design for Altera FPGAs Using Simulink, HDL Coder, and Altera DSP Builder Advanced Blockset

Refer to the HDL Code Generation from a Simulink Model tutorial provided with HDL Coder for

details on how to generate code using the GUI.

Generating HDL Test Bench and Simulation Scripts

For this example model, the command to generate test bench and simulation scripts is:

>> makehdltb(hdlcoder _ slsysgen/SLandSysGen);

Handling Simulation Mismatch When Valid Signal Not Asserted

The DSPB subsystem simulation may not match its generated codes behavior when the valid signal is

not asserted under certain circumstances, such as when the design employs the folding optimization

and/or floating-point support. You may observe such mismatches by turning on the Folding option

in both hdlcoder _ sldspba/SLandDSPBA/DSPBA Subsystem/ChannelIn and hdlcoder _

sldspba/SLandDSPBA/DSPBA Subsystem/ChannelOut. The mismatch affects the downstream

Simulink design and causes a test bench simulation failure.

To see the mismatch, you can turn on the folding setting for the ChannelIn and ChannelOut blocks:

>> set _ param(hdlcoder _ sldspba/SLandDSPBA/DSPBA Subsystem/ChannelIn,

FoldingEnabled, 1);

>> set _ param(hdlcoder _ sldspba/SLandDSPBA/DSPBA Subsystem/ChannelOut,

FoldingEnabled, 1);

Then, generate the HDL code and test bench again:

>> makehdl(hdlcoder _ sldspba/SLandDSPBA);

>> makehdltb(hdlcoder _ sldspba/SLandDSPBA);

After simulating the generated code and test bench, you can see that the outputs from HDL Coder

match the reference data only when the valid signal is asserted as shown in Figure 8.

Figure 8. Simulation mismatch when valid signal not asserted.

W h i t e Pa p e r

Model-Based Design for Altera FPGAs Using Simulink, HDL Coder, and Altera DSP Builder Advanced Blockset

As the message from the test bench indicates, the mismatch is expected.

To avoid this simulation mismatch, insert an enabled subsystem at the DSPB subsystem output signals,

before they reach the Simulink part of your design or the output ports of the overall design. Figure 9

shows how to connect signals to the enabled subsystem.

>> open _ system(hdlcoder _ sldspba/SLandDSPBA2);

Figure 9. Use of enabled subsystem with DSPB subsystem to avoid mismatch when valid not asserted.

Further Reading

For more HDL Coder videos and examples, visit mathworks.com/products/hdl-coder/examples.html.

W h i t e Pa p e r

10

Model-Based Design for Altera FPGAs Using Simulink, HDL Coder, and Altera DSP Builder Advanced Blockset

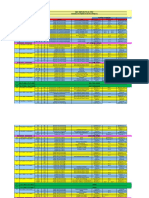

Appendix: Feature Comparison of HDL Coder and Altera DSP Builder

Advanced Blockset

The table below summarizes the complementary features and benefits of HDL Coder and DSP Builder

Advanced Blockset. Used independently, each approach provides an effective FPGA design flow.

Feature

HDL Coder

DSP Builder

Advanced

Blockset

Benefit

Software and hardware code

generation

Partition algorithms

between processors and

hardware

Access to Simulink block library

Rapidly assemble system

models using existing

blocks

Support for native Simulink blocks

Easily migrate system

model to hardware

Floating- to fixed-point conversion

Design exploration

Rapidly explore hardware

solution space

Automatic test bench generation

Verify hardware against

system models

Transaction-Level Model (TLM)

component generation

Hardware cosimulation

MATLAB to HDL code generation

and hardware cosimulation

Follow a hardware design

workflow without using

Simulink

Readable, traceable HDL code

Streamline standards

compliance and reporting

Access Altera IP in Simulink

X

(when used

with DSP

Builder)

Analog data acquisition

Hardware deployment

Shorten design cycles

Use system-level modeling

methodologies

X

Verify hardware

implementations on Altera

development boards

Generate implementations

optimized for Altera targets

Verify algorithms with

real-world analog data

Deploy designs in hardware

without FPGA design

experience

2014 The MathWorks, Inc. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See mathworks.com/trademarks for a list of additional trademarks.

Other product or brand names may be trademarks or registered trademarks of their respective holders.

W h i t e Pa p e r

11

92161v00 02/14

Das könnte Ihnen auch gefallen

- Simulink HDL CoderDokument7 SeitenSimulink HDL CoderAmr YassinNoch keine Bewertungen

- PDK Reference ManualDokument85 SeitenPDK Reference ManualIrfanAhmadNoch keine Bewertungen

- 08.546 DSD With VHDL Lecture Notes - Module 1Dokument70 Seiten08.546 DSD With VHDL Lecture Notes - Module 1Assini Hussain100% (1)

- PLC Programming Using SIMATIC MANAGER for Beginners: With Basic Concepts of Ladder Logic ProgrammingVon EverandPLC Programming Using SIMATIC MANAGER for Beginners: With Basic Concepts of Ladder Logic ProgrammingBewertung: 4 von 5 Sternen4/5 (1)

- Course Project - Agra: ObjectivesDokument5 SeitenCourse Project - Agra: ObjectivesTanmay Kumar GhoshNoch keine Bewertungen

- 92077v00 Xilinx WhitePaper FinalDokument15 Seiten92077v00 Xilinx WhitePaper FinalUlloa JavierNoch keine Bewertungen

- HDL Coder and System GeneratorDokument15 SeitenHDL Coder and System Generatorsikisiki1982Noch keine Bewertungen

- System GeneratorDokument23 SeitenSystem GeneratorJuan Carlos UribeNoch keine Bewertungen

- Intro To FPGA Design Using MATLAB and Simulink PublishedDokument31 SeitenIntro To FPGA Design Using MATLAB and Simulink PublishedelectrocarbonNoch keine Bewertungen

- How Do I Implement My MATLAB Algorithm in An FPGADokument2 SeitenHow Do I Implement My MATLAB Algorithm in An FPGAAnonymous JnvCyu85Noch keine Bewertungen

- Xilinx WorkbookDokument94 SeitenXilinx WorkbookdmctekNoch keine Bewertungen

- HDL Coder Workshop R2015bDokument211 SeitenHDL Coder Workshop R2015bShankar GunaNoch keine Bewertungen

- Inverter Using SimulinkDokument8 SeitenInverter Using SimulinkprakashroutNoch keine Bewertungen

- UWBR Matlab IseDokument20 SeitenUWBR Matlab IsejebileeNoch keine Bewertungen

- 12 - Chapter - 5Dokument13 Seiten12 - Chapter - 5Er Amarsinh RNoch keine Bewertungen

- DSP Lab ManualDokument169 SeitenDSP Lab Manualapi-26783388100% (2)

- Generating Optimizing and Verifying HDL Code With Matlab and SimulinkDokument46 SeitenGenerating Optimizing and Verifying HDL Code With Matlab and Simulinkkpkarthi80Noch keine Bewertungen

- AssignmentDokument9 SeitenAssignmentSumit Kumar YadavNoch keine Bewertungen

- TMS320F2812-Program Development ToolsDokument26 SeitenTMS320F2812-Program Development ToolsPantech ProLabs India Pvt LtdNoch keine Bewertungen

- 8.programmable Asic Design SoftwareDokument21 Seiten8.programmable Asic Design Softwaresalinsweety50% (2)

- Matlab and Ccs Interface Manual With Filter ProgramDokument65 SeitenMatlab and Ccs Interface Manual With Filter ProgramSugumar Sar DuraiNoch keine Bewertungen

- Silvaco EDA DemoDokument11 SeitenSilvaco EDA DemobhataviNoch keine Bewertungen

- Code Generation ToolsDokument4 SeitenCode Generation ToolsshreenandanraoNoch keine Bewertungen

- Ece5950 Tut2 DC PDFDokument15 SeitenEce5950 Tut2 DC PDFsudip_on_air1Noch keine Bewertungen

- VLSI Lab Manual - 2022-1Dokument54 SeitenVLSI Lab Manual - 2022-1SuhailNoch keine Bewertungen

- VHDL NotesDokument40 SeitenVHDL Notesangel_hunNoch keine Bewertungen

- Getting Started With The SDCC/MetaLink 8051 C Cross Compiler/Assembler and The XS 40 Prototyping Platform - A User's GuideDokument46 SeitenGetting Started With The SDCC/MetaLink 8051 C Cross Compiler/Assembler and The XS 40 Prototyping Platform - A User's Guideprabhunithin1Noch keine Bewertungen

- Vlsi Lab Manual 2013Dokument64 SeitenVlsi Lab Manual 2013harish33330% (1)

- Mentor Graphics Tutorial - From VHDL To Silicon Layout Design FlowDokument7 SeitenMentor Graphics Tutorial - From VHDL To Silicon Layout Design FlowbipbulNoch keine Bewertungen

- SGXDokument14 SeitenSGXchristophmairNoch keine Bewertungen

- Fpgas and DSP: Design Alternatives For DSP SolutionsDokument8 SeitenFpgas and DSP: Design Alternatives For DSP Solutionsnguyendinh126Noch keine Bewertungen

- Data Converter BIST Development Tools: Ian Grout, Thomas O'Shea and Jeffrey RyanDokument2 SeitenData Converter BIST Development Tools: Ian Grout, Thomas O'Shea and Jeffrey Ryansarin.gaganNoch keine Bewertungen

- Matlab 6713Dokument15 SeitenMatlab 6713ameiyappan5697Noch keine Bewertungen

- Ece5745 Tut2 DCDokument15 SeitenEce5745 Tut2 DCMisbahNoch keine Bewertungen

- Lab1 DocDokument14 SeitenLab1 DocThanos GkanNoch keine Bewertungen

- VLSI Lab ManualDokument83 SeitenVLSI Lab ManualSri SandhiyaNoch keine Bewertungen

- Xapp890 Zynq Sobel Vivado HlsDokument16 SeitenXapp890 Zynq Sobel Vivado HlsRamanarayan MohantyNoch keine Bewertungen

- 1.1 EDA ToolsDokument18 Seiten1.1 EDA ToolsPurushotham NeerugattiNoch keine Bewertungen

- Modern GPUDokument221 SeitenModern GPUx2y2z2rmNoch keine Bewertungen

- LoopBack ApplicationDokument12 SeitenLoopBack ApplicationGytis BernotasNoch keine Bewertungen

- Introduction To VerilogDokument32 SeitenIntroduction To VerilogVamsi Krishna KNoch keine Bewertungen

- Gcbasic PDFDokument799 SeitenGcbasic PDFBrian LaiNoch keine Bewertungen

- Fpga: Digital Designs: Team Name:Digital DreamersDokument8 SeitenFpga: Digital Designs: Team Name:Digital DreamersRishabhNoch keine Bewertungen

- Hardware Description Languages and Programmable LogicDokument30 SeitenHardware Description Languages and Programmable LogicJay UlomiNoch keine Bewertungen

- Baniaga Jeandy A Task1Dokument4 SeitenBaniaga Jeandy A Task1Jeandy BaniagaNoch keine Bewertungen

- Embedded CoderDokument8 SeitenEmbedded CoderBenjamin FischerNoch keine Bewertungen

- Verilog (About Tool and Steps)Dokument4 SeitenVerilog (About Tool and Steps)udayNoch keine Bewertungen

- Digital Signal Processing Lab: CODE NO: EC05177 List of ExperimentsDokument33 SeitenDigital Signal Processing Lab: CODE NO: EC05177 List of ExperimentsSai SaranyaNoch keine Bewertungen

- HDL Verifier™ Release NotesDokument30 SeitenHDL Verifier™ Release NotesHaniEsmaeelzadehNoch keine Bewertungen

- EE326 Lab 2Dokument25 SeitenEE326 Lab 2krishneelNoch keine Bewertungen

- ADC (Analog To Digital Converter) Module For FPGA DesignDokument2 SeitenADC (Analog To Digital Converter) Module For FPGA DesignIonela100% (4)

- Embedded System and Matlab SIMULINK PDFDokument31 SeitenEmbedded System and Matlab SIMULINK PDFclaudiunicolaNoch keine Bewertungen

- EEE413 Quiz 2Dokument7 SeitenEEE413 Quiz 2Sabit AnjirNoch keine Bewertungen

- Dreamcast Architecture: Architecture of Consoles: A Practical Analysis, #9Von EverandDreamcast Architecture: Architecture of Consoles: A Practical Analysis, #9Noch keine Bewertungen

- Intermediate C Programming for the PIC Microcontroller: Simplifying Embedded ProgrammingVon EverandIntermediate C Programming for the PIC Microcontroller: Simplifying Embedded ProgrammingNoch keine Bewertungen

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemVon EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNoch keine Bewertungen

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkVon EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkNoch keine Bewertungen

- C Programming for the PIC Microcontroller: Demystify Coding with Embedded ProgrammingVon EverandC Programming for the PIC Microcontroller: Demystify Coding with Embedded ProgrammingNoch keine Bewertungen

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Von EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Noch keine Bewertungen

- Color Profile: Exploring Visual Perception and Analysis in Computer VisionVon EverandColor Profile: Exploring Visual Perception and Analysis in Computer VisionNoch keine Bewertungen

- Data ProjectDokument16 SeitenData ProjectamyNoch keine Bewertungen

- 1.differential EquationsDokument13 Seiten1.differential EquationsAbhishek SakatNoch keine Bewertungen

- Teste Diagnostico de Ingles 5o AnoDokument3 SeitenTeste Diagnostico de Ingles 5o AnoCentro De Explicações CentroBookNoch keine Bewertungen

- Works: Filipino Bayombong, Nueva VizcayaDokument2 SeitenWorks: Filipino Bayombong, Nueva VizcayaRant RaveNoch keine Bewertungen

- Filetype PDF ActionscriptDokument2 SeitenFiletype PDF ActionscriptTrudellNoch keine Bewertungen

- A Pali Grammar - Wilhelm Geiger OCRDokument129 SeitenA Pali Grammar - Wilhelm Geiger OCRAnders Fernstedt82% (17)

- Introduction To Emerging LiteraturesDokument8 SeitenIntroduction To Emerging LiteraturesPhilip Sumalbag Arcalas100% (1)

- Logical Database DesignDokument39 SeitenLogical Database DesignuldsNoch keine Bewertungen

- QC Welding Inspector Interview Questions & Answers: Search For Jobs..Dokument1 SeiteQC Welding Inspector Interview Questions & Answers: Search For Jobs..kokaanilkumarNoch keine Bewertungen

- Letter of EndorsementDokument2 SeitenLetter of Endorsementrizalina maxilomNoch keine Bewertungen

- 08MAT T2 NotificationDokument2 Seiten08MAT T2 NotificationAngela HuangNoch keine Bewertungen

- FrancDokument445 SeitenFranctomad100% (1)

- RE 630 Iec61850prot 756793 ENdDokument304 SeitenRE 630 Iec61850prot 756793 ENdThuy Dinh100% (1)

- Data Mining News ArticleDokument30 SeitenData Mining News ArticleSupri KyanoNoch keine Bewertungen

- Detailed Lesson Plan in Art Appreciation Prepared By: Hex GroupDokument25 SeitenDetailed Lesson Plan in Art Appreciation Prepared By: Hex GroupArzy N ChanNoch keine Bewertungen

- Wrox Press Professional XML 2nd (2001) PDFDokument1.286 SeitenWrox Press Professional XML 2nd (2001) PDFmicroserverNoch keine Bewertungen

- Eng 521 Course Outline 2015-16Dokument2 SeitenEng 521 Course Outline 2015-16api-243329537Noch keine Bewertungen

- Sow Form 2Dokument6 SeitenSow Form 2mohanaaprkashNoch keine Bewertungen

- A2 Section A Narrative and Media TheoriesDokument31 SeitenA2 Section A Narrative and Media TheoriesAdPamula100% (1)

- Foucault and The Critique of The PresentDokument53 SeitenFoucault and The Critique of The PresentfedzmeoNoch keine Bewertungen

- Java Interview QuestionsDokument62 SeitenJava Interview Questionssudarshan_369Noch keine Bewertungen

- Data Basics MCQ's - T4TutorialsDokument5 SeitenData Basics MCQ's - T4TutorialsGashaw MekonnenNoch keine Bewertungen

- Components of Technical Writing VS Essays: Lecturer: Zeenatullah " Sail "Dokument14 SeitenComponents of Technical Writing VS Essays: Lecturer: Zeenatullah " Sail "Shabeer Maheer100% (1)

- AOMEI Backupper Standard v6.8.0 Free - MediaketDokument2 SeitenAOMEI Backupper Standard v6.8.0 Free - MediaketDejan NNoch keine Bewertungen

- Change LogDokument9 SeitenChange Logdikyaprilianto01Noch keine Bewertungen

- ST1 Prerequisite TestDokument1 SeiteST1 Prerequisite TestJesus Ponce GNoch keine Bewertungen

- Efi Fiery Fs300pro How-To Print Perfect Bound BookletDokument5 SeitenEfi Fiery Fs300pro How-To Print Perfect Bound Bookletandria kasumaNoch keine Bewertungen

- Morning Glory SACD Editing NotesDokument12 SeitenMorning Glory SACD Editing NotesPablo RodrigoNoch keine Bewertungen

- Lesson Plan For Science 10Dokument2 SeitenLesson Plan For Science 10Kevin GeradaNoch keine Bewertungen