Beruflich Dokumente

Kultur Dokumente

Basic Inverter

Hochgeladen von

Nireekshan SodavaramOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Basic Inverter

Hochgeladen von

Nireekshan SodavaramCopyright:

Verfügbare Formate

Sodavaram Nireekshan Kumar

ICGraph Features

Sodavaram Nireekshan Kumar

Knowing the Tool

Status Line

Pulldown

Menus

Popup Menu

(RMB)

Message Bar

Palette Menus

Sodavaram Nireekshan Kumar

Knowing the Tool

Context

Toolbar

Prompt Bar

Process

Cursor

Location

IC Layout

window

Sodavaram Nireekshan Kumar

Setting the Grid values

Sodavaram Nireekshan Kumar

Sodavaram Nireekshan Kumar

Opening the Layer Palette

Sodavaram Nireekshan Kumar

Lab on Full Custom Layout of Inverter

To start with the inverter with basic editing features you must be clear with the target

technologys process file and the rule file.

The inverter you will be creating now is targeting the ADK 3.0 ami05 process. The

Lambda value for this process is 1 micron.

Before starting make sure that you are in the $WORK/Basic_inv folder.

Invoke the IC station tool by typing the following command

ic &

You will be seeing the below window.

Sodavaram Nireekshan Kumar

Now choose the create option from the palette

You should see the following window

Sodavaram Nireekshan Kumar

In the Cell Name tab type inv

In the Process tab browse to $ADK/technology/ic/process/ami05

In the Rules file tab browse to $ADK/technology/ic/process/ami05.rules

Leave the remaining tabs to default settings.

Select OK.

Sodavaram Nireekshan Kumar

You should be seeing the following window.

10

Sodavaram Nireekshan Kumar

Set the grid to 0.1X0.1 micron. To do this:

Select Menu > Other > Window > Set Grid

as shown in the figure below.

11

Sodavaram Nireekshan Kumar

Set the Snap X to 0.1 and Snap Y to 0.1 and others to default.

12

Sodavaram Nireekshan Kumar

Now select the layers in which you want to work.

For this select Menu > Other > Layers > Show Layer Palette as shown below.

13

Sodavaram Nireekshan Kumar

Here, scroll down a bit and select the layers that you want to display by pressing the

ctrl button as shown below. For drawing this inverter select

PWELL, NWELL, ACTIVE, P_PLUS_SELECT, N_PLUS_SELECT, POLY,

CONTACT_TO_POLY, CONTACT_TO_ACTIVE, METAL1, VIA, METAL2.

14

Sodavaram Nireekshan Kumar

Select OK here the layout window should get updated as shown below.

Now add the ruler from the origin to draw the inverter.

15

Sodavaram Nireekshan Kumar

Select Edit in the palette. Now click on the RU* tab. You will get the prompt as

shown below.

Click OK to start drawing the ruler.

16

Sodavaram Nireekshan Kumar

Draw the ruler for a height of 120 microns as shown in the figure.

17

Sodavaram Nireekshan Kumar

Now we start drawing the inverter.

Start with drawing the VSS Metal. This is drawn in the Metal1 layer. Choose the

METAL1 Layer from the Palette as shown below.

18

Sodavaram Nireekshan Kumar

Now draw a path to layout the Metal1 VSS rail.

For this, choose the PAT* from the palette so that you would get the PATH prompt as

shown below.

19

Sodavaram Nireekshan Kumar

Select the options tab and enter the width as 10 microns as shown below.

20

Sodavaram Nireekshan Kumar

Choose OK and draw the Metal1 near the origin for the VSS rail as shown below. Draw it

for a length of 25 microns.

Now you have to place the NPLUS_Select to create the N Active region for the

transistor.

21

Sodavaram Nireekshan Kumar

The Nplus region is drawn at a distance of 14 microns from the top edge of the VSS

metal and 4 microns from away from the reference ruler. This is shown in the figure

below

Choose the Nplus layer from the Layer palette.

Select the PAT* from the palette to add the path. Choose the Options tab and enter the

width as 9 as shown below.

22

Sodavaram Nireekshan Kumar

Draw the Nplus region for 17 microns.

Now to flatten the Nplus path to shape, select the Nplus path.

Choose the Edit > Flatten option.

This is shown in the fig below.

23

Sodavaram Nireekshan Kumar

Next you will be drawing the N-Active to get the N diffusion.

Here the N-Active region is drawn inside the N-Plus region with a clearance of 2microns.

This is shown in the figure below.

24

Sodavaram Nireekshan Kumar

Choose the Active layer from the Layer palette as shown in the figure below.

Choose the PAT* from the palette and select the Options tab and enter the width as 5

as shown in the figure below.

25

Sodavaram Nireekshan Kumar

Draw the path for 13microns. The Nactive and the Nplus looks as shown below.

26

Sodavaram Nireekshan Kumar

Now you will be placing the contact on the N-Active region with 1.5 microns distance

from the left inner edge of the Active region as shown below.

27

Sodavaram Nireekshan Kumar

Select the Contact_to_Active layer from the layer palette and choose the width of the

contact as 2microns by selecting the PAT* option from the palette and draw the

contact to distance of 2microns as shown in the figure below.

28

Sodavaram Nireekshan Kumar

Now draw the contact on the right side of the Active region with the same distance and

dimension from the inner edge of the Active as the previous contact as shown below.

29

Sodavaram Nireekshan Kumar

Draw the Metal overlap on these contacts at a distance of 0.5microns from the inner edge

of N-Active region as shown below.

30

Sodavaram Nireekshan Kumar

31

Sodavaram Nireekshan Kumar

Now select Metal1 from the Layer Palette and choose PAT* from the palette, enter the

width as 4microns. Draw the Metal overlapping the contact for a distance of 4microns.

Draw another metal overlap on the other side contact with the same distance and

dimension as the one you just drawn. After adding both the Metals, the complete N

region should look as shown below.

32

Sodavaram Nireekshan Kumar

Now connect the VSS rail to one of the contact in the N-Region with a metal of width 3

microns.

33

Sodavaram Nireekshan Kumar

Draw the Pwell region surrounding the N Region. For this, mark the dimension of 27

microns from the top edge of the VSS rail as shown in the figure below.

34

Sodavaram Nireekshan Kumar

Select the Pwell layer from the layer palette. Choose the PAT* from the palette, choose

the width of 27 microns and draw it to a distance of 25 microns as shown below.

35

Sodavaram Nireekshan Kumar

Place the P-WELL contact to connect the bulk of the N transistor to Ground. For this,

Right Click on layout window. Select the ADD > Cell option.

Browse to the folder:

$ADK/technology/ic/process/ami05_via.

Choose the P_WELL_CONTACT cells and place it on the VSS rail such that it also

overlaps on the P_WELL region that you have already drawn as shown below.

36

Sodavaram Nireekshan Kumar

After this, draw the VDD rail with a width of 10microns for a distance of 25microns as

shown below.

37

Sodavaram Nireekshan Kumar

Draw the P-Plus region at a distance of 19 microns from the bottom edge of the VDD rail

and 4microns from the reference marker as shown below.

38

Sodavaram Nireekshan Kumar

Choose the P_PLUS layer from the layer palette. Select the PAT* from the palette.

Enter the width as 14 microns. Draw the P_PLUS region for a distance of 17 microns as

shown below.

39

Sodavaram Nireekshan Kumar

Place the Active region at a distance of 2microns from the inner edge of the PPLUS layer

as shown below. Choose the Active Layer from the Layer palette. Select the PAT*

from the palette and enter the width as 10 microns. Draw it for a distance of 13microns as

shown below.

40

Sodavaram Nireekshan Kumar

Place the contacts in the Pdiff laver. Place the contact at a distance of 1.5microns from

the inner walls of the active region. Place 2 contacts on each side for better connectivity.

The distance between the contacts that are placed one below the other should be

3microns. Please refer the figure below. The contact dimensions should be exactly 2X2

microns.

41

Sodavaram Nireekshan Kumar

Place the Metal1 overlapping the contact with a width of 4microns. Draw the metal at a

distance of 0.5 microns from the inner edge of the Active as shown below.

42

Sodavaram Nireekshan Kumar

Connect the output metal from the P-Region to the N-Region. The Metal width is

3microns.

Please refer the below figure.

43

Sodavaram Nireekshan Kumar

Place the Nwell surrounding the Pregion with a width of 37 microns starting from the

point of reference marker and the bottom part of VDD rail. Draw the Nwell for a distance

of 25microns. Please refer figure below.

44

Sodavaram Nireekshan Kumar

Connect the VDD to the metal in the P-Diffusion with a width of 3micron as shown

below.

45

Sodavaram Nireekshan Kumar

Place the gate poly with a width of 2microns. The poly has an end cap of 2microns on

either side. This is placed at a distance of 1micron from the metal1 edges. This is as

shown in the figure below.

46

Sodavaram Nireekshan Kumar

Place the nwell contact on the VDD rail to make the Bulk connection of the PMOS as

shown below.

47

Sodavaram Nireekshan Kumar

Next is to make the Input connection to the poly. For this extend the poly in between the

PMOS and NMOS for about 5X5micron as shown below.

48

Sodavaram Nireekshan Kumar

Place the Metal1 overlap with a dimension of 4X4 microns and with a distance of

0.5microns from the poly inner edge.

Place the Poly contact by choosing the CONTACT_TO_POLY layer in the layer palette.

The contact dimension is 2X2 microns. Place it at a distance of 1micron from the inner

edge of the metal1. This is as shown below.

49

Sodavaram Nireekshan Kumar

Extend the Metal1 with a width of 3micron away from the poly layer so that you

construct a port by bringing the connection to Metal2. Now at the edge of Metal1 Place a

4X4micron Metal1 layer and place 4X4micron Metal2 over the Metal1 square as shown

in the figure.

50

Sodavaram Nireekshan Kumar

Place the via of size 2X2 micron at a distance of 1micron from the inner edge of Metal2

as shown in the figure below.

51

Sodavaram Nireekshan Kumar

52

Sodavaram Nireekshan Kumar

Similarly create an output port for the output Metal1 layer. Both the ports should look

something like shown below.

The complete inverter looks as shown below.

53

Sodavaram Nireekshan Kumar

Now check the DRC by choosing the Checking > DRC (ICRules). You should see the

count Total results:0 in the transcript window at the bottom of the tool.

Creating Ports:

1. Select the VDD Metal. Choose the Objects > Make > Port menu.

Choose the port type as Power. Direction as Bidirectional. Enter the Port name as VDD.

2. Select the VSS Metal. Choose the Objects > Make > Port menu.

Choose the port type as Power. Direction as Bidirectional. Enter the Port name as VSS.

3. Select the IN Metal. Choose the Objects > Make > Port menu.

Choose the port type as Signal. Direction as In. Enter the Port name as IN.

4. Select the OUT Metal. Choose the Objects > Make > Port menu.

Choose the port type as Signal. Direction as Out. Enter the Port name as Out.

This completes the basic inverter.

54

Das könnte Ihnen auch gefallen

- 1.3.1 General AASHTO LRFD Design EquationDokument1 Seite1.3.1 General AASHTO LRFD Design EquationElmo CharlesNoch keine Bewertungen

- 철근콘크리트 휨부재의 최소 철근 규정Dokument9 Seiten철근콘크리트 휨부재의 최소 철근 규정jinwook75Noch keine Bewertungen

- Sapa Aluminum DeckDokument4 SeitenSapa Aluminum DeckoiuedcNoch keine Bewertungen

- LRFD-8 AppendexE5Dokument159 SeitenLRFD-8 AppendexE5diablopapanatasNoch keine Bewertungen

- D6432 16937Dokument18 SeitenD6432 16937prasadNoch keine Bewertungen

- Part Ii - Particular Technical Specifications Chapter 13 - Permanent Access Bridge 13. PERMANENT ACCESS BRIDGE........................................................ 13-1Dokument11 SeitenPart Ii - Particular Technical Specifications Chapter 13 - Permanent Access Bridge 13. PERMANENT ACCESS BRIDGE........................................................ 13-1Anonymous KHIyWRIWmaNoch keine Bewertungen

- ETCulvert V2 Brochure Web PDFDokument2 SeitenETCulvert V2 Brochure Web PDFjorgesalinasengNoch keine Bewertungen

- Study of Interfacial Pressure Distribution For Preloaded Bolted ConnectionDokument6 SeitenStudy of Interfacial Pressure Distribution For Preloaded Bolted ConnectionRohit JayashreeNoch keine Bewertungen

- Analysis Anda Design Pre Stressd SleepersDokument25 SeitenAnalysis Anda Design Pre Stressd SleeperspoezpietaNoch keine Bewertungen

- Strut and Tie Models Recommended ReadingDokument2 SeitenStrut and Tie Models Recommended ReadingBadr AmmarNoch keine Bewertungen

- OCEN 201 Introduction To Ocean & Coastal EngineeringDokument28 SeitenOCEN 201 Introduction To Ocean & Coastal EngineeringbalumaxNoch keine Bewertungen

- Tips For Designers PDFDokument5 SeitenTips For Designers PDFSushil DhunganaNoch keine Bewertungen

- MC PT-Injection Brochure UK 07-2013 ScreenDokument40 SeitenMC PT-Injection Brochure UK 07-2013 Screenpetronela.12Noch keine Bewertungen

- Errata: Transportation OfficialsDokument24 SeitenErrata: Transportation OfficialsHector Enrique Reza ReyesNoch keine Bewertungen

- Guidelines For Earth Fill DamsDokument23 SeitenGuidelines For Earth Fill DamsjnfNoch keine Bewertungen

- Concrete Model in AdinaDokument28 SeitenConcrete Model in AdinaAdolfo Gálvez VillacortaNoch keine Bewertungen

- WinFlume Guide PDFDokument17 SeitenWinFlume Guide PDFカーン アブドゥルラヒムNoch keine Bewertungen

- PLAXIS-UDSM-Masonry Model (V20Update1)Dokument22 SeitenPLAXIS-UDSM-Masonry Model (V20Update1)NISHANT ROYNoch keine Bewertungen

- Pavement RepairDokument15 SeitenPavement RepairtoddlbyrnesNoch keine Bewertungen

- Wind Load 102Dokument1 SeiteWind Load 102lincah marpaungNoch keine Bewertungen

- Report On Code Usage Exercise For DEEPSOIL V2.5 (Installed On An XP Home Edition System)Dokument12 SeitenReport On Code Usage Exercise For DEEPSOIL V2.5 (Installed On An XP Home Edition System)hricha_20Noch keine Bewertungen

- Tutorials Pad Footing Nta 5 (2012&2013)Dokument3 SeitenTutorials Pad Footing Nta 5 (2012&2013)Host FredyNoch keine Bewertungen

- Chapter 5 Snow LoadsDokument30 SeitenChapter 5 Snow LoadsbranimirNoch keine Bewertungen

- Sharma Et Al-2017-Structural Concrete As PublishedDokument9 SeitenSharma Et Al-2017-Structural Concrete As PublisheddebiNoch keine Bewertungen

- Load Testing of Highway BridgeDokument6 SeitenLoad Testing of Highway BridgeBalasubramanian MahadevanNoch keine Bewertungen

- JL-98-November-December Restraint Moments in Precast Prestressed Concrete Continuous BridgesDokument18 SeitenJL-98-November-December Restraint Moments in Precast Prestressed Concrete Continuous Bridgesjrobert123321Noch keine Bewertungen

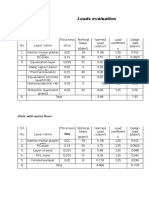

- Loads Evaluation: TerraceDokument9 SeitenLoads Evaluation: Terraceandreeah37Noch keine Bewertungen

- ACI 214.3 (R1997) SimpleVersion-RP-Eval-StrengthTestResults-Concrete PDFDokument8 SeitenACI 214.3 (R1997) SimpleVersion-RP-Eval-StrengthTestResults-Concrete PDFphilipyapNoch keine Bewertungen

- 4 - P. Moze, D. Beg - On The Bearing Resistance of Bolted ConnectionsDokument10 Seiten4 - P. Moze, D. Beg - On The Bearing Resistance of Bolted ConnectionsChandana KumaraNoch keine Bewertungen

- Evaluation, Repair, Modification and Steel Moment Frame Fema267 PDFDokument415 SeitenEvaluation, Repair, Modification and Steel Moment Frame Fema267 PDFTharach JanesuapasaereeNoch keine Bewertungen

- Use of Flat Slabs in Multi-Storey Commercial Building Situated in High Seismic ZoneDokument14 SeitenUse of Flat Slabs in Multi-Storey Commercial Building Situated in High Seismic ZoneZimit SukhadiaNoch keine Bewertungen

- Nonlinear Finite Element Analysis of An RC FrameDokument12 SeitenNonlinear Finite Element Analysis of An RC Framearash250100% (1)

- Durability TestsDokument44 SeitenDurability TestsBudigi Venkata Ramana PrasadNoch keine Bewertungen

- Astm C1196Dokument6 SeitenAstm C1196Lorenzo GambassiNoch keine Bewertungen

- Flaky Elongated AggregatesDokument7 SeitenFlaky Elongated AggregatesAnkur GoyalNoch keine Bewertungen

- Shell Flintkote 3: Product Technical Data SheetDokument3 SeitenShell Flintkote 3: Product Technical Data SheetAhmed TahsinNoch keine Bewertungen

- Calibration of The Live Load Factor in LFRD Design GuidelinesDokument115 SeitenCalibration of The Live Load Factor in LFRD Design Guidelinesravi varmaNoch keine Bewertungen

- Applications of Pretensioned Anchor Rods in Industrial FacilitiesDokument10 SeitenApplications of Pretensioned Anchor Rods in Industrial FacilitiesAndré Luiz NogueiraNoch keine Bewertungen

- Lec1 Steel Design 2nd Sem 2011-12Dokument6 SeitenLec1 Steel Design 2nd Sem 2011-12Jesus Ray M. MansayonNoch keine Bewertungen

- Rolltec Coupler BrochureDokument4 SeitenRolltec Coupler BrochureMohammad Aasimuddin100% (1)

- Sample Method Statement Astm d1194Dokument6 SeitenSample Method Statement Astm d1194Gio ReyesNoch keine Bewertungen

- FAARFIELD 2.0.7 Readme 2021-09-14Dokument5 SeitenFAARFIELD 2.0.7 Readme 2021-09-14Miguel O PNoch keine Bewertungen

- K-Series Final 030911Dokument54 SeitenK-Series Final 030911Alvaro Alexis Mendoza PradaNoch keine Bewertungen

- Life-365 - v2.2.3 - Users - Manual (1) - 26-53Dokument28 SeitenLife-365 - v2.2.3 - Users - Manual (1) - 26-53Fernando RosalesNoch keine Bewertungen

- UCASE Incremental DesignDokument76 SeitenUCASE Incremental DesignctrleNoch keine Bewertungen

- Iii. Load Evaluation: A) Permanent LoadsDokument10 SeitenIii. Load Evaluation: A) Permanent LoadsropotavladNoch keine Bewertungen

- ASCE Intermediate Diaphragms SC.1943-5576.0000272Dokument10 SeitenASCE Intermediate Diaphragms SC.1943-5576.0000272jrhst36100% (1)

- Flare Groove Welds To HSS CornersDokument6 SeitenFlare Groove Welds To HSS CornersPO AsselinNoch keine Bewertungen

- Trapezoidal Sheet As A Bracing Preventing Flat Trusses From Out-Of-Plane BucklingDokument7 SeitenTrapezoidal Sheet As A Bracing Preventing Flat Trusses From Out-Of-Plane BucklingWilliam Pol100% (1)

- 02 Monorail PDFDokument295 Seiten02 Monorail PDFDerry Trey FebriansyahNoch keine Bewertungen

- Aashto M 6-13Dokument5 SeitenAashto M 6-13Abu Alhassan A.Noch keine Bewertungen

- Anchored Crane Beams in Hydroelectric Caverns PDFDokument14 SeitenAnchored Crane Beams in Hydroelectric Caverns PDFSushmit SharmaNoch keine Bewertungen

- Development of A Precast Bent Cap SystemDokument402 SeitenDevelopment of A Precast Bent Cap SystemvNoch keine Bewertungen

- Foundations For Dynamic and Sensitive Equipment: University of Minnesota - Structures Seminar October 30, 2015Dokument40 SeitenFoundations For Dynamic and Sensitive Equipment: University of Minnesota - Structures Seminar October 30, 2015Dimas RussyNoch keine Bewertungen

- Fatigue Strength of Welded ComponentsDokument40 SeitenFatigue Strength of Welded ComponentsVinit Ahluwalia100% (1)

- K-Band Waveguide BPF Design Using Agilent Empro 2013: Anurag Bhargava Application Consultant Agilent Eesof EdaDokument22 SeitenK-Band Waveguide BPF Design Using Agilent Empro 2013: Anurag Bhargava Application Consultant Agilent Eesof EdaBibek BoxiNoch keine Bewertungen

- Ejemplo Guiado Stiffneer Con Catia V5Dokument12 SeitenEjemplo Guiado Stiffneer Con Catia V5elprofedemcursoNoch keine Bewertungen

- Microwind TutorialDokument60 SeitenMicrowind TutorialMiguel Angel Garcia CanoNoch keine Bewertungen

- Tutorial 2Dokument21 SeitenTutorial 2Suren D. SalvatoreNoch keine Bewertungen

- Cmos Inverter Layout Tutorial: Prepared By: Eng. Hazem W. MararDokument12 SeitenCmos Inverter Layout Tutorial: Prepared By: Eng. Hazem W. Mararkrsrajesh1Noch keine Bewertungen

- PDF Applied Failure Analysis 1 NSW - CompressDokument2 SeitenPDF Applied Failure Analysis 1 NSW - CompressAgungNoch keine Bewertungen

- Uj 76 HD 5 CdivutDokument18 SeitenUj 76 HD 5 Cdivuttfrcuy76Noch keine Bewertungen

- Spice Board BBLDokument24 SeitenSpice Board BBLvenkatpficoNoch keine Bewertungen

- How To Apply For The UpcatDokument3 SeitenHow To Apply For The UpcatAaron ReyesNoch keine Bewertungen

- Functional Specifications For Purchase Order: 1. Business RequirementsDokument5 SeitenFunctional Specifications For Purchase Order: 1. Business RequirementsTom MarksNoch keine Bewertungen

- FBL ManualDokument12 SeitenFBL Manualaurumstar2000Noch keine Bewertungen

- Assignment On Industrial Relation of BDDokument12 SeitenAssignment On Industrial Relation of BDKh Fahad Koushik50% (6)

- ExamDokument446 SeitenExamkartikNoch keine Bewertungen

- Relational NotationDokument3 SeitenRelational NotationTweetrudi WhyteNoch keine Bewertungen

- Piping Tie in Procedure Rev A PDFDokument15 SeitenPiping Tie in Procedure Rev A PDFMohammed Sibghatulla100% (1)

- SDS enDokument6 SeitenSDS enAnup BajracharyaNoch keine Bewertungen

- Ten Rules of NetiquetteDokument11 SeitenTen Rules of NetiquetteAriel CancinoNoch keine Bewertungen

- 1GR FE LubricationDokument19 Seiten1GR FE LubricationJesus LayaNoch keine Bewertungen

- (A) Universality Principle and Subject To I.LDokument11 Seiten(A) Universality Principle and Subject To I.LKELVIN A JOHNNoch keine Bewertungen

- Lynette Hawkins, BMG Awesome InsightDokument2 SeitenLynette Hawkins, BMG Awesome Insightawesomei100% (1)

- Metrologic Colombia S.A.S. Medellín Medellín Colombia: Oferta Economica CO20233ADokument3 SeitenMetrologic Colombia S.A.S. Medellín Medellín Colombia: Oferta Economica CO20233AJulian MoraNoch keine Bewertungen

- 1 s2.0 S0959652618323667 MainDokument12 Seiten1 s2.0 S0959652618323667 MaintaliagcNoch keine Bewertungen

- Essays From Previous Years For HseeDokument2 SeitenEssays From Previous Years For HseeGagan TottempudiNoch keine Bewertungen

- Read Me - CADWorx Plant 2019 SP2 HF1Dokument4 SeitenRead Me - CADWorx Plant 2019 SP2 HF1Himanshu Patel (Himan)Noch keine Bewertungen

- 2011 Hyundai Service FiltersDokument18 Seiten2011 Hyundai Service FiltersTan JaiNoch keine Bewertungen

- AMEM211 Lab2 PotentiometerDokument10 SeitenAMEM211 Lab2 PotentiometerB.s. BhosleNoch keine Bewertungen

- 03 Zero Emissions and Eco-Town in KawasakiDokument21 Seiten03 Zero Emissions and Eco-Town in KawasakiAlwi AmarNoch keine Bewertungen

- Honeywell Aquatrol 2000 PDFDokument60 SeitenHoneywell Aquatrol 2000 PDFvsilickasNoch keine Bewertungen

- MCMCHistoryDokument18 SeitenMCMCHistoryAli S.Noch keine Bewertungen

- BeechDokument1 SeiteBeechperovojNoch keine Bewertungen

- GROZ Tools & Equipment 2018Dokument3 SeitenGROZ Tools & Equipment 2018ayush bansalNoch keine Bewertungen

- SQA Plan TemplateDokument105 SeitenSQA Plan Templatestudent1291Noch keine Bewertungen

- The Cycle of Leadership Through Transformational, Eccles - (Leadership) PDFDokument16 SeitenThe Cycle of Leadership Through Transformational, Eccles - (Leadership) PDFEliana LopezNoch keine Bewertungen

- Invoice-1Dokument2 SeitenInvoice-1atipriya choudharyNoch keine Bewertungen

- Road Book - MoroccoDokument28 SeitenRoad Book - MoroccoCarrie YangNoch keine Bewertungen