Beruflich Dokumente

Kultur Dokumente

Trabajo de Sistemas Digitales I

Hochgeladen von

German OrlandoOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Trabajo de Sistemas Digitales I

Hochgeladen von

German OrlandoCopyright:

Verfügbare Formate

E.P.

INGENIERIA ELECTRONICA

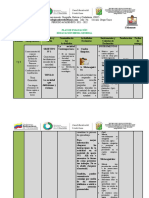

TRABAJO DE SISTEMAS DIGITALES I

German Orlando Callohuanca Rojas

-

Caracteres ASCII en formato bytes:

Cod. 094728

E.P. INGENIERIA ELECTRONICA

-

Caracteres ASCII en formato hexadecimal:

Cdigo HAMMING:

En informtica, el cdigo de Hamming es un cdigo detector y corrector de

errores que lleva el nombre de su inventor, Richard Hamming. En los datos

codificados en Hamming se pueden detectar errores en un bit y corregirlos, sin

embargo no se distingue entre errores de dos bits y de un bit (para lo que se usa

Hamming extendido). Esto representa una mejora respecto a los cdigos con bit

de paridad, que pueden detectar errores en slo un bit, pero no pueden corregirlo.

Si se aaden junto al mensaje ms bits detectores-correctores de error y si esos

bits se pueden ordenar de modo que diferentes bits de error producen diferentes

resultados, entonces los bits errneos podran ser identificados. En un conjunto de

siete bits, hay slo siete posibles errores de bit, por lo que con tres bits de control

de error se podra especificar, adems de que ocurri un error, en qu bit fue.

El algoritmo es el siguiente:

E.P. INGENIERIA ELECTRONICA

1. Todos los bits cuya posicin es potencia de dos se utilizan como bits de paridad

(posiciones 1, 2, 4, 8, 16, 32, 64, etc.).

2. Los bits del resto de posiciones son utilizados como bits de datos (posiciones 3, 5, 6, 7,

9, 10, 11, 12, 13, 14, 15, 17, etc.).

3. Cada bit de paridad se obtiene calculando la paridad de alguno de los bits de datos. La

posicin del bit de paridad determina la secuencia de los bits que alternativamente

comprueba y salta, a partir de ste, tal y como se explica a continuacin. Posicin 1: salta

0, comprueba 1, salta 1, comprueba 1, etc. Posicin 2: salta 1, comprueba 2, salta 2,

comprueba 2, etc. Posicin 4: salta 3, comprueba 4, salta 4, comprueba 4, etc. Posicin 8:

salta 7, comprueba 8, salta 8, comprueba 8, etc. Posicin 16: salta 15, comprueba 16,

salta 16, comprueba 16, etc. Regla general para la posicin n es: salta n-1 bits,

comprueba n bits, salta n bits, comprueba n bits... Y as sucesivamente. En otras

palabras, el bit de paridad de la posicin comprueba los bits en las posiciones que tengan

al bit k en su representacin binaria. Dicho a la inversa, el bit 4, chequea los bits 4, 5, 6, 7,

al ser estos los de su representacin binaria: 4=100(2), 5=101(2), 6=110(2) y 7=111(2).

Por el contrario, el mismo bit de paridad no comprueba el bit 8, debido a que en su

representacin binaria el bit nmero 3 (=4) es igual a 0 (8=1000B). As, por ejemplo, para

los primeros trminos se tiene: En la Posicin 1 (2^0 = 1), comprobaramos los bits: 1, 3,

5, 7, 9, 11, 13... En la Posicin 2 (2^1 = 2), los bits: 2, 3, 6, 7, 10, 11, 14, 15... En la

Posicin 4 (2^2 = 4), los bits: 4, 5, 6, 7, 12, 13, 14, 15, 20, 21, 22, 23... En la Posicin 8

(2^3 = 8) tendramos: 8, 9, 10, 11, 12, 13, 14, 15, 24-31... Siguiendo el algoritmo hasta

completar la nueva cadena.

Ejemplo

Consideremos la palabra de datos de 7 bits "0110101". Para ver cmo se generan y

utilizan los cdigos Hamming para detectar un error, observe las tablas siguientes. Se

utiliza la d para indicar los bits de datos y la p para los de paridad.

En primer lugar los bits de datos se insertan en las posiciones apropiadas y los bits de

paridad calculados en cada caso usando la paridad par.

p1

Palabra de datos (sin paridad):

p1

p2

d1

p3

d2

d3

d4

p4

d5

d6

d7

E.P. INGENIERIA ELECTRONICA

p2

p3

p4

Palabra de datos (con paridad):

Clculo de los bits de paridad en el cdigo Hamming

P1 =

D1

exor

D2

exor

D4

exor

D5

exor

D7

P2 =

D1

exor

D3

exor

D4

exor

D6

exor

D7

P3 =

D2

exor

D3

exor

D4

P4 = D5 exor D6 exor D7

La nueva palabra de datos (con los bits de paridad) es ahora "10001100101".

Consideremos ahora que el bit de la derecha, por error, cambia de 1 a 0. La nueva

palabra de datos ser ahora "10001100100".

Sin errores

p1

Palabra

de datos 1

recibida:

p1

p2

p3

p2

d1

p3

d2

d3

d4

p4

d5

d6

d7

Prueba

de

paridad

Correcto

Correcto

Correcto

Bit

de

comprobacin

E.P. INGENIERIA ELECTRONICA

p4

Correcto

Comprobacin de los bits de paridad (con primer bit de la derecha sin cambiar)

Con errores

p1

Palabra

de datos 1

recibida:

p1

p2

p3

p2

d1

p3

d2

d3

d4

p4

d5

d6

d7

Prueba

de

paridad

Error

Error

Correcto

Error

p4

Bit

de

comprobacin

Comprobacin de los bits de paridad (con primer bit de la derecha cambiado)

Si se analiza en la tabla anterior la paridad que se debe obtener a la derecha

tras la llegada del mensaje sin errores debe ser siempre 0 (por cada fila), pero

en el momento en que ocurre un error esta paridad cambia a 1, de all el

nombre de la columna "prueba de paridad 1". Se observa que en la fila en que

el cambio no afect la paridad es cero y llega sin errores.

El paso final es evaluar los bits de paridad (recuerde que el fallo se encuentra

en d7). El valor entero que representan los bits de paridad es 11 (si no

hubieran ocurrido errores este valor seria 0), lo que significa que el bit dcimo

primero de la palabra de datos (bits de paridad incluidos) es el errneo y

necesita ser cambiado.

E.P. INGENIERIA ELECTRONICA

p4

p3

p2

p1

Binario

Decimal

= 11

Cambiando el bit dcimo primero 10001100100 se obtiene de nuevo

10001100101. Eliminando los bits de patrn de la paridad no se tienen en

cuenta los bits de paridad. Si el error se produjera en uno de ellos, en la

comprobacin slo se detectara un error, justo el correspondiente al bit de

paridad causante del mismo.

HAMMING EXTENDIDO

Finalmente, para detectar errores en 2 bits se utiliza un bit adicional de

paridad (Hamming Extendido) donde puede darse el caso de 3

posibilidades:

1.-' No hay error -> Hamming =0, Paridad OK

2.- Un bit de error -> Paridad Fallo entonces

a) Hamming = 0, P = incorrecto, en este caso se cambia el valor del bit de

paridad.

b) Hamming <> 0, corrijo segn Hamming

3.- Dos bit en error -> Paridad Ok, Hamming <> 0, por lo tanto informo, NO

corrijo.

TIMER 555:

El temporizador IC 555 es un circuito integrado (chip) que se utiliza en una

variedad de aplicaciones y se aplica en la generacin de pulsos y de oscilaciones.

El 555 puede ser utilizado para proporcionar retardos de tiempo, como un

oscilador, y como un circuito integrado flip-flop. Sus derivados proporcionan hasta

cuatro circuitos de sincronizacin en un solo paquete. Introducido en 1971

porSignetics, el 555 sigue siendo de uso generalizado debido a su facilidad de

uso, precio bajo y la estabilidad. Lo fabrican muchas empresas en bipolares y

tambin en CMOS de baja potencia. A partir de 2003, se estimaba que mil millones

de unidades se fabricaban cada ao.

E.P. INGENIERIA ELECTRONICA

-

ASTABLE: Este tipo de funcionamiento se caracteriza por una salida con forma de

onda cuadrada (o rectangular) continua de ancho predefinido por el diseador del

circuito. El esquema de conexin es el que se muestra. La seal de salida tiene un

nivel alto por un tiempo t1 y un nivel bajo por un tiempo t2. La duracin de estos

tiempos dependen de los valores de R1, R2 y C, segn las frmulas siguientes:

[segundos]

y

[segundos]

La frecuencia con que la seal de salida oscila est dada por la frmula:

el perodo es simplemente:

Tambin decir que si lo que queremos es un generador con frecuencia variable,

debemos variar la capacidad del condensador, ya que si el cambio lo hacemos

mediante los resistores R1 y/o R2, tambin cambia el ciclo de trabajo o ancho de

pulso (D) de la seal de salida segn la siguiente expresin:

Hay que recordar que el perodo es el tiempo que dura la seal hasta que sta se

vuelve a repetir (Tb - Ta).

-MONOASTABLE:

En este caso el circuito entrega un solo pulso de un ancho establecido por el diseador.

E.P. INGENIERIA ELECTRONICA

El esquema de conexin es el que se muestra. La frmula para calcular el tiempo de

duracin (tiempo en el que la salida est en nivel alto) es:

[s]

[segundos]

Das könnte Ihnen auch gefallen

- Fuentes OpticasDokument28 SeitenFuentes OpticasGerman OrlandoNoch keine Bewertungen

- Examen Fisica MDokument3 SeitenExamen Fisica MGerman OrlandoNoch keine Bewertungen

- Multimetro, Generador de Funciones y OsciloscopioDokument17 SeitenMultimetro, Generador de Funciones y OsciloscopioGerman OrlandoNoch keine Bewertungen

- Multimetro AnalogicoDokument9 SeitenMultimetro AnalogicoGerman OrlandoNoch keine Bewertungen

- Redacción AdministrativaDokument12 SeitenRedacción AdministrativaGerman OrlandoNoch keine Bewertungen

- Trabajo Economia GeneralDokument9 SeitenTrabajo Economia GeneralGerman OrlandoNoch keine Bewertungen

- Crisis de La Edad Media en EspañaDokument8 SeitenCrisis de La Edad Media en EspañaGerman OrlandoNoch keine Bewertungen

- Analizador Lexico TrabajoDokument5 SeitenAnalizador Lexico TrabajoGerman OrlandoNoch keine Bewertungen

- Clase N - 1 - Introducción A Los MaterialesDokument24 SeitenClase N - 1 - Introducción A Los MaterialesSebastian Ruiz PeraltaNoch keine Bewertungen

- Noelia Oliver AutocandidaturaDokument4 SeitenNoelia Oliver AutocandidaturaNoelia OliverNoch keine Bewertungen

- Klein Tools Desde 1957Dokument402 SeitenKlein Tools Desde 1957eliasfendiNoch keine Bewertungen

- Control de Calidad Del Concreto en ObraDokument8 SeitenControl de Calidad Del Concreto en ObraDaniel MrTnzNoch keine Bewertungen

- Montaje de Correas y Poleas en VDokument11 SeitenMontaje de Correas y Poleas en Vgilguillermo25Noch keine Bewertungen

- Tarea MRUVDokument3 SeitenTarea MRUVABELINO BALAM CASTRO PEREZNoch keine Bewertungen

- Uso de La Protoboard Marcos y DiegoDokument7 SeitenUso de La Protoboard Marcos y DiegoDiego Smash MusicNoch keine Bewertungen

- Santander-Sierra Parayas: Horario y Mapa de La Línea S2 de AutobúsDokument5 SeitenSantander-Sierra Parayas: Horario y Mapa de La Línea S2 de AutobúsCésar García EguigurenNoch keine Bewertungen

- Historia Del ConcretoDokument13 SeitenHistoria Del ConcretoCamila NavarroNoch keine Bewertungen

- Lapicero Tactil - Producto InnovadorDokument78 SeitenLapicero Tactil - Producto InnovadorMeli GutiérrezNoch keine Bewertungen

- Laboratorio BI PDFDokument47 SeitenLaboratorio BI PDFFátima Rodríguez LlicánNoch keine Bewertungen

- Basura InorganicaDokument7 SeitenBasura InorganicaRikardo HReyNoch keine Bewertungen

- Exposicion ItilDokument29 SeitenExposicion ItilErnie PozoNoch keine Bewertungen

- Funciones MunicipiosDokument11 SeitenFunciones MunicipiosIvan BeltranNoch keine Bewertungen

- Caso MedcoDokument13 SeitenCaso MedcoeivanmaNoch keine Bewertungen

- Linea de Agua, de Fangos y Gas de Una Planta de TratamientoDokument11 SeitenLinea de Agua, de Fangos y Gas de Una Planta de TratamientoJeremy AlexisNoch keine Bewertungen

- Instalacion Openfire y SparkwebDokument6 SeitenInstalacion Openfire y SparkwebtlcarrillopNoch keine Bewertungen

- Agrupamiento de CapacitoresDokument9 SeitenAgrupamiento de CapacitoreshelofiNoch keine Bewertungen

- Separata Problemas de Teorìas de Rotura y Cilindros de Pared GruesaDokument39 SeitenSeparata Problemas de Teorìas de Rotura y Cilindros de Pared GruesaJS Vargas TNoch keine Bewertungen

- Actividad #3 5to Año GHCDokument3 SeitenActividad #3 5to Año GHCPedro Muro MorenoNoch keine Bewertungen

- Articulo de La Etica Del Respeto A La Naturaleza (Autoguardado) 2Dokument5 SeitenArticulo de La Etica Del Respeto A La Naturaleza (Autoguardado) 2Fabian GarciaNoch keine Bewertungen

- Doc-Gc-004 Matriz de Riesgos Gestion de La CalidadDokument15 SeitenDoc-Gc-004 Matriz de Riesgos Gestion de La CalidadErick Leonardo Valle Mendoza100% (1)

- Maquina Dispensadora de LecheDokument30 SeitenMaquina Dispensadora de LecheRogelio Antonio Madera DelgadoNoch keine Bewertungen

- Lizárraga Denisse Act2.Dokument7 SeitenLizárraga Denisse Act2.denisseNoch keine Bewertungen

- Resumen RRCC 2016Dokument44 SeitenResumen RRCC 2016Eduardo TorresNoch keine Bewertungen

- S02.s2-Taller 1 de Uso de Lean CanvasDokument23 SeitenS02.s2-Taller 1 de Uso de Lean CanvasVladimir Rojas PelaezNoch keine Bewertungen

- Manejo Sanitario y Fitosanitario de Especies Animales y VegetalesDokument3 SeitenManejo Sanitario y Fitosanitario de Especies Animales y VegetalesVinicio Viviano Varela Muñoz50% (4)

- Anyela Daniela Bravo GalvánDokument3 SeitenAnyela Daniela Bravo GalvánPipol ChinaskiNoch keine Bewertungen

- 171772538-Motoniveladora-24M 1111Dokument23 Seiten171772538-Motoniveladora-24M 1111Aron Calizaya M100% (1)

- BIOETICADokument8 SeitenBIOETICAjunior198619Noch keine Bewertungen