Beruflich Dokumente

Kultur Dokumente

07a3ec03 Switchingthoeryandlogicdesign

Hochgeladen von

Vijay KumarOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

07a3ec03 Switchingthoeryandlogicdesign

Hochgeladen von

Vijay KumarCopyright:

Verfügbare Formate

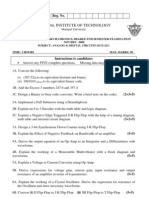

Code No: 07A3EC03

R07

Set No. 2

II B.Tech I Semester Examinations,May 2011

SWITCHING THOERY AND LOGIC DESIGN

Common to BME, ICE, E.COMP.E, E.CONT.E, EIE, EEE

Time: 3 hours

Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

?????

1. (a) Differentiate between synchronous and asynchronous circuits.

(b) Design a 2 to 4 decoder using NAND gates

[8+8]

2. Draw an ASM chart for a synchronous sequential logic circuit which produces an

output THREE 1s if three or more consecutive 1s follow the last 0 output.

Design the data processing unit and a control unit for implementing the design.

[16]

3. Explain the procedure for the following with an example

(a) Conversion from Binary to decimal number

(b) Binary subtraction using 1s complement

(c) Binary subtraction using 2s complement

(d) Conversion from gray to binary number

[16]

4. (a) Design a 4-bit Bidirectional Shift Register.

(b) Convert D flip flop to T flip flop.

5. Convert the following Mealy machine into a corresponding Moore machine.

PS

NS,Z

X=0 X=1

A C,0

B,0

B

A,1 D,0

C

B,1

A,1

D D,1 C,0

[8+8]

[16]

6. Design a combinational logic circuit with 4 inputs A, B, C, D. The output Y goes

HIGH if and only if A and C inputs go HIGH. Draw the Truth table. Minimize the

Boolean function using K-map. Draw the circuit diagram.

[16]

7. Implement the following functions in a ROM. Specify the size of ROMs required to

implement the following functions

(a) Full adder

(b) Binary to BCD converter

[16]

8. (a) Convert the following SOP equation into its POS form.

G = XY0 Z + X0 YZ0

1

Code No: 07A3EC03

R07

Set No. 2

(b) Reduce the following Boolean expressions to three literals.

A0 C0 + ABC +AC0

?????

8+8]

Code No: 07A3EC03

R07

Set No. 4

II B.Tech I Semester Examinations,May 2011

SWITCHING THOERY AND LOGIC DESIGN

Common to BME, ICE, E.COMP.E, E.CONT.E, EIE, EEE

Time: 3 hours

Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

?????

1. Draw an ASM chart for a synchronous sequential logic circuit which produces an

output THREE 1s if three or more consecutive 1s follow the last 0 output.

Design the data processing unit and a control unit for implementing the design.

[16]

2. (a) Differentiate synchronous and asynchronous circuits

(b) Design a 2 to 4 decoder using NAND gates

[8+8]

3. Implement the following functions in a ROM. Specify the size of ROMs required to

implement the following functions

(a) Full adder

(b) Binary to BCD converter

[16]

4. Design a combinational logic circuit with 4 inputs A, B, C, D. The output Y goes

HIGH if and only if A and C inputs go HIGH. Draw the Truth table. Minimize the

Boolean function using K-map. Draw the circuit diagram.

[16]

5. Convert the following Mealy machine into a corresponding Moore machine.

PS

NS,Z

X=0 X=1

A C,0

B,0

B

A,1 D,0

C

B,1

A,1

D D,1 C,0

[16]

6. Explain the procedure for the following with an example

(a) Conversion from Binary to decimal number

(b) Binary subtraction using 1s complement

(c) Binary subtraction using 2s complement

(d) Conversion from gray to binary number

[16]

7. (a) Design a 4-bit Bidirectional Shift Register.

(b) Convert D flip flop to T flip flop.

8. (a) Convert the following SOP equation into its POS form.

G = XY0 Z + X0 YZ0

3

[8+8]

Code No: 07A3EC03

R07

Set No. 4

(b) Reduce the following Boolean expressions to three literals.

A0 C0 + ABC +AC0

?????

8+8]

Code No: 07A3EC03

R07

Set No. 1

II B.Tech I Semester Examinations,May 2011

SWITCHING THOERY AND LOGIC DESIGN

Common to BME, ICE, E.COMP.E, E.CONT.E, EIE, EEE

Time: 3 hours

Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

?????

1. Design a combinational logic circuit with 4 inputs A, B, C, D. The output Y goes

HIGH if and only if A and C inputs go HIGH. Draw the Truth table. Minimize the

Boolean function using K-map. Draw the circuit diagram.

[16]

2. (a) Convert the following SOP equation into its POS form.

G = XY0 Z + X0 YZ0

(b) Reduce the following Boolean expressions to three literals.

A0 C0 + ABC +AC0

8+8]

3. Explain the procedure for the following with an example

(a) Conversion from Binary to decimal number

(b) Binary subtraction using 1s complement

(c) Binary subtraction using 2s complement

(d) Conversion from gray to binary number

[16]

4. (a) Differentiate synchronous and asynchronous circuits

(b) Design a 2 to 4 decoder using NAND gates

5. Convert the following Mealy machine into a corresponding Moore machine.

PS

NS,Z

X=0 X=1

A C,0

B,0

B

A,1 D,0

C

B,1

A,1

D D,1 C,0

[8+8]

[16]

6. (a) Design a 4-bit Bidirectional Shift Register.

(b) Convert D flip flop to T flip flop.

[8+8]

7. Draw an ASM chart for a synchronous sequential logic circuit which produces an

output THREE 1s if three or more consecutive 1s follow the last 0 output.

Design the data processing unit and a control unit for implementing the design.

[16]

8. Implement the following functions in a ROM. Specify the size of ROMs required to

implement the following functions

(a) Full adder

5

Code No: 07A3EC03

R07

(b) Binary to BCD converter

Set No. 1

[16]

?????

Code No: 07A3EC03

R07

Set No. 3

II B.Tech I Semester Examinations,May 2011

SWITCHING THOERY AND LOGIC DESIGN

Common to BME, ICE, E.COMP.E, E.CONT.E, EIE, EEE

Time: 3 hours

Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

?????

1. (a) Differentiate synchronous and asynchronous circuits

(b) Design a 2 to 4 decoder using NAND gates

[8+8]

2. Draw an ASM chart for a synchronous sequential logic circuit which produces an

output THREE 1s if three or more consecutive 1s follow the last 0 output.

Design the data processing unit and a control unit for implementing the design.

[16]

3. Explain the procedure for the following with an example

(a) Conversion from Binary to decimal number

(b) Binary subtraction using 1s complement

(c) Binary subtraction using 2s complement

(d) Conversion from gray to binary number

4. Convert the following Mealy machine into a corresponding Moore machine.

PS

NS,Z

X=0 X=1

A C,0

B,0

B

A,1 D,0

C

B,1

A,1

D D,1 C,0

[16]

[16]

5. (a) Design a 4-bit Bidirectional Shift Register.

(b) Convert D flip flop to T flip flop.

[8+8]

6. Implement the following functions in a ROM. Specify the size of ROMs required to

implement the following functions

(a) Full adder

(b) Binary to BCD converter

[16]

7. Design a combinational logic circuit with 4 inputs A, B, C, D. The output Y goes

HIGH if and only if A and C inputs go HIGH. Draw the Truth table. Minimize the

Boolean function using K-map. Draw the circuit diagram.

[16]

8. (a) Convert the following SOP equation into its POS form.

G = XY0 Z + X0 YZ0

7

Code No: 07A3EC03

R07

Set No. 3

(b) Reduce the following Boolean expressions to three literals.

A0 C0 + ABC +AC0

?????

8+8]

Das könnte Ihnen auch gefallen

- Intermediate Logic Student Book SampleDokument91 SeitenIntermediate Logic Student Book SamplecompasscinemaNoch keine Bewertungen

- GST Functional P2P FlowDokument74 SeitenGST Functional P2P FlowKommanapalli Jeeten100% (5)

- Human Resource Management SystemDokument84 SeitenHuman Resource Management SystemEzra Melaku100% (1)

- 9A04401 Switching Theory & Logic DesignDokument4 Seiten9A04401 Switching Theory & Logic DesignsivabharathamurthyNoch keine Bewertungen

- Digital Logic NotesDokument32 SeitenDigital Logic Notesjadad50% (2)

- Chapter 4 PLCDokument38 SeitenChapter 4 PLCDilip TheLip100% (1)

- PHP ProgrammingDokument245 SeitenPHP Programmingarogar180% (5)

- II B.Tech II Semester, Regular Examinations, April - 2012 Switching Theory and Logic DesignDokument8 SeitenII B.Tech II Semester, Regular Examinations, April - 2012 Switching Theory and Logic Design142545Noch keine Bewertungen

- Switching Theory and Logic Design QuestionsDokument8 SeitenSwitching Theory and Logic Design QuestionsvasuvlsiNoch keine Bewertungen

- 9A04306 Digital Logic DesignDokument4 Seiten9A04306 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- Switching Theory and Logic Design Exam QuestionsDokument4 SeitenSwitching Theory and Logic Design Exam QuestionsrangerNoch keine Bewertungen

- 07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrDokument8 Seiten07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrObula ReddyNoch keine Bewertungen

- Digital Logic Design Exam Questions and AnswersDokument38 SeitenDigital Logic Design Exam Questions and AnswersRajesh ViswanadhamNoch keine Bewertungen

- Switching Theory and Logic DesignDokument6 SeitenSwitching Theory and Logic DesignVijay MNoch keine Bewertungen

- 21 - 2010 - Nov - R09 - STLDDokument8 Seiten21 - 2010 - Nov - R09 - STLDvasuvlsiNoch keine Bewertungen

- R07 Set No. 2Dokument8 SeitenR07 Set No. 2Samiullah MohammedNoch keine Bewertungen

- Switching Theory and Logic DesignDokument8 SeitenSwitching Theory and Logic DesignVenkat ChadalavadaNoch keine Bewertungen

- Switching Theory and Logic DesignDokument8 SeitenSwitching Theory and Logic DesignSubrahmanyam VjsNoch keine Bewertungen

- 9A12301 Digital Logic Design & Computer OrganizationDokument4 Seiten9A12301 Digital Logic Design & Computer OrganizationsivabharathamurthyNoch keine Bewertungen

- Digital Logic DesignDokument4 SeitenDigital Logic DesignrppvchNoch keine Bewertungen

- 9A04401 Switching Theory and Logic DesignDokument4 Seiten9A04401 Switching Theory and Logic DesignsivabharathamurthyNoch keine Bewertungen

- STLD Regular Jntu Question Papers 2008Dokument9 SeitenSTLD Regular Jntu Question Papers 2008anjaneyulud100% (1)

- 9a04306-Digital Logic DesignDokument1 Seite9a04306-Digital Logic DesignSheikh Noor MohammadNoch keine Bewertungen

- 08AB303 - DIGITAL LOGIC CIRCUITSDokument3 Seiten08AB303 - DIGITAL LOGIC CIRCUITSChandru RamaswamyNoch keine Bewertungen

- RR 210204 Switching Theory & Logic DesignDokument1 SeiteRR 210204 Switching Theory & Logic DesignsivabharathamurthyNoch keine Bewertungen

- 9A12301 Digital Logic Design and Computer OrganizationDokument4 Seiten9A12301 Digital Logic Design and Computer OrganizationsivabharathamurthyNoch keine Bewertungen

- R7210504 Digital Logic DesignDokument1 SeiteR7210504 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- Ec2203 Digital Electronics r8Dokument3 SeitenEc2203 Digital Electronics r8jenifar777Noch keine Bewertungen

- Midterm LDST 2012 BatchDokument2 SeitenMidterm LDST 2012 BatchyazdanieNoch keine Bewertungen

- Rr310401-Digital Ic ApplicationsDokument2 SeitenRr310401-Digital Ic ApplicationsSRINIVASA RAO GANTANoch keine Bewertungen

- Sir Syed University of Engineering & Technology, Karachi LDST Final Exam 2011, Batch 2010Dokument2 SeitenSir Syed University of Engineering & Technology, Karachi LDST Final Exam 2011, Batch 2010Faisal YazdanieNoch keine Bewertungen

- RT 21053112016Dokument4 SeitenRT 21053112016RaunaqNoch keine Bewertungen

- Analog & Digital CircuitsDokument1 SeiteAnalog & Digital CircuitsAkhil GuptaNoch keine Bewertungen

- LDST Supplementary 2012Dokument2 SeitenLDST Supplementary 2012yazdanieNoch keine Bewertungen

- 9A04306 Digital Logic Design3Dokument1 Seite9A04306 Digital Logic Design3Mahaboob SubahanNoch keine Bewertungen

- 9A04306 Digital Logic DesignDokument4 Seiten9A04306 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- Metropolitan University, SylhetDokument1 SeiteMetropolitan University, SylhetJashon RoyNoch keine Bewertungen

- 07a80305 ComputerorganizationandarchitectureDokument8 Seiten07a80305 ComputerorganizationandarchitectureSharanya ThirichinapalliNoch keine Bewertungen

- 9A04401 Switching Theory & Logic DesignDokument4 Seiten9A04401 Switching Theory & Logic DesignsivabharathamurthyNoch keine Bewertungen

- 9A04401 Switching Theory & Logic DesignDokument1 Seite9A04401 Switching Theory & Logic DesignsivabharathamurthyNoch keine Bewertungen

- Digital Logic DesignDokument4 SeitenDigital Logic DesignShareef KhanNoch keine Bewertungen

- CS-64 Bachelor in Computer Applications Term-End Examination December, 2009 CS-64Dokument4 SeitenCS-64 Bachelor in Computer Applications Term-End Examination December, 2009 CS-64Prince AroraNoch keine Bewertungen

- (Nov-11) (EUREE-504) : Unit-IiiDokument1 Seite(Nov-11) (EUREE-504) : Unit-IiiAnand KalNoch keine Bewertungen

- CRC of BCA (2) Assignment (Revised Syllabus)Dokument17 SeitenCRC of BCA (2) Assignment (Revised Syllabus)BshrinivasNoch keine Bewertungen

- Sample - Final Exam - DLDDokument5 SeitenSample - Final Exam - DLDadlinarashid03Noch keine Bewertungen

- Computer GraphicsDokument6 SeitenComputer GraphicsPradeep KumarNoch keine Bewertungen

- 9A04306 Digital Logic DesignDokument4 Seiten9A04306 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- r05220403 Switching Theory and Logic DesignDokument8 Seitenr05220403 Switching Theory and Logic DesignSRINIVASA RAO GANTANoch keine Bewertungen

- Digital Techniques Sample Question PaperDokument5 SeitenDigital Techniques Sample Question PaperAshutosh PatilNoch keine Bewertungen

- R7210504 Digital Logic DesignDokument1 SeiteR7210504 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- R07 Set No. 2Dokument7 SeitenR07 Set No. 2Mothilal KaramtothuNoch keine Bewertungen

- pastyearDokument1 SeitepastyearharshsharmaisgreatNoch keine Bewertungen

- r05221201 Computer GraphicsDokument5 Seitenr05221201 Computer Graphicslibrarian_abitNoch keine Bewertungen

- Digital Logic Design Practice Problems Covering Number Systems, Logic Gates, Boolean Expressions & MoreDokument36 SeitenDigital Logic Design Practice Problems Covering Number Systems, Logic Gates, Boolean Expressions & MoreAlexanderHmNoch keine Bewertungen

- WWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic DesignDokument4 SeitenWWW - Manaresults.Co - In: II B. Tech I Semester Model Question Paper Oct/Nov - 2017 Switching Theory and Logic Designbadiganti tejakrishnaNoch keine Bewertungen

- S T L DDokument12 SeitenS T L DMohan Krishna0% (1)

- Veermata Jijabai Technological Institute: End Semester Examination December 2018 SEM-I, First Year MCADokument3 SeitenVeermata Jijabai Technological Institute: End Semester Examination December 2018 SEM-I, First Year MCApradnya kingeNoch keine Bewertungen

- Even Odd 2009 LDST 2013Dokument2 SeitenEven Odd 2009 LDST 2013yazdanieNoch keine Bewertungen

- Following Paper ID and Roll No. To Be Filled in Your Answer Book)Dokument3 SeitenFollowing Paper ID and Roll No. To Be Filled in Your Answer Book)Param WassonNoch keine Bewertungen

- EE370A Practice ProblemsDokument2 SeitenEE370A Practice ProblemsMalay Kumar MohantaNoch keine Bewertungen

- R7220404 Switching Theory and Logic DesignDokument1 SeiteR7220404 Switching Theory and Logic DesignsivabharathamurthyNoch keine Bewertungen

- Mca 1 Sem Computer Organization and Architecture Kca105 2022Dokument1 SeiteMca 1 Sem Computer Organization and Architecture Kca105 2022kimog66911Noch keine Bewertungen

- Attainable Region Theory: An Introduction to Choosing an Optimal ReactorVon EverandAttainable Region Theory: An Introduction to Choosing an Optimal ReactorNoch keine Bewertungen

- CST Reporting Reconciling AssetsDokument68 SeitenCST Reporting Reconciling AssetsVijay KumarNoch keine Bewertungen

- Expo OrtDokument36 SeitenExpo OrtVijay KumarNoch keine Bewertungen

- R11i10 Approvals Management ERDDokument1 SeiteR11i10 Approvals Management ERDMarwan SNoch keine Bewertungen

- Tpti ExportDokument36 SeitenTpti ExportVijay KumarNoch keine Bewertungen

- Personnel HR General ERD PDFDokument1 SeitePersonnel HR General ERD PDFkike309Noch keine Bewertungen

- FAQ On Covid 19-OICL 24 - 04 - 20Dokument5 SeitenFAQ On Covid 19-OICL 24 - 04 - 20Vijay KumarNoch keine Bewertungen

- Junior Assistant Cum Computer OperatorDokument24 SeitenJunior Assistant Cum Computer OperatorKrishna SharmaNoch keine Bewertungen

- (WWW - Entrance-Exam - Net) - Computer Proficiency PDFDokument5 Seiten(WWW - Entrance-Exam - Net) - Computer Proficiency PDFVijay KumarNoch keine Bewertungen

- FAQ On Covid 19-OICL 24 - 04 - 20Dokument5 SeitenFAQ On Covid 19-OICL 24 - 04 - 20Vijay KumarNoch keine Bewertungen

- Excel4Apps GL Wand Validated Integration With Oracle E-Business Suite 12.2Dokument2 SeitenExcel4Apps GL Wand Validated Integration With Oracle E-Business Suite 12.2Vijay KumarNoch keine Bewertungen

- Fixed Asset Reporting PDFDokument28 SeitenFixed Asset Reporting PDFamine_tunisiaNoch keine Bewertungen

- Revised - Uniform-Acquittance-2020-21Dokument1 SeiteRevised - Uniform-Acquittance-2020-21Vijay KumarNoch keine Bewertungen

- Excel4Apps GL Wand Validated Integration With Oracle E-Business Suite 12.2Dokument2 SeitenExcel4Apps GL Wand Validated Integration With Oracle E-Business Suite 12.2Vijay KumarNoch keine Bewertungen

- Analysis With Subledger EG Format - Tax Reporting CSV - DEM-02Dokument14 SeitenAnalysis With Subledger EG Format - Tax Reporting CSV - DEM-02Vijay KumarNoch keine Bewertungen

- Timesheet TemplateDokument3 SeitenTimesheet TemplateVijay KumarNoch keine Bewertungen

- R12.x Oracle Financials Functional Foundation (Training On Demand)Dokument4 SeitenR12.x Oracle Financials Functional Foundation (Training On Demand)Vijay KumarNoch keine Bewertungen

- FAQ On Covid 19-OICL 24 - 04 - 20Dokument5 SeitenFAQ On Covid 19-OICL 24 - 04 - 20Vijay KumarNoch keine Bewertungen

- (WWW - Entrance-Exam - Net) - Computer Proficiency PDFDokument5 Seiten(WWW - Entrance-Exam - Net) - Computer Proficiency PDFVijay KumarNoch keine Bewertungen

- Po Detail RPTDokument13 SeitenPo Detail RPTVijay KumarNoch keine Bewertungen

- Revised - Uniform-Acquittance-2020-21Dokument1 SeiteRevised - Uniform-Acquittance-2020-21Vijay KumarNoch keine Bewertungen

- Project QuestionsDokument2 SeitenProject QuestionsVijay KumarNoch keine Bewertungen

- Revised - Uniform-Acquittance-2020-21Dokument1 SeiteRevised - Uniform-Acquittance-2020-21Vijay KumarNoch keine Bewertungen

- How To Build Report On OBIEE PDFDokument19 SeitenHow To Build Report On OBIEE PDFVijay KumarNoch keine Bewertungen

- Gds Telangana 2019 NotificationDokument45 SeitenGds Telangana 2019 NotificationQ TubeNoch keine Bewertungen

- How To Build Report On OBIEE PDFDokument19 SeitenHow To Build Report On OBIEE PDFVijay KumarNoch keine Bewertungen

- QueiresDokument17 SeitenQueiresdbareddyNoch keine Bewertungen

- An Optimized Pixel-Wise Weighting Approach For Patch-Based Image DenoisingDokument5 SeitenAn Optimized Pixel-Wise Weighting Approach For Patch-Based Image DenoisingVijay KumarNoch keine Bewertungen

- A Novel Approach For Patch-Based Image Denoising Based On Optimized Pixel-Wise WeightingDokument6 SeitenA Novel Approach For Patch-Based Image Denoising Based On Optimized Pixel-Wise WeightingVijay KumarNoch keine Bewertungen

- ADokument2 SeitenAMa JunNoch keine Bewertungen

- PLC Editor ManualEN V13Dokument46 SeitenPLC Editor ManualEN V13S KumarNoch keine Bewertungen

- Hardware & VHDL QuestionsDokument3 SeitenHardware & VHDL QuestionswahidNoch keine Bewertungen

- Note 3 PDFDokument7 SeitenNote 3 PDFProdipto OrchoNoch keine Bewertungen

- DEL Lab Manual - Experiment 7Dokument6 SeitenDEL Lab Manual - Experiment 7sara michiko100% (1)

- Title: To Study and Implement Conjunction, Disjunc-Tion and NegationDokument15 SeitenTitle: To Study and Implement Conjunction, Disjunc-Tion and NegationEVEREST NEPALNoch keine Bewertungen

- "Boolean Algebra and Its Application": Master of ScienceDokument52 Seiten"Boolean Algebra and Its Application": Master of ScienceMaster PrintersNoch keine Bewertungen

- 104 2011 3 BDokument18 Seiten104 2011 3 BRian0% (1)

- A Practical Theory of Programming, 2005, Eric C. R. HehnerDokument242 SeitenA Practical Theory of Programming, 2005, Eric C. R. HehnerVedran Jhoy ErdeljanNoch keine Bewertungen

- MATH PATTERNS & LANGUAGEDokument4 SeitenMATH PATTERNS & LANGUAGEJEAN VIKTORIA GETUBIGNoch keine Bewertungen

- Basic Electronics November 2018 1920 103Dokument5 SeitenBasic Electronics November 2018 1920 103James MukhwanaNoch keine Bewertungen

- MMW Module 4Dokument27 SeitenMMW Module 4Cha Eun WooNoch keine Bewertungen

- 1.0 Computer System 2021 - 2022 StudentsDokument145 Seiten1.0 Computer System 2021 - 2022 Studentsnurain syuhadaNoch keine Bewertungen

- PLC Editor ManualV1.5-EnDokument92 SeitenPLC Editor ManualV1.5-Entarom nasteknikaNoch keine Bewertungen

- CU-2022 B.Sc. (General) Computer Science Semester-1 Paper-CC1-GE1 QPDokument2 SeitenCU-2022 B.Sc. (General) Computer Science Semester-1 Paper-CC1-GE1 QPgozombie43Noch keine Bewertungen

- PSET 3 MOS Logic Gates - QDokument4 SeitenPSET 3 MOS Logic Gates - QramchanduriNoch keine Bewertungen

- Lecture 4 S1.2.2 Mathematical Language and Symbols (Truth Tables)Dokument12 SeitenLecture 4 S1.2.2 Mathematical Language and Symbols (Truth Tables)Dum AccountNoch keine Bewertungen

- Cpe 301 Lab 1 - CaringalDokument8 SeitenCpe 301 Lab 1 - CaringalAlecxis CaringalNoch keine Bewertungen

- Boolean algebra concepts and applicationsDokument25 SeitenBoolean algebra concepts and applicationsSoni Mishra TiwariNoch keine Bewertungen

- Logic and Critical Reasoning BookDokument223 SeitenLogic and Critical Reasoning BookmsbooonNoch keine Bewertungen

- 3) Mathematical ReasoningDokument6 Seiten3) Mathematical ReasoningJanakiNoch keine Bewertungen

- Arch Module Final-1Dokument148 SeitenArch Module Final-1Elijah IbsaNoch keine Bewertungen

- Java FundamentalsDokument85 SeitenJava FundamentalsKene BirhanuNoch keine Bewertungen

- GE - Math Module 6Dokument11 SeitenGE - Math Module 6Cha SantoniaNoch keine Bewertungen

- 2 Logical ReasoningDokument49 Seiten2 Logical ReasoningM4r14gNoch keine Bewertungen

- Experiment 3 (A) : Washing Machine Control Using Basic AND & NOT GatesDokument2 SeitenExperiment 3 (A) : Washing Machine Control Using Basic AND & NOT GatesDivyanshu BoseNoch keine Bewertungen