Beruflich Dokumente

Kultur Dokumente

VLSI Design Assignment2 2015

Hochgeladen von

AkshayCopyright

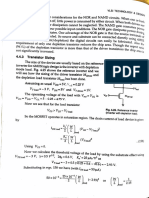

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

VLSI Design Assignment2 2015

Hochgeladen von

AkshayCopyright:

Verfügbare Formate

VLSI Design, V sem B.

E (E&C)

Assignment 2 [L. No. L9-L16]

I Design/analysis problems/ descriptive questions

1. Implement the given function S which gives the sum of two inputs with a carry bit, using

NMOS pass transistor logic.

BC

(BC) +

(AB) C + A

S = ABC + A

2. Give the optimal implementation of two input XOR function using

[i] Only n-type/ p-type pass transistors

[ii] TGs

[iii] CMOS gate based approach

3. With the circuit diagram of CMOS inverter explain how the transfer characteristic is

obtained graphically. Explain the working operation of CMOS inverter for different regions.

4. Derive the expression for the Vinv voltage for a CMOS inverter

5. Refer the pass-transistor based logic network given in Fig. 5

[i] Determine the truth table for the circuit. What logic function does it implement?

[ii] Does the PMOS transistor serve any useful purpose?

6. Give the realization of half adder using CMOS gate based logic.

7. Find the midpoint voltage Vx and output voltage Vo, for the chain of two NMOS pass

transistors shown in Fig. 7. Assume VDD = 2.5V and Vthn = 0.5V.

8. Follow the procedure below to construct the CMOS logic gate for the function =

+

[i] Write the equation for the nMOS network.

[ii] Write the equation for the pMOS network.

[iii] Use the equations in (a) and (b) to construct a schematic for f.

[iv] Verify the nMOS and pMOS networks are proper complements (series groups in nMOS

are parallel in pMOS etc.)

9. Give the implementation of 4:1 MUX using a) NMOS pass transistors and b) Transmission

gates

10. Why depletion load NMOS inverter preferred over Enhancement load inverter? Explain

with proper circuit diagram.

11. Find the output voltage for the pass transistor networks shown in Fig. 11. Neglect the body

effect.

12. Derive Zpu/Zpd ratio for NMOS Inverter with depletion mode pull up.

13. Give the circuit implementation for following:

[i] Depletion load NMOS inverter [ii] CMOS Inverter [iii] Two-input NMOS NOR gate [iv]

Three variable NMOS majority function [v] Two-input NMOS EXOR gate [vi] Two-input

CMOS EX-NOR gate [vii] Two-input CMOS NOR gate

14. Derive Zpu/ Zpd for driven NMOS inverter when the input is applied through NMOS pass

transistor.

II Give objective/specific answers

1.

2.

3.

4.

5.

6.

7.

Why length of MOSFET is always kept minimum?

Why does drain current reduce due to body effect?

Is CMOS a ratioed logic? What do you understand by the term ratioed logic?

Why some CMOS gate based circuits use aspect ratios? Explain

What are the advantages of TGs over pass transistors?

Discuss the effect of n/p on the transfer characteristic of CMOS inverter.

Compare the transfer curve for NMOS (with depletion mode pull up) and CMOS

Inverter.

8. Why NMOS pass transistors were preferred over PMOS ones for switch based design?

Fig. 5

Fig. 7

Fig. 11

Date for completion: 3rd Sept 2015

*****

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- A. Nagoor Kani - Microprocessor (8085) and Its Applications-McGraw-Hill Education (2005) PDFDokument392 SeitenA. Nagoor Kani - Microprocessor (8085) and Its Applications-McGraw-Hill Education (2005) PDFGulrez M40% (5)

- Microelectronic Circuit Design 5th Edition Jaeger Solutions ManualDokument25 SeitenMicroelectronic Circuit Design 5th Edition Jaeger Solutions Manualserenadinhmzi100% (27)

- Microprocessors NPTELDokument400 SeitenMicroprocessors NPTELDebajyoti DattaNoch keine Bewertungen

- Analysis and Characterization of The Depletion-Mode IgfetDokument10 SeitenAnalysis and Characterization of The Depletion-Mode Igfetbalaji_gawalwad9857Noch keine Bewertungen

- Mod 5 LP VLSI - Ktunotes - in PDFDokument115 SeitenMod 5 LP VLSI - Ktunotes - in PDFakhilabrahamNoch keine Bewertungen

- An Overview of MicroprocessorDokument16 SeitenAn Overview of MicroprocessorPraveen SinghNoch keine Bewertungen

- Fundamentals of CMOS VLSI (Complete Notes) PDFDokument214 SeitenFundamentals of CMOS VLSI (Complete Notes) PDFENG18EC0062-MD TANVEERNoch keine Bewertungen

- Depletion MOSFETsDokument10 SeitenDepletion MOSFETsXavier Pacheco PaulinoNoch keine Bewertungen

- Syllabus EXTC Sem 6 NewDokument21 SeitenSyllabus EXTC Sem 6 Newudhayakumar_cNoch keine Bewertungen

- Unit # 3 Basics of Digital Cmos Design: Chapter 1: Combinational Mos Logic CircuitsDokument67 SeitenUnit # 3 Basics of Digital Cmos Design: Chapter 1: Combinational Mos Logic CircuitsPunith Gowda M B50% (2)

- CourceMeterials DEL34Dokument206 SeitenCourceMeterials DEL34Jeramaine Torres100% (1)

- 28-Pseudo Nmos, DCVSL and Dynamic Logic-12!09!2020 (12-Sep-2020) Material I 12-Sep-2020 CMOS Combinational Circuit DesignDokument22 Seiten28-Pseudo Nmos, DCVSL and Dynamic Logic-12!09!2020 (12-Sep-2020) Material I 12-Sep-2020 CMOS Combinational Circuit DesignParth VijayNoch keine Bewertungen

- Maths Predicts Earthquakes: Digikey - Co.UkDokument28 SeitenMaths Predicts Earthquakes: Digikey - Co.UkstevesalmNoch keine Bewertungen

- Transistor SizingDokument3 SeitenTransistor Sizingsargamrastogi8Noch keine Bewertungen

- CMOS Transistor Layout KungFu Preliminary ReleaseDokument35 SeitenCMOS Transistor Layout KungFu Preliminary ReleaseBabu ChintapalliNoch keine Bewertungen

- FUNDAMENTALS of CMOS VLSI 5th SEM ECE PDFDokument190 SeitenFUNDAMENTALS of CMOS VLSI 5th SEM ECE PDFVarunKaradesaiNoch keine Bewertungen

- Chipworks Analysis - Linear Technology's LTC3108 DC-DC ConverterDokument4 SeitenChipworks Analysis - Linear Technology's LTC3108 DC-DC ConverteraalvarcaNoch keine Bewertungen

- Dynamic Logic CktsDokument16 SeitenDynamic Logic CktsaashishscribdNoch keine Bewertungen

- Cmos Vtu NotesDokument35 SeitenCmos Vtu NotesManoj Aditya0% (1)

- Read-Only Memory - WikipediaDokument17 SeitenRead-Only Memory - WikipediaMuhammad usamaNoch keine Bewertungen

- LPVLSI Unit 1 NotesDokument37 SeitenLPVLSI Unit 1 NotesSai Sreeja100% (2)

- Pass Transistor Logic PDFDokument25 SeitenPass Transistor Logic PDFTejas KumbarNoch keine Bewertungen

- Microprocessor and ApplicationsDokument4 SeitenMicroprocessor and ApplicationsNabaraj KhatiwadaNoch keine Bewertungen

- Logic Gate Families: Learning ObjectivesDokument23 SeitenLogic Gate Families: Learning Objectiveskalyan100% (1)

- Question BankDokument13 SeitenQuestion BankRishi JhaNoch keine Bewertungen

- Class 08: NMOS, Pseudo-NMOSDokument6 SeitenClass 08: NMOS, Pseudo-NMOSPoonam Pratap KadamNoch keine Bewertungen

- Complete Notes of MicroprocesserDokument36 SeitenComplete Notes of Microprocesser2008 AvadhutNoch keine Bewertungen

- Low Power VLSI Circuits & Systems Complete NotesDokument66 SeitenLow Power VLSI Circuits & Systems Complete NotesSai SreejaNoch keine Bewertungen

- 8085 Microprocessor SimulatorDokument30 Seiten8085 Microprocessor Simulatorapi-3798769100% (4)

- IBPS IT Officer Model Questions Computer MIcroprocessor and Assembly Language MCQ Question BankDokument146 SeitenIBPS IT Officer Model Questions Computer MIcroprocessor and Assembly Language MCQ Question BankNaveen KrishnanNoch keine Bewertungen