Beruflich Dokumente

Kultur Dokumente

IDT Power Supply

Hochgeladen von

RishiCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

IDT Power Supply

Hochgeladen von

RishiCopyright:

Verfügbare Formate

Power Supply Noise Rejection

AN-806

APPLICATION NOTE

Introduction

This application note describes the procedure used within the Timing and Synchronization (TSD) division of IDT to analyze the

PSNR for its devices. Power supply noise rejection (PSNR) is a measurement of how well a circuit rejects noise from various

frequencies which are coupled into the power supply. In actual high speed analog and digital circuitry, the power supply pins are

vulnerable to random noise Most customer designs use linear voltage regulators or switching voltage regulators as the power

supply for ICs. Linear regulators will almost always get input voltage from a switching DC/DC converter. Therefore, power supply

noises in a customer board typically come from the switching noise of the power supply and coupling from other high-frequency

sections of the circuit board.

Many of the problems facing PCB designers today are related to power supply noise. There are guidelines that can be used to

solve simple issue. For more complex issues, a better understanding and consideration of all the parameters will be required to

provide a clean solution. For this reason, it is essential to understand the PSNR of the clock devices. This can assist in designing

the correct bypassing and decoupling for the system.

Power Supply Filtering Topology

Figure 1 is a simplified 3-component power supply filtering circuit that is recommended for a power rail. It consists of a 0.1F

capacitor (C1) a ferrite bead (FB1) and a 10F capacitor (C2). While C1, FB1 and C2 are for the power rail, C3 is used for each

power pin supplied by this rail. If a power rail supplies multiple power pins, each power pin will have a 0.1F capacitor for

decoupling.

Figure 1. Power Supply Filtering Circuit Topology

The ferrite bead above is any surface-mount bead with sufficient current rating for the circuits supplied. Please refer to AN-805

for ferrite bead recommendations.

Effectiveness Study of the Noise Rejection Circuits

The frequency response is used to study the attenuation capability the above circuit demonstrates on different frequency

elements of a signal (noise). In the following sections of this application note, frequency response of the circuit is plotted by

sweeping C1, C2 and C3, respectively:

Figure 2: Sweeping C1 while keeping C2 = 10F, C3 = 0.1F Optimal value for C1 is 0.1F

Figure 3: Sweeping C2 while keeping C1 = 0.1F, C3 = 0.1F Optimal value for C2 is 10F

Figure 4: Sweeping C3 while keeping C1 = 0.1F, C2 = 10F Optimal value for C3 is 0.1F

AN-806 REVISION A 12/04/13

2013 Integrated Device Technology, Inc.

AN-806

POWER SUPPLY NOISE REJECTION

Figure 2. Sweeping C1 while keeping C2 = 10F, C3 = 0.1F

Figure 3. Sweeping C2 while keeping C1 = 0.1F, C3 = 0.1F

AN-806 REVISION A 12/04/13

AN-806

POWER SUPPLY NOISE REJECTION

Figure 4. Sweeping C3 while keeping C1 = 0.1F, C2 = 10F

Power Supply Noise Rejection Measurements

PSNR is measured by injecting a sinusoidal signal of a known amplitude and frequency onto the various power supply pins of

the devices. Many of the devices in the TSD portfolio contain multiple power supply pins. The two of interest are the core power

pin and the analog power pin. The core power pin primarily supplies voltage to all PLL peripherals while the analog power pin

supplies the voltage to the PLL. Each power pin should be analyzed independently, and noise should be applied to one power

pin at a time.

The technique used for applying the injected frequency into the device supply uses an inductor which presents a high AC

impedance back to the supply. Then a signal from a generator is injected through a capacitor after the inductor at the pin of the

DUT. Refer to Figure 1. Both the input and output should be monitored with an oscilloscope and Spectrum analyzer. The

oscilloscope is used to ensure the signal amplitude while the spectrum analyzer is used to measure the deterministic jitter.

Figure 5. PSNR Schematic

AN-806 REVISION A 12/04/13

AN-806

POWER SUPPLY NOISE REJECTION

In order to analyze the performance of the device, initially all external bypass and decoupling capacitors should be removed. A

50mV signal is swept from a start to a stop frequency. The 1kHz to 50MHz sweep range covers most of standard frequencies

which occur in typical applications.

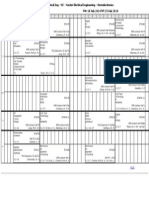

Table 1. PSNR Configuration

Power Pin

Temperature (C) Signal Amplitude (mV) Start Frequency (kHz) Stop Frequency (MHz)

Core Voltage

25

50

50

Analog Voltage

25

50

50

The following graph represents three tests of PSNR data. First, the device was swept without any decoupling or bypass

capacitors. Notice, the deterministic jitter peaked at approximately 400kHz. Next, a 0.1f bypass capacitor was added and the

noise decreased significantly. Lastly, in addition to the 0.1f, a 10f capacitor was added and majority of the noise is filtered.

Refer to Figure 2.

In conclusion, the combination of a 0.1f and 10f capacitor will attenuate some of the noise generated by a switching power

supplies. For many of the TSD devices, a power supply filter with a ferrite bead is recommended. This will attenuate noise

between 100kHz and 600kHz.

Figure 6. Deterministic Jitter versus Noise Frequency

Device without any bypass

or decoupling capacitors

Bypass capacitor

Bypass and

Decoupling capacitor

1k

10k

100k

1M

10M

100M

Summary

This application note proposes a simple power supply noise rejection topology consisting of two capacitors and a ferrite bead.

By sweeping the values of the capacitors, a noise-filtering circuit with recommended component values is provided in Figure 1.

The filter performance is designed for a wide range of noise frequencies. This low-pass filter starts to attenuate noise at

approximately 10kHz. If a specific frequency noise component is known, such as switching power supply frequencies, it is

recommended that component values be adjusted and if required, additional filtering be added. Additionally, good general design

practices for power plane voltage stability suggests adding bulk capacitance in the local area of all devices.

Overall, this filtering circuit provides significant noise attenuation in frequency range of 10KHz to 100MHz compared with a

0.1F-only filtering. Figure7 shows the comparison between a 0.1F-only filter and Figure 1 filtering circuit.

AN-806 REVISION A 12/04/13

AN-806

POWER SUPPLY NOISE REJECTION

Figure 7. Noise Rejection Comparison: 0.1F Capacitor Only vs Filtering Circuit by Figure 1

AN-806 REVISION A 12/04/13

AN-806

POWER SUPPLY NOISE REJECTION

Corporate Headquarters

Sales

Tech Support

6024 Silver Creek Valley Road

San Jose, CA 95138 USA

1-800-345-7015 or

408-284-8200

Fax: 408-284-2775

www.IDT.com

email: clocks@idt.com

480-763-2056

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDTs sole discretion. All information in this document,

including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not

guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the

suitability of IDTs products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any

license under intellectual property rights of IDT or any third parties.

IDTs products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Product specification subject to change without notice. Other trademarks and service marks used herein, including protected names, logos and

designs, are the property of IDT or their respective third party owners.

Copyright 2013. All rights reserved.

Das könnte Ihnen auch gefallen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- What To Bring To The RegistrationDokument1 SeiteWhat To Bring To The RegistrationRishiNoch keine Bewertungen

- Bode PlotDokument19 SeitenBode Plotkoolking786Noch keine Bewertungen

- Random Story 2 WorksheetDokument1 SeiteRandom Story 2 WorksheetRishiNoch keine Bewertungen

- 56QFN SocketDokument2 Seiten56QFN SocketRishiNoch keine Bewertungen

- Demystifying Noise Spectre ExampleDokument20 SeitenDemystifying Noise Spectre ExampleRishiNoch keine Bewertungen

- Interval-Valued and Fuzzy-Valued Random Variables: From Computing Sample Variances To Computing Sample CovariancesDokument8 SeitenInterval-Valued and Fuzzy-Valued Random Variables: From Computing Sample Variances To Computing Sample CovariancesMichael HaleNoch keine Bewertungen

- Interval-Valued and Fuzzy-Valued Random Variables: From Computing Sample Variances To Computing Sample CovariancesDokument8 SeitenInterval-Valued and Fuzzy-Valued Random Variables: From Computing Sample Variances To Computing Sample CovariancesMichael HaleNoch keine Bewertungen

- Readme (Counter)Dokument1 SeiteReadme (Counter)dabs230Noch keine Bewertungen

- Keep Burglars OutDokument2 SeitenKeep Burglars OutRishiNoch keine Bewertungen

- Inventory List Van HasseltlaanDokument1 SeiteInventory List Van HasseltlaanRishiNoch keine Bewertungen

- Hominid EvolutionDokument2 SeitenHominid EvolutionJosephine TorresNoch keine Bewertungen

- Sample WordSample - WordDokument1 SeiteSample WordSample - WordAlvin TanNoch keine Bewertungen

- Five Minute Guide To LatexDokument6 SeitenFive Minute Guide To LatexΚΛΕΑΝΘΗΣ ΜΑΝΩΛΟΠΟΥΛΟΣNoch keine Bewertungen

- Eduroam in TU DelftDokument5 SeitenEduroam in TU DelftRishiNoch keine Bewertungen

- Bode PlotDokument19 SeitenBode Plotkoolking786Noch keine Bewertungen

- Eduroam For MobileDokument2 SeitenEduroam For MobileRishiNoch keine Bewertungen

- TU Delft Time Table3 - 1Dokument1 SeiteTU Delft Time Table3 - 1RishiNoch keine Bewertungen

- Airport MapDokument1 SeiteAirport MapRishiNoch keine Bewertungen

- MOSFET Amplifier Large Signal Analysis: Circuits ElectronicsDokument21 SeitenMOSFET Amplifier Large Signal Analysis: Circuits ElectronicsRishiNoch keine Bewertungen

- LPF CurvesDokument1 SeiteLPF CurvesRishiNoch keine Bewertungen

- Eduroam in TU DelftDokument5 SeitenEduroam in TU DelftRishiNoch keine Bewertungen

- Mixed Mode Journal ArticleDokument16 SeitenMixed Mode Journal ArticleRishiNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Samsung Color Laser Printer CLP 510 510N Parts and Service ManualDokument227 SeitenSamsung Color Laser Printer CLP 510 510N Parts and Service Manualmehdi_palangiNoch keine Bewertungen

- Hkts 200 Sub: Service ManualDokument39 SeitenHkts 200 Sub: Service Manualjuan camaneyNoch keine Bewertungen

- Oz964gn PDFDokument14 SeitenOz964gn PDFJesus E Lopez B100% (1)

- BC817Dokument7 SeitenBC817RaduNoch keine Bewertungen

- Power Inverter: Model BI800T and BI800FDokument18 SeitenPower Inverter: Model BI800T and BI800FG NAIRNoch keine Bewertungen

- Switching Power Supply Type SPD 120W New DIN Rail Mounting: Product de Scrip Tion Ordering Key SP D 24 120 1 B NDokument4 SeitenSwitching Power Supply Type SPD 120W New DIN Rail Mounting: Product de Scrip Tion Ordering Key SP D 24 120 1 B Nimadz853Noch keine Bewertungen

- Operating Mannual of Digital Automatic Voltage Regulator (Davr)Dokument31 SeitenOperating Mannual of Digital Automatic Voltage Regulator (Davr)ArvindPrasadNoch keine Bewertungen

- 04 Trobleshooting PDFDokument46 Seiten04 Trobleshooting PDFDwane Duncan100% (1)

- EMC Analysis WorkflowDokument46 SeitenEMC Analysis WorkflowCườngNoch keine Bewertungen

- USB3 Accelerator Module DatasheetDokument22 SeitenUSB3 Accelerator Module DatasheetSourabh SaikiaNoch keine Bewertungen

- Biovibez - Motion Sensor - Model - Mp-Ac1-R2: Save Energy and AutomateDokument8 SeitenBiovibez - Motion Sensor - Model - Mp-Ac1-R2: Save Energy and AutomateVikaas JainNoch keine Bewertungen

- DSH 332-207 1Dokument4 SeitenDSH 332-207 1alizanelectronicNoch keine Bewertungen

- Screenshot 2023-07-03 at 17.23.05Dokument1 SeiteScreenshot 2023-07-03 at 17.23.05Invincible DestroyerNoch keine Bewertungen

- DBATU UG EXTC Engg Syllabus With Cover Page 1Dokument155 SeitenDBATU UG EXTC Engg Syllabus With Cover Page 1Sudhirkumar DhotreNoch keine Bewertungen

- LG 42PQ30 Plasma TV Single Scan Troubleshooting Training Manual 1 PDFDokument123 SeitenLG 42PQ30 Plasma TV Single Scan Troubleshooting Training Manual 1 PDFJim FordNoch keine Bewertungen

- High Efficiency 200W Power Supply For Leds Lighting ApplicationsDokument21 SeitenHigh Efficiency 200W Power Supply For Leds Lighting Applicationsorange2011Noch keine Bewertungen

- Schematic 1. Basic ZVS DriverDokument23 SeitenSchematic 1. Basic ZVS DriverRoberto AlejandroNoch keine Bewertungen

- Cours Bob Ines Ferrite SDokument975 SeitenCours Bob Ines Ferrite SJosé Miguel MartínezNoch keine Bewertungen

- Wavefront Compact Series: Applications GuideDokument247 SeitenWavefront Compact Series: Applications GuidejassconsNoch keine Bewertungen

- DC-DC Converters - Buck Converter - 1Dokument17 SeitenDC-DC Converters - Buck Converter - 1Ashraf YusofNoch keine Bewertungen

- Welch Allyn SolarcDokument34 SeitenWelch Allyn SolarcigabygNoch keine Bewertungen

- Designing An LLC Resonant Half-BridgeDokument36 SeitenDesigning An LLC Resonant Half-Bridgecristian.rodriguezNoch keine Bewertungen

- Resonant OcnverterDokument7 SeitenResonant Ocnvertersatyam swarup dubeyNoch keine Bewertungen

- Features Description: D D D D D D D D D D D DDokument41 SeitenFeatures Description: D D D D D D D D D D D DqeqeNoch keine Bewertungen

- Samsung Scx-4824fn-Xbh 4828fn SMDokument177 SeitenSamsung Scx-4824fn-Xbh 4828fn SMPreduta MonicaNoch keine Bewertungen

- Elektor Electronics 2021 05-06.UKDokument116 SeitenElektor Electronics 2021 05-06.UKPoka007100% (3)

- Soundbar Design From Start To Finish PDFDokument25 SeitenSoundbar Design From Start To Finish PDFgrtabhilkwNoch keine Bewertungen

- PDF LR8 MicrochipDokument16 SeitenPDF LR8 MicrochipElijah MathewNoch keine Bewertungen

- ABL7REDokument16 SeitenABL7REeehassaanNoch keine Bewertungen

- DC DC Converters Output NoiseDokument10 SeitenDC DC Converters Output NoiseMallickarjuna AsNoch keine Bewertungen