Beruflich Dokumente

Kultur Dokumente

N-Channel Trenchmos Transistor Irf630, Irf630S: Features Symbol Quick Reference Data

Hochgeladen von

lord mace tyrellOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

N-Channel Trenchmos Transistor Irf630, Irf630S: Features Symbol Quick Reference Data

Hochgeladen von

lord mace tyrellCopyright:

Verfügbare Formate

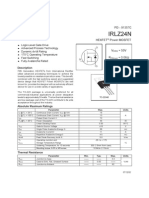

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

FEATURES

IRF630, IRF630S

SYMBOL

QUICK REFERENCE DATA

Trench technology

Low on-state resistance

Fast switching

Low thermal resistance

VDSS = 200 V

ID = 9 A

g

RDS(ON) 400 m

s

GENERAL DESCRIPTION

N-channel, enhancement mode field-effect power transistor using Trench technology, intended for use in off-line

switched mode power supplies, T.V. and computer monitor power supplies, d.c. to d.c. converters, motor control circuits

and general purpose switching applications.

The IRF630 is supplied in the SOT78 (TO220AB) conventional leaded package

The IRF630S is supplied in the SOT404 (D2PAK) surface mounting package

PINNING

SOT78 (TO220AB)

PIN

SOT404 (D2PAK)

DESCRIPTION

tab

tab

gate

drain1

source

tab

drain

1 23

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER

CONDITIONS

MIN.

MAX.

UNIT

VDSS

VDGR

VGS

ID

Drain-source voltage

Drain-gate voltage

Gate-source voltage

Continuous drain current

Tj = 25 C to 175C

Tj = 25 C to 175C; RGS = 20 k

IDM

PD

Tj, Tstg

Pulsed drain current

Total power dissipation

Operating junction and

storage temperature

- 55

200

200

20

9

6.3

36

88

175

V

V

V

A

A

A

W

C

Tmb = 25 C; VGS = 10 V

Tmb = 100 C; VGS = 10 V

Tmb = 25 C

Tmb = 25 C

1 It is not possible to make connection to pin:2 of the SOT404 package

August 1999

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF630, IRF630S

AVALANCHE ENERGY LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER

EAS

Non-repetitive avalanche

energy

IAS

Peak non-repetitive

avalanche current

CONDITIONS

MIN.

MAX.

UNIT

250

mJ

Unclamped inductive load, IAS = 5 A;

tp = 380 s; Tj prior to avalanche = 25C;

VDD 25 V; RGS = 50 ; VGS = 10 V; refer

to fig;14

THERMAL RESISTANCES

SYMBOL PARAMETER

Rth j-mb

Rth j-a

Thermal resistance junction

to mounting base

Thermal resistance junction

to ambient

CONDITIONS

MIN.

SOT78 package, in free air

SOT404 package, pcb mounted, minimum

footprint

TYP. MAX. UNIT

1.7

K/W

60

50

K/W

K/W

ELECTRICAL CHARACTERISTICS

Tj= 25C unless otherwise specified

SYMBOL PARAMETER

CONDITIONS

V(BR)DSS

VGS = 0 V; ID = 0.25 mA;

VGS(TO)

Drain-source breakdown

voltage

Gate threshold voltage

MIN.

Tj = -55C

VDS = VGS; ID = 1 mA

Tj = 175C

Tj = -55C

RDS(ON)

gfs

IGSS

IDSS

Drain-source on-state

resistance

Forward transconductance

Gate source leakage current

Zero gate voltage drain

current

VGS = 10 V; ID = 5.4 A

Tj = 175C

VDS = 25 V; ID = 5.4 A

VGS = 20 V; VDS = 0 V

VDS = 200 V; VGS = 0 V

VDS = 160 V; VGS = 0 V; Tj = 175C

200

178

2

1

3.8

-

TYP. MAX. UNIT

3

300

9

10

0.05

-

4

6

400

1.12

100

10

250

V

V

V

V

V

m

S

nA

A

A

Qg(tot)

Qgs

Qgd

Total gate charge

Gate-source charge

Gate-drain (Miller) charge

ID = 5.9 A; VDD = 160 V; VGS = 10 V

39

6.3

21

nC

nC

nC

td on

tr

td off

tf

Turn-on delay time

Turn-on rise time

Turn-off delay time

Turn-off fall time

VDD = 100 V; RD = 10 ;

VGS = 10 V; RG = 5.6

Resistive load

8

19

25

15

ns

ns

ns

ns

Ld

Ld

Internal drain inductance

Internal drain inductance

3.5

4.5

nH

nH

Ls

Internal source inductance

Measured tab to centre of die

Measured from drain lead to centre of die

(SOT78 package only)

Measured from source lead to source

bond pad

7.5

nH

Ciss

Coss

Crss

Input capacitance

Output capacitance

Feedback capacitance

VGS = 0 V; VDS = 25 V; f = 1 MHz

959

93

54

pF

pF

pF

August 1999

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF630, IRF630S

REVERSE DIODE LIMITING VALUES AND CHARACTERISTICS

Tj = 25C unless otherwise specified

SYMBOL PARAMETER

VSD

Continuous source current

(body diode)

Pulsed source current (body

diode)

Diode forward voltage

trr

Qrr

Reverse recovery time

Reverse recovery charge

IS

ISM

August 1999

CONDITIONS

MIN.

TYP. MAX. UNIT

36

IF = 9 A; VGS = 0 V

0.85

1.2

IF = 9 A; -dIF/dt = 100 A/s;

VGS = -10 V; VR = 25 V

92

0.5

ns

C

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF630, IRF630S

Normalised Power Derating, PD (%)

10

Transient thermal impedance, Zth j-mb (K/W)

100

90

80

D = 0.5

70

0.2

60

0.1

50

40

P

D

0.05

0.1

30

D = tp/T

tp

0.02

20

single pulse

10

0.01

1E-06

0

0

25

50

75

100

125

Mounting Base temperature, Tmb (C)

150

175

1E-05

T

1E-04

1E-03

1E-02

1E-01

1E+00

Pulse width, tp (s)

Fig.1. Normalised power dissipation.

PD% = 100PD/PD 25 C = f(Tmb)

Fig.4. Transient thermal impedance.

Zth j-mb = f(t); parameter D = tp/T

Drain Current, ID (A)

10

Normalised Current Derating, ID (%)

100

Tj = 25 C

VGS = 10V

90

6V

8V

5.5 V

80

7

70

60

50

40

30

20

5V

10

4.5 V

0

0

25

50

75

100

125

Mounting Base temperature, Tmb (C)

150

175

Fig.2. Normalised continuous drain current.

ID% = 100ID/ID 25 C = f(Tmb); VGS 10 V

0.4

0.6

0.8

1

1.2

1.4

Drain-Source Voltage, VDS (V)

1.6

1.8

Fig.5. Typical output characteristics, Tj = 25 C.

ID = f(VDS)

Peak Pulsed Drain Current, IDM (A)

100

0.2

0.5

Drain-Source On Resistance, RDS(on) (Ohms)

4.5 V

0.45

RDS(on) = VDS/ ID

5V

Tj = 25 C

0.4

tp = 10 us

10

0.35

5.5 V

0.3

100 us

0.25

D.C.

1 ms

0.2

10 ms

0.15

100 ms

0.1

6V

VGS = 10V

8V

0.05

0.1

0

1

10

100

Drain-Source Voltage, VDS (V)

1000

Fig.3. Safe operating area

ID & IDM = f(VDS); IDM single pulse; parameter tp

August 1999

3

4

5

6

Drain Current, ID (A)

10

Fig.6. Typical on-state resistance, Tj = 25 C.

RDS(ON) = f(ID)

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF630, IRF630S

Drain current, ID (A)

4.5

10

VDS > ID X RDS(ON)

Threshold Voltage, VGS(TO) (V)

3.5

2.5

maximum

typical

minimum

175 C

1.5

1

Tj = 25 C

0.5

1

0

0

0

0.5

1.5

2.5

3.5

4.5

5.5

-60

-40

-20

Gate-source voltage, VGS (V)

20

40

60

80

100 120 140 160 180

Junction Temperature, Tj (C)

Fig.7. Typical transfer characteristics.

ID = f(VGS)

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Fig.10. Gate threshold voltage.

VGS(TO) = f(Tj); conditions: ID = 1 mA; VDS = VGS

Transconductance, gfs (S)

1.0E-01

VDS > ID X RDS(ON)

Tj = 25 C

Drain current, ID (A)

1.0E-02

175 C

minimum

1.0E-03

typical

1.0E-04

maximum

1.0E-05

1.0E-06

0

4

5

6

Drain current, ID (A)

10

Fig.8. Typical transconductance, Tj = 25 C.

gfs = f(ID)

0.5

1

1.5

2

2.5

3

3.5

Gate-source voltage, VGS (V)

4.5

Fig.11. Sub-threshold drain current.

ID = f(VGS); conditions: Tj = 25 C

Normalised On-state Resistance

2.9

2.7

2.5

2.3

2.1

1.9

1.7

1.5

1.3

1.1

0.9

0.7

0.5

Capacitances, Ciss, Coss, Crss (pF)

10000

Ciss

1000

Coss

100

Crss

10

-60

-40

-20

0

20 40 60 80 100 120 140 160 180

Junction temperature, Tj (C)

0.1

Fig.9. Normalised drain-source on-state resistance.

RDS(ON)/RDS(ON)25 C = f(Tj)

August 1999

1

10

Drain-Source Voltage, VDS (V)

100

Fig.12. Typical capacitances, Ciss, Coss, Crss.

C = f(VDS); conditions: VGS = 0 V; f = 1 MHz

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF630, IRF630S

Maximum Avalanche Current, IAS (A)

Source-Drain Diode Current, IF (A)

10

10

VGS = 0 V

9

8

25 C

7

6

175 C

Tj = 25 C

Tj prior to avalanche = 150 C

4

3

2

1

0

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1.1

0.1

0.001

1.2

Source-Drain Voltage, VSDS (V)

0.1

10

Avalanche time, tAV (ms)

Fig.13. Typical reverse diode current.

IF = f(VSDS); conditions: VGS = 0 V; parameter Tj

August 1999

0.01

Fig.14. Maximum permissible non-repetitive

avalanche current (IAS) versus avalanche time (tAV);

unclamped inductive load

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF630, IRF630S

MECHANICAL DATA

Plastic single-ended package; heatsink mounted; 1 mounting hole; 3-lead TO-220

SOT78

A

A1

q

D1

L1

L2(1)

Q

b1

3

c

10 mm

scale

DIMENSIONS (mm are the original dimensions)

(1)

UNIT

A1

b1

D1

mm

4.5

4.1

1.39

1.27

0.9

0.7

1.3

1.0

0.7

0.4

15.8

15.2

6.4

5.9

10.3

9.7

L1

2.54

15.0

13.5

3.30

2.79

L2

max.

3.0

3.8

3.6

3.0

2.7

2.6

2.2

Note

1. Terminals in this zone are not tinned.

OUTLINE

VERSION

SOT78

REFERENCES

IEC

JEDEC

EIAJ

EUROPEAN

PROJECTION

ISSUE DATE

97-06-11

TO-220

Fig.15. SOT78 (TO220AB); pin 2 connected to mounting base (Net mass:2g)

Notes

1. This product is supplied in anti-static packaging. The gate-source input must be protected against static

discharge during transport or handling.

2. Refer to mounting instructions for SOT78 (TO220AB) package.

3. Epoxy meets UL94 V0 at 1/8".

August 1999

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF630, IRF630S

MECHANICAL DATA

Plastic single-ended surface mounted package (Philips version of D2-PAK); 3 leads

(one lead cropped)

SOT404

A

A1

mounting

base

D1

HD

2

Lp

3

c

b

e

2.5

5 mm

scale

DIMENSIONS (mm are the original dimensions)

UNIT

A1

mm

4.50

4.10

1.40

1.27

0.85

0.60

0.64

0.46

OUTLINE

VERSION

D

max.

D1

11

1.60

1.20

10.30

9.70

Lp

HD

2.54

2.90

2.10

15.40

14.80

2.60

2.20

REFERENCES

IEC

JEDEC

EIAJ

EUROPEAN

PROJECTION

ISSUE DATE

98-12-14

99-06-25

SOT404

Fig.16. SOT404 surface mounting package. Centre pin connected to mounting base.

Notes

1. This product is supplied in anti-static packaging. The gate-source input must be protected against static

discharge during transport or handling.

2. Refer to SMD Footprint Design and Soldering Guidelines, Data Handbook SC18.

3. Epoxy meets UL94 V0 at 1/8".

August 1999

Rev 1.100

Philips Semiconductors

Product specification

N-channel TrenchMOS transistor

IRF630, IRF630S

MOUNTING INSTRUCTIONS

Dimensions in mm

11.5

9.0

17.5

2.0

3.8

5.08

Fig.17. SOT404 : soldering pattern for surface mounting.

DEFINITIONS

Data sheet status

Objective specification

This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification

This data sheet contains final product specifications.

Limiting values

Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and

operation of the device at these or at any other conditions above those given in the Characteristics sections of

this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

Philips Electronics N.V. 1999

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the

copyright owner.

The information presented in this document does not form part of any quotation or contract, it is believed to be

accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any

consequence of its use. Publication thereof does not convey nor imply any license under patent or other

industrial or intellectual property rights.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these

products can be reasonably expected to result in personal injury. Philips customers using or selling these products

for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting

from such improper use or sale.

August 1999

Rev 1.100

Das könnte Ihnen auch gefallen

- N-Channel Trenchmos Transistor Irf540, Irf540S: Features Symbol Quick Reference DataDokument10 SeitenN-Channel Trenchmos Transistor Irf540, Irf540S: Features Symbol Quick Reference DatathedrodNoch keine Bewertungen

- Dual N-Channel Enhancement Mode Phn210T Trenchmos TransistorDokument8 SeitenDual N-Channel Enhancement Mode Phn210T Trenchmos TransistorCristian ViolaNoch keine Bewertungen

- N-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Dokument11 SeitenN-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Kevin TateNoch keine Bewertungen

- Fdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MDokument11 SeitenFdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MKevin TateNoch keine Bewertungen

- Irfp 260 NDokument9 SeitenIrfp 260 NJolaine MojicaNoch keine Bewertungen

- N 308 ApDokument11 SeitenN 308 Apdragon-red0816Noch keine Bewertungen

- IRF650B / IRFS650B: 200V N-Channel MOSFETDokument10 SeitenIRF650B / IRFS650B: 200V N-Channel MOSFETbinoelNoch keine Bewertungen

- IRF8788Dokument9 SeitenIRF8788Robert KovacsNoch keine Bewertungen

- International Rectifier IRFP2907Dokument9 SeitenInternational Rectifier IRFP2907scribd20110526Noch keine Bewertungen

- FDP 8896Dokument11 SeitenFDP 8896condejhonnyNoch keine Bewertungen

- Irfb4020Pbf: Digital Audio MosfetDokument8 SeitenIrfb4020Pbf: Digital Audio Mosfetto_netiksNoch keine Bewertungen

- IRF540NDokument7 SeitenIRF540Nmichaelliu123456Noch keine Bewertungen

- Irfp 90 N 20 DDokument9 SeitenIrfp 90 N 20 DAndré Frota PaivaNoch keine Bewertungen

- Irfp2907Pbf: Typical ApplicationsDokument9 SeitenIrfp2907Pbf: Typical Applicationsrajeev_kumar_1231852Noch keine Bewertungen

- FQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETDokument9 SeitenFQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETsoweloNoch keine Bewertungen

- IRFP360LCDokument8 SeitenIRFP360LCΗρακλης ΖερκελιδηςNoch keine Bewertungen

- IRF740B/IRFS740B: 400V N-Channel MOSFETDokument11 SeitenIRF740B/IRFS740B: 400V N-Channel MOSFETMistery of the souldNoch keine Bewertungen

- IRF650B / IRFS650B: 200V N-Channel MOSFETDokument11 SeitenIRF650B / IRFS650B: 200V N-Channel MOSFETMiloud ChouguiNoch keine Bewertungen

- P-Channel Enhancement Mode BSH205 MOS Transistor: Features Symbol Quick Reference DataDokument7 SeitenP-Channel Enhancement Mode BSH205 MOS Transistor: Features Symbol Quick Reference DataKumar Amit VermaNoch keine Bewertungen

- IRFB4227Dokument8 SeitenIRFB4227Fco. Jefferson Ferreira de SáNoch keine Bewertungen

- IRFZ34N Datasheet - KDokument8 SeitenIRFZ34N Datasheet - KNairo FilhoNoch keine Bewertungen

- FET 75N75 TransistorDokument8 SeitenFET 75N75 Transistorshahid iqbalNoch keine Bewertungen

- Irf740b PDFDokument10 SeitenIrf740b PDFMed SamiNoch keine Bewertungen

- Irfps 3810 PBFDokument8 SeitenIrfps 3810 PBFCrisan Radu-HoreaNoch keine Bewertungen

- Irf 1407Dokument10 SeitenIrf 1407Adilson BogadoNoch keine Bewertungen

- Fdb045An08A0: N-Channel Powertrench MosfetDokument12 SeitenFdb045An08A0: N-Channel Powertrench MosfetRocio HernandezNoch keine Bewertungen

- Irf1405 DatasheetDokument9 SeitenIrf1405 DatasheetE Alejandro G. BenavidesNoch keine Bewertungen

- Irlz 24 NDokument9 SeitenIrlz 24 NRobson PontinNoch keine Bewertungen

- Power Transistor: SPP17N80C3 SPA17N80C3 Cool MOS™Dokument13 SeitenPower Transistor: SPP17N80C3 SPA17N80C3 Cool MOS™cmlcaldeira10Noch keine Bewertungen

- Irfz46n PDFDokument9 SeitenIrfz46n PDFYunier FernandezNoch keine Bewertungen

- Irf1324s 7ppbfDokument10 SeitenIrf1324s 7ppbfAnonymous Gblw2LNoch keine Bewertungen

- Irf 3205 ZPBFDokument13 SeitenIrf 3205 ZPBFOsman KoçakNoch keine Bewertungen

- P11N60Dokument14 SeitenP11N60AndrewerNoch keine Bewertungen

- Buz 100Dokument10 SeitenBuz 100Alejandra SeguraNoch keine Bewertungen

- PHB 55n03lta Logic Level FetDokument15 SeitenPHB 55n03lta Logic Level FetyusufwpNoch keine Bewertungen

- Data Sheet IRFB42N20DDokument8 SeitenData Sheet IRFB42N20DvalubaNoch keine Bewertungen

- Description: N-Channel Enhancement Mode Field-Effect TransistorDokument14 SeitenDescription: N-Channel Enhancement Mode Field-Effect TransistorFernando Gonzales SanchezNoch keine Bewertungen

- Fdms0308Cs: N-Channel Powertrench SyncfetDokument8 SeitenFdms0308Cs: N-Channel Powertrench Syncfetdreyes3773Noch keine Bewertungen

- Irl 1004Dokument9 SeitenIrl 1004Luiz RvNoch keine Bewertungen

- IRFZ48NDokument8 SeitenIRFZ48NLuay IssaNoch keine Bewertungen

- Irfb4310 MosfetDokument12 SeitenIrfb4310 MosfetprasadNoch keine Bewertungen

- Irfb4410Zgpbf: V 100V R Typ. 7.2M Max. 9.0M I 97ADokument8 SeitenIrfb4410Zgpbf: V 100V R Typ. 7.2M Max. 9.0M I 97AWalter Hurtado ToroNoch keine Bewertungen

- Irfp 150 NDokument8 SeitenIrfp 150 NPerversso SkellingtonNoch keine Bewertungen

- Mosfet 10NM60NDokument19 SeitenMosfet 10NM60NRicardo Misael Torres0% (1)

- FD3055Dokument8 SeitenFD3055maldomattNoch keine Bewertungen

- N-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataDokument9 SeitenN-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataroozbehxoxNoch keine Bewertungen

- Irfp 2907Dokument9 SeitenIrfp 2907Anonymous u8GkNaNoch keine Bewertungen

- Irf 730 ADokument9 SeitenIrf 730 Ajose_mamani_51Noch keine Bewertungen

- Irf1503Pbf: Typical ApplicationsDokument9 SeitenIrf1503Pbf: Typical ApplicationsBochonMixNoch keine Bewertungen

- Irf7811Avpbf Irf7811Avpbf: Absolute Maximum RatingsDokument6 SeitenIrf7811Avpbf Irf7811Avpbf: Absolute Maximum RatingsnewmailsNoch keine Bewertungen

- FQB8N60C / FQI8N60C: 600V N-Channel MOSFETDokument9 SeitenFQB8N60C / FQI8N60C: 600V N-Channel MOSFETemelchor57Noch keine Bewertungen

- Irfi 3205 Power MosfetDokument9 SeitenIrfi 3205 Power MosfetAndy WilsonNoch keine Bewertungen

- SMD 357Dokument6 SeitenSMD 357Marcoantonio AntonioNoch keine Bewertungen

- BUK951R6-30E: 1. Product ProfileDokument13 SeitenBUK951R6-30E: 1. Product ProfileTom BeanNoch keine Bewertungen

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsVon EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNoch keine Bewertungen

- 110 Waveform Generator Projects for the Home ConstructorVon Everand110 Waveform Generator Projects for the Home ConstructorBewertung: 4 von 5 Sternen4/5 (1)

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsVon EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsBewertung: 3.5 von 5 Sternen3.5/5 (6)

- No Woman No Cry Ukulele Tab - Bob MarleyDokument1 SeiteNo Woman No Cry Ukulele Tab - Bob Marleylord mace tyrellNoch keine Bewertungen

- LM2907Dokument21 SeitenLM2907leorio88Noch keine Bewertungen

- ThousandYearsKrisFuchigami PDFDokument2 SeitenThousandYearsKrisFuchigami PDFlord mace tyrellNoch keine Bewertungen

- Transcribed Kalei Viva PDFDokument10 SeitenTranscribed Kalei Viva PDFlord mace tyrellNoch keine Bewertungen

- Fender Players Club: Chord FormulasDokument2 SeitenFender Players Club: Chord Formulaslord mace tyrellNoch keine Bewertungen

- Escala La MayorDokument1 SeiteEscala La MayorCecil MiccelliNoch keine Bewertungen

- Pink PantherDokument2 SeitenPink Pantherbobo249Noch keine Bewertungen

- Datasheet Irfz22Dokument6 SeitenDatasheet Irfz22lord mace tyrellNoch keine Bewertungen

- Flyer BMP180 08 2013 WebDokument2 SeitenFlyer BMP180 08 2013 Weblord mace tyrellNoch keine Bewertungen

- Switching Power SupplyDokument138 SeitenSwitching Power SupplyStephen Dunifer95% (22)

- Motorola An 780ADokument6 SeitenMotorola An 780ArobinsonsNoch keine Bewertungen

- Low Voltage Temperature Sensors / /: TMP35 TMP36 TMP37Dokument19 SeitenLow Voltage Temperature Sensors / /: TMP35 TMP36 TMP37lord mace tyrellNoch keine Bewertungen

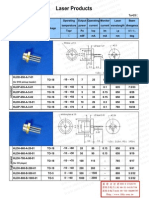

- Laser DiodeDokument1 SeiteLaser Diodelord mace tyrellNoch keine Bewertungen

- Motorola An 780ADokument6 SeitenMotorola An 780ArobinsonsNoch keine Bewertungen

- lm741 PDFDokument7 Seitenlm741 PDFDarilho Batista IgnacioNoch keine Bewertungen

- lm741 PDFDokument7 Seitenlm741 PDFDarilho Batista IgnacioNoch keine Bewertungen

- LM124X 4Dokument13 SeitenLM124X 4tsuyoshi7171Noch keine Bewertungen

- Ne556 Sa556 Se556Dokument10 SeitenNe556 Sa556 Se556lord mace tyrellNoch keine Bewertungen

- Amplificador Tlo82Dokument11 SeitenAmplificador Tlo82Miguel CombarizaNoch keine Bewertungen

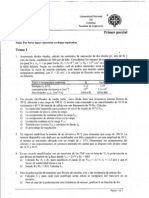

- Electronica 1Dokument1 SeiteElectronica 1lord mace tyrellNoch keine Bewertungen

- Electronica 1 Parcial UNCoDokument1 SeiteElectronica 1 Parcial UNColord mace tyrellNoch keine Bewertungen

- Electronica 1 Parcial UNCoDokument1 SeiteElectronica 1 Parcial UNColord mace tyrellNoch keine Bewertungen

- Electronica 1 Parcial UNCoDokument1 SeiteElectronica 1 Parcial UNColord mace tyrellNoch keine Bewertungen

- Electronica 1 Parcial UNCoDokument1 SeiteElectronica 1 Parcial UNColord mace tyrellNoch keine Bewertungen

- Semiconductor Technical Data: Mechanical CharacteristicsDokument3 SeitenSemiconductor Technical Data: Mechanical CharacteristicsAjay TomarNoch keine Bewertungen

- Electronica 1 Parcial UNCoDokument1 SeiteElectronica 1 Parcial UNColord mace tyrellNoch keine Bewertungen

- English Is The Window To The World. MimieDokument2 SeitenEnglish Is The Window To The World. MimieFARAH NADIANoch keine Bewertungen

- Practicality and Efficiency: Presented By: Grace EscabasDokument11 SeitenPracticality and Efficiency: Presented By: Grace EscabasMiaeNoch keine Bewertungen

- 67 - Es - Ut Republic Csalamade BooDokument47 Seiten67 - Es - Ut Republic Csalamade BooTyler LeeNoch keine Bewertungen

- Stulz C7000R 01 PDFDokument198 SeitenStulz C7000R 01 PDFNarciso Torres0% (1)

- Connecting Your Database and Auto Generate ID Using VB - Net 2008 and MySQL DatabaseDokument1 SeiteConnecting Your Database and Auto Generate ID Using VB - Net 2008 and MySQL DatabaseAgusWibowoNoch keine Bewertungen

- FZ1 Parts CatalogDokument78 SeitenFZ1 Parts CatalogAntonis Fotis100% (1)

- Cell Cycle Karyotyping Lab ReportDokument11 SeitenCell Cycle Karyotyping Lab ReportRichie JustinNoch keine Bewertungen

- SOS Children's Village: by Bekim RamkuDokument21 SeitenSOS Children's Village: by Bekim RamkuAbdulKerim AyubNoch keine Bewertungen

- Lab 5 (... )Dokument10 SeitenLab 5 (... )Zeeshan JuttNoch keine Bewertungen

- ROV Inspection and Intervention VesselDokument2 SeitenROV Inspection and Intervention VesselAhmad Reza AtefNoch keine Bewertungen

- Boolean Operations in 3D - AutoCAD 2016 Tutorial and VideosDokument19 SeitenBoolean Operations in 3D - AutoCAD 2016 Tutorial and VideosRohit Chandrakant SalveNoch keine Bewertungen

- Key Shortcuts WinDokument26 SeitenKey Shortcuts WinrockskartikNoch keine Bewertungen

- Pertemuan 1 - Verb, Noun, Adjective and AdverbDokument6 SeitenPertemuan 1 - Verb, Noun, Adjective and AdverbHaris PambudiNoch keine Bewertungen

- Department of Education: Activity Completion ReportDokument1 SeiteDepartment of Education: Activity Completion ReportJanineJavier100% (1)

- Pepperdine Resume Ico William Kong Updated BDokument1 SeitePepperdine Resume Ico William Kong Updated Bapi-278946246Noch keine Bewertungen

- Aitkensmethod 170829115234Dokument17 SeitenAitkensmethod 170829115234Yumi koshaNoch keine Bewertungen

- Elephant Catalog V13 PDFDokument96 SeitenElephant Catalog V13 PDFsamuelNoch keine Bewertungen

- Swot Analysis of Revlon IncDokument5 SeitenSwot Analysis of Revlon IncSubhana AsimNoch keine Bewertungen

- ABB - Composite Station Post InsulatorsDokument6 SeitenABB - Composite Station Post InsulatorsDominic SantiagoNoch keine Bewertungen

- DLL - English 5 - Q3 - W8Dokument8 SeitenDLL - English 5 - Q3 - W8Merlyn S. Al-osNoch keine Bewertungen

- Soft Sculpture EventsDokument28 SeitenSoft Sculpture EventsAlabala BalaaNoch keine Bewertungen

- Engineering Data: 2. CV CalculationDokument1 SeiteEngineering Data: 2. CV Calculationdj22500Noch keine Bewertungen

- 4 MFL67658602 00 160519 1Dokument329 Seiten4 MFL67658602 00 160519 1Cédric MorisotNoch keine Bewertungen

- MC68 HC05 B4 UDokument253 SeitenMC68 HC05 B4 Uflo724Noch keine Bewertungen

- BCO120Dokument3 SeitenBCO120erwin_simsensohnNoch keine Bewertungen

- Acceptance To An Offer Is What A Lighted Matchstick Is To A Train of GunpowderDokument2 SeitenAcceptance To An Offer Is What A Lighted Matchstick Is To A Train of GunpowderAnushka SharmaNoch keine Bewertungen

- Nola PenderDokument9 SeitenNola PenderAndrea YangNoch keine Bewertungen

- Srinivasa Ramanujan Institute of TechnologyDokument2 SeitenSrinivasa Ramanujan Institute of TechnologyPandu RangareddyNoch keine Bewertungen

- Tssiig GC e Module 1 PDFDokument6 SeitenTssiig GC e Module 1 PDFLoiweza AbagaNoch keine Bewertungen

- Measuring PovertyDokument47 SeitenMeasuring PovertyPranabes DuttaNoch keine Bewertungen