Beruflich Dokumente

Kultur Dokumente

Analysis of Pulsewidth Modulation Control and Digital Control Approach For Asymmetric Dc-Ac Cascaded Hbridge Multilevel Inverter

Hochgeladen von

sugavanamkrOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Analysis of Pulsewidth Modulation Control and Digital Control Approach For Asymmetric Dc-Ac Cascaded Hbridge Multilevel Inverter

Hochgeladen von

sugavanamkrCopyright:

Verfügbare Formate

VOL. 10, NO.

16, SEPTEMBER 2015

ISSN 1819-6608

ARPN Journal of Engineering and Applied Sciences

2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

ANALYSIS OF PULSEWIDTH MODULATION CONTROL AND DIGITAL

CONTROL APPROACH FOR ASYMMETRIC DC-AC CASCADED HBRIDGE MULTILEVEL INVERTER

K. Mohana Sundaram1, K. R. Sugavanam 2and R. Senthil Kumar2

1Department

2Department

of Electrical and Electronics Engineering, Vel Tech MultiTech, Chennai, India

of Electrical and Electronics Engineering, Vel Tech HighTech, Chennai, India

E-Mail:kumohanasundaram@gmail.com

ABSTRACT

This paper analyze an effective comparison between Pulse width modulation (PWM) control approach and digital

control approach for asymmetric DC-AC cascaded H-bridge multilevel inverter.The conventional available approach

produces 2n+1 output level for n independent DC sources and the digital control approach produces 2n+1-1 output level for

the same n independent DC sources with the same number switches. The proposed method also brings out the salient

features of using Digital control over the conventional PWM control by producing a low total harmonic distortion level

(THD) level while considering R-load. The simulation is done with the help of MATLAB and subsequently verified

experimentally.

Keywords: cascaded H-bridge inverter, multilevel inverter, THD, PWM control strategy, digital control strategy.

1. INTRODUCTION

Recently, India has been put into the list of power

starved country with states famished for power, also

produces power cuts for about 8-10 hrs. A day, protest

against the commissioning of nuclear power etc. but the

need for power just grows daily which is in the range of

megawatt. Considering these scenario multilevel inverters

stands firmly and promises a better solution in the future.

Multilevel inverters can be implemented in three different

types of strategies they are diode clamped multilevel

inverter, flying capacitor and cascaded H-bridge inverter.

Cascaded multilevel inverter uses DC sources which are

suitable for renewable energy sources such as fuel cell,

hydrogen cell, photovoltaic cell and biomass. Cascaded

inverters are advantages of having least number of

components to achieve the required level. The softswitching techniques can be used to reduce switching

losses and the stresses in devices.

This paper analyzes and provides comparative

results between the conventional PWM control and digital

control approach. The conventional method available

produces 2n+1 output level for n DC input but the digital

technique produces 2n+1-1 output level for n DC input

sources.

0,-Vdc.the voltage levels are produced with the different

switching combination of switches in the H-bridge.

Cascaded multilevel inverters can be used both in single

and three phases by just adding the number of H-bridge

used. The input DC source may be any DC sources such as

photovoltaic cell and the final total output is the

summation of individual H-bridge used .the control

techniques for the H-bridge inverters are PWM technique,

SVM technique etc.

2. MATERIALS AND METHODS

2.2. Cascaded PWM multilevel inverter

Cascaded H bridge multilevel inverter [2]

comprises of a series of H bridge inverter. Cascaded

inverter uses separate dc sources which can be obtained

from fuel cell, hydrogen cell, photovoltaic cell etc. the

cells are connected in series manner so that they add up the

voltage. The main advantage of Cascaded inverter that it

does not requires any voltage-clamping diodes or voltagebalancing capacitors. Considering, if there are any n level

2.1 cascaded multilevel inverter

Cascaded multilevel inverter consists of n

independent DC sources with n H-Bridge circuits. Hbridge consists of four switches, {MOSFET [1], IGBT,

Thyristor and etc] in which two switches works in positive

cycle and two switches operates during the negative cycle.

Each H-bridge produces three voltage level they are +Vdc,

Figure-1.Cascaded multilevel inverter.

6863

VOL. 10, NO. 16, SEPTEMBER 2015

ISSN 1819-6608

ARPN Journal of Engineering and Applied Sciences

2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

inverters

and

the

output

voltage

Van=

Va1+Va2+Va3+.Van. The output of the inverter are

three stages they are +Vdc, 0, and-Vdc. In this proposed

system two H-bridge inverters were used , with each

inverters has four switches, put together the circuit has

eight switches they are S1,S2,S3,S4,S5,S6,S7,S8.and the

two dc voltage source used are Vdc1,Vdc2. The circuit

diagram is shown in Figure-2and Figure-3.

The Figure-2shows the PWM multilevel inverter

with R Load. Figure-3 shows the PWM control H-bridge

inverter with motor as load. The conventional switching

approach produces 2n+1 output for n dc sources. The

proposed circuit uses 2 H-bridge inverters so for

conventional PWM method the output is 2(2)+1=5output

levels and the Conduction table for cascaded PWM

multilevel inverter is shown in Table-1.

Figure-2.PWM multilevel inverter with R load.

Table-1.Conduction table for cascaded PWM multilevel inverter.

Switch/

volts

30V

S1

S2

S3

S4

S5

S6

S7

S8

20V

10V

0V

-10V

-20V

-30V

Figure-3.PWM multilevel inverter with motor load.

The Figure-4 shows the switching state for the

conventional multilevel inverter.

Figure-4.Switching states of .PWM multilevel inverter.

6864

VOL. 10, NO. 16, SEPTEMBER 2015

ISSN 1819-6608

ARPN Journal of Engineering and Applied Sciences

2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

2.3 Cascaded digital control multilevel inverter

The two sides of driver [3] control are active-low

and active-high control. In active-low control the FET is

closed when the control signal is low or 0, and the FET

remains open when the signal is high or 1.In active-high

control the control signal is reverse phenomenon. Similarly

when the control is used in H-Bridge along with two

switches working in active-low and active-High control

the opening and closing of the switch depends upon the

PWM signal along with the Enable signal, suppose the

enable signal is high the circuit remains open and it will

not conduct.

The digital control [4] uses 4 flip flops as shown

in Figure-5. they are JK flip flop1,JK flip flop2,JK flip

flop3,JK

flip

flop4

and

the

outputs

are

(Q1,Q1),(Q2,Q2),(Q3,Q3),(Q4,Q4). The flip- flops

generally are clock edge triggered instead of level

triggered, the flip flops are given a clock signal and the

input for the JK flip flop1 is given through the constant as

1.The technique is similar to counter and in this process to

obatin a seven level output the requirement is n+2 bit

counters. The output of JK flip flop1 and JK flip flop2 are

made to operate in the first half cycle of the positive cycle

and in opposite in the second half of the positive cycle.

During the first half of the cycle it acts as a up counter as

the steps starts on increasing are done by Q3 in the second

half of the cycle it acts as a down counter as the steps

starts on decreasing are done by Q3.Q4 and Q4 has been

used as the control bits and they are also used to separate

the positive and negative switches.

counter directly ,hence JK flip flops are used and the

output of flipflop is applied to the AND or OR gates

inorder to generate the necessary gating pattern. The

output of logic gates is Boolean so inorder to convert

Boolean to double data conversion block is used. The

rationale behind to use double as the conversion type is

IGBT devices accept firing signals only in the form of

double. The Figure-6 shows the firing circuit with three

different sections counter section, logic circuit and pulse

separation. The counter counts from 0000 to 1111. Q3 and

Q4 are used as control bits for the logic circuit and pulse

separation between positive and negative pulses the

various switching pattern in the circuit is given in Table-2.

Figure-6.Gate signal generator for digital control

multilevel inverter.

Figure-5.Digital control in multilevel inverter.

Figure-7.Firing sequence.

In the proposed approach two dc sources were

used namely Vdc and Vdc/2, but MATLAB doesnt support

6865

VOL. 10, NO. 16, SEPTEMBER 2015

ISSN 1819-6608

ARPN Journal of Engineering and Applied Sciences

2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

Table-2.Conduction table for cascaded digital control in multilevel inverter.

Switch/

volts

30V

S1

S2

S3

S4

S5

S6

S7

S8

20V

10V

-10V

-20V

-30V

The THD level of the PWD cascaded multilevel

inverter is obtained using the FFT analysis.The THD level

is found to be 30.18%, which is shown in Figure-10.

Figure-8.Digital control with motor load.

Figure-8 shows the digital control technique with

a motor load [5].

3. RESULTS AND DISCUSSIONS

The simulation results are obtained from

MATLAB/SIMULINK.

The simulation results of the output are shown in

Figure-11 which uses switches S1, S2, S3, S4, S5, S6, S7

and S8, the input of 1st H-bridge and 2nd bridge combine

together to produce five level output. The Figure-9.Shows

the conventional PWM cascaded multilevel inverter.

Figure-10.FFT analysis of PWM cascaded multilevel

inverter.

The gate pattern for the digital control technique

is shown below for switches S1, S2, S3, S4, S5, S6, S7 and

S8 from Figures 11(a) to 11(e).

Figure-9. Output of PWM cascaded multilevel inverter.

Figure-11(a).Gating pattern of switch S1,S5.

6866

VOL. 10, NO. 16, SEPTEMBER 2015

ISSN 1819-6608

ARPN Journal of Engineering and Applied Sciences

2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

Figure-11(b).Gating pattern of Switch S2.

Figure-11(f). Gating pattern of switch S8.

The output of digital control of cascaded

multilevel inverter is shown in Figure-12. The THD level

of Digital control cascaded multilevel inverter is obtained

by using the FFT analysis. The THD[8] level is found to

be 14.32% is shown in Figure-13.

Figure-11(c). Gating pattern of switch S3,S7.

Figure-12.Output of digital control of cascaded multilevel

inverter.

Figure-11(d). Gating pattern of switch S4.

Figure-11(e). Gating pattern of switch S6.

Figure-13.FFT analysis of digital control of multilevel

inverter.

6867

VOL. 10, NO. 16, SEPTEMBER 2015

ISSN 1819-6608

ARPN Journal of Engineering and Applied Sciences

2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

The Table-3 gives a comparison .between

conventional and proposed method.

Table-3. Conduction table for cascaded digital control in

multilevel inverter.

S.No.

1

2

3

4

Parameters

for n sources

Number of

levels

Number of

switches

THD(without

filter)

Complexity in

designing

circuit

Conventional

method

Proposed

method

2n+1

2(n+1)-1

4n

4n

20.48%

16.80%

Complex

simple

Figure-16.Hardware setup.

Figure-17.Experimental results.

Figure-14. Speed graph of PWM multilevel inverter.

The speed Characteristics of the PWM inverter is

shown in Figure-14 and that of the digital approach is

shown in Figure-15, the speed of the PWM inverter fed

motor runs faster than that of the digital control but the

input to digital is very smooth so that the life of the motor

is better compared to that of the PWM and speed variation

is smooth in digital in comparison with PWM inverter. The

experimental set up is shown in Figure-16 and the results

are shown in Figure-17 respectively.

4. CONCLUSIONS

Thus the digital switching approach is employed

and the advantage of using digital scheme is that it reduces

the uneven degradation of power switches, switching

losses when compared to the conventional PWM technique

and harmonics are reduced. From the THD analysis the

conventional inverter produces a THD of 30.18% whereas

the digital control technique produces a THD of 14.32%

also the output level has been noted that a seven level

output is obtained by increasing the number of stages and

its efficiency is also increased. The output results are

verified using both by simulation and experimental setup.

REFERENCES

Leon M. Tolbert, Fang Zhen Pengand Thomas G.

Habetler. 1999. Multilevel Converter for Large Electric

Drives. IEEE transactions on industry applications. 35(1).

Jos

Rodrguez,Jih-Sheng

Lai,ZhengPeng.

2002.

Multilevel Inverters: A Survey of Topologies, Controls,

and Applications.IEEE transactions on industrial

electronics. 49(4).

Figure-15. Speed characteristics of digital control

multilevel inverter.

Zhong Du, Leon M. Tolbert, BurakOzpineci, and John N.

Chiasson. 2009. Fundamental Frequency Switching

Strategies of a Seven-Level Hybrid Cascaded H-Bridge

Multilevel Inverter. IEEE transactions on power

electronics. 24(1).

C.Kiruthika,

T.Ambika,

Dr.R.Seyezhai.

2012.

Implementation of digital control strategy for asymmetric

6868

VOL. 10, NO. 16, SEPTEMBER 2015

ISSN 1819-6608

ARPN Journal of Engineering and Applied Sciences

2006-2015 Asian Research Publishing Network (ARPN). All rights reserved.

www.arpnjournals.com

cascaded multilevel inverter. 2012 International

Conference on Computing, Electronics and Electrical

Technologies [ICCEET].

Sujitha.N and Ramani.K. 2012. A new hybrid cascaded Hbridge multilevel inverter-performance analysis. IEEEInternational Conference on Advances in Engineering,

Science and Management (lCAESM -2012).

S.Albert Alexander, T.Manigandan, N.Senthilnathan.

2009. Digital Switching Scheme for Cascaded Multilevel

Inverters. Third International Conference on Power

Systems, Kharagpur, India.

Jose Rodriguez,Steffen Bernet and BinWu. 2007.

Multilevel voltage source converter topologies for

Industrial medium voltage Drives.IEEE Transactions on

Industrial Electronics. 54(6): 2930-2945.

Yu Liu, Hoon Hong and Alex Q. Huang. 2009. Real time

calculation of switching angles minimizing THD for

multilevel inverters with step modulation. IEEE

Transactions on Induatrial Electronics. 56(6): 285-293.

6869

Das könnte Ihnen auch gefallen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Ble Enhanced Decentralised Work Time Sheet and Real Time Monitoring Using Smart Id CardDokument5 SeitenBle Enhanced Decentralised Work Time Sheet and Real Time Monitoring Using Smart Id CardsugavanamkrNoch keine Bewertungen

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Elimination of Electric Shocks Through Dual Voltage Switching Supply SystemDokument6 SeitenElimination of Electric Shocks Through Dual Voltage Switching Supply SystemsugavanamkrNoch keine Bewertungen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- Online Internal Fault Identification in Transformers Based On Direction and Location of Magnetizing Signature PatternsDokument4 SeitenOnline Internal Fault Identification in Transformers Based On Direction and Location of Magnetizing Signature PatternsPrabha KaranNoch keine Bewertungen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- A PSO Algorithm Based PI Controller Design For Soft Starting of Induction MotorDokument8 SeitenA PSO Algorithm Based PI Controller Design For Soft Starting of Induction MotorsugavanamkrNoch keine Bewertungen

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Design of FLC For OVR Reduction of Negative Output KY ConverterDokument12 SeitenDesign of FLC For OVR Reduction of Negative Output KY ConvertersugavanamkrNoch keine Bewertungen

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- GSM Based Fully Automated Surveillance Ensuring Road Safety and Data Acquisition For Legal ProsecutionDokument14 SeitenGSM Based Fully Automated Surveillance Ensuring Road Safety and Data Acquisition For Legal ProsecutionsugavanamkrNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Cost Optimization in DC Solenoid Valve Used in Air Braking by Replacing Copper Winding Wire To AluminumDokument4 SeitenCost Optimization in DC Solenoid Valve Used in Air Braking by Replacing Copper Winding Wire To AluminumsugavanamkrNoch keine Bewertungen

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Novel Vigilant Real Time Monitoring and Security System For Atm CentreDokument7 SeitenNovel Vigilant Real Time Monitoring and Security System For Atm CentresugavanamkrNoch keine Bewertungen

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Forensic Photogrammetric Analysis For Photo and Photo Scanned Images Using Wavelet TransformationDokument6 SeitenForensic Photogrammetric Analysis For Photo and Photo Scanned Images Using Wavelet TransformationsugavanamkrNoch keine Bewertungen

- A Study of Electric Power QualityDokument4 SeitenA Study of Electric Power QualitysugavanamkrNoch keine Bewertungen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Online Internal Fault Identification in Transformers Based On Direction and Location of Magnetizing Signature PatternsDokument4 SeitenOnline Internal Fault Identification in Transformers Based On Direction and Location of Magnetizing Signature PatternsPrabha KaranNoch keine Bewertungen

- Lesson PlanDokument5 SeitenLesson PlansugavanamkrNoch keine Bewertungen

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- 5V/3.3V/3V/Adjustable, High-Efficiency, Low I, Step-Down DC-DC ConvertersDokument12 Seiten5V/3.3V/3V/Adjustable, High-Efficiency, Low I, Step-Down DC-DC ConvertersJorge Centeno RamosNoch keine Bewertungen

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Full BridgeDokument7 SeitenFull Bridgebryan eduardo villegas carrascoNoch keine Bewertungen

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- TIE 2016 ModulationDokument15 SeitenTIE 2016 ModulationHana AliNoch keine Bewertungen

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Implementation of SPWM Technique For 3 - VSI Using STM32F4 Discovery Board Interfaced With MATLABDokument5 SeitenImplementation of SPWM Technique For 3 - VSI Using STM32F4 Discovery Board Interfaced With MATLABkiratNoch keine Bewertungen

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Allen Bradley PowerFlex 4 User ManualDokument32 SeitenAllen Bradley PowerFlex 4 User Manualtariq001Noch keine Bewertungen

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- CH 6Dokument3 SeitenCH 6atmroo9Noch keine Bewertungen

- Servo Motor & D.C Motor Interfacing With Atmega32Dokument33 SeitenServo Motor & D.C Motor Interfacing With Atmega32Yash TripathiNoch keine Bewertungen

- Fuction Description X038IDokument12 SeitenFuction Description X038IRafa TejedaNoch keine Bewertungen

- Jss Academy of Technical Education: Department of Electrical & Electronics EngineeringDokument11 SeitenJss Academy of Technical Education: Department of Electrical & Electronics EngineeringBiplav SinghNoch keine Bewertungen

- Manual Controlador de Procesos Burkert 110Dokument96 SeitenManual Controlador de Procesos Burkert 110Fabián Herrera100% (1)

- Unit-2 Case Study Embedded System For Automatic Washing MachineDokument11 SeitenUnit-2 Case Study Embedded System For Automatic Washing Machinesujith84% (19)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- HW DSGN Guidelines Spraas1a PDFDokument31 SeitenHW DSGN Guidelines Spraas1a PDFsomethingfornowNoch keine Bewertungen

- What Does This Knob Do PDFDokument171 SeitenWhat Does This Knob Do PDFJairo DallosNoch keine Bewertungen

- Autonomous Maze Solving Robot: ThesisDokument55 SeitenAutonomous Maze Solving Robot: ThesisAlex GhiteaNoch keine Bewertungen

- NE/SA/SE555/SE555C Timer: Description Pin ConfigurationsDokument8 SeitenNE/SA/SE555/SE555C Timer: Description Pin ConfigurationsLalantha Munasinghe ArachchigeNoch keine Bewertungen

- PDC 1Dokument13 SeitenPDC 1gamingsquad5262Noch keine Bewertungen

- Mobile Wind Charger for Automobile BatteriesDokument7 SeitenMobile Wind Charger for Automobile Batteriessuraj dhulannavarNoch keine Bewertungen

- 5V/-12V/-15V or Adjustable, High-Efficiency, Low I Inverting DC-DC ControllersDokument16 Seiten5V/-12V/-15V or Adjustable, High-Efficiency, Low I Inverting DC-DC ControllersDext JafremNoch keine Bewertungen

- KS0085 Keyestudio Smart Home Kit For ArduinoDokument191 SeitenKS0085 Keyestudio Smart Home Kit For ArduinomparejacursoNoch keine Bewertungen

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Simulation of Flyback Converter With Peak Current Mode ControlDokument6 SeitenSimulation of Flyback Converter With Peak Current Mode ControlAbhijit SinghNoch keine Bewertungen

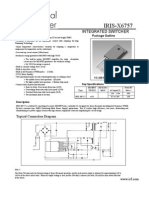

- IRIS-X6757: FeaturesDokument10 SeitenIRIS-X6757: Featuresmiguel angel jaramilloNoch keine Bewertungen

- Controlling Servomotors With MicrocontrollersDokument28 SeitenControlling Servomotors With MicrocontrollersAbdulla AshoorNoch keine Bewertungen

- Test SetupDokument11 SeitenTest SetupKarthik PariharNoch keine Bewertungen

- Samsung ML-2850 Series ML-2850D / ML-2851ND Service ManualDokument151 SeitenSamsung ML-2850 Series ML-2850D / ML-2851ND Service ManualVicent Selfa Oliver100% (10)

- D D D D D D D D D: DescriptionDokument34 SeitenD D D D D D D D D: DescriptionSukandar TeaNoch keine Bewertungen

- Pebb Concept Applications in High Power Electronics ConvertersDokument6 SeitenPebb Concept Applications in High Power Electronics ConvertersdineshpeterNoch keine Bewertungen

- PEEC Electronic System Functional TestsDokument66 SeitenPEEC Electronic System Functional TestsRichard Chua0% (1)

- SSP 412 Audi 2.0l 125 KW TDI Engine With Pump Injection SystemDokument40 SeitenSSP 412 Audi 2.0l 125 KW TDI Engine With Pump Injection Systemfrancois.garcia31100% (4)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Bt31r0521-p1 Power ElectronicsDokument34 SeitenBt31r0521-p1 Power ElectronicsgtchsekharNoch keine Bewertungen

- Programmable controller MCX152V with Ethernet, SD card and large I/ODokument7 SeitenProgrammable controller MCX152V with Ethernet, SD card and large I/Oxie samNoch keine Bewertungen