Beruflich Dokumente

Kultur Dokumente

Resume (VLSI)

Hochgeladen von

MANIKANDANCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Resume (VLSI)

Hochgeladen von

MANIKANDANCopyright:

Verfügbare Formate

VENKATESH SARAF

Amarashilpi #EWS-837, 1st main, 1st cross, Navanagar, Hubli - 580025

:

09611622465

vsaraf05@gmail.com

in.linkedin.com/in/venkateshsaraf

CAREER OBJECTIVE

Aspiring to join a Semiconductor Industry where I can apply my skills and knowledge to deliver value added results as

well as further enhance my learning and develop my career.

EDUCATION

Qualification

B.E.

(E & C)

12th Std

10th Std

University / Board

VTU, Belgaum

Dept. of PU

Education

KSEEB

Institution

Year of Passing

Aggregate

2014

60.56%

2010

72.33%

2008

91.36%

K. L. E. Institute of

Technology, Hubli

SMPU Science

College, Dharwad

SDM School,

Dharwad

PROJECTS UNDERTAKEN

I.

Arithmetic Logic Unit (ALU)

Arithmetic logic unit (ALU) is a Digital circuit that

performs arithmetic and bitwise logical operations

on integer binary numbers

This project involves the entire Chip Development

Cycle of Specification, Design, Simulation, Layout,

Verification and Documentation

I took the Lead in designing layout for

ADD_SUB_BIT1 which formed a major block.

Given Constraints:

2 inputs of 3bits each. 1 output of 5bits and a sign

bit. 3 control bits for 8 operations

1.8V supply voltage, Frequency of 10MHz,

Temperature variations of -40 C to 125 C

Implementation in GPDK 180nm technology

Performances Achieved:

A: No. of Transistors = 460 (W*L area = 74.52 sq.um)

B: Average supply current for all 8 operations (WC across

PVT) = 8.89uA

C: Delay b/n Input & Output (WC across PVT) = 1.4ns

D: Total Rectangular Layout Area = 2870.42 sq.um

FOM: (A*B*C*D) = 1.56 E-20 Coulomb.m2

III.

Band Gap Reference

A BGR is a temperature independent circuit that produces

constant reference voltage irrespective of power supply

variations and temperature changes.

Few Highlights that Ive implemented in BGR Layout:

Coaxial shielding technique for output Reference

voltages

Double guard rings for BJT and Placing of dummy

devices around BJTs

Interleaved pattern for Current Mirror, Resistors

and Common-Centroid for Differential pairs

Same routing pattern for Matched devices

BJT and Resistors kept close to each other

IV.

Power Management Module

A Power Management Module is voltage convertor/

regulator that convert input voltage to the output voltage

level that the circuit requires.

Few Highlights that Ive implemented in PM Layout:

Top-down floorplan approach

Reuse of Improvised BGR, Error amplifier and

Buffer blocks

Decaps to boost power supply and act as fillers

Design of Analog and Digital Power transistors

II.

5_Pack_Amplifier

with EM constraints as follows

Analog Layout Design of OPAMP

M1 M5 : 1um 0.5mA

Matching patterns for Current Mirror load and

M6 : 1um 3mA

(Power rails)

Differential pair

Hierarchical DRC and LVS verifications

Guard ring & Dummy FETs to protect transistors

Double contacts & Double guard rings for Power

Parasitic Extraction

MOSFETs

V.

Phase-Locked Loop

H-type clock routings to feed clock signals to

different blocks in order to achieve equal delay

As a lead, I took the responsibility to do top level

routings for Fractional Divider block

Design of 11 track PR Grid of height = 7.7um

Usage of Bindkeys to reduce time-to-market

A phase-locked loop is a feedback system combining a

voltage controlled oscillator (VCO) and a phase comparator

so connected that the oscillator maintains a constant

phase angle relative to a reference signal. Phase-locked

loops can be used, for example, to generate stable output

high frequency signals from a fixed low-frequency signal.

Few Highlights of Customer level PLL Layout design:

Top-down floorplan approach indicating the pin

positions, power rails and critical routings

Isolated Digital and Analog blocks

Performances Achieved:

Area = 1,67,824 sq.um ;

Aspect ratio = 1.25

Height = 459 um

;

Width = 365 um

I took the Lead for Fractional Divider block

which forms 60% of the whole Chip area

Fractional divider consisted of three sub blocks

namely Mash, Decoder and Integer Divider

High density and High performance layout

PROJECTS SUMMARY

Hands-on experience on various tools like

Cadence Virtuoso v6.1, Virtuoso Analog Design

Environment and Assura Physical Verification

Knowledge of Cadence SKILL and Perl

programming needed for Design Automation

In-depth knowledge of Fabrication steps, Analog,

Digital and Mixed signal Chips development

Architecture, Design, Layout and Verification

Knowledge on Reliability issues like Antenna

effects, Electromigration (EM), Electrostatic

discharge (ESD) and Latch-up

Good understanding of Circuit theory

CO - CURRICULAR ACTIVITIES

1. Elected as a President of Students Association (2014 batch) PHOENIX in ECE Dept, KLEIT Hubli.

2. Presented a paper on Built-In Self Test and Concurrent Testing for Digital Circuits at National Level Technical

fest in BVBCET [Pleiades13]

3. Presented a paper on Fuzzy logic and related applications in Accident Control at State Level Technical fest in

SDMCET [Techspin12]

ACHIEVEMENTS

1. Won Gold medals at Asian & International level Karate Tournaments in A.P. and Sri Lanka respectively.

2. Awarded as the Best Boy in High School for the Academic batch 2007-08.

3. Completed B and C certificates in NCC at the grade of Sergeant.

PERSONAL STRENGTHS

Quick learner

Self Motivated

Good analytical skill

Good presentation skill

Hard worker and Flexible

Problem solving skills

PERSONAL DETAILS

Date of Birth

Fathers Name

Passport number

Nationality

Languages known

Hobbies

:

:

:

:

:

:

26th March 1992

Laxman J Saraf

G7310095

Indian

English, Hindi, Kannada

Exploring things, Reading novels, Listening music, Physical fitness

DECLARATION

I hereby declare that the above mentioned particulars are true to the best of my knowledge and belief.

Place: Hubli

(Venkatesh Saraf)

Das könnte Ihnen auch gefallen

- Jump and Branch InstructionsDokument1 SeiteJump and Branch InstructionsMANIKANDANNoch keine Bewertungen

- Std10 Science EM 1Dokument71 SeitenStd10 Science EM 1MANIKANDANNoch keine Bewertungen

- MicroC2 eCh15L08ARMDevelopmentToolsDokument39 SeitenMicroC2 eCh15L08ARMDevelopmentToolsMANIKANDANNoch keine Bewertungen

- Lpc2148 DatasheetDokument38 SeitenLpc2148 DatasheetSandeep ThompsonNoch keine Bewertungen

- SubroutinesDokument1 SeiteSubroutinesMANIKANDANNoch keine Bewertungen

- Manchester EncodingDokument5 SeitenManchester EncodingMANIKANDANNoch keine Bewertungen

- Electronics GuideDokument22 SeitenElectronics GuideFernandes KennethNoch keine Bewertungen

- Analogue To Digital Converters (ADC)Dokument3 SeitenAnalogue To Digital Converters (ADC)MANIKANDANNoch keine Bewertungen

- Memory Timing AnalysisDokument3 SeitenMemory Timing AnalysisMANIKANDANNoch keine Bewertungen

- 6800 Address ModesDokument1 Seite6800 Address ModesMANIKANDANNoch keine Bewertungen

- Formal Report 1: Arrange 10 Numbers in Ascending OrderDokument2 SeitenFormal Report 1: Arrange 10 Numbers in Ascending OrderMANIKANDANNoch keine Bewertungen

- Delay LoopsDokument2 SeitenDelay LoopsMANIKANDANNoch keine Bewertungen

- DramDokument3 SeitenDramMANIKANDANNoch keine Bewertungen

- 6800 Internal RegistersDokument3 Seiten6800 Internal RegistersMANIKANDANNoch keine Bewertungen

- Formal Report 1: Arrange 10 Numbers in Ascending OrderDokument2 SeitenFormal Report 1: Arrange 10 Numbers in Ascending OrderMANIKANDANNoch keine Bewertungen

- VHDL FSM Tutorial MY FIRST FSMDokument29 SeitenVHDL FSM Tutorial MY FIRST FSMMANIKANDANNoch keine Bewertungen

- VHDL TutorialDokument68 SeitenVHDL TutorialPedro Pablo Parra AlbaNoch keine Bewertungen

- Memory Timing AnalysisDokument3 SeitenMemory Timing AnalysisMANIKANDANNoch keine Bewertungen

- Review QuestionsDokument4 SeitenReview QuestionsMANIKANDANNoch keine Bewertungen

- Program Control InstructionsDokument3 SeitenProgram Control InstructionsMANIKANDANNoch keine Bewertungen

- Numbering Systems TutorialDokument5 SeitenNumbering Systems TutorialMANIKANDANNoch keine Bewertungen

- Using EcalDokument4 SeitenUsing EcalMANIKANDANNoch keine Bewertungen

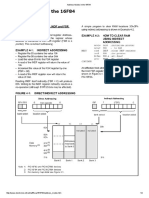

- Address Modes in The 16F84Dokument2 SeitenAddress Modes in The 16F84MANIKANDANNoch keine Bewertungen

- FT021/3 Computer Systems Summer 2004Dokument2 SeitenFT021/3 Computer Systems Summer 2004MANIKANDANNoch keine Bewertungen

- FT021/3 Computer Systems Summer 2004Dokument2 SeitenFT021/3 Computer Systems Summer 2004MANIKANDANNoch keine Bewertungen

- Introduction To Parallel PortsDokument5 SeitenIntroduction To Parallel PortsMANIKANDANNoch keine Bewertungen

- Pic16f8x PDFDokument126 SeitenPic16f8x PDFGilberto MataNoch keine Bewertungen

- 6800 Internal RegistersDokument3 Seiten6800 Internal RegistersMANIKANDANNoch keine Bewertungen

- Fetch and ExecuteDokument2 SeitenFetch and ExecuteMANIKANDANNoch keine Bewertungen

- Memory Timing AnalysisDokument3 SeitenMemory Timing AnalysisMANIKANDANNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (120)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Process Plant Layout - Becoming A Lost ArtDokument7 SeitenProcess Plant Layout - Becoming A Lost ArtRajendraNoch keine Bewertungen

- An Objective of Dress Code PolicyDokument4 SeitenAn Objective of Dress Code PolicySiddhraj Singh KushwahaNoch keine Bewertungen

- 1 Relative Maxima, Relative Minima and Saddle PointsDokument3 Seiten1 Relative Maxima, Relative Minima and Saddle PointsRoy VeseyNoch keine Bewertungen

- Cambridge Latin Course Book I Vocabulary Stage 1 Stage 2Dokument3 SeitenCambridge Latin Course Book I Vocabulary Stage 1 Stage 2Aden BanksNoch keine Bewertungen

- Molina Vs de La Riva 6 Phil 12 INOKDokument2 SeitenMolina Vs de La Riva 6 Phil 12 INOKErick Jay InokNoch keine Bewertungen

- Mag Issue137 PDFDokument141 SeitenMag Issue137 PDFShafiq Nezat100% (1)

- Working With Regular Expressions: Prof. Mary Grace G. VenturaDokument26 SeitenWorking With Regular Expressions: Prof. Mary Grace G. VenturaAngela BeatriceNoch keine Bewertungen

- The First Quality Books To ReadDokument2 SeitenThe First Quality Books To ReadMarvin I. NoronaNoch keine Bewertungen

- Hapter 2: Theoretical FrameworkDokument18 SeitenHapter 2: Theoretical FrameworkMohamed HamzaNoch keine Bewertungen

- Sample DCCM, DLHTM and DCLRDokument38 SeitenSample DCCM, DLHTM and DCLREagle100% (5)

- Correct Translation of 2-16Dokument19 SeitenCorrect Translation of 2-16muhammad_zubair708110Noch keine Bewertungen

- Hussain Kapadawala 1Dokument56 SeitenHussain Kapadawala 1hussainkapda7276Noch keine Bewertungen

- Cns Spectrums: The Clinical Challenges of Akathisia CME Review ArticleDokument16 SeitenCns Spectrums: The Clinical Challenges of Akathisia CME Review Articledzakiyah nurul israNoch keine Bewertungen

- Chryso CI 550Dokument2 SeitenChryso CI 550Flavio Jose MuhaleNoch keine Bewertungen

- History RizalDokument6 SeitenHistory RizalIrvin LevieNoch keine Bewertungen

- Creating The HardboiledDokument20 SeitenCreating The HardboiledBen NallNoch keine Bewertungen

- Future Dusk Portfolio by SlidesgoDokument40 SeitenFuture Dusk Portfolio by SlidesgoNATALIA ALSINA MARTINNoch keine Bewertungen

- The 5 Basic Sentence PatternsDokument6 SeitenThe 5 Basic Sentence PatternsShuoNoch keine Bewertungen

- DR LukeDokument126 SeitenDR Lukegabryelbarretto7Noch keine Bewertungen

- United States v. Government of The Virgin Islands, 363 F.3d 276, 3rd Cir. (2004)Dokument19 SeitenUnited States v. Government of The Virgin Islands, 363 F.3d 276, 3rd Cir. (2004)Scribd Government DocsNoch keine Bewertungen

- Types of Non Verbal CommunicationDokument7 SeitenTypes of Non Verbal Communicationgaurav gharat100% (1)

- Operations Research Letters: Meichun Lin, Woonghee Tim Huh, Guohua WanDokument8 SeitenOperations Research Letters: Meichun Lin, Woonghee Tim Huh, Guohua WanQuỳnh NguyễnNoch keine Bewertungen

- Communist Party of India - WikipediaDokument104 SeitenCommunist Party of India - WikipediaRameshwar ChandravanshiNoch keine Bewertungen

- Perception On The Impact of New Learning Tools in Humss StudentDokument6 SeitenPerception On The Impact of New Learning Tools in Humss StudentElyza Marielle BiasonNoch keine Bewertungen

- Management of Liver Trauma in Adults: Nasim Ahmed, Jerome J VernickDokument7 SeitenManagement of Liver Trauma in Adults: Nasim Ahmed, Jerome J VernickwiraNoch keine Bewertungen

- WhatsApp Chat With MiniSoDokument28 SeitenWhatsApp Chat With MiniSoShivam KumarNoch keine Bewertungen

- Quality of Life After Functional Endoscopic Sinus Surgery in Patients With Chronic RhinosinusitisDokument15 SeitenQuality of Life After Functional Endoscopic Sinus Surgery in Patients With Chronic RhinosinusitisNarendraNoch keine Bewertungen

- DBS AR 2019 Final Final PDFDokument371 SeitenDBS AR 2019 Final Final PDFDevi Nurusr100% (1)

- Donna Haraway - A Cyborg Manifesto - An OutlineDokument2 SeitenDonna Haraway - A Cyborg Manifesto - An OutlineKirill RostovtsevNoch keine Bewertungen

- List of Naruto Char.Dokument40 SeitenList of Naruto Char.Keziah MecarteNoch keine Bewertungen