Beruflich Dokumente

Kultur Dokumente

2710507

Hochgeladen von

Smit PatelOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

2710507

Hochgeladen von

Smit PatelCopyright:

Verfügbare Formate

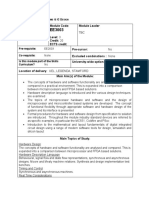

GUJARAT TECHNOLOGICAL UNIVERSITY

ELECTRONICS & COMMUNICATION (COMMUNICATION SYSTEMS ENGG)

(05)

ASIC DESIGN

SUBJECT CODE: 2710507

SEMESTER: I

Type of course: Major Elective - I

Prerequisite: Logic gates and flip-flops, Combinational and sequential Logic circuits

Rationale: This course is first step for PG students in the field of ASIC prototyping which is also called

FPGA (Field programmable gate array) / SoC (System on Chip) prototyping. With large resource of

configurable logic blocks FPGA is designed to be configured by designer using hardware description

language for digital system design. This Course offers a variety of topics of immediate relevance to

digital VLSI System Design

Teaching and Examination Scheme:

Teaching Scheme

T

P

Credits

C

Theory Marks

ESE PA (M)

(E)

70

30

Examination Marks

Practical Marks

PA (V)

PA (I)

ESE

OEP

PA

RP

20

10

20

0

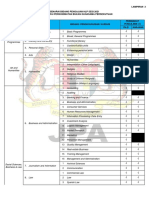

Content:

Sr.

Topics

No.

Introduction

ASIC Design flow, Design Methodologies, Hardware modeling issues,

1

Overview of FPGA and CPLD technology

Hardware Description Language

Elements of VHDL, Entity, architecture, configuration declaration.

2

Identifiers, data types and operators, Assignment statement, Objects in

VHDL signals, variables, constants, files, Attributes of objects.

Behavioral modeling

Process statement, Signal and variable assignment, Wait statement, if

statement, Case statement, Loops, exit, and next statement, Assertion

3

and report statement, Multiple process, Postponed process.

Subprograms procedures and functions, Subprogram overloading and

operator overloading. RTL description

Dataflow modeling

Concurrent signal assignment, sequential signal assignment, delta

delay, multiple drivers, conditional signal assignment using when

4

else, selected signal assignment using with select, block statement,

concurrent assertion signal

Structural modeling

Component declaration, generics and component instantiation, Example

5

of making hierarchical circuit. Generate statement, aliases, mixed

modeling style

6

Finite State Machine (FSM)

Total

Marks

150

Teaching

Hrs.

Module

Weightage

15

15

15

15

Stat diagrams and state tables, Moore and Mealy finite state machine,

encoding style, FSM issues, Timing issues, pipelining, resource

sharing, metastability, synchronization, MTBF Analysis, setup/hold

time of various types of flip-flops, synchronization between multiple

clock domains, reset recovery

Configuration and packages

Configuration specification and declaration, conversion functions,

direct instantiation, incremental binding. Package declaration, package

body, design file

Test Benches and library

File I/O operations, Test bench architecture, test bench examples,

library declaration and user defined library

Programmable Logic Design

Basics of Programmable logic devices - PROM, PAL, PLA, etc,

CPLD architecture and its building blocks, FPGA architectures and its

building blocks, Carry chains in FPGA, Dedicated multipliers and

memory in FPGA, RTL synthesis test methodology, Design synthesis,

Technology mapping for FPGAs: SRAM, Fuse, Antifuse, EPROM

programming techniques. Design implementation using CPLD and

FPGA, Floor planning, Placement and routing

20

Reference Books:

1. Douglas L. Perry, VHDL programming by examples, 4th Ed., Tata McGraw Hill.

2. J. Bhasker, VHDL Primer, Pearson Education Asia, Low Price Edition

3. Charles H Roth, Jr., Principles of Digital Systems Design using VHDL, Cengage Learning

4. Kevin Skahill, VHDL for programmable logic, Pearson Education Asia, Low Price Edition

5. Michael John Sebastian Smith, Application Specific Integrated Circuits, Pearson Education Asia.

6. Wakerly, J. F., Digital Design: Principles and Practices 4th Edition, Pearson

7. Xilinx and Altera Application Notes on the architecture of FPGAs and CPLDs

Course Outcome:

After learning the course the students should be able to design digital systems using hardware description

languages required for VLSI Design such as VHDL. The students shall learn how to program and test

programs on FPGAs or CPLD. The students shall get exposure to the Various Digital Design Issues, ASIC

Technology and Design techniques.

List of Experiments:

(with Open Ended Problems)

1. Write entity with 2 inputs a, b and 7 outputs x1 to x7 for logic gates NOT, AND, OR, NAND, NOR,

XOR, XNOR respectively.

2. Write code for 4x1 MUX with structural modeling and using same, implement 8x1 MUX. Extend

above programs for 16x1 MUX.

3. Write code for 2x4 Decoder with structural modeling and using same, implement 3x8 decoder.

Extend program for 4x16 decoder.

4. Write code for D-latch with structural modeling and implement 4-bit register using same. Extend

above program for 16-bit register.

5. Write VHDL code to realize a 4 bit, 4 X 1 multiplexer.

Write the architecture using equations

Write the architecture using dataflow model using (with ... select) construct

Write the architecture using dataflow model using (when ... else) construct

Write the behavioral code using (case ... when ...) construct

Write the behavioral code using (if ... then ...) construct.

6. Implement the following in VHDL code.

An 8-bit ripple adder (use equations)

An 8-bit carry look ahead adder (use equations)

Implement an 8 bit adder using the operator .+. in .ieee.std_logic_unsigned package.

8-bit ripple adder using structural modeling with generate statement.

8-bit ripple adder and subtractor using mode control input.

Synthesis code for any target FPGA device and compare the area (resource utilization) and performance

(delay) in each case.

7. Write VHDL code to implement various flip flops.

8. Write VHDL code to implement 16-bit universal shift register, which supports shift-left, shift right,

and parallel-in modes.

9. Write VHDL code for the clock divider to get 1 Hz clock from 1 MHz clock input.

10. Write VHDL code to implement up-down counter.

11. Write VHDL code to implement Parallel to serial converter and Serial to Parallel Converter.

12. Write VHDL code for sequence detector using FSM

Major Equipments: Kits with Xilinx / Altera FPGA

List of Open Source Software/learning website:

Xilinx ISE

Das könnte Ihnen auch gefallen

- COMSATS Institute of Information Technology Abbottabad: GoalsDokument2 SeitenCOMSATS Institute of Information Technology Abbottabad: GoalsSohail MashwaniNoch keine Bewertungen

- Session - 8 - PLA PALDokument14 SeitenSession - 8 - PLA PALmohammedsaniyaamrinNoch keine Bewertungen

- Embedded Systems Design with Platform FPGAs: Principles and PracticesVon EverandEmbedded Systems Design with Platform FPGAs: Principles and PracticesBewertung: 5 von 5 Sternen5/5 (1)

- Multicore FPGA Paper - FINALDokument9 SeitenMulticore FPGA Paper - FINALunicycle1234Noch keine Bewertungen

- ME VLSI & EmdDokument58 SeitenME VLSI & EmdAnil V. WalkeNoch keine Bewertungen

- PG Diploma in Embedded Systems Design (PG-DESD) Course FocusDokument3 SeitenPG Diploma in Embedded Systems Design (PG-DESD) Course Focusabhijeetv2Noch keine Bewertungen

- ADSD SyllabusDokument2 SeitenADSD SyllabuswroxtarNoch keine Bewertungen

- Please Succ Me ' (Dokument1 SeitePlease Succ Me ' (;(Noch keine Bewertungen

- PG Diploma in Embedded Systems Design (PG-DESD) Course FocusDokument7 SeitenPG Diploma in Embedded Systems Design (PG-DESD) Course Focusabhijeetv2Noch keine Bewertungen

- Computer Engineering Sem-1Dokument8 SeitenComputer Engineering Sem-1waniasimNoch keine Bewertungen

- Digital Design Through Verilog HDL Course Outcomes For LabDokument1 SeiteDigital Design Through Verilog HDL Course Outcomes For LabSyed AshmadNoch keine Bewertungen

- EC6612 - VLSI Design Laboratory ManualDokument39 SeitenEC6612 - VLSI Design Laboratory ManualSriramNoch keine Bewertungen

- Altera Enixs Course PDFDokument3 SeitenAltera Enixs Course PDFLe LamNoch keine Bewertungen

- Literature Review On FpgaDokument4 SeitenLiterature Review On Fpgaafdtfhtut100% (1)

- 8 Bit ALU by XilinxDokument16 Seiten8 Bit ALU by XilinxDIPTANU MAJUMDERNoch keine Bewertungen

- Joydeep Saha: ObjectiveDokument2 SeitenJoydeep Saha: ObjectiveJoydeep SahaNoch keine Bewertungen

- FALLSEM2022-23 BECE102L TH VL2022230104438 Reference Material I 21-07-2022 BECE102LDokument3 SeitenFALLSEM2022-23 BECE102L TH VL2022230104438 Reference Material I 21-07-2022 BECE102LUrjoshi AichNoch keine Bewertungen

- Ug Vlsi Design LabDokument2 SeitenUg Vlsi Design LabvlsijpNoch keine Bewertungen

- Jsaha Resume NewDokument2 SeitenJsaha Resume NewJoydeep SahaNoch keine Bewertungen

- Computer Logic LabsDokument75 SeitenComputer Logic LabsІко Оджо Віктор ОдаудуNoch keine Bewertungen

- Foundations of ARM64 Linux Debugging, Disassembling, and Reversing (Dmitry Vostokov) (Z-Library)Dokument170 SeitenFoundations of ARM64 Linux Debugging, Disassembling, and Reversing (Dmitry Vostokov) (Z-Library)372060579Noch keine Bewertungen

- VHDL Modeling and Synthesis in The Laboratory: Session 2647Dokument12 SeitenVHDL Modeling and Synthesis in The Laboratory: Session 2647Красимир КостадиновNoch keine Bewertungen

- Design and Simulation of Mathematical Models Using Mixed HDL PlatformDokument11 SeitenDesign and Simulation of Mathematical Models Using Mixed HDL PlatformInternational Journal of Application or Innovation in Engineering & ManagementNoch keine Bewertungen

- Foundations of Arm64 Linux Debugging Disassembling and Reversing Dmitry Vostokov Full ChapterDokument67 SeitenFoundations of Arm64 Linux Debugging Disassembling and Reversing Dmitry Vostokov Full Chapterkim.mason215100% (8)

- Syllabus FPGA B TechDokument1 SeiteSyllabus FPGA B TechHarmandeep SinghNoch keine Bewertungen

- Hassan Ullah Khan CV (FPGA)Dokument2 SeitenHassan Ullah Khan CV (FPGA)hassan ullah khanNoch keine Bewertungen

- Bece102l - Digital-Systems-Design - TH - 1.0 - 71 - Bece102l - 66 AcpDokument2 SeitenBece102l - Digital-Systems-Design - TH - 1.0 - 71 - Bece102l - 66 AcpsggrfgfNoch keine Bewertungen

- Master Thesis FpgaDokument5 SeitenMaster Thesis Fpgatashahollowaylittlerock100% (1)

- VLSI Lab ManualDokument117 SeitenVLSI Lab ManualSusmitha BollimunthaNoch keine Bewertungen

- Comprehensive Study of Flow To Program FPGA Kit Using VHDLDokument4 SeitenComprehensive Study of Flow To Program FPGA Kit Using VHDLIJRECENoch keine Bewertungen

- Summer Training Report On Vlsi and Fpga ImplementationDokument44 SeitenSummer Training Report On Vlsi and Fpga ImplementationsaurabhNoch keine Bewertungen

- 20VL004 - FPGA Based System Design: Embedded Processor Hardware DesignDokument2 Seiten20VL004 - FPGA Based System Design: Embedded Processor Hardware DesignBarzNoch keine Bewertungen

- A Brief History of Programmable Logic - CourseraFPGA - M1V2Dokument12 SeitenA Brief History of Programmable Logic - CourseraFPGA - M1V2Miguel MurilloNoch keine Bewertungen

- Computer TechnologyDokument192 SeitenComputer TechnologyAmit PatelNoch keine Bewertungen

- GTU Digital ElectronicsDokument3 SeitenGTU Digital Electronicssjbv.hardik582Noch keine Bewertungen

- Ch02 HandoutDokument69 SeitenCh02 HandoutVijay PreethamNoch keine Bewertungen

- Digital System Design Using VHDL PDFDokument47 SeitenDigital System Design Using VHDL PDFSneha S RevankarNoch keine Bewertungen

- Handbook of CSEDokument24 SeitenHandbook of CSEBala KumarNoch keine Bewertungen

- Ece5017 Digital-Design-with-fpga Eth 1.0 40 Ece5017Dokument3 SeitenEce5017 Digital-Design-with-fpga Eth 1.0 40 Ece5017Daniel MNoch keine Bewertungen

- Digital Design With An Introduction To The Verilog HDL VHDL and Systemverilog 6 E Sixth Edition Global Edition Ciletti Full ChapterDokument52 SeitenDigital Design With An Introduction To The Verilog HDL VHDL and Systemverilog 6 E Sixth Edition Global Edition Ciletti Full Chapterflorence.hernandez892100% (3)

- EE3003 - E S & Ic D: Mbedded Ystems EsignDokument4 SeitenEE3003 - E S & Ic D: Mbedded Ystems EsignCharles BradleyNoch keine Bewertungen

- BEC7L1 - Digital Cmos Vlsi-LabDokument66 SeitenBEC7L1 - Digital Cmos Vlsi-LabRamkumardevendiranDevenNoch keine Bewertungen

- R&D Facilities at ECE DepartmentDokument3 SeitenR&D Facilities at ECE DepartmentArpita MukherjeeNoch keine Bewertungen

- Ankit ResumeDokument3 SeitenAnkit ResumenikkyjNoch keine Bewertungen

- Definition:: Field-Programmable Gate ArrayDokument6 SeitenDefinition:: Field-Programmable Gate ArrayyaduyadavendraNoch keine Bewertungen

- Teaching Field Programmable Gate Array Design of Digital Signal Processing SystemsDokument4 SeitenTeaching Field Programmable Gate Array Design of Digital Signal Processing Systemsnamhoa02Noch keine Bewertungen

- Pavitra Jinaga ResumeDokument3 SeitenPavitra Jinaga Resumeastitva08Noch keine Bewertungen

- Microcontroller Architecture and Organization: Unit IDokument6 SeitenMicrocontroller Architecture and Organization: Unit IhemanthdreamzNoch keine Bewertungen

- VHDL Lab Manual PDFDokument21 SeitenVHDL Lab Manual PDFashwani_agrawal50% (2)

- EC4002 - Digital Logic DesignDokument5 SeitenEC4002 - Digital Logic DesignTarangNoch keine Bewertungen

- VHDL CourseworkDokument7 SeitenVHDL Courseworkafiwhwlwx100% (2)

- Btech New SyllabusDokument8 SeitenBtech New SyllabusDrBhoopal RaoNoch keine Bewertungen

- Computer Science (Theory) Class XII (Theory) - PythonDokument8 SeitenComputer Science (Theory) Class XII (Theory) - PythonAnu RadhaNoch keine Bewertungen

- Proposed - BE E & TC 2019 - VLSI SyllabusDokument3 SeitenProposed - BE E & TC 2019 - VLSI SyllabusRavindra DabhadeNoch keine Bewertungen

- Fpga Based 32 Bit Risc Processor DesignDokument18 SeitenFpga Based 32 Bit Risc Processor DesignAchit YadavNoch keine Bewertungen

- System On Chip Design and ModellingDokument131 SeitenSystem On Chip Design and ModellingGurram KishoreNoch keine Bewertungen

- Thesis Based On VHDLDokument8 SeitenThesis Based On VHDLevkrjniig100% (2)

- Vlsi RecordDokument61 SeitenVlsi RecordRaghul MNoch keine Bewertungen

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesVon EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesNoch keine Bewertungen

- MAT565 - Tutorial - Inverse LaplaceDokument2 SeitenMAT565 - Tutorial - Inverse LaplacefaqhrulNoch keine Bewertungen

- MIT 6.00 Notes From Lessons 1,2 and 3.Dokument8 SeitenMIT 6.00 Notes From Lessons 1,2 and 3.Nikola Nino IvankovićNoch keine Bewertungen

- Bidang Pengajian HLP 2021 - Perkhidmatan Bukan Gunasama PersekutuanDokument4 SeitenBidang Pengajian HLP 2021 - Perkhidmatan Bukan Gunasama PersekutuanMasnah Insyirah AnneskiNoch keine Bewertungen

- REVISION For END COURSE TEST - Criticial ThinkingDokument14 SeitenREVISION For END COURSE TEST - Criticial Thinkingmai đặngNoch keine Bewertungen

- Laguda, Clemente (Judicial Counter-Affidavit)Dokument19 SeitenLaguda, Clemente (Judicial Counter-Affidavit)SelurongNoch keine Bewertungen

- Ethical Issues in SupervisionDokument10 SeitenEthical Issues in SupervisionBiona FranciscoNoch keine Bewertungen

- Visallo Brochure PDFDokument2 SeitenVisallo Brochure PDFchris jonasNoch keine Bewertungen

- Quiz Unit 2 B3Dokument9 SeitenQuiz Unit 2 B3Nicolás Felipe Moreno PáezNoch keine Bewertungen

- Bqs PDFDokument14 SeitenBqs PDFMiguel ColinaNoch keine Bewertungen

- 169-Article Text-987-1-10-20220530Dokument8 Seiten169-Article Text-987-1-10-20220530Ika PratiwiNoch keine Bewertungen

- 2010-2011 CatalogDokument339 Seiten2010-2011 CatalogSimon TabNoch keine Bewertungen

- Sans Nom 2Dokument320 SeitenSans Nom 2khalidNoch keine Bewertungen

- National AnthemsDokument6 SeitenNational AnthemszhannurazimbaiNoch keine Bewertungen

- Disconnected ManDokument4 SeitenDisconnected ManBecky100% (1)

- Evacuated Flat Plate Collector PDFDokument2 SeitenEvacuated Flat Plate Collector PDFMattNoch keine Bewertungen

- Q1. Read The Passage Below and Answer The Questions That FollowDokument3 SeitenQ1. Read The Passage Below and Answer The Questions That FollowAryan KananiNoch keine Bewertungen

- GRADES 1 To 12 Daily Lesson Log Grade 3 Science Quarter 1: I. Objectives Monday Tuesday Wednesday Thursday FridayDokument10 SeitenGRADES 1 To 12 Daily Lesson Log Grade 3 Science Quarter 1: I. Objectives Monday Tuesday Wednesday Thursday Fridayblood lustNoch keine Bewertungen

- Sel KompetenDokument12 SeitenSel KompetenEnung Warsita DahlanNoch keine Bewertungen

- High School Kids Science Fiction Short StoriesDokument5 SeitenHigh School Kids Science Fiction Short StoriesHarshal bhardwaj100% (1)

- Arrays in C++Dokument13 SeitenArrays in C++weggie alcarazNoch keine Bewertungen

- Lessons Electric Circuits 1 PDFDokument530 SeitenLessons Electric Circuits 1 PDFStefano SintoniNoch keine Bewertungen

- Extemporaneous Speech in Oral CommunicationDokument3 SeitenExtemporaneous Speech in Oral CommunicationStephanie BengcoNoch keine Bewertungen

- Indonesia Fertilisers 2009Dokument5 SeitenIndonesia Fertilisers 2009George Van BommelNoch keine Bewertungen

- Family Day by Day - The Guide To A Successful Family LifeDokument212 SeitenFamily Day by Day - The Guide To A Successful Family Lifeprajya100% (3)

- Social Psychology-E BookDokument4 SeitenSocial Psychology-E BookShamilka Fernando60% (5)

- Control System QBDokument29 SeitenControl System QBPrabhavathi AadhiNoch keine Bewertungen

- KSS 41 END enDokument702 SeitenKSS 41 END enJavier Del Pozo Garcia100% (1)

- Aman-Gupta CVDokument2 SeitenAman-Gupta CVShrish GaurNoch keine Bewertungen

- Vxworks Kernel Programmers Guide 6.8Dokument802 SeitenVxworks Kernel Programmers Guide 6.8hisahinNoch keine Bewertungen

- Foundation of Computing Systems: Linked ListsDokument28 SeitenFoundation of Computing Systems: Linked ListsAnand BiradarNoch keine Bewertungen