Beruflich Dokumente

Kultur Dokumente

Sequesnce Detector

Hochgeladen von

Dinesh DevaracondaOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Sequesnce Detector

Hochgeladen von

Dinesh DevaracondaCopyright:

Verfügbare Formate

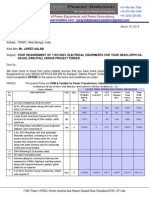

Lab Project 2: Sequence Detectors (phase 1)

201 3R .W. A l l ison

C ECS 301 CS ULB

Revision: Feb.11,2013

STUDENT

I am submitting my own work, and I understand penalties will

be assessed if I submit work for credit that is not my own.

Print Name

Estimated Work Hours

1

PointScale

4:Exemplary

3:Complete

2:Incomplete

1:Minoreffort

0:Notsubmitted

9 10

ID Number

5%will be deducted from total score

Sign Name

for each day late

Date

Score=Pointsawarded(Pts)xWeight(Wt)

GRADER

#

Demonstration

Wt

Demo working Sequence Detectors

Documentation / Source Code

Testbench / Simulation-Verification

Pts

Score

Grader Signature

Date

Days

TotalInLab

Score

Late

GeneralStatement: You are to design and implement a sequential

circuit (in verilog) that functions as a dual implementation nonoverlapping sequence detector. The sequence detector will have an

input X that will be used to detect the non-overlapping sequence of

101101. The output Z is to become 1 upon completion of the

correct input sequence, and is 0 otherwise. Your circuit will have a

both a Mealy implementation and a Moore implementation. A

"mode" input (M) specifies which type of sequence detector is

being exercised: If M = 0, exercise the Moore implementation; if

M = 1, switch to the Mealy implementation.

Clocking and I/O Specifications: The clock input to the sequence detector is to be provided by debounced

push-button switch (BTN0) developed in Lab 1 (clocked by a 500Hz clock). The reset input is to come from

another push button switch (BTN3). Input M is to come from slide switch SW7. Input X is to come from slide

switches SW0. The single output Z is to be displayed on LD0. Display the 3-bit present state (e.g. Q[2:0]) for the

respective sequence detector on LD7..LD5.

Top Level Specifications: You are to create a schematic diagram (see next page) that instantiates the clock

divider module, the debounce module and the sequence detector, connecting them to the input (X) and output

(Z), the 50MHz board clock and reset, including appropriate BUFG for high speed inputs (e.g. 50 MHz clock).

The verilog module that implements the sequence detector must be a structural implementation that

instantiates the necessary D flip flops and assigns (using verilog assign statements) the inputs to each flip flop

with the outputs of appropriate combinational logic for the next state. The Z output is also to be assigned

according to the appropriate combinational logic.

DueDate:Monday,February18,2013

{Monday of Week 5}

301 Lab Assignment 2 Page 1

Lab Project 2: Sequence Detectors (phase 1)

Revision: Feb.11,2013

201 3R .W. A l l ison

C ECS 301 CS ULB

Simulation/Verification: The simulation of the sequence detector module is to be according to a verilog

testbench module (see p. 3) that will instantiate the sequence detector and feed it with the appropriate test

sequence. In Xilinx ISE, a verilog testbench module is created by right clicking on the appropriate module in

the Sources windows, specifying New Source, and then selecting Verilog Test Fixture. Once you have

typed in the verilog code for the testbench module (copied from page 3) you invoke the ISE simulator by

selecting the testbench file while in the Simulation section in Hierarchy window pane and then double

clicking on the Simulate Behavioral Model in the Processes window pane. Note: it is very important that

you have the `timescaledirective on the first line of the testbench!

Deliverables: Your must turn in (1) these specification sheets, followed by (2) a printout of your schematic, (3)

the state diagram and state table for the Moore implementation, (4) K-maps and derivations for your state and

output equations for the Moore implementation, (5) the state diagram and state table for the Mealy

implementation, (6) K-maps and derivations for your state and output equations for the Mealy implementation,

(7) printouts of the verilog files for the sequence detector module and the verilog testbench module, and (8) the

printouts of both "simulation" waveforms (i.e. the results of the verilog testbench) that show all functions work

correctly.

301 Lab Assignment 2 Page 2

Lab Project 2: Sequence Detectors (phase 1)

201 3R .W. A l l ison

C ECS 301 CS ULB

Revision: Feb.11,2013

`timescale 1ps / 100fs

module testbench();

//

//

//

//

//

//

DATE:

AUTHOR:

MODULE:

FILENAME:

PROJECT:

VERSION:

Mon Aug 24 09:44:44 2012

Your_Name

sequence_detector_101101

sequence_detector_101101

301_lab2

Version 2.0

// Inputs

reg clk, reset, X, M;

// Outputs

wire

Z;

wire [2:0] Q;

// Local Declarations

reg [44:1] sequence_pattern;

integer

i;

// Instantiate the Unit Under Test

sequence_detector_101101 uut (

.clk(clk), .reset(reset),

.X(X),

.M(M),

.Z(Z)

.Q(Q) );

Youllhavetoeditthispart,dependingonthe

nameofyoursequencedetectormodule,and

theorderandnameofyourinputs,outputs.

// Generate 10 ps Clock

always

#5 clk = ~clk;

// Initialize Inputs

initial begin

$timeformat(-12, 1, " ps", 8);

clk = 0; reset = 0; X = 0; M = 0;

sequence_pattern = 44'b01100010101101011011111001011011011011101010;

@(negedge clk)

reset = 1;

@(negedge clk)

reset = 0;

M = 0;

// Mealy implementation (M=0); to simulate the

//

Moore implementation, set M = 1 and run the simulation again

// this loop will "feed" the sequence detector with the

// test sequence pattern from MSB to LSB

for (i=44; i > 0; i=i-1) begin

// change inputs on negative edge of clock

@(negedge clk)

X = sequence_pattern[i];

// display outputs after the positive clock

@(posedge clk)

#1 $display("Time=%t X=%b Q=%b Z=%b", $time, X, Q, Z);

end

$stop;

end

endmodule

301 Lab Assignment 2 Page 3

Das könnte Ihnen auch gefallen

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- VariCAD 2D 3D Light Industrial and Mechanical CAD SystemDokument178 SeitenVariCAD 2D 3D Light Industrial and Mechanical CAD Systemicad100% (4)

- Astm A307-14Dokument6 SeitenAstm A307-14Xamir Suarez Alejandro100% (2)

- Installation Manual Series D 1FH: Proportional DC ValveDokument20 SeitenInstallation Manual Series D 1FH: Proportional DC ValveАлексей Бурлаков100% (1)

- Power Equipment Suppliers for NTPC ProjectDokument17 SeitenPower Equipment Suppliers for NTPC ProjectSharafat AliNoch keine Bewertungen

- Vision and Scope DocumentDokument7 SeitenVision and Scope DocumentCyra ArifeenNoch keine Bewertungen

- Manual de La Ingleteadora BOSCH GCM12SDDokument164 SeitenManual de La Ingleteadora BOSCH GCM12SDChristopher DavisNoch keine Bewertungen

- STLD Notes 0Dokument177 SeitenSTLD Notes 0Dinesh DevaracondaNoch keine Bewertungen

- MOS Transistors and CMOS InvertersDokument34 SeitenMOS Transistors and CMOS InvertersGaurav GopalkrishnaNoch keine Bewertungen

- 16D 5Dokument13 Seiten16D 5Sumanth VarmaNoch keine Bewertungen

- VLSIDokument16 SeitenVLSIDinesh DevaracondaNoch keine Bewertungen

- M.Tech VLSI Design Engineer Seeks Memory Design RoleDokument2 SeitenM.Tech VLSI Design Engineer Seeks Memory Design RoleDinesh DevaracondaNoch keine Bewertungen

- Read Stability and Write Ability .Dokument12 SeitenRead Stability and Write Ability .Dinesh DevaracondaNoch keine Bewertungen

- lm4f120h5qr 124014Dokument1.191 Seitenlm4f120h5qr 124014Dinesh DevaracondaNoch keine Bewertungen

- M.Tech VLSI Design Engineer Seeks Memory Design RoleDokument2 SeitenM.Tech VLSI Design Engineer Seeks Memory Design RoleDinesh DevaracondaNoch keine Bewertungen

- lm4f120h5qr 124014Dokument1.191 Seitenlm4f120h5qr 124014Dinesh DevaracondaNoch keine Bewertungen

- Lec 31Dokument22 SeitenLec 31Dinesh DevaracondaNoch keine Bewertungen

- Design of The 11011 Sequence Detector: Slide 1 of 23 Slides Revised 9/28/2009Dokument23 SeitenDesign of The 11011 Sequence Detector: Slide 1 of 23 Slides Revised 9/28/2009sgoshi84Noch keine Bewertungen

- VLSI Interview QuestionsDokument43 SeitenVLSI Interview QuestionsDinesh DevaracondaNoch keine Bewertungen

- Unit-3 (ASIC)Dokument48 SeitenUnit-3 (ASIC)Dinesh DevaracondaNoch keine Bewertungen

- Pipelining Instruction Execution and Cache Memory PoliciesDokument10 SeitenPipelining Instruction Execution and Cache Memory PoliciesDinesh DevaracondaNoch keine Bewertungen

- Loading Violation ReportDokument41 SeitenLoading Violation ReportDinesh DevaracondaNoch keine Bewertungen

- Power Analysis Using Soc EncounterDokument8 SeitenPower Analysis Using Soc EncounterDinesh DevaracondaNoch keine Bewertungen

- 2013 01 OscDokument182 Seiten2013 01 OscDinesh DevaracondaNoch keine Bewertungen

- Cadence Layout TipsDokument4 SeitenCadence Layout TipsBhargav CoolNoch keine Bewertungen

- Lab6 SOCE EngDokument7 SeitenLab6 SOCE EngAvas RoyNoch keine Bewertungen

- Lab6 SOCE EngDokument7 SeitenLab6 SOCE EngAvas RoyNoch keine Bewertungen

- Hello WordDokument1 SeiteHello WordDinesh DevaracondaNoch keine Bewertungen

- Formulas and practice problems for time and distance examsDokument3 SeitenFormulas and practice problems for time and distance examsDinesh DevaracondaNoch keine Bewertungen

- Hello WordDokument1 SeiteHello WordDinesh DevaracondaNoch keine Bewertungen

- Service Manual: SharpDokument21 SeitenService Manual: SharpMarco MinottiNoch keine Bewertungen

- 2N2369Dokument7 Seiten2N2369Martín SayagoNoch keine Bewertungen

- How To Turn Off or Disable Hardware Acceleration in Windows 11 - 10Dokument10 SeitenHow To Turn Off or Disable Hardware Acceleration in Windows 11 - 10favio lopezNoch keine Bewertungen

- Monoprice Select Mini WiringDokument1 SeiteMonoprice Select Mini Wiringchart328Noch keine Bewertungen

- SICK - Reles de SegurançaDokument78 SeitenSICK - Reles de SegurançachnanduNoch keine Bewertungen

- SELinux For DummiesDokument38 SeitenSELinux For DummiesdbahanyNoch keine Bewertungen

- Chapter 9: 8086/8088 Hardware SpecificationsDokument28 SeitenChapter 9: 8086/8088 Hardware SpecificationsChanchan LebumfacilNoch keine Bewertungen

- IoulistDokument4 SeitenIoulisthaji85Noch keine Bewertungen

- Cisco Lab OSPF EncapsulationDokument23 SeitenCisco Lab OSPF EncapsulationMike OwlyNoch keine Bewertungen

- AV Receiver Audio Debug ModesDokument108 SeitenAV Receiver Audio Debug ModesLogan IngramNoch keine Bewertungen

- Addressable Fire Detection and Control Miniplex TranspondersDokument8 SeitenAddressable Fire Detection and Control Miniplex TranspondersAfdhal SyahrullahNoch keine Bewertungen

- Service Mode & Error Codes - Led Blinking Codes - Philips Pfl-Series LCD TvsDokument4 SeitenService Mode & Error Codes - Led Blinking Codes - Philips Pfl-Series LCD TvsEnrik VillaNoch keine Bewertungen

- PC800 800LC 8R1 LoadingDokument24 SeitenPC800 800LC 8R1 LoadingAkhmad SebehNoch keine Bewertungen

- Sartech ARG5410 EPIRB TesterDokument3 SeitenSartech ARG5410 EPIRB TesterEric PskdNoch keine Bewertungen

- Qualcomm Robotics RB5 Development Kit User Guide: 80-88500-5 Rev. AE December 7, 2023Dokument89 SeitenQualcomm Robotics RB5 Development Kit User Guide: 80-88500-5 Rev. AE December 7, 2023Priya NynaruNoch keine Bewertungen

- Unix Operating System: 1 STC TechnologiesDokument29 SeitenUnix Operating System: 1 STC TechnologiesrajNoch keine Bewertungen

- 11.3 Paper PDFDokument6 Seiten11.3 Paper PDFChandan ChoudhuryNoch keine Bewertungen

- Sandy Bridge CPU and Cougar Point PCH schematics documentDokument64 SeitenSandy Bridge CPU and Cougar Point PCH schematics documentArcangelo Di BattistaNoch keine Bewertungen

- Reverse Engineering For BeginnersDokument924 SeitenReverse Engineering For Beginnersmobscribe0% (1)

- 621 Sell SheetDokument2 Seiten621 Sell Sheetintegra_emsNoch keine Bewertungen

- Gas Gauge Ic With Smbus Interface: Features General DescriptionDokument33 SeitenGas Gauge Ic With Smbus Interface: Features General DescriptiongayamartNoch keine Bewertungen

- P43AL Series Manual en V1.0Dokument74 SeitenP43AL Series Manual en V1.0Cel Groaznic PimNoch keine Bewertungen

- Ntfs & Fat DiffDokument3 SeitenNtfs & Fat DiffJoe SylvineNoch keine Bewertungen

- Bildr Use The Easydriver Stepper Motor Driver..Dokument5 SeitenBildr Use The Easydriver Stepper Motor Driver..fayazrashNoch keine Bewertungen