Beruflich Dokumente

Kultur Dokumente

Transistor Como Inrerruptor

Hochgeladen von

Daniel Andres KayeCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Transistor Como Inrerruptor

Hochgeladen von

Daniel Andres KayeCopyright:

Verfügbare Formate

Preparacin de reportes de Informe de laboratorios

POLARIZACION DEL JFET

Daniel adres calle Amaya

Kayets125@hotmail.com

RESUMEN: en el siguiente laboratorio crearemos

las condiciones necesarias para poner a prueba

los transistores 2n5457 y k40c ,el cual es un nuevo

modelo a estudiar por nuestro curso, para poder

determinar sus valores, usaremos una fuente

sencilla de 12 voltios.

es ID=IS, tanto para transistores de canal n como

para los de canal p, tampoco hay que olvidarse de

la ecuacin de Shockley, con esto en mente ya se

puede ver algunos tipos de polarizacin.

Se vern 3 tipos de polarizacin los cuales son:

Polarizacin de puerta del JFET.

del JFET se realiza mediante

Polarizacin por autopolarizacin del JFET.

tensin continua y consiste en prepararlo para que

Polarizacin por divisor de tensin del

1 INTRODUCCIN

La polarizacin

en un circuito, en el cual se le quiere utilizar, a

JFET.

travs del JFET circule una cantidad de corriente

ID por el drenaje, y a su vez se obtenga una

tensin entre el drenaje y la fuente VDS para esa

cantidad de corriente ID, a esto se le llama obtener

el punto de operacin o punto Q. La corriente ID va

depender de la tensin compuerta fuente VGS que

exista en la malla de entrada, la VDS depender

Para ver los diferentes tipos de polarizacin se

utilizar un JFET de canal n, se proceder

a obtener una ecuacin en la malla de entrada y

otra en la malla de salida. Para polarizar un JFET

de canal p se proceder de manera similar,

teniendo en cuanta que las tensiones de

polarizacin tendrn que invertirse, lo cual dar

como resultado que la ID cuyo sentido se mide del

drenaje hacia la fuente, tambin se invierta.

de la malla de salida del circuito, para ver esto ser

de utilidad la grfica de entrada y la de salida del

JFET.

2 1.- Polarizacin de puerta del JFET.

Anteriormente se ha visto que el JFET tiene una

corriente drenaje fuente de saturacin IDSS, la

cual indica cual es la corriente mxima que podr

circular entre el drenaje y la fuente, entonces la

corriente ID al cual se polarizar el transistor solo

podr tener valores comprendidos entre 0mA y

IDSS.

Como la corriente de la compuerta IG=0, hay que

tener siempre presente que la corriente de drenaje

ID y la corriente de fuente IS son iguales esto

Este tipo polarizacin se caracteriza porque se

utilizan dos fuentes de alimentacin, una de ellas

se conecta directamente entre la compuerta y la

fuente, si esta fuente de alimentacin es variable

se puede controlar la ID, lo cual a su vez provocar

que el punto de operacin del JFET cambie y

como consecuencia cambiar VDS, de esta forma

se puede hacer que el JFET trabaje en la regin

hmico o en la regin activa; este es el tipo de

polarizacin que se utilizar si se quiere hacer

trabajar al JFET como resistencia variable

controlada por voltaje.

1

electrnica anloga 2

laboratorio de

Preparacin de reportes de Informe de laboratorios

.

El arreglo principal para este tipo de polarizacin

para un JFET de canal n y uno de canal p, es el

que se muestra a continuacin:

VDS=0, en este caso si se despeja se obtiene

ID=VDD/RD lo cual se conoce como corriente de

drenaje de saturacin IDsat; por lo tanto los dos

puntos que necesitamos ubicar sobre el grfico de

salida para trazar la recta de carga sern

VDScorte=VDD para ID=0 y IDsat=VDD/RD para

VDS=0.

Los trazos de la recta de carga para la entrada y

de la recta de carga para la salida en forma

general para este tipo de polarizacin estn

representados en la siguiente figura.

De la malla de entrada, por Kirchhoff se puede ver

para el JFET de canal n que VGS=-VGG y para el

de canal p VGS=VGG, estas sern sus ecuaciones

de entrada, son rectas paralelas al eje ID, las

cuales hay que trazar sobre la grfica de entrada,

donde estas rectas corten a la curva de

transferencia ser el punto de operacin para la

entrada del JFET, a partir de este punto de corte se

traza una paralela al eje VGS y se conocer el

valor de la ID para el punto de operacin del JFET;

si en la malla de salida se aplica nuevamente

Kirchhoff se obtendr una ecuacin a partir de la

cual se puede despejar VDS y se tendr:

Para el JFET de canal n: VDS=VDD-ID*RD, que es

su ecuacin de recta de salida.

Para el JFET de canal p: VDS=-VDD+ID*RD, que

es su ecuacin de recta de salida.

Si en la ecuacin recta de carga de la salida se

reemplaza el valor de ID para el punto de

operacin, obtenida a partir de la curva de

transferencia, se puede hallar la VDS para el punto

de operacin del transistor.

En lo que sigue se comentar para el caso del

JFET de canal n, lo cual tambin ser vlido para

los JFET de canal p, con la nica diferencia de que

hay que invertir las polaridades; de la ecuacin de

recta de carga de salida obtenida para el JFET de

canal n, hay que ubicar 2 puntos para trazarla, uno

de los puntos se obtendr haciendo ID=0, si se

despeja se obtiene VDS=VDD, lo cual se conoce

como tensin de drenaje fuente de corte VDScorte;

el otro punto se obtendr haciendo en la ecuacin

En la figura se puede ver que si la fuente de

alimentacin cambia en valor VGG se cambiar

VGSQ, lo cual a su vez cambiar ID lo que har

que la recta de carga de salida cambie y como

consecuencia cambie el punto de operacin, este

fenmeno es aprovechado cuando se quiere

utilizar el JFET como resistencia variable, otra

forma en que cambiar el punto de operacin es si

se cambia el JFET, ya que la curva de

transferencia cambiar, por lo cual el punto

de cruce de la recta de carga de entrada con la

curva de transferencia cambiar lo que dar un

nuevo valor para IDQ, entonces la recta de carga

de salida se cruzar con una curva de salida

diferente dando como resultado que el punto de

operacin cambie; mayormente el cambio de

posicin del punto de operacin es demasiado

grande cuando se cambia el JFET, de all que si se

quiere un punto de operacin que no vare si se

cambia el JFET este tipo de polarizacin no sea lo

mejor.

2

electrnica anloga 2

laboratorio de

Preparacin de reportes de Informe de laboratorios

3 Polarizacin por autopolarizacin.

En este tipo de polarizacin solamente se necesita

una fuente de alimentacin, en la figura siguiente

se muestra este tipo de arreglo para un JFET de

canal n, es muy similar para el caso del JFET de

canal p, con la diferencia de que hay que invertir

las polaridades.

transferencia que tambin depende de VGS e ID,

el punto donde se intercepten ambos trazos ser el

punto de operacin del JFET.

Por lo tanto, lo primero que hay que hacer es

trazar la curva de transferencia, luego dibujar la

recta de carga de la entrada sobre la curva de

transferencia, para lo cual necesitamos obtener la

ecuacin de la recta de entrada, entonces

aplicando Kirchhoff en esta malla:

VGS+VRS+VRG=0, luego

VGS+IS*RS+IG*RG=0, Pero IG=0 y IS=ID

VGS+ID*RS=0, de donde

VGS=-ID*RS, esta es la ecuacin de la recta de

entrada.

Como se puede ver en la fuente del JFET se

coloca una resistencia RS, esta resistencia ser la

que polarice la compuerta, es decir la VGS que

existir en el transistor la cual decidir cuanta ser

la corriente de drenaje ID que es igual a la

corriente de la fuente IS; la resistencia RG es una

resistencia del orden de los mega ohmios que se

utiliza principalmente para los circuitos de

amplificacin para no perder la impedancia de

entrada del JFET, en el vdeo que sigue ms abajo

se comenta como es que actuar, adems como

IG=0 entonces VG=0 por tanto la compuerta est

conectada a tierra.

Los datos IDSS y VGScorte se obtienen de la hoja

de datos del JFET, con los cuales se trazar la

curva de transferencia.

La idea para resolver o disear este tipo de

circuitos es a partir de la malla de entrada obtener

una ecuacin de una recta que depender de VGS

e ID, luego trazar esta recta sobre la grfica de

Se ve que la VGS es un valor negativo, que es

como tiene que ser para un JFET de canal n, para

trazar la recta de entrada sobre la curva de

transferencia se necesita 2 puntos por lo menos ,

uno de ellos puede ser por ejemplo para ID=0, lo

que dar VGS=0, siendo el primer punto entonces

(0,0); como IDSS es dato ese valor se puede

reemplazar en la ecuacin para obtener el otro

punto, que es VGS=-IDSS*RS, con lo cual el otro

punto sera (-IDSS*RS,IDSS), al trazar esta recta

sobre la curva de transferencia donde se

intercepten ese ser el punto de operacin de

JFET, a partir del cual se puede conocer VGSQ y

la IDQ.

Para encontrar el valor VDSQ ser recurre a la

malla de salida a la cual se aplica Kirchhoff

VDD-VRD-VDS-VRS=0, luego

VDD-ID*RD-VDS-IS*RS=0, Pero IS=ID

VDD-VDS-ID*(RS+RD), de donde al despejar

VDS=VDD-ID*(RS+RD), que ser la ecuacin de la

recta de salida.

Si en esta ecuacin se reemplaza IDQ obtenida

anteriormente se encontrar el valor de VDSQ, por

lo tanto el punto de operacin del JFET ser

(VDSQ,IDQ), si se quiere trazar la recta de carga

de salida, son necesarios dos puntos uno de ellos

ser cuando ID=0, de donde VDScorte=VDD, el

otro punto ser para VDS=0, de donde IDsat=VDD/

3

electrnica anloga 2

laboratorio de

Preparacin de reportes de Informe de laboratorios

.

(RS+RD), en el punto donde se intercepte la recta

de carga de salida con la curva que le corresponda

a la corriente IDQ para VGSQ en la salida, ese

ser el punto de operacin el JFET; los grficos

deben ser algo as:

Como se puede ver en la en la malla de la entrada

del circuito, ahora hay dos resistencia, las cuales

sern de gran ohmiaje del orden de los mega

ohmios, esto es para no perder la alta impedancia

de entrada de los JFET en los circuitos de

amplificacin, entre las dos forman un divisor de

tensin, por lo cual la tensin de la compuerta VG

tendr un valor positivo.

Los datos IDSS y VGScorte se obtienen de la hoja

de datos del JFET, con los cuales se trazar la

curva de transferencia.

La idea para resolver o disear este tipo de

circuitos es a partir de la malla de entrada obtener

una ecuacin de una recta que depender de VGS

e ID, luego trazar esta recta sobre la grfica de

transferencia que tambin depende de VGS e ID,

el punto donde se intercepten ambos trazos ser el

punto de operacin del JFET.

3.1 Polarizacin por divisor de tensin del

JFET.

Por lo tanto, lo primero que hay que hacer es

trazar la curva de transferencia, luego dibujar la

recta de carga de la entrada sobre la curva de

transferencia, para lo cual necesitamos obtener la

ecuacin de la recta de entrada, la que obtendr a

partir de:

VGS=VG-VS, adems

Para este tipo de polarizacin, el punto de

operacin del JFET se ve menos afectado cuando

se cambia un transistor por otro, siendo ambos de

la misma familia, por ejemplo el 2N3819. En este

caso tambin se polariza el JFET con una sola

fuente de alimentacin, en la siguiente figura se

muestra el arreglo para la polarizacin por divisor

de tensin.

VS=RS*IS, pero IS=ID, entonces

VGS=VG-RS*ID, esta es la ecuacin de la recta de

entrada.

Donde por divisin de tensin VG=VDD*R2/

(R1+R2);

VGS ser un valor negativo, ya que es un JFET de

canal n, para trazar la recta de entrada sobre la

curva de transferencia se necesita 2 puntos por lo

menos , uno de ellos puede ser por ejemplo para

ID=0, lo que dar VGS=VG, siendo el primer punto

entonces (VG,0); para el otro punto se tomar

VGS=0 de donde ID=VG/RS por lo cual el otro

punto sera (0,VG/RS), al trazar esta recta sobre la

curva de transferencia donde se intercepten ese

ser el punto de operacin de JFET, a partir del

cual se puede conocer VGSQ y la IDQ.

Para encontrar el valor VDSQ ser recurre a la

malla de salida a la cual se aplica Kirchhoff

VDD-VRD-VDS-VRS=0, luego

4

electrnica anloga 2

laboratorio de

Preparacin de reportes de Informe de laboratorios

.

VDD-ID*RD-VDS-IS*RS=0, Pero IS=ID

VDD-VDS-ID*(RS+RD), de donde al despejar

VDS=VDD-ID*(RS+RD), que ser la ecuacin de la

recta de salida.

Si en esta ecuacin se reemplaza IDQ obtenida

anteriormente se encontrar el valor de VDSQ, por

lo tanto el punto de operacin del JFET ser

(VDSQ,IDQ), si se quiere trazar la recta de carga

de salida, son necesarios dos puntos uno de ellos

ser cuando ID=0, de donde VDScorte=VDD, el

otro punto ser para VDS=0, de donde IDsat=VDD/

(RS+RD), en el punto donde se intercepte la recta

de carga de salida con la curva que le corresponda

a la corriente IDQ para VGSQ en la salida, ese

ser el punto de operacin el JFET; los grficos

deben ser algo as:

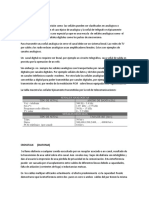

magnitud

VDS

VGS

VGD

IS

ID

IG

valor

valor medido calculado

9.26 v

0,57 v

9.8 v

1.2 mA

1.3 mA

0 mA

Procedimiento

1. Arme el siguiente circuito, ubique en forma

adecuada los instrumentos tal que pueda medir ID

y VGS; encienda las fuentes y anote los valores de

ID y VGS as tambin VDS.

5

electrnica anloga 2

laboratorio de

Preparacin de reportes de Informe de laboratorios

2. Arme el circuito mostrado en la siguiente figura

3. Arme el circuito mostrado en la siguiente figura 3

2. Conecte adecuadamente los instrumentos para

y haga las medidas de ID as como las tensiones

medir ID y VGS, encienda las fuente y anote los

en los diferentes nodos y puntos del circuito.

valores de ID, VGS y las dems tensiones del

circuito. Todo circuito debe ser armado con las

fuentes apagadas previamente ajustadas al valor

dado en el diagrama.

magnitud

VDS

VGS

VGD

IS

ID

IG

valor

valor medido calculado

10,13 v

0,57 v

9,6 v

5,8mA

1,3 mA

0 mA

magnitud

VDS

VGS

VGD

IS

ID

IG

6

electrnica anloga 2

valor

valor medido calculado

7,06 V

0,35 V

7,39 V

2,2 mA

2 mA

77,1 a

laboratorio de

Preparacin de reportes de Informe de laboratorios

4. conclusiones

En el laboratorio interior se puso a prueba los

temas visto anterior mente en clase los cuales aran

los diferentes tipos de polarizacin del jfet, gracias

a estos tres tipos de combinaciones observamos el

comportamiento de los jfet, planteando su estado

de saturacin el momento de tener oV en VG y

permitiendo todo el flujo de la corriente.

En el primer circuito comprobamos que al no haber

una resistencia en el source el VD es igual al VS

puesto que al no haber un elemento resistivo se

permite el flujo de corriente sin ninguna cada de

tensin.

En la figura 2 encontramos que gracias a la

configuracin de auto polarizacin el voltaje que

fluye a travs del circuito es casi igual que el de

Lafuente, adems este circuito mejora las

corrientes y permite una mejor amplificacin.

Con el divisor de voltaje de la figura 3 observamos

que la corriente de entrada en el G era demasiado

baja puesto que es uno de los parmetros

producidos por el divisor de voltaje, permitiendo as

un voltaje alto en las dems mallas del circuito.

Referencias

http://mrelbernitutoriales.com/transistorjfet/conociendo-el-jfet/pruebas-con-eljfet/curva-de-transferencia-del-jfet/polarizaciondel-jfet/

7

electrnica anloga 2

laboratorio de

Das könnte Ihnen auch gefallen

- Practicas RealizadasDokument28 SeitenPracticas RealizadasRaysha Ross Enciso RaveloNoch keine Bewertungen

- DiafoniaDokument3 SeitenDiafoniakuinonyNoch keine Bewertungen

- Carpeta Completa de TPS 2020Dokument85 SeitenCarpeta Completa de TPS 2020MariaNoch keine Bewertungen

- Deber 2 2018ADokument2 SeitenDeber 2 2018AJorgeCastillo0% (1)

- Multirack Setup SpanishDokument23 SeitenMultirack Setup SpanishSergio PerroneNoch keine Bewertungen

- Modos de Operación Del BJTDokument3 SeitenModos de Operación Del BJTAlvin Del Valle Benitez0% (1)

- ESA Training English PDFDokument53 SeitenESA Training English PDFRay LatinoNoch keine Bewertungen

- Resumen Recursos TecnológicosDokument7 SeitenResumen Recursos TecnológicosGRACE CERDANoch keine Bewertungen

- Práctica 1. Funcionamiento Del Diodo SemiconductorDokument11 SeitenPráctica 1. Funcionamiento Del Diodo SemiconductorBayron A. Pérez AyalaNoch keine Bewertungen

- Medida de Un PixelDokument17 SeitenMedida de Un Pixelsaul2347Noch keine Bewertungen

- ListarDokument9 SeitenListaredocuevas9250Noch keine Bewertungen

- Ejercicios Compuertas LogicasDokument16 SeitenEjercicios Compuertas LogicasAme TrineNoch keine Bewertungen

- Catalogo Jensembler AbrilDokument113 SeitenCatalogo Jensembler AbrilRogelio HernandezNoch keine Bewertungen

- FCO3Dokument9 SeitenFCO3yotuel perezNoch keine Bewertungen

- Notebook Inspiron 14 3000 Intel Core I3-5005u 6GB 1TB 14 UbuntuDokument2 SeitenNotebook Inspiron 14 3000 Intel Core I3-5005u 6GB 1TB 14 UbuntuNico InfanteNoch keine Bewertungen

- Dispositivos FlexiblesDokument20 SeitenDispositivos Flexiblestdbo120Noch keine Bewertungen

- Chasis HP BladeSystem c7000 Instrucciones para La Instalación RápidaDokument16 SeitenChasis HP BladeSystem c7000 Instrucciones para La Instalación RápidaJonatan SajbinNoch keine Bewertungen

- Manual Tristation 15-04-10Dokument75 SeitenManual Tristation 15-04-10JuCeMoOr100% (1)

- Investigacion de Significado de Materiales ElectricosDokument2 SeitenInvestigacion de Significado de Materiales ElectricosOSCAR FABIAN GONZALEZ CASTRONoch keine Bewertungen

- Tubos Al VacioDokument17 SeitenTubos Al Vacioteban007Noch keine Bewertungen

- Informe de HardwareDokument7 SeitenInforme de HardwareAnthony Lopez100% (1)

- Circuitos SecuencialesDokument24 SeitenCircuitos SecuencialesDaniel GarciaNoch keine Bewertungen

- Informe 3 Circuito Fijador de Voltaje y Doblador de VoltajeDokument4 SeitenInforme 3 Circuito Fijador de Voltaje y Doblador de VoltajeMichael Jara López100% (2)

- Proyecto Television Digital Por CableDokument17 SeitenProyecto Television Digital Por CableVargas Galarza JhonnyNoch keine Bewertungen

- ProcesadoresDokument6 SeitenProcesadoresYuseth De Jesus Jimenez VillanuevaNoch keine Bewertungen

- 150 Problemas DeTeorías de CircuitosDokument254 Seiten150 Problemas DeTeorías de CircuitosGregori GomezNoch keine Bewertungen

- Previo FiltrosDokument11 SeitenPrevio FiltrosAlejandro GaSpar HuamaníNoch keine Bewertungen

- Capitulo 07 Instrucciones BasicasDokument74 SeitenCapitulo 07 Instrucciones BasicasAbel AndradaNoch keine Bewertungen

- Informe de Laboratorio 4 - Convertidor Buck y BoostDokument9 SeitenInforme de Laboratorio 4 - Convertidor Buck y BoostVICTOR MANUEL DELGADO CUBILLOSNoch keine Bewertungen