Beruflich Dokumente

Kultur Dokumente

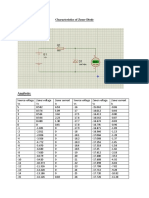

XC Sun49

Hochgeladen von

Alaa RamadanOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

XC Sun49

Hochgeladen von

Alaa RamadanCopyright:

Verfügbare Formate

Tolerance Calculations in

Power Distribution Networks

The impedance gradient of power planes around bypass capacitors

depends on the impedance of planes and the loss of bypass capacitor.

by Istvan Novak, Ph.D.

Senior Signal Integrity Staff Engineer

Sun Microsystems

istvan.novak@sun.com

More designers are determining the requirements

and completing the design of power distribution

networks (PDN) for FPGAs and CPUs in the frequency domain. Although the ultimate goal is to

keep the time-domain voltage fluctuation (noise)

on the PDN under a pre-determined maximum

level, the transient noise current that creates the

noise fluctuations may have many independent and

highly uncertain components, which in a complex

system are hard to predict or measure.

00

Xcell Journal

Summer 2004

Bypass Capacitor

predictable, so much so that we

often forget to analyze our PDN

designs against component tolerances. In this article, well show

how tolerances of bypass-capacitor

parameters, such as capacitance

(C), effective series resistance

(ESR), effective series inductance

(ESL), and capacitor location

impact the impedance of PDNs.

Power Planes

Active Device

Test Point 1

PCB

Test Point 2

Figure 1 Simple sketch of a PDN with two active devices,

three capacitors, and one pair of power planes

ESR

ESL

Figure 2 Three-element equivalent

circuit of bypass capacitors

Figure 1 is a simple sketch of a PDN [1]

with two test points. In the frequency

domain, you can describe this network

with a two-by-two impedance matrix,

where the indices refer to the test points.

Z11 and Z22 are the self impedances at test

points 1 and 2, respectively, and Z12 and

Z21 are the transfer impedances between

test points 1 and 2.

With very few exceptions, the PDN

components are electrically reciprocal;

therefore the two transfer impedances are

identical, and can be replaced with a mutual impedance term:

Z12 = Z21 = ZM.

You cannot assume electrical symmetry, however, so Z11 and Z22 are, in general, different. You can calculate the noise

voltages at test points 1 and 2 generated

by the noise currents of I1(t) and I2(t) of

the two active devices with the following

formula:

V 1(t) = Z 11I 1(t) + Z MI 2(t)

V 2(t) = Z MI 1(t) + Z 22I 2(t)

A PDN comprises power sources

(DC/DC, AC/DC converters, batteries);

low- and medium-frequency bypass capacitors; PCB planes or other metal structures

(a collection of traces or patches); packages

with their PDN components; and the

PDN elements of the silicon [2]. When

dealing with board-level PDN, its impedance contributions to the overall PDN performance are much more stable and

Summer 2004

could use in a PDN. Each curve has a label,

giving the C, ESR, and ESL values

assumed for the part. The SRF and Q values are also shown for each part. With these

numbers, the 100 uF part could be a tantalum brick; the 1 uF and 0.1 uF parts could

be multi-layer ceramic capacitors (MLCC).

When connecting capacitors with different SRFs in parallel, they may create

anti-resonance peaks where the impedance

magnitude exceeds the lower boundary of

the composing capacitors impedance magnitude values [4] [5]. The impedance

penalty gets bigger as the Q of capacitors

gets bigger, or as their SRFs are farther

apart in frequency.

The anti-resonance peaks get even bigger when you consider the possible tolerances associated with the capacitor

parameters. We illustrate this in Figure 4,

which shows what happens in typical, best,

and worst cases when you connect the three

capacitors from Figure 3 in parallel. The

plot assumes no connection impedance or

delay between the capacitors. You can use

this assumption as long as the distance

between the capacitors is much less than

the wavelength of higher frequency of

interest, and the connecting series plane

impedance is much less than the impedance of capacitors.

The frequency plot extends up to 100

C, ESR, and ESL Tolerance Effects

Figure 2 shows the simple equivalent circuit of a bypass capacitor when neglecting

the parallel leakage of the capacitor. The

series capacitor-resistor-inductor circuit

shows a resonance frequency with a given

quality factor (Q). You can calculate the

series resonance frequency (SRF) and Q

from the equations below:

ESL

1

C

SRF =

; Q=

ESR

2 C * ESL

Although in a general case all three elements in the equivalent circuit are frequency-dependent [3], for the sake of simplicity,

and because it would not change the conclusions of this article, well use frequencyindependent constant parameters.

Figure 3 shows the impedance magnitudes of three different capacitors you

Impedance Magnitudes of Capacitors [Ohm]

1.E+00

1.E-01

100 uF

1 uF

0.1 uF

0.1 Ohm

0.02 Ohm

0.05 Ohm

10 nH

3 nH

0.8 nH

SRF = 0.16 MHz

SRF = 2.91 MHz

SRF = 17.8 MHz

Q = 0.1

Q = 2.7

Q = 1.8

1.E-02

1.E-02

1.E-01

1.E+00

1.E+01

1.E+02

Frequency [MHz]

Figure 3 Impedance magnitudes of three stand-alone bypass capacitors

Xcell Journal

00

Impedance of Three Parallel Capacitors [Ohm]

Max: 0.77

Typ: 0.24

Min: 0.13

1.E+00

Max: 0.22

Typ: 0.11

Min: 0.079

1.E-01

1.E-02

1.E-02

1.E-01

1.E+00

1.E+01

Frequency [MHz]

Figure 4 Typical, highest, and lowest impedance curves of the three parallel

connected capacitors shown in Figure 3

1.E+02

nent tolerances, the second anti-resonance

peak increases from 0.24 Ohms to 0.77

Ohms, a 220% increase. The contributors

to the second anti-resonance peak are the

ESR and ESL of the 1 uF capacitor, and the

C and ESR of the 0.1 uF capacitor. The sum

of the tolerances of these four parameters is

145%, but they increase the impedance at

the peak by 220%. This illustrates that the

resonance magnifies the tolerance window.

Bypass Capacitor Range

Bypass capacitors are considered to be

charge reservoir components, and common

wisdom tells you to put them close to the

active device they need to feed. We will

show here that when the capacitor and the

active device are connected with planes, the

ratio of plane impedance and ESR of

capacitor will determine the spatial gradient of impedance around the capacitor.

Even at low frequencies, the impedance

gradient can be significant.

Lets look at the self-impedance distribution over a 2 x 2 plane pair with 50 mil

plane separation. You will get this plane

separation if you have just a few layers in

the board and if they are not placed next to

each other in the stack-up. The characteristic impedance of these planes is approximately 1.7 Ohms. You can calculate the

approximate plane impedance from our

third equation [7]:

Figure 4 also shows the impedance magMHz, which represents a wavelength of 15

nitudes of the individual capacitors with

meters in FR4 PCB dielectrics. This tells us

thin lines. The three heavy lines in the figthat the lumped approximation is valid in

ure represent the maximum, typical, and

this entire frequency range, no matter

minimum values from all possible tolerance

where we place these capacitors on a typipermutations. All three curves exhibit two

cal-size PCB.

peaks: the first around 1 MHz and a secTable 1 lists the percentage tolerance

ond around 10 MHz.

ranges for the C, ESR, and ESL values

The trace representing the typical case

used in Figure 3. We calculated the

has an impedance magnitude of 0.11

impedance curves and tolerance analysis

Ohms and 0.24 Ohms at these peak frewith a simple spreadsheet [6]. The spreadquencies, respectively. Impedance at and

sheet calculates the complex impedance

resulting from the three parallel connected

around the first peak is mostly below the

532 h

Zp =

impedances. During tolerance analysis,

impedance curves of the 100 uF and 1 uF

r P

the spreadsheet steps each parameter syscapacitors. The second peak, however,

tematically though their minimum and

exceeds the lower boundary of the impedwhere Zp is the approximate plane impedmaximum values specified by the tolerance curves of the 1 uF and 0.1 uF capaciance in Ohms and h and P are the plane

ance percentage entered and accumutors by about a factor of two. This is a

separation and plane periphery, respeclates the lowest and highest magnitudes at

typical anti-resonance scenario.

tively, in the same but arbitrary units.

each frequency point.

In a worst-case combination of compoWe assume one piece of capacitor located

For Figure 4, we assume a

in the middle of the

capacitance tolerance of +-20%

planes. MLCC capacitors

C1

tol. [%]

C2

tol. [%]

C3

tol. [%]

for all three capacitors. For ESR,

are available with as much

datasheets usually state the maxas a few hundred uF

Capacitance [uF]: 100

20

1

20

0.1

20

imum value but no minimum,

capacitance in the 1210

-20

-20

-20

so we can assume a +0 to -50%

case style, and their ESR

ESR [Ohms]:

0.1

0

0.02

0

0.05

0

tolerance around the nominal

can be as low as one mil-50

-50

-50

value. ESL strongly depends on

liohm. For this example,

ESL [nH]:

10

25

3

25

0.8

25

both the capacitors construcwe use C = 100 uF, ESR =

-25

-25

-25

tion and its mounting geometry.

0.001 Ohm, ESL = 1 nH.

For this example, we assume

The SRF of this part is

+-25% inductance variation.

Table 1 Parameters used for Figure 4

0.5 MHz.

00

Xcell Journal

Summer 2004

Note that this trend does not change if

The surface plot of Figure 5 shows the

Conclusion

we have more capacitors on the board. If

variation of self-impedance magnitude

The impedance tolerance window at the

we have significantly different plane

over the plane at 0.5 MHz. The gray botanti-resonance peak of paralleled discrete

impedance and cumulative ESR of capactom area of the graph represents the top

bypass capacitors widens with higher Q

itors, the impedance gradient will be big,

view of the planes. The grid on the botcapacitors. To keep the impedance window

and we must use many capacitors to hold

tom area shows the locations where the

due to tolerances small, you need either

the impedance uniformly down over a

impedance was calculated: the granularity

many different SRF values tightly spaced

bigger area even at low frequencies.

was 0.2 inches. The logarithmic vertical

on the frequency axis, or the Qs of capaciscale shows the impedance magnitude

tors must be low.

between 1 and 10 milliohms.

Contrary to popular belief, the servSelf-Impedance Magnitude [Ohm]

We calculated the surface impedice range of low-ESR capacitors is

ance with a spreadsheet [8]. The

severely limited when connected to

macro in the spreadsheet calculates

planes of much higher impedance. But

the impedance matrix by evaluating 1.E-02

you can achieve the lowest spatial

the double series of cavity resoimpedance gradient if the cumulative

nances. It then combines the comESR of bypass capacitors is close to the

plex impedance of plane pair with

characteristic impedance of planes.

the complex impedance of the

bypass capacitor.

References

The impedance surface at 0.5

[1] Novak, I. Frequency-Domain PowerMHz has a sharp minimum in the

Distribution Measurements An Overview,

middle; here the capacitor forces its

Part I in HP-TF2, Measurement of Power

ESR value over the plane impedDistribution Networks and their Elements.

1.E-03

DesignCon East, June 23, 2003, Boston.

ance. However, as we move away

from the capacitor, the impedance

[2] Smith, L.D., R.E. Anderson, D.W.

rises very sharply. At 0.2 inches away,

Forehand, T.J. Pelc, and T. Roy. 1999. Power

the impedance is approximately

Distribution System Methodology and

Capacitor Selection for Modern CMOS

50% higher; 0.4 inches away, the

Technology. IEEE Transactions on Advanced

Figure

5

Self-impedance

at

0.5

MHz

on

a

2

x

2

impedance magnitude doubles. At

plane

pair

with

50

mils

dielectric

separation,

with

a

100

uF,

Packaging 22(3): 284-290.

the corners of the 2 x 2 plane pair,

0.001 Ohm, 1 nH capacitor located in the middle

the impedance magnitude is almost

[3] Novak, I., and J. R. Miller. FrequencyDependent Characterization of Bulk and

10 milliohms.

Self-Impedance

Magnitude

[Ohm]

Ceramic Bypass Capacitors in Proceedings of

When changing either the plane

EPEP, October 2003, Princeton, NJ.

impedance or the ESR of capacitor

so that their values are closer, the

[4] Brooks, Douglas. 2003. Signal Integrity

Issues and Printed Circuit Board Design.

variation of impedance over the

Upper Saddle River: Prentice Hall.

plane shape gets smaller. Figure 6 1.E-02

shows the impedance surface of the

[5] Ritchey, Lee W. 2003. Right the First Time,

same plane shape and same capaciA Practical Handbook on High Speed PCB

tor in the middle, except we

and System Design, Volume 1. Glen Ellen:

Speeding Edge.

increased ESR from 1 to 7 milliohms and decreased the plane sep[6] Download Microsoft Excel spreadsheet

aration from 50 to 20 mils. Now

at http://home.att.net/~istvan.novak/tools/

the impedance surface at SRF varies

bypass49.xls

only about 10% over the plane area.

[7] Novak, I., L. Noujeim, V. St. Cyr, N.

For Figures 5 and 6, you can see

Biunno, A. Patel, G. Korony, and A. Ritter.

1.E-03

the same characteristic behavior if

2002. Distributed Matched Bypasssing for

you sweep the frequency over a wider

Board-Level Power Distribution Networks.

IEEE Transactions on Advanced Packaging

frequency range in the spreadsheet.

25(2):230-243.

The impedance surface of Figure 5

changes and fluctuates significantly,

[8] Download Microsoft Excel spreadsheet at

Figure 6 Self-impedance at 0.5 MHz on a 2 x 2

while the impedance surface of

http://home.att.net/~istvan.novak/tools/

plane pair with 20 mils dielectric separation, and a 100 uF,

0.007

Ohm,

1

nH

capacitor

located

in

the

middle

Caprange_rev10.xls

Figure 6 changes less with frequency.

Summer 2004

Xcell Journal

00

Das könnte Ihnen auch gefallen

- Ds 266hsh Nsh-En 02 2011Dokument28 SeitenDs 266hsh Nsh-En 02 2011Alaa RamadanNoch keine Bewertungen

- CalculationsDokument2 SeitenCalculationskhialzadaNoch keine Bewertungen

- Dsd213 Electrical Load Calculation WorksheetDokument1 SeiteDsd213 Electrical Load Calculation WorksheetAlaa RamadanNoch keine Bewertungen

- 03192005214235Dokument0 Seiten03192005214235Daniela Buse0% (2)

- Wiring and LLDokument10 SeitenWiring and LLAlaa RamadanNoch keine Bewertungen

- 0 Electrical Load CalculationsDokument1 Seite0 Electrical Load CalculationsAlaa RamadanNoch keine Bewertungen

- 5.4. Electric Resistance ChartDokument1 Seite5.4. Electric Resistance ChartAlaa RamadanNoch keine Bewertungen

- Calculating Electric Flux Through A Disk: Page 1 of 1 Masteringphysics 2.0: Problem Print ViewDokument1 SeiteCalculating Electric Flux Through A Disk: Page 1 of 1 Masteringphysics 2.0: Problem Print ViewAlaa RamadanNoch keine Bewertungen

- Calculating Ampacity in Small-Gauge, Electrical Cables: Greig S. Latham, Member, IEEEDokument4 SeitenCalculating Ampacity in Small-Gauge, Electrical Cables: Greig S. Latham, Member, IEEEAlaa RamadanNoch keine Bewertungen

- Ladder 2010Dokument2 SeitenLadder 2010Alaa RamadanNoch keine Bewertungen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- SPIF301 SunplusDokument16 SeitenSPIF301 SunplustrutleptNoch keine Bewertungen

- 28V 3A Step-Down Switching Regulator: Power Management Features DescriptionDokument19 Seiten28V 3A Step-Down Switching Regulator: Power Management Features Descriptionteban09Noch keine Bewertungen

- Unisonic Technologies Co., LTD: Middling Voltage Fast-Switching NPN Power TransistorDokument3 SeitenUnisonic Technologies Co., LTD: Middling Voltage Fast-Switching NPN Power TransistorAnabell RodriguezNoch keine Bewertungen

- Innovative High Throw Copper Electrolytic ProcessDokument6 SeitenInnovative High Throw Copper Electrolytic Processyonathan fausaNoch keine Bewertungen

- Marcel - Dekker.protective - Relaying.theory - And.applications.2nd - Ebook TLFeBOOKDokument426 SeitenMarcel - Dekker.protective - Relaying.theory - And.applications.2nd - Ebook TLFeBOOKMahesh Singh94% (17)

- Voice Integrated Speed and Direction Control For DC MotorDokument6 SeitenVoice Integrated Speed and Direction Control For DC MotorRahul Kumar SinghNoch keine Bewertungen

- Magnetic Circuits ProblemDokument9 SeitenMagnetic Circuits ProblemBISLA ANONoch keine Bewertungen

- EMCO Compact 5 CNC Maintenance ManualDokument233 SeitenEMCO Compact 5 CNC Maintenance ManualIvanka Vanja MilenkovicNoch keine Bewertungen

- ARC5 Conversion Phil AD5XDokument9 SeitenARC5 Conversion Phil AD5XCliff MillerNoch keine Bewertungen

- PT3 - 13 - FSK Modulator PDFDokument20 SeitenPT3 - 13 - FSK Modulator PDFTempaNoch keine Bewertungen

- Notes On The Troubleshooting and Repair of Small Switchmode Power SuppliesDokument53 SeitenNotes On The Troubleshooting and Repair of Small Switchmode Power SuppliesJeremy MeyerNoch keine Bewertungen

- Euler PathDokument10 SeitenEuler PathSopno GhuriNoch keine Bewertungen

- Siei PDPDokument28 SeitenSiei PDPRoxana NegoitaNoch keine Bewertungen

- Jtag Boundary Scan PDFDokument64 SeitenJtag Boundary Scan PDFvinothsanNoch keine Bewertungen

- Reverse Phase Relay: MODEL 2532Dokument2 SeitenReverse Phase Relay: MODEL 2532mecmakNoch keine Bewertungen

- Written Report - Electrolysis SetupDokument6 SeitenWritten Report - Electrolysis SetupIbn Arqam AbdulaNoch keine Bewertungen

- Zener DiodeDokument4 SeitenZener DiodeEysha qureshiNoch keine Bewertungen

- AMP Regen Clamp SpecsheetDokument2 SeitenAMP Regen Clamp SpecsheetElectromateNoch keine Bewertungen

- The SMD Code BookDokument79 SeitenThe SMD Code BookNajam Rafi67% (3)

- 7PA26 27 30 Catalog SIP E6Dokument5 Seiten7PA26 27 30 Catalog SIP E6tduskoNoch keine Bewertungen

- Type 2Dokument7 SeitenType 2AnOnYmOuS_1995Noch keine Bewertungen

- Superposition TheoremDokument18 SeitenSuperposition TheoremShoubhik SahaNoch keine Bewertungen

- 1.converter TransformerDokument33 Seiten1.converter TransformerOrcun CalayNoch keine Bewertungen

- Converters For Electric VehicleDokument8 SeitenConverters For Electric VehicleAirton FloresNoch keine Bewertungen

- The D Flip FlopDokument7 SeitenThe D Flip FlopAlinChanNoch keine Bewertungen

- Diode Ratings - How To Understand A Diode DatasheetDokument9 SeitenDiode Ratings - How To Understand A Diode DatasheetcesarinigillasNoch keine Bewertungen

- Crowbar ProtectionDokument1 SeiteCrowbar Protectionkishan14175Noch keine Bewertungen

- Application Inspiration Office LED Lighting Interactive Guide INTDokument28 SeitenApplication Inspiration Office LED Lighting Interactive Guide INTEddy Suyono ArchitectsNoch keine Bewertungen

- Analysis of Interface Switching For NB Doped SrTiO3 Single Crystal Device Using Complex Impedance SpectrosDokument3 SeitenAnalysis of Interface Switching For NB Doped SrTiO3 Single Crystal Device Using Complex Impedance SpectrosEl Mostafa BourimNoch keine Bewertungen

- F28M35xx InfoSheet Rev1 0-09-07 11 ReleaseDokument6 SeitenF28M35xx InfoSheet Rev1 0-09-07 11 ReleaseDionisio2006Noch keine Bewertungen