Beruflich Dokumente

Kultur Dokumente

r059210202 Pulse Digital Circuits

Hochgeladen von

andhracollegesOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

r059210202 Pulse Digital Circuits

Hochgeladen von

andhracollegesCopyright:

Verfügbare Formate

www.andhracolleges.

com The Complete Information About Colleges in Andhra Pradesh

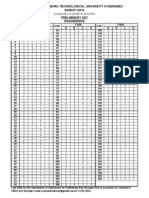

Code No: R059210202 Set No. 1

II B.Tech I Semester Regular Examinations, November 2006

PULSE & DIGITAL CIRCUITS

( Common to Electrical & Electronic Engineering, Electronics &

Communication Engineering, Electronics & Instrumentation Engineering

and Electronics & Telematics)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

www.andhracolleges.com

All Questions carry equal marks

⋆⋆⋆⋆⋆

1. (a) Explain the response of a high pass circuit to an exponential input is applied.

(b) Write short note on piping process. [8+8]

2. (a) Explain transfer characteristics of the emitter coupled clipper and derive the

necessary equations.

(b) Draw the basic circuit diagram of positive peak clamper circuit and explain

its operation. [8+8]

3. Write Short notes on:

(a) Diode switching times

(b) Switching characteristics of transistors

(c) FET as a switch. [4+8+4]

4. (a) Design a collector coupled transistor monostable multivibrator to produce a

time delay of 100 µsec. Use transistors have hF E of 250. Use ±12v sources,

www.andhracolleges.com

VCE(sat) = 0.3v, VBE(sat) = 0.7v and VBEcutof f = 0v

(b) Show that the astable multivibrator works as voltage controlled oscillator.

[10+6]

5. (a) Draw and explain the typical waveform of a time-base voltage.

(b) Explain the principle of working of exponential sweep circuit with neat circuit

diagram and also derive the equations for slope , transmission and displace-

ment error. [6+10]

6. (a) Explain the factors which influence the stability of a relaxation divider with

the help of a neat waveforms.

(b) A UJT sweep operates with Vv = 3V, Vp=16V and η=0.5. A sinusoidal

synchronizing voltage of 2V peak is applied between bases and the natural

frequency of the sweep is 1kHz, over what range of sync signal frequency will

the sweep remain in 1:1 synchronism with the sync signal? [8+8]

7. (a) What is sampling gate? Explain how it differ from Logic gates?

(b) What is pedestal? How it effects the output of a sampling gates?

(c) What are the drawbacks of two diode sampling gate? [6+6+4]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210202 Set No. 1

8. (a) What are the basic logic gates which perform almost all the operations in

Digital communication systems.

(b) Give some applications of logic gates.

(c) Define a positive and negative logic systems.

(d) Draw a pulse train representing a 11010111 in a synchronous positive logic

digital system. [4+4+4+4]

www.andhracolleges.com ⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

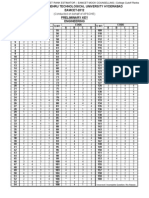

Code No: R059210202 Set No. 2

II B.Tech I Semester Regular Examinations, November 2006

PULSE & DIGITAL CIRCUITS

( Common to Electrical & Electronic Engineering, Electronics &

Communication Engineering, Electronics & Instrumentation Engineering

and Electronics & Telematics)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

www.andhracolleges.com

All Questions carry equal marks

⋆⋆⋆⋆⋆

1. (a) A square wave of 5 V amplitude with an ON time of 1 msec and an OFF time

of 3 m sec is applied to a high pass RC circuit with R = 2K and C = 0.1 µ f.

Sketch the steady state output waveform showing all the details

(b) Explain the operation of RC high pass circuit when exponential input is ap-

plied. [8+8]

2. (a) Draw the circuit diagram of slicer circuit using Zener diodes and explain its

operation with the help of its transfer characteristic.

(b) Draw the circuit diagram of emitter coupled clipper. Draw its transfer charac-

teristics indicating all intercepts, slopes and voltage levels derive the necessary

equations. [8+8]

3. (a) Sketch neatly the waveforms of current & voltages for a transistor switch with

capacitance loading circuit.

(b) What are catching diodes? [12+4]

www.andhracolleges.com

4. (a) Explain the reason for the occurrence of overshoot at the base of normally ON

transistor of one shot. Derive an expression for overshoot.

(b) Discuss a few applications of a monostable multivibrator. Explain how it

differs with that of a binary. [8+8]

5. (a) How are linearly varying current waveforms generated?

(b) In the boot strap circuit shown in figure5 Vcc = 25 V, VEE = -15 V, R = 10 K

ohms, RB = 150 K ohms, C = 0.05 µF. The gating waveform has a duration

of 300 µs. The transistor parameters are hie = 1.1Kohms, hre = 2.5 x 10−4 K

ohmshf e =50 hoe = 1/40K ohms.

i. Draw the waveform of IC1 and Vo , labeling all current and voltage levels,

ii. What is the slope error of the sweep?

iii. What is the sweep speed and the maximum value of the sweep voltage?

iv. What is the retrace time Tr for C to discharge completely?

v. Calculate the recovery time T1 for C1 to recharge completely. [6+10]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

3 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210202 Set No. 2

www.andhracolleges.com

Figure 5

6. (a) What do you mean by synchronization ?

(b) What is the condition to be met for pulse synchronization?

(c) Compare sine wave synchronization with pulse synchronization? [4+6+6]

7. (a) Draw and explain an emitter coupled bi-directional sampling gate.

(b) For the four diode gate shown in figure 7 with a divider resistance R used .

www.andhracolleges.com

Vs =25V, Rf =20 ohms, RL =RC =200K ohms and R= 100 ohms. Find Vcmin ,

A and Vnmin ? [8+8]

Figure 7

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

3 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210202 Set No. 2

8. (a) What are the basic logic gates which perform almost all the operations in

Digital communication systems.

(b) Give some applications of logic gates.

(c) Define a positive and negative logic systems.

(d) Draw a pulse train representing a 11010111 in a synchronous positive logic

digital system. [4+4+4+4]

www.andhracolleges.com ⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

3 ofUSA-UK-Australia-Germany-France-NewZealand

3 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210202 Set No. 3

II B.Tech I Semester Regular Examinations, November 2006

PULSE & DIGITAL CIRCUITS

( Common to Electrical & Electronic Engineering, Electronics &

Communication Engineering, Electronics & Instrumentation Engineering

and Electronics & Telematics)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

www.andhracolleges.com

All Questions carry equal marks

⋆⋆⋆⋆⋆

1. (a) An ideal 1 µ -Sec pulse is fed to a low pass circuit. Calculate and plot the

output waveform under the following conditions: The upper 3-dB frequency

is

i. 10 MHz

ii. .1 MHz

iii. .0.1 MHz.

(b) Explain RLC ringing circuit. [10+6]

2. (a) Design a clipping circuit with ideal components, which can give the waveform

shown in figure 2a for a sinusoidal input.

www.andhracolleges.com

capacitance loading circuit.

(b) What are catching diodes?

Figure 2a

(b) State and prove clamping circuit theorem.

4. (a) Explain the operation of Astable multivibrator with a circuit diagram with

relevant waveforms.

[8+8]

3. (a) Sketch neatly the waveforms of current & voltages for a transistor switch with

[12+4]

(b) A collector coupled monostable multi using n-p-n silicon transistor has the

following parameters Vcc = 12v, VBB = 3v, RC = 2k, R1 = R2 = R = 20k,

hF E = 30, rbb = 200 Ω and c = 1000pF. Calculate and plot to scale the wave

slopes at each base and collector. Also find width of the o/p pulse. [8+8]

5. (a) What type of Voltage input is required to obtain a linear current sweep?

(b) The transistor bootstrap circuit shown in Figure 5 has the following parame-

ters VCC = 10 V, VEE = -10V, RB = 30 K ohms, C=0.002 µF, C1 =0.25µF

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210202 Set No. 3

and CB may be taken as arbitrarily large. The input gate has an amplitude

of 1V and a width of 50µs. The transistor parameters are hF E = hf e = 60,

hie =2kohms, 1/hoe = 10 K ohms, hre = 10−4 . ICBO = 0, and the forward

biased junction voltages are negligible. The diode is ideal.

i. Plot the gate voltage, collector current iC1 , and the output voltage Vo.

ii. Evaluate the sweep speed and amplitude of the sweep at its maximum

value

www.andhracolleges.com

iii. Find time it takes to discharge C at the end of the sweep,

iv. Find peak voltage change across C1 and the time required to replace the

lost charge

v. Find slope error. [6+10]

www.andhracolleges.com Figure 5

6. (a) What do you mean by synchronization ?

(b) What is the condition to be met for pulse synchronization?

(c) Compare sine wave synchronization with pulse synchronization?

7. (a) With the help of a neat diagram, explain the working of two-diode sampling

[4+6+6]

gate.

(b) Derive expressions for gain and minimum control voltages of a bi-directional

two- diode sampling gate. [8+8]

8. (a) Draw and explain the circuit diagram of a diode AND gate for positive logic.

(b) Derive the output equation for a diode OR gate for positive logic. [8+8]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210202 Set No. 4

II B.Tech I Semester Regular Examinations, November 2006

PULSE & DIGITAL CIRCUITS

( Common to Electrical & Electronic Engineering, Electronics &

Communication Engineering, Electronics & Instrumentation Engineering

and Electronics & Telematics)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

www.andhracolleges.com

All Questions carry equal marks

⋆⋆⋆⋆⋆

1. (a) Explain double differentiator with the help of neat sketches.

(b) A limited ramp is applied to an RC differentiator. What is the peak of the

out put wave form for

i. T = RC

ii. T= 0.2RC

iii. T= 5RC. [8+8]

2. (a) State and prove clamping -circuit theorem.

(b) A clamping circuit and input wave form is shown in figure 2b calculate and

plot to scale the steady state output [8+8]

www.andhracolleges.com Figure 2b

3. (a) Describe the switching times of BJT by considering the charge distribution

across the base region. Explain this for cut-off, active and saturation region.

(b) Explain phenomenon of latching in a transistor. [12+4]

4. (a) Draw the circuit diagram of a Schmitt trigger circuit and explain its operation.

Derive the Expressions for its UTP and LTP.

(b) Explain how an Schmitt trigger circuit acts as a comparator. [12+4]

5. (a) What is a Linear time base generator? Give its Applications

(b) Write the differences between the voltage and current time base generators?

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R059210202 Set No. 4

(c) Why the time base generators are called sweep circuits? [6+6+4]

6. (a) What is relaxation oscillator? Name some negative resistance devices used as

relaxation oscillators and give its applications.

(b) With the help of a circuit diagram and waveforms, explain the frequency

division by an astable multivibrator? [8+8]

www.andhracolleges.com

7. (a) What is sampling gate? Explain how it differ from Logic gates?

(b) What is pedestal? How it effects the output of a sampling gates?

(c) What are the drawbacks of two diode sampling gate? [6+6+4]

8. (a) Why totem pole is used in DTL? Draw the circuit diagram and explain a DTL

gate with this.

(b) Verify the truth table of RTL NOR gate with the circuit diagram of two inputs.

[8+8]

⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

Das könnte Ihnen auch gefallen

- R05 EdcDokument10 SeitenR05 EdcandhracollegesNoch keine Bewertungen

- Electrical and Electronics Engineering (Com. To CE, ME, AME)Dokument7 SeitenElectrical and Electronics Engineering (Com. To CE, ME, AME)andhracollegesNoch keine Bewertungen

- r059210404 Electronic Circuit AnalysisDokument8 Seitenr059210404 Electronic Circuit AnalysisandhracollegesNoch keine Bewertungen

- r05010401 Network AnalysisDokument15 Seitenr05010401 Network AnalysisandhracollegesNoch keine Bewertungen

- 6rr320204 InstrumentationDokument8 Seiten6rr320204 InstrumentationandhracollegesNoch keine Bewertungen

- Electronic Devices and Circuits 2008 Question PaperDokument6 SeitenElectronic Devices and Circuits 2008 Question Paperelimelek100% (3)

- r07320204 InstrumentationDokument6 Seitenr07320204 InstrumentationandhracollegesNoch keine Bewertungen

- Srr320404 Microwave EngineeringDokument7 SeitenSrr320404 Microwave EngineeringandhracollegesNoch keine Bewertungen

- R05 BeeDokument8 SeitenR05 BeeandhracollegesNoch keine Bewertungen

- 07 Rr320204 InstrumentationDokument6 Seiten07 Rr320204 InstrumentationandhracollegesNoch keine Bewertungen

- rr320403 Electronic Measurements - InstrumentationDokument8 Seitenrr320403 Electronic Measurements - InstrumentationSRINIVASA RAO GANTANoch keine Bewertungen

- r07320205 Switch Gear and ProtectionDokument6 Seitenr07320205 Switch Gear and ProtectionandhracollegesNoch keine Bewertungen

- r05221101 Pulse and Digital CircuitsDokument9 Seitenr05221101 Pulse and Digital CircuitssridiviNoch keine Bewertungen

- r05220503 Principles of CommunicationsDokument7 Seitenr05220503 Principles of CommunicationsandhracollegesNoch keine Bewertungen

- r059210202 Pulse and Digital CircuitsDokument11 Seitenr059210202 Pulse and Digital CircuitsSrinivasa Rao GNoch keine Bewertungen

- r07220205 Control SystemsDokument9 Seitenr07220205 Control SystemsandhracollegesNoch keine Bewertungen

- r5100207 Electronic Devices and CircuitsDokument4 Seitenr5100207 Electronic Devices and CircuitssivabharathamurthyNoch keine Bewertungen

- Linear and Dig Italic Applications Jntu Model Paper WWW Student Yogi Com 100113195343 Phpapp02Dokument8 SeitenLinear and Dig Italic Applications Jntu Model Paper WWW Student Yogi Com 100113195343 Phpapp02Ranjith ReddyNoch keine Bewertungen

- EmDokument8 SeitenEmandhracollegesNoch keine Bewertungen

- r05310403 Antennas and Wave PropagationDokument8 Seitenr05310403 Antennas and Wave PropagationandhracollegesNoch keine Bewertungen

- r05320204 InstrumentationDokument6 Seitenr05320204 InstrumentationMounikaManuNoch keine Bewertungen

- Rr-10205-Edc Apr 2003Dokument8 SeitenRr-10205-Edc Apr 2003mpssassygirlNoch keine Bewertungen

- Google 11Dokument2 SeitenGoogle 11Suraj TiwariNoch keine Bewertungen

- R7410402 Electronic Measurements & InstrumentationDokument4 SeitenR7410402 Electronic Measurements & InstrumentationsivabharathamurthyNoch keine Bewertungen

- CTT Study Guide PDFDokument13 SeitenCTT Study Guide PDFmade_up-down65Noch keine Bewertungen

- Instrumentation exam questionsDokument6 SeitenInstrumentation exam questionsprahari7Noch keine Bewertungen

- Edc 4Dokument10 SeitenEdc 429viswa12Noch keine Bewertungen

- r05410409 Satellite CommunicationsDokument5 Seitenr05410409 Satellite CommunicationsandhracollegesNoch keine Bewertungen

- Power Systems IIIDokument8 SeitenPower Systems IIIrajaniramNoch keine Bewertungen

- 08r05310403 Antennas and Wave PropagationDokument8 Seiten08r05310403 Antennas and Wave PropagationandhracollegesNoch keine Bewertungen

- Rr410203 Computer Methods in Power SystemsDokument9 SeitenRr410203 Computer Methods in Power SystemsandhracollegesNoch keine Bewertungen

- Basicelectronicdevicesandcircuits Jntu Model Paper (WWW - Studentyogi.com)Dokument7 SeitenBasicelectronicdevicesandcircuits Jntu Model Paper (WWW - Studentyogi.com)sapabapliveNoch keine Bewertungen

- r05320204 InstrumentationDokument4 Seitenr05320204 InstrumentationSRINIVASA RAO GANTANoch keine Bewertungen

- 07a60204 - InstrumentationDokument5 Seiten07a60204 - InstrumentationMounikaManuNoch keine Bewertungen

- rr320403 Electronic Measurements and InstrumentationDokument8 Seitenrr320403 Electronic Measurements and InstrumentationSRINIVASA RAO GANTANoch keine Bewertungen

- 08rr410404 Optical CommunicationDokument8 Seiten08rr410404 Optical CommunicationandhracollegesNoch keine Bewertungen

- Rr420402 Radar EngineeringDokument4 SeitenRr420402 Radar EngineeringandhracollegesNoch keine Bewertungen

- Edc 8Dokument9 SeitenEdc 829viswa12Noch keine Bewertungen

- Pulse and Digital Circuits NotesDokument8 SeitenPulse and Digital Circuits NotesLavanya_123Noch keine Bewertungen

- RR Set No. 2Dokument8 SeitenRR Set No. 2radhakodirekka8732Noch keine Bewertungen

- r05320204 InstrumentationDokument7 Seitenr05320204 InstrumentationSRINIVASA RAO GANTANoch keine Bewertungen

- Fts 2007Dokument7 SeitenFts 2007andhracollegesNoch keine Bewertungen

- r5210203 Pulse and Digital CircuitsDokument1 Seiter5210203 Pulse and Digital CircuitssivabharathamurthyNoch keine Bewertungen

- 08 r05310404 Digital CommunicationDokument8 Seiten08 r05310404 Digital CommunicationandhracollegesNoch keine Bewertungen

- r05220405 Analog CommunicationsDokument8 Seitenr05220405 Analog CommunicationsandhracollegesNoch keine Bewertungen

- Code No: 37041/37042Dokument6 SeitenCode No: 37041/37042SRINIVASA RAO GANTANoch keine Bewertungen

- Images Eeeqp 07 - rr320205 Power Systems III PDFDokument7 SeitenImages Eeeqp 07 - rr320205 Power Systems III PDFtamann2004Noch keine Bewertungen

- WWW - Manaresults.Co - In: II B. Tech I Semester Regular Examinations, Jan - 2015 Electronic Devices and CircuitsDokument4 SeitenWWW - Manaresults.Co - In: II B. Tech I Semester Regular Examinations, Jan - 2015 Electronic Devices and CircuitsUr's Lovely NagNoch keine Bewertungen

- Ec05497 Pulse and Digital CircuitsDokument1 SeiteEc05497 Pulse and Digital CircuitssivabharathamurthyNoch keine Bewertungen

- Sr05220205 Control SystemsDokument8 SeitenSr05220205 Control SystemsandhracollegesNoch keine Bewertungen

- r5100406 Network AnalysisDokument4 Seitenr5100406 Network AnalysissivabharathamurthyNoch keine Bewertungen

- Measurement Instruments Exam QuestionsDokument5 SeitenMeasurement Instruments Exam QuestionsNamanNoch keine Bewertungen

- Lsa r07Dokument8 SeitenLsa r07andhracollegesNoch keine Bewertungen

- 07a70206 HighvoltageengineeringDokument4 Seiten07a70206 HighvoltageengineeringSamiullah MohammedNoch keine Bewertungen

- 07a1ec06-Electronic Devices and Ckts.Dokument7 Seiten07a1ec06-Electronic Devices and Ckts.SRINIVASA RAO GANTANoch keine Bewertungen

- Ac 1Dokument8 SeitenAc 1andhracollegesNoch keine Bewertungen

- EcaDokument11 SeitenEcaandhracollegesNoch keine Bewertungen

- Electronics Explained: Fundamentals for Engineers, Technicians, and MakersVon EverandElectronics Explained: Fundamentals for Engineers, Technicians, and MakersBewertung: 5 von 5 Sternen5/5 (5)

- Differential Forms on Electromagnetic NetworksVon EverandDifferential Forms on Electromagnetic NetworksBewertung: 4 von 5 Sternen4/5 (1)

- Eamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 CutoffsDokument3 SeitenEamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 Cutoffsandhracolleges33% (3)

- Polycet 2014 SC BC Oc Certificatates Verification DatesDokument1 SeitePolycet 2014 SC BC Oc Certificatates Verification DatesandhracollegesNoch keine Bewertungen

- Polycet2014 Web Counselling NotificationDokument2 SeitenPolycet2014 Web Counselling NotificationandhracollegesNoch keine Bewertungen

- JEE Main Advanced Paper I Answer Key 25 May 2014Dokument1 SeiteJEE Main Advanced Paper I Answer Key 25 May 2014andhracollegesNoch keine Bewertungen

- JEE Main Advanced 2014 Paper I Maths Paper Answer SolutionsDokument4 SeitenJEE Main Advanced 2014 Paper I Maths Paper Answer Solutionsandhracolleges100% (1)

- Polycet 2014 ST Certificatates Verification DatesDokument1 SeitePolycet 2014 ST Certificatates Verification DatesandhracollegesNoch keine Bewertungen

- ICET 2014 Preliminary Key Primary Key AndhracollegesDokument2 SeitenICET 2014 Preliminary Key Primary Key AndhracollegesandhracollegesNoch keine Bewertungen

- JEE Advanced 2014 Paper I Chemistry Paper Answer SolutionsDokument4 SeitenJEE Advanced 2014 Paper I Chemistry Paper Answer SolutionsandhracollegesNoch keine Bewertungen

- Andhracollege Eamcet 2014 Engineering Question Paper With Key SolutionsDokument62 SeitenAndhracollege Eamcet 2014 Engineering Question Paper With Key Solutionsandhracolleges50% (4)

- Eamcet 2014 Engineering Jntu Preliminary Key AndhracollegesDokument1 SeiteEamcet 2014 Engineering Jntu Preliminary Key AndhracollegesandhracollegesNoch keine Bewertungen

- JEE Advanced 2014 Paper I PHYSICS Paper Answer SolutionsDokument6 SeitenJEE Advanced 2014 Paper I PHYSICS Paper Answer SolutionsandhracollegesNoch keine Bewertungen

- Eamcet 2014 Engineering Key SolutionsDokument42 SeitenEamcet 2014 Engineering Key Solutionsandhracolleges100% (1)

- Eamcet 2014 Medical Question Paper With Key Solutions AndhracollegesDokument62 SeitenEamcet 2014 Medical Question Paper With Key Solutions Andhracollegesandhracolleges100% (1)

- EAMCET 2014 Agriculture & Medical Preliminary Answer KeysDokument1 SeiteEAMCET 2014 Agriculture & Medical Preliminary Answer KeysLohith_EnggNoch keine Bewertungen

- Eamcet 2014 Engineering Key Solutions AndhracollegesDokument42 SeitenEamcet 2014 Engineering Key Solutions Andhracollegesandhracolleges75% (8)

- Eamcet 2012 Medical PaperDokument60 SeitenEamcet 2012 Medical Paperandhracolleges100% (1)

- Eamcet 2014 Medical Question Paper AndhracollegesDokument62 SeitenEamcet 2014 Medical Question Paper Andhracollegesandhracolleges100% (1)

- Polycet 2014 Question PaperDokument24 SeitenPolycet 2014 Question PaperandhracollegesNoch keine Bewertungen

- Eamcet 2013 Medical PaperDokument62 SeitenEamcet 2013 Medical PaperandhracollegesNoch keine Bewertungen

- Eamcet 2012 Engineering Paper KeyDokument1 SeiteEamcet 2012 Engineering Paper KeyandhracollegesNoch keine Bewertungen

- Eamcet 2013 Engineering PaperDokument62 SeitenEamcet 2013 Engineering Paperandhracolleges0% (1)

- Eamcet 2008 Engineering PaperDokument62 SeitenEamcet 2008 Engineering PaperandhracollegesNoch keine Bewertungen

- Eamcet 2011 Engineering PaperDokument61 SeitenEamcet 2011 Engineering PaperandhracollegesNoch keine Bewertungen

- Eamcet 2012 Medical Paper KeyDokument1 SeiteEamcet 2012 Medical Paper KeyandhracollegesNoch keine Bewertungen

- Eamcet 2012 Engineering Paper KeyDokument1 SeiteEamcet 2012 Engineering Paper KeyandhracollegesNoch keine Bewertungen

- Eamcet 2012 Engineering PaperDokument62 SeitenEamcet 2012 Engineering Paperandhracolleges100% (1)

- Eamcet 2010 Medical PaperDokument63 SeitenEamcet 2010 Medical PaperandhracollegesNoch keine Bewertungen

- Eamcet 2007 Engineering PaperDokument13 SeitenEamcet 2007 Engineering Paperandhracolleges100% (1)

- Eamcet 2009 Engineering Chemistry PaperDokument16 SeitenEamcet 2009 Engineering Chemistry PaperandhracollegesNoch keine Bewertungen

- Eamcet 2006 Engineering PaperDokument14 SeitenEamcet 2006 Engineering PaperandhracollegesNoch keine Bewertungen