Beruflich Dokumente

Kultur Dokumente

Hoja Caracteristicas 7476

Hochgeladen von

GroplyCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Hoja Caracteristicas 7476

Hochgeladen von

GroplyCopyright:

Verfügbare Formate

Revised July 2001

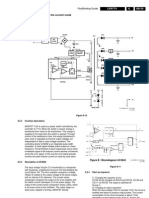

DM7476

Dual Master-Slave J-K Flip-Flops with

Clear, Preset, and Complementary Outputs

General Description

This device contains two independent positive pulse triggered J-K flip-flops with complementary outputs. The J and

K data is processed by the flip-flop after a complete clock

pulse. While the clock is LOW the slave is isolated from the

master. On the positive transition of the clock, the data

from the J and K inputs is transferred to the master. While

the clock is HIGH the J and K inputs are disabled. On the

negative transition of the clock, the data from the master is

transferred to the slave. The logic state of J and K inputs

must not be allowed to change while the clock is HIGH.

The data is transferred to the outputs on the falling edge of

the clock pulse. A LOW logic level on the preset or clear

inputs will set or reset the outputs regardless of the logic

levels of the other inputs.

Ordering Code:

Order Number

DM7476N

Package Number

N16E

Package Description

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Connection Diagram

Function Table

Inputs

Outputs

PR

CLR

CLK

H

H

(Note 1) (Note 1)

Q0

Q0

L

Toggle

H = HIGH Logic Level

L = LOW Logic Level

X = Either LOW or HIGH Logic Level

= Positive pulse data. The J and K inputs must be held constant while

the clock is HIGH. Data is transferred to the outputs on the falling

edge of the clock pulse.

Q0 = The output logic level before the indicated input conditions were

established.

Toggle = Each output changes to the complement of its previous level on

each complete active HIGH level clock pulse.

Note 1: This configuration is nonstable; that is, it will not persist when the

preset and/or clear inputs return to their inactive (HIGH) level.

2001 Fairchild Semiconductor Corporation

DS006528

www.fairchildsemi.com

DM7476 Dual Master-Slave J-K Flip-Flops with Clear, Preset, and Complementary Outputs

September 1986

DM7476

Absolute Maximum Ratings(Note 2)

Supply Voltage

Note 2: The Absolute Maximum Ratings are those values beyond which

the safety of the device cannot be guaranteed. The device should not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The Recommended Operating Conditions table will define the conditions

for actual device operation.

7V

Input Voltage

5.5V

0C to +70C

Operating Free Air Temperature Range

65C to +150 C

Storage Temperature Range

Recommended Operating Conditions

Symbol

Parameter

Min

Nom

Max

4.75

5.25

Units

VCC

Supply Voltage

VIH

HIGH Level Input Voltage

VIL

LOW Level Input Voltage

0.8

IOH

HIGH Level Output Current

0.4

mA

IOL

LOW Level Output Current

fCLK

Clock Frequency (Note 3)

tW

Pulse Width

Clock HIGH

20

(Note 3)

Clock LOW

47

Preset LOW

25

Clear LOW

16

mA

15

MHz

ns

25

tSU

Input Setup Time (Note 3)(Note 4)

tH

Input Hold Time (Note 3)(Note 4)

TA

Free Air Operating Temperature

ns

ns

70

Note 3: TA = 25C and V CC = 5V.

Note 4: The symbol (, ) indicates the edge of the clock pulse is used for reference () for rising edge, () for falling edge.

Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

Symbol

Parameter

Conditions

VI

Input Clamp Voltage

VCC = Min, II = 12 mA

VOH

HIGH Level

VCC = Min, IOH = Max

Output Voltage

VIL = Max, VIH = Min

LOW Level

VCC = Min, IOL = Max

Output Voltage

VIH = Min, VIL = Max

VOL

Min

2.4

Typ

(Note 5)

Max

Units

1.5

3.4

0.2

V

0.4

mA

II

Input Current @ Max Input Voltage VCC = Max, VI = 5.5V

IIH

HIGH Level

VCC = Max

J, K

40

Input Current

VI = 2.4V

Clock

80

Clear

80

Preset

80

IIL

LOW Level

VCC = Max

J, K

1.6

Input Current

VI = 0.4V

Clock

3.2

(Note 6)

Clear

3.2

Preset

3.2

IOS

Short Circuit Output Current

VCC = Max (Note 7)

ICC

Supply Current

VCC = Max (Note 8)

18

18

mA

34

mA

Note 6: Clear is measured with preset HIGH and preset is measured with clear HIGH.

Note 7: Not more than one output should be shorted at a time.

Note 8: With all outputs OPEN, ICC is measured with the Q and Q outputs HIGH in turn. At the time of measurement the clock input is grounded.

mA

55

Note 5: All typicals are at VCC = 5V, TA = 25C.

www.fairchildsemi.com

at VCC = 5V and TA = 25C

Symbol

Parameter

From (Input)

To (Output)

fMAX

Maximum Clock Frequency

tPHL

Propagation Delay Time

HIGH-to-LOW Level Output

tPLH

Propagation Delay Time

LOW-to-HIGH Level Output

tPHL

Propagation Delay Time

HIGH-to-LOW Level Output

tPLH

Propagation Delay Time

LOW-to-HIGH Level Output

tPHL

Propagation Delay Time

HIGH-to-LOW Level Output

tPLH

Propagation Delay Time

LOW-to-HIGH Level Output

RL = 400, CL = 15 pF

Min

Units

Max

15

MHz

Preset to Q

40

ns

Preset to Q

25

ns

Clear to Q

40

ns

Clear to Q

25

ns

Clock to Q or Q

40

ns

Clock to Q or Q

25

ns

www.fairchildsemi.com

DM7476

Switching Characteristics

DM7476 Dual Master-Slave J-K Flip-Flops with Clear, Preset, and Complementary Outputs

Physical Dimensions inches (millimeters) unless otherwise noted

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Package Number N16E

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and

Fairchild reserves the right at any time without notice to change said circuitry and specifications.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

2. A critical component in any component of a life support

device or system whose failure to perform can be reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the

user.

www.fairchildsemi.com

www.fairchildsemi.com

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

Das könnte Ihnen auch gefallen

- PCM ProjectDokument7 SeitenPCM Projectsuresh NamgiriNoch keine Bewertungen

- ASK2Dokument5 SeitenASK2Tala JaberNoch keine Bewertungen

- Lab1 VHDLDokument9 SeitenLab1 VHDLGautam GowdaNoch keine Bewertungen

- Arc Uhp MW XX 4 DatasheetDokument6 SeitenArc Uhp MW XX 4 DatasheetJose VazNoch keine Bewertungen

- Clase 17 Diseño Por Medio Del LGR PIDDokument46 SeitenClase 17 Diseño Por Medio Del LGR PIDCristhian RamosNoch keine Bewertungen

- TL074 Datasheet Op - AmpDokument15 SeitenTL074 Datasheet Op - Ampsergio_741Noch keine Bewertungen

- Tutorial 7Dokument9 SeitenTutorial 7tutulkarNoch keine Bewertungen

- Design Task 1 Final LabDokument15 SeitenDesign Task 1 Final Labrazorblademk2Noch keine Bewertungen

- 1.3.1.3 Packet Tracer - Skills Integration ChallengeDokument4 Seiten1.3.1.3 Packet Tracer - Skills Integration ChallengeBryan GualotoNoch keine Bewertungen

- VHDL Implementation of A Mips-32 Pipeline ProcessorDokument5 SeitenVHDL Implementation of A Mips-32 Pipeline Processorfatima kishwar abidNoch keine Bewertungen

- EML 5311 Project 28 April Ramin ShamshiriDokument33 SeitenEML 5311 Project 28 April Ramin ShamshiriRedmond R. ShamshiriNoch keine Bewertungen

- Previo 2AmplificacionS MGSDokument5 SeitenPrevio 2AmplificacionS MGSmartin gonzalezNoch keine Bewertungen

- Bascom and AVR, EncodersDokument5 SeitenBascom and AVR, Encodersulil amriNoch keine Bewertungen

- PID ModesTraining LabVoltDokument34 SeitenPID ModesTraining LabVoltRiccardo VianelloNoch keine Bewertungen

- 8251A USART - Programmable Communication InterfaceDokument15 Seiten8251A USART - Programmable Communication InterfaceselvaNoch keine Bewertungen

- MX25L4005APC - Macronix International BIOSDokument44 SeitenMX25L4005APC - Macronix International BIOSRyosuke RaijiNoch keine Bewertungen

- Adc0808 and 8253Dokument35 SeitenAdc0808 and 8253Avanish NiranjanNoch keine Bewertungen

- Experiment No.3 Carry Lookahead Adders: Computer EngineeringDokument7 SeitenExperiment No.3 Carry Lookahead Adders: Computer EngineeringIn Fee Knee TeaNoch keine Bewertungen

- Section PL7-1 LanguageDokument27 SeitenSection PL7-1 LanguageTalyson AlexandreNoch keine Bewertungen

- Scope Fundamentals For EE StudentsDokument29 SeitenScope Fundamentals For EE StudentsAugustin GireadaNoch keine Bewertungen

- ELT50 ELR50: User and Technical ManualDokument96 SeitenELT50 ELR50: User and Technical ManualRogerNoch keine Bewertungen

- 07 Microondas Tarea01Dokument6 Seiten07 Microondas Tarea01Michel OlveraNoch keine Bewertungen

- Implementation of Digital Lock Using VHDLDokument13 SeitenImplementation of Digital Lock Using VHDLVaibhav TripathiNoch keine Bewertungen

- TO Cryptography: StanoyevitchDokument7 SeitenTO Cryptography: StanoyevitchRamziNoch keine Bewertungen

- Lab 11 DAC and ADC Full PackageDokument5 SeitenLab 11 DAC and ADC Full PackageLoveWorldCanadaNoch keine Bewertungen

- Jeopardy 2 - 03 Dynamic Routing ProtocolsDokument33 SeitenJeopardy 2 - 03 Dynamic Routing ProtocolsPablo V SalazarNoch keine Bewertungen

- Signals & Systems - Chapter 4: T U e eDokument14 SeitenSignals & Systems - Chapter 4: T U e eAlgerian AissaouiNoch keine Bewertungen

- Datasheet 74hc45Dokument10 SeitenDatasheet 74hc45aleallenderNoch keine Bewertungen

- Interfacing Programs For 8085Dokument37 SeitenInterfacing Programs For 8085archankumarturagaNoch keine Bewertungen

- A 8bit Sequential MultiplierDokument6 SeitenA 8bit Sequential MultiplierJyoti TeliNoch keine Bewertungen

- Manual Diseno Antena YaguiDokument9 SeitenManual Diseno Antena YaguiJorgeNoch keine Bewertungen

- PIC Microcontrollers Have 10 BIT ADCDokument4 SeitenPIC Microcontrollers Have 10 BIT ADCveerakumarsNoch keine Bewertungen

- Power Transistor Array STA463C: Absolute Maximum Ratings Electrical Characteristics External DimensionsDokument1 SeitePower Transistor Array STA463C: Absolute Maximum Ratings Electrical Characteristics External DimensionsAntony TorrezNoch keine Bewertungen

- ALU 74181 SpecificationDokument1 SeiteALU 74181 SpecificationDražen BorčićNoch keine Bewertungen

- TDA7442 TDA7442D: Tone Control and Surround Digitally Controlled Audio ProcessorDokument17 SeitenTDA7442 TDA7442D: Tone Control and Surround Digitally Controlled Audio ProcessormochuraNoch keine Bewertungen

- Datasheet Diodo SMD Ss54Dokument2 SeitenDatasheet Diodo SMD Ss54JUSTSOLUTIONSMXNoch keine Bewertungen

- Electronics - and - Telecommunications - Noise, F R CONNOR PDFDokument143 SeitenElectronics - and - Telecommunications - Noise, F R CONNOR PDFAjay VarmaNoch keine Bewertungen

- Power One Model SLI-48-115 Data SheetDokument5 SeitenPower One Model SLI-48-115 Data SheetshartsellNoch keine Bewertungen

- Data Sheet Antenas AndrewDokument13 SeitenData Sheet Antenas AndrewCarlos León PalominoNoch keine Bewertungen

- Model Three ManualDokument86 SeitenModel Three ManualMarjan Stojanovski100% (1)

- Amplitude Shift Keying Modulator DemodulatorDokument10 SeitenAmplitude Shift Keying Modulator DemodulatorSandi M MNoch keine Bewertungen

- PHILIPS CDR775 - AlimentaciónDokument10 SeitenPHILIPS CDR775 - Alimentaciónvideoson100% (1)

- LTSpiceDokument21 SeitenLTSpicedellxps3941Noch keine Bewertungen

- LAb 1Dokument8 SeitenLAb 1nazmyNoch keine Bewertungen

- Quanser Coupled Tanks Modeling and Parameter PDFDokument7 SeitenQuanser Coupled Tanks Modeling and Parameter PDFAnonymous rTRz30fNoch keine Bewertungen

- User Configuration Manual Digital Relay ICS-W0813A V1Dokument17 SeitenUser Configuration Manual Digital Relay ICS-W0813A V1Diego NavarreteNoch keine Bewertungen

- Robotprojects Ver7.5.4Dokument203 SeitenRobotprojects Ver7.5.4Adel AshyapNoch keine Bewertungen

- Ejercicios Del Capitulo Reaimentacion de Analysis and Design of Analog Integrated Circuits, Gray-Meyer, 5th EditionDokument3 SeitenEjercicios Del Capitulo Reaimentacion de Analysis and Design of Analog Integrated Circuits, Gray-Meyer, 5th Editionkerusacba_2011Noch keine Bewertungen

- RP Jain Adc DacDokument27 SeitenRP Jain Adc DacAnand SinghNoch keine Bewertungen

- Amplitude Shift Keying (ASK) Modulation MATLAB Simulation: C Amp. Sin (2 Pi FC T) % For Generating Carrier Sine WaveDokument6 SeitenAmplitude Shift Keying (ASK) Modulation MATLAB Simulation: C Amp. Sin (2 Pi FC T) % For Generating Carrier Sine WaveAbdullah Al Mamun ParvezNoch keine Bewertungen

- Introduction To High Frequency Hybrid Pi or Giacoletto Model of BJTDokument2 SeitenIntroduction To High Frequency Hybrid Pi or Giacoletto Model of BJTSai Sadiq100% (1)

- AQH2223 DatasheetDokument6 SeitenAQH2223 DatasheetleonttiNoch keine Bewertungen

- Presentation PDFDokument17 SeitenPresentation PDFvinodNoch keine Bewertungen

- 8255Dokument34 Seiten8255Manjula Bn100% (1)

- Foxboro 823DPDokument3 SeitenFoxboro 823DPMaria TipantuñaNoch keine Bewertungen

- Hoja Caracteristicas 7476Dokument5 SeitenHoja Caracteristicas 7476Hardian SyaputraNoch keine Bewertungen

- DM7473 Dual Master-Slave J-K Flip-Flops With Clear and Complementary OutputsDokument4 SeitenDM7473 Dual Master-Slave J-K Flip-Flops With Clear and Complementary OutputsAbhishek VishwakarmaNoch keine Bewertungen

- 74LS109Dokument5 Seiten74LS109ЭРекиNoch keine Bewertungen

- DM7474 PDFDokument5 SeitenDM7474 PDFRaffi SkNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- AssignmentDokument9 SeitenAssignmentRazi BaigNoch keine Bewertungen

- B28 VivaDokument27 SeitenB28 VivashubhamNoch keine Bewertungen

- Medical Laboratory Technology Journal: Kadar Vitamin C Jeruk Sunkist Peras Dan Infused WaterDokument5 SeitenMedical Laboratory Technology Journal: Kadar Vitamin C Jeruk Sunkist Peras Dan Infused WaterlinggaNoch keine Bewertungen

- 7 Market EquilibriumDokument4 Seiten7 Market EquilibriumAdeeba iqbalNoch keine Bewertungen

- Universal Law of GravitationDokument17 SeitenUniversal Law of GravitationScionNoch keine Bewertungen

- 4july BookDokument5 Seiten4july BookDevansh AggarwalNoch keine Bewertungen

- How Microprocessors Work PDFDokument2 SeitenHow Microprocessors Work PDFdanielconstantin4Noch keine Bewertungen

- DPP 01 Periodic Table JH Sir-3576 PDFDokument5 SeitenDPP 01 Periodic Table JH Sir-3576 PDFChessNoch keine Bewertungen

- Condensation and BoilingDokument14 SeitenCondensation and BoilingCrislyn Akilit Bayawa100% (1)

- Caliper Xy MemoryDokument6 SeitenCaliper Xy MemoryA MuNoch keine Bewertungen

- Post Hoc Test in ANOVADokument17 SeitenPost Hoc Test in ANOVAJelly Jean PayeNoch keine Bewertungen

- Mitchell-Banki Turbine Design Document PDFDokument37 SeitenMitchell-Banki Turbine Design Document PDFprojetosschillingNoch keine Bewertungen

- 1.basic Electrical Engineering Lecture Part-1Dokument17 Seiten1.basic Electrical Engineering Lecture Part-1jimvalenciaNoch keine Bewertungen

- Chapter 11Dokument53 SeitenChapter 11Vijendhar ReddyNoch keine Bewertungen

- Code Division DuplexingDokument19 SeitenCode Division DuplexingNitin SakpalNoch keine Bewertungen

- Understanding The Use of Ofdm in Ieee 802.16 (Wimax) : Roberto SacchiDokument8 SeitenUnderstanding The Use of Ofdm in Ieee 802.16 (Wimax) : Roberto SacchiHarald KerresNoch keine Bewertungen

- (Ibps-Spl) It-Specialist Officer Previous Question Papers From 2012 and 2013 Exam Professional Knowledge Information Technology Section McqsDokument18 Seiten(Ibps-Spl) It-Specialist Officer Previous Question Papers From 2012 and 2013 Exam Professional Knowledge Information Technology Section McqsshashankniecNoch keine Bewertungen

- Mothballing Requires More Than Idle ThoughtDokument4 SeitenMothballing Requires More Than Idle Thoughtfawmer61Noch keine Bewertungen

- Upcoming: Advisor Webcast: Oracle Database Resource ManagerDokument41 SeitenUpcoming: Advisor Webcast: Oracle Database Resource ManagerLayne MoránNoch keine Bewertungen

- Purified Water Specification From European Pharmacopoeia Edition 8Dokument3 SeitenPurified Water Specification From European Pharmacopoeia Edition 8puut100% (1)

- The Whys and Wherefores of Microphone Array Crosstalk in Multichannel Microphone Array DesignDokument6 SeitenThe Whys and Wherefores of Microphone Array Crosstalk in Multichannel Microphone Array DesignmewarulesNoch keine Bewertungen

- HVSI804T WGD 83Dokument6 SeitenHVSI804T WGD 83mnezamiNoch keine Bewertungen

- Summative Test in Grade 10 Science PDF FreeDokument2 SeitenSummative Test in Grade 10 Science PDF FreeMalyn ReyesNoch keine Bewertungen

- Physics XIDokument13 SeitenPhysics XIArokiaraj RajNoch keine Bewertungen

- Beration of LightDokument7 SeitenBeration of LightAnonymous i71HvPXNoch keine Bewertungen

- IIEE La Union Harmonics AnalysisDokument128 SeitenIIEE La Union Harmonics AnalysisCarlnagum 123456789Noch keine Bewertungen

- Science 3 PDFDokument12 SeitenScience 3 PDFJelyn CandoNoch keine Bewertungen

- Haaland EquationDokument1 SeiteHaaland EquationAmir AzmiNoch keine Bewertungen

- Math 9 Textbook AnswersDokument43 SeitenMath 9 Textbook AnswersMehak GillNoch keine Bewertungen

- Piaggio X8 250 I.E. (EN)Dokument289 SeitenPiaggio X8 250 I.E. (EN)Manualles100% (8)