Beruflich Dokumente

Kultur Dokumente

Combinational Logic

Hochgeladen von

Pranjul SachanCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Combinational Logic

Hochgeladen von

Pranjul SachanCopyright:

Verfügbare Formate

EE 414 Introduction to VLSI Design

CMOS Combinational Logic

Module #6 Combinational Logic

CMOS Combinational Logic

- combinational logic refers to circuits with 2 or more inputs and 1 output

Agenda

- the output depends on the combination of the input values

- we describe the logic operation of a circuit using truth tables

1. Combinational Logic

- from this, we can find a minimal Sum of Products expression using K-maps

- n-Input Gates & Equivalent Inverter

- AOI/OAI Logic Synthesis

- Transmission Gates

- Layout of Complex Logic

- once we have a logic expression, we then move into the transistor-level implementation stage

Announcements

1. Read Chapter 7

EELE 414 Introduction to VLSI Design

Module #6

Page 1

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

Module #6

Page 2

CMOS Combinational Logic

CMOS Basic Gates

- in CMOS, we always have:

CMOS 2-Input NOR Gate

- the truth table for a 2-input NOR gate is:

- a pull-up network using PMOS transistors

- a pull-down network using NMOS transistors

- the pull-up and pull-down networks are configured in a complementary topology

- the complementary topology guarantees that when driving a 1, the pull-up network is ON

and the pull-down network is OFF

- it also guarantees that when driving a 0, the pull-up network is OFF

and the pull-down network is ON

- circuit topology gives us the ability to design logic functionality where transistors:

- in series = an ANDing function

- in parallel = an ORing function

EELE 414 Introduction to VLSI Design

Module #6

Page 3

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

Module #6

Page 4

CMOS Combinational Logic

CMOS 2-Input NOR Gate

PMOS Pull-Up Network

CMOS 2-Input NOR Gate

- the transistor level implementation for the NOR gate is:

- The only time the pull-up network drives the output is when we have two 0s on the inputs.

- Since the pull-up network uses PMOS transistors (0=ON), we can say that the pull-up

network is conducting if VA AND VB are 0.

- This implies a series configuration in the pull-up (PMOS) network.

NMOS Pull-Down Network

- The pull-down network is continually driving the output unless VA AND VB are 0.

- Since the pull-down network uses NMOS transistors (1=ON), we can say that the pull-down

network is conducting if VA OR VB are 1.

- This implies a parallel configuration in the pull-down (NMOS) network.

EELE 414 Introduction to VLSI Design

Module #6

Page 5

EELE 414 Introduction to VLSI Design

Module #6

Page 6

CMOS Combinational Logic

CMOS Combinational Logic

CMOS 2-Input NOR Gate

- we have already derived expressions for how to find the critical voltages for an inverter

CMOS 2-Input NOR Gate

- we can model a 2-Input NOR gate as an equivalent inverter as follows:

- of specific interest is Vth, which we can adjust with the sizing of the transistors

- in order to analyze a more complex logic gate, we convert it into an equivalent inverter

Transistors in Series

- conceptually, the current flowing in series transistors needs to go through two channels,

each with an equivalent resistance (or transconductance k)

- with the effective resistance doubling, we can say that the transconductance (or the

ability to drive a current given an input voltage) is divided by 2

- transistors in series with the same size can be modeled as an equivalent transistor with keq=k/2

Transistors in Parallel

- lets use representative voltages of VDD=5v and Vth=2.5 to illustrate the derivation

- conceptually, the current flowing in parallel transistors can conduct twice the amount of current

compared to a a single transistor with the same gate voltage.

- we can model this behavior with an equivalent transistor with keq=2k

EELE 414 Introduction to VLSI Design

Module #6

Page 7

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

Module #6

Page 8

CMOS Combinational Logic

CMOS 2-Input NOR Gate

- we can derive the switching threshold by stating that:

CMOS 2-Input NOR Gate

- now we look at the PMOS network, which has a +2.5v drop across it.

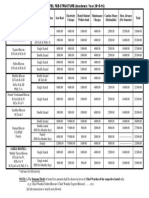

Vin Vout VA VB Vth

- since both transistors are ON, we can estimate that ~1.25v drops across each transistor:

VDS ,M 3 VDS ,M 4 1.25v

- we can begin by writing the KCL equation at the Vout node:

I D,nnetwork I D, p network

- looking at M3, we know that VGS,p|M3= -2.5v and VDS,p|M3= -1.25v so M3 is in the linear region.

- for the NMOS, since VGS,n=VDS,n, we know what both transistors are in saturation

- looking at M4, the node between M3 and M4 is estimated to be at ~3.75 (i.e., 5v 1.25v)

- in addition, we can state that the current at the Vout node is the combination of both NMOS currents

- this puts VDS,p|M4= -1.25v and VGS,p|M4= -1.25v, which means M4 is in the saturation region.

I D ,n network 2 I D ,n|sat

1

2

2

I D ,n network 2 k n Vth VT ,n k n Vth VT ,n

2

- rearranging this equation to get in terms of Vth, we have:

I D ,n network

Vth VT ,n

kn

EELE 414 Introduction to VLSI Design

Module #6

Page 9

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

CMOS Combinational Logic

CMOS 2-Input NOR Gate

- since we know the regions of operation for M3 and M4, we can write:

1

2

I DS ,3|lin k p 2 VGS , p VT , p VDS , p VDS

,p

2

CMOS 2-Input NOR Gate

- M4 is in the saturation region so we can write the current as:

1

I DS , 4|sat k p VGS , p VT , p

2

- Since the PMOS current is expressed terms of IDS, we can rewrite this as:

- Again, the PMOS current can be rewritten as:

I DS ,n I SD, p I DS , p

I DS ,n I SD, p I DS , p

- we know that for M3, VGS,p = Vth-VDD. substituting this in and carrying the (-) through, in we get:

1

2

I SD,3|lin I DS ,3|lin k p 2 Vth VDD VT , p VDS , p VDS

,p

2

1

2

I SD,3|lin k p 2 VDD Vth VT , p VSD, p VSD

,p

2

Module #6

Page 10

- we know that for M4:

VGS , p|M 4 Vth (VDD VSD3 )

VDS , p|M 4 Vth (VDD VSD3 )

- which gives the M4 current as:

1

2

I SD, 4|sat I DS , 4|sat k p Vth VDD VSD3 VT , p

2

2

1

I SD, 4|sat k p VDD Vth VT , p VSD3

2

EELE 414 Introduction to VLSI Design

Module #6

Page 11

EELE 414 Introduction to VLSI Design

Module #6

Page 12

CMOS Combinational Logic

CMOS Combinational Logic

CMOS 2-Input NOR Gate

- Now we can relate the drain currents knowing that ID3=ID4=ID,n giving a a 2nd equation relating Vth to ID:

VDD Vth VT , p 2

CMOS 2-Input NOR Gate

- in an equivalent inverter model, to get Vth=VDD/2, we can use:

ID

kp

kR

- combining this with our previous expression we get:

VT ,n

Vth ( NOR2)

1 1

VDD | VT , p |

2 kR

1

- or

VT ,n

Vth ( NOR2)

k p 4 kn

1 1

2 kR

- note that the PMOS series network has to be sized larger in

order to overcome the voltage drop across each stage.

1

VDD | VT , p |

4 kR

1

1

4 kR

EELE 414 Introduction to VLSI Design

Module #6

Page 13

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

kn

2 kn

1

kp

kp

2

Module #6

Page 14

CMOS Combinational Logic

CMOS N-Input NOR Gate

- to expand the NOR gate to N-inputs,

CMOS N-Input NOR Gate

- our Vth expression for an N-input NOR gate becomes:

- add more PMOS transistors in series in the Pull-up Network

- add more NMOS transistors in parallel in the Pull-down Network

VT ,n

Vth ( NOR)

1

N

1

VDD VT , p

kR

1

N

1

kR

- and our rule of thumb for an ideal symmetric equivalent inverter becomes:

Output

kn

N kn

1

kp

kp

N

k p N 2 kn

kR

GND

GND

EELE 414 Introduction to VLSI Design

Module #6

Page 15

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

Module #6

Page 16

CMOS Combinational Logic

CMOS N-Input NOR Gate

CMOS 2-Input NOR Gate Layout

- an equivalent network for series-connected

transistors with the same sizes:

L equivalent

1

1

L N

- an equivalent network for parallel-connected

transistors with the same sizes:

W

W

L equivalent

L N

EELE 414 Introduction to VLSI Design

Module #6

Page 17

EELE 414 Introduction to VLSI Design

Module #6

Page 18

CMOS Combinational Logic

CMOS Combinational Logic

CMOS 2-Input NAND Gate

CMOS 2-Input NAND Gate

- the truth table for a 2-input NAND gate is:

PMOS Pull-Up Network

- The pull-up network is continually driving the output unless VA AND VB are 1.

- Since the pull-up network uses PMOS transistors (0=ON), we can say that the pull-up

network is conducting if VA OR VB are 0.

- This implies a parallel configuration in the pull-up (PMOS) network.

NMOS Pull-Down Network

- The only time the pull-down network drives the output is when we have two 1s on the inputs

- This means the pull-down network is conducting only when VA AND VB are 1.

- This implies a series configuration in the pull-down (NMOS) network.

EELE 414 Introduction to VLSI Design

Module #6

Page 19

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

CMOS Combinational Logic

CMOS 2-Input NAND Gate

- the transistor level implementation for the NAND gate is:

EELE 414 Introduction to VLSI Design

Module #6

Page 21

EELE 414 Introduction to VLSI Design

- the switching threshold for the 2-input NAND gate is:

VT ,n 2

CMOS 2-Input NAND Gate

- in an equivalent inverter model, to get Vth=VDD/2, we can use:

1

VDD | VT , p |

kR

1 2

Module #6

Page 22

CMOS Combinational Logic

CMOS 2-Input NAND Gate

Vth ( NAND )

CMOS 2-Input NAND Gate

- we can model the 2-Input NAND gate as an equivalent invert as follows:

CMOS Combinational Logic

Module #6

Page 20

kR

1

kR

kn

k 2

1 n

kp

2kp

4 k p kn

- note that the NMOS series network has to be sized larger in

order to overcome the voltage drop across each series stage.

EELE 414 Introduction to VLSI Design

Module #6

Page 23

EELE 414 Introduction to VLSI Design

Module #6

Page 24

CMOS Combinational Logic

CMOS Combinational Logic

CMOS N-Input NAND Gate

CMOS N-Input NAND Gate

- our Vth expression for an N-input NAND gate becomes:

- to expand the NAND gate, we

VDD

1

VDD | VT , p |

kR

VT ,n N

- add more PMOS transistors in parallel in the Pull-up Network

- add more NMOS transistors in series in the Pull-down Network

Vth ( NAND )

VT ,n

Vth ( NAND )

N2

VDD | VT , p |

kR

1

Output

kR

EELE 414 Introduction to VLSI Design

N2

kR

- and our rule of thumb for an ideal symmetric equivalent inverter becomes:

kn

kn

N

1

kp

N kp

N 2 k p kn

Module #6

Page 25

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

1

kR

1 N

VDD

Module #6

Page 26

CMOS Combinational Logic

CMOS 2-Input NAND Gate Layout

Complex CMOS Logic Circuits

- we can implement any logic functions using NANDs, NORs, and INVs.

- however, the timing and area of the standard SOP approach can be improved further

by creating the entire logic function in one circuit.

- we can design a complex function by:

1) Creating the NMOS pull-down network of F where:

- an OR is performed using parallel connected NMOSs

- an AND is performed using series connected NMOSs

NOTE:

this is an NMOS pull-down network so the logic function must be in

an F form (or a dual of F).

NOTE:

these rules can be used in a nested configuration to form any

logic function

2) Creating the PMOS pull-up network to be the complement of the pull-down network

EELE 414 Introduction to VLSI Design

Module #6

Page 27

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

Module #6

Page 28

CMOS Combinational Logic

Complex CMOS Logic Circuits

- an example of the NMOS pull-down network synthesis is:

Complex CMOS Logic Graphs

- the complementary PMOS network is created with a technique called a dual pull-up/down graph

F A D E B C

- this is a graphical way to create the PMOS network for a given NMOS pull-down circuit.

- we first create the pull-down graph by representing:

- D+E is created with two NMOSs in parallel

- A(D+E) puts an NMOS in series with the (D+E) network

- the entire A(D+E) network is in parallel with the BC network

- the BC network is created with two series NMOSs

1) each NMOS transistor as an edge (i.e., a line), and

2) each node as a vertex (i.e., a dot)

- we orient the pull-down graph in the same orientation as the NMOS circuit

(Vout on top, VSS on bottom)

EELE 414 Introduction to VLSI Design

Module #6

Page 29

EELE 414 Introduction to VLSI Design

Module #6

Page 30

CMOS Combinational Logic

CMOS Combinational Logic

Complex CMOS Logic Graphs

- next, we create the dual pull-up graph on top of the pull-down graph.

Complex CMOS Logic Graphs

- now we can separate the graphs and synthesize the PMOS pull-up network

- we orient the pull-up graph with VDD on the left and Vout on the right.

Remember that:

an edge (a line) = a transistor

a vertex (a dot) = a node

- we create the pull-up graph using the rules:

1) a new vertex is created within each confined area of the pull-down graph

2) each vertex is connected by an edge which crosses each edge of the pull-down graph

EELE 414 Introduction to VLSI Design

Module #6

Page 31

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

CMOS Combinational Logic

AOI / OAI CMOS Logic

- we classify the common types of logic expression forms as:

AOI

Module #6

Page 32

AOI / OAI CMOS Logic

- AOI and OAI logic expressions can create standardized layouts due to their symmetry

- AND-OR-INVERT

- this corresponds to a Sum-of-Products logic expression form:

ex)

OAI

F A B B'C C ' D

AOI

- OR-AND-INVERT

- this corresponds to a Products-of-Sums logic expression form:

ex) F A B B'C C ' D

OAI

- Note that we have the Invert portion in these forms so that we can directly synthesize the

NMOS pull-down network.

- we can create this form of a logic expression using DeMorgans Theorem

EELE 414 Introduction to VLSI Design

Module #6

Page 33

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

CMOS Combinational Logic

Complex CMOS Logic Graphs (XOR)

- lets design a 2-input XOR gate.

Complex CMOS Logic Graphs (XOR)

3) We directly synthesize the pull-down network and create its equivalent pull-down graph

1) we first find the traditional SOP expression

4) We then create the dual pull-up graph on top of the pull-down graph

2) we then manipulate it into an OAI or AOI form so that the pull-down network can be

directly synthesized

EELE 414 Introduction to VLSI Design

Module #6

Page 34

Module #6

Page 35

- insert a vertex in each enclosed region of the pull-down graph (vertex=node)

- connect each vertex such that each pull-down is crossed by one pull-up edge (edge=PMOS)

EELE 414 Introduction to VLSI Design

Module #6

Page 36

CMOS Combinational Logic

CMOS Combinational Logic

Complex CMOS Logic Graphs (XOR)

5) we then unfold the dual pull-up/down graph and directly synthesize the pull-up network

Complex CMOS Logic Equivalent Inverters

- to calculate the performance of a complex Logic Circuit, we need create an equivalent inverter

- we then use our equations for Vth, PHL, and LHL on the equivalent transconductance values

- we know that

- an equivalent network for series-connected

transistors with the same sizes:

L equivalent

1

1

L N

- an equivalent network for parallel-connected

transistors with the same sizes:

Module #6

Page 37

EELE 414 Introduction to VLSI Design

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

W

W

L equivalent

L N

Module #6

Page 38

CMOS Combinational Logic

Complex CMOS Logic Equivalent Inverters

- for example:

Complex CMOS Logic Stick-Diagrams

- a stick diagram is a graphical way to map a complex CMOS circuit into a layout diagram

L P equivalent

L N equivalent

- in a stick diagram, draw the general layout configuration that will be used in order to figure out

how the diffusion layer contacts are placed.

1

W

L A

1

1

1

W W

1

1

L

B L C

W

W

L

L

D E

- a stick diagram has:

- diffusion regions as rectangles

- metal traces are lines

- contacts are circles

- polysilicon inputs are columns

- the intent of a stick diagram is to figure out how the

inputs and outputs are connected to the diffusion regions

1

1

1

1

1

1

W

W W

W

W

L A L D L E L B L C

- we dont put any size information in this diagram

- we typically sketch this out with pencil-and-paper prior

to going into the tool

- planning ahead can save a lot of time in the tool

EELE 414 Introduction to VLSI Design

Module #6

Page 39

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

Module #6

Page 40

CMOS Combinational Logic

Transmission Gate (Pass Gate)

- A Transmission Gate (T-gate or TG or pass gate) is a bi-directional switch made up of an NMOS

and PMOS is parallel.

- a control signal is connected to the gate of the NMOS (C) and its complement is sent to the

gate of the PMOS (C)

Transmission Gate (Pass Gate)

- When the control signal is HIGH (VDD):

both transistors are turned on

- a low resistance path exists between A and B

- When the control signal is LOW (0v)

- The T-gate is a bidirectional switch between A and B which is controlled by C

- both transistors are off

- the T-gate looks like an open circuit

- this type of operation is commonly used in bus situations where only one gate can drive

the bus line at the same time

- T-gates are put on the output of each gate on the bus. The circuit that drives will use a T-gate

to connect to the bus with a low impedance path. All other circuits that arent driving will switch

their T-gates to be a high-impedance.

EELE 414 Introduction to VLSI Design

Module #6

Page 41

EELE 414 Introduction to VLSI Design

Module #6

Page 42

CMOS Combinational Logic

CMOS Combinational Logic

Transmission Gate (Pass Gate)

Transmission Gate (Pass Gate)

- When the T-gate is on, the regions of operation of the transistors will depend on Vin and Vout

- we typically model the T-gate as a switch with an equivalent resistance

- lets say we drive Vin=VDD and initially Vout=0v

- at any point, the equivalent resistance is given by:

- As Vout moves from 0v to VDD, the regions of operation for the transistors are as follows:

Req ,n

VDD Vout

I DS ,n

Req , p

VDD Vout

I SD, p

Req ,TG Req ,n // Req , p

EELE 414 Introduction to VLSI Design

Module #6

Page 43

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

CMOS Combinational Logic

Transmission Gate (Pass Gate)

Region 1

VDD Vout

1

2

k n VDD Vout VT ,n

2

VDD Vout

Req , p1

2

1

k p VDD VT , p

2

Req ,n1

Region 2

Module #6

Page 44

Transmission Gate (Pass Gate)

- as the PMOS and NMOS transistors turn on/off, they keep the overall T-gate

resistance LOW

VDD Vout

1

2

k n VDD Vout VT ,n

2

VDD Vout

1

2

k p 2 VDD VT , p VDD Vout VDD Vout

2

Req ,n 2

Req , p 2

Region 3

Req ,n 3 HIGH

Req , p 3

VDD Vout

1

2

k p 2 VDD VT , p VDD Vout VDD Vout

2

EELE 414 Introduction to VLSI Design

Module #6

Page 45

EELE 414 Introduction to VLSI Design

CMOS Combinational Logic

CMOS Combinational Logic

Transmission Gate (Pass Gate)

- T-gates can be used to create combinational logic

2-input Multiplexer

Module #6

Page 46

Transmission Gate (Pass Gate)

- complex logic using T-gates has an advantage when it comes to layout because of

the symmetry of the PMOS and NMOS. One N-well can be used for all PMOSs

Exclusive OR (XOR)

EELE 414 Introduction to VLSI Design

Module #6

Page 47

EELE 414 Introduction to VLSI Design

Module #6

Page 48

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Report SeminarDokument45 SeitenReport SeminarPranjul SachanNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- 6 Log Anti Log AmplifiersDokument32 Seiten6 Log Anti Log AmplifiersAnonymous eWMnRr70q0% (1)

- PCB Design Tutorial Rev ADokument25 SeitenPCB Design Tutorial Rev Arahuldhar2142249529100% (30)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- PCB Design TipsDokument29 SeitenPCB Design Tipsizzati_2607Noch keine Bewertungen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Fee Structure 2015-16Dokument1 SeiteFee Structure 2015-16Pranjul SachanNoch keine Bewertungen

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Mathematics 11 Guide (2014)Dokument231 SeitenMathematics 11 Guide (2014)HumairaNoch keine Bewertungen

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Concept of StrategyDokument3 SeitenConcept of StrategyvikasmishraelexNoch keine Bewertungen

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- 1 1.1 ComputationDokument72 Seiten1 1.1 ComputationGanesh KumarNoch keine Bewertungen

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Objective Mapping and Kriging: 5.1 Contouring and Gridding ConceptsDokument24 SeitenObjective Mapping and Kriging: 5.1 Contouring and Gridding Conceptsforscribd1981Noch keine Bewertungen

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- Differential Calculus - Module 1Dokument7 SeitenDifferential Calculus - Module 1Noel S. De Juan Jr.Noch keine Bewertungen

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Syllabus Mathematics in The Modern WorldDokument19 SeitenSyllabus Mathematics in The Modern WorldJham L. PatraNoch keine Bewertungen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Javacc FaqDokument66 SeitenJavacc FaqFrederick Bejarano SanchezNoch keine Bewertungen

- Model Development and Loads Analysis of An Offshore Wind Turbine On A Tension Leg Platform, With A Comparison To Other Floating Turbine ConceptsDokument129 SeitenModel Development and Loads Analysis of An Offshore Wind Turbine On A Tension Leg Platform, With A Comparison To Other Floating Turbine ConceptsUbani Obinna RanksNoch keine Bewertungen

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Kombinasi Hukum I Dan II Termodinamika - enDokument17 SeitenKombinasi Hukum I Dan II Termodinamika - enEkok Ec100% (1)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Spe 199716 MSDokument43 SeitenSpe 199716 MSJamesNoch keine Bewertungen

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Unit III Nurbs and Solid ModelingDokument120 SeitenUnit III Nurbs and Solid Modelingpalaniappan_pandian100% (1)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Lesson 9Dokument7 SeitenLesson 9Mitzi. SumaderoNoch keine Bewertungen

- Instrumentation & Control HandoutDokument95 SeitenInstrumentation & Control HandoutPandimadevi SelvakumarNoch keine Bewertungen

- 3D Graphics With OpenGLDokument31 Seiten3D Graphics With OpenGLMusariri TalentNoch keine Bewertungen

- Chemical Engineering Plant Economics MCQ Questions & Answers - Chemical EngineeringDokument6 SeitenChemical Engineering Plant Economics MCQ Questions & Answers - Chemical Engineeringsrinu02062Noch keine Bewertungen

- Chapter 3 - Multiple Random Variables-UpdatedDokument25 SeitenChapter 3 - Multiple Random Variables-Updatedfarouq_razzaz2574Noch keine Bewertungen

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- DocxDokument16 SeitenDocxDeepika PadukoneNoch keine Bewertungen

- Kindergarten DLL Week 4Dokument6 SeitenKindergarten DLL Week 4Precious MamuyacNoch keine Bewertungen

- Ai ML MCQ CombinedDokument54 SeitenAi ML MCQ CombinedAbhinav JoshiNoch keine Bewertungen

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Crane DesingDokument243 SeitenCrane Desingjulianzl2110Noch keine Bewertungen

- Tutorial Week 10 - Internal Bone RemodellingDokument13 SeitenTutorial Week 10 - Internal Bone RemodellingHussam El'SheikhNoch keine Bewertungen

- Problems Involving Sets2.0Dokument39 SeitenProblems Involving Sets2.0Agnes AcapuyanNoch keine Bewertungen

- Mathematics: Circle and Its PartsDokument30 SeitenMathematics: Circle and Its PartsDom Martinez100% (2)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (120)

- OS-Kings College Unit WiseDokument8 SeitenOS-Kings College Unit WisePradeep KumarNoch keine Bewertungen

- 4.ResM Non Stat CodingDokument9 Seiten4.ResM Non Stat CodingSwati RathiNoch keine Bewertungen

- Crystallography: Lattice, Point Group and Systems Reality Is Analyzed and Concluded As Laws of Learning CrystalsDokument44 SeitenCrystallography: Lattice, Point Group and Systems Reality Is Analyzed and Concluded As Laws of Learning Crystalsmanas773Noch keine Bewertungen

- Dray Etal 2014 EcologyDokument8 SeitenDray Etal 2014 EcologySofia Julieta AcBäNoch keine Bewertungen

- 2 of A Kind: Trick Courtesy Of: Mike (Mike)Dokument27 Seiten2 of A Kind: Trick Courtesy Of: Mike (Mike)Jeppo X. JulianNoch keine Bewertungen

- Navigational Strategies of Mobile Robots: A Review: Dayal R. ParhiDokument21 SeitenNavigational Strategies of Mobile Robots: A Review: Dayal R. ParhiSMITH CAMILO QUEVEDONoch keine Bewertungen

- Corrada - Geometry - El Lissitzky PDFDokument9 SeitenCorrada - Geometry - El Lissitzky PDFAnnie PedretNoch keine Bewertungen

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)