Beruflich Dokumente

Kultur Dokumente

LOGIC DESIGN MCQ: BCD, Binary Systems, Boolean Algebra & Logic Gates

Hochgeladen von

NIRALIOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

LOGIC DESIGN MCQ: BCD, Binary Systems, Boolean Algebra & Logic Gates

Hochgeladen von

NIRALICopyright:

Verfügbare Formate

LOGIC DESIGN MCQ

1)

2)

3)

4)

5)

6)

7)

BCD stands for_____________________

a. Binary Coded Decimal

b. Binary Coding decode

c. Binary code discuss

d. Binary code domain

All fractional decimal number is split into ____________

a. Two Parts

b. Single Parts

c. Three Parts

d. All the Above

The transistor can represent the value ___________ by off state and the value ________ by on state

a. 0 and 1

b. 1 and 0

c. 2 and 1

d. 3 and 1

The base of Octal number system is ______________ different ways

a. 8

b. 7

c. 6

d. 5

The base of Hexadecimal number system is ___________ means different ways.

a. 16

b. 15

c. 14

d. 11

How to represent the Hexadecimal value 1A3F in decimal format.

a. 671910

b. 789610

c. 963510

d. 4563210

Match The Following Table

1) 4 bits

2) 8 bits

3) 16 bits

4) 32 bit

a.

b.

c.

d.

8)

D,c,b,c

A,b,c,d

C , b, d , a

B,c,a,d

The MSB Stand For ____________________

a. Most Significant Bit

b. Most Signified Bit

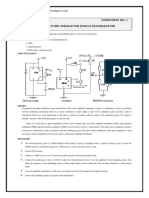

a) Word

b) Half Word

c) Byte

d) Nibble

LOGIC DESIGN MCQ

c. Most Sign Bit

d. Most Signal Bit

9)

The LSB Stands For __________________________

a. Least Significant Bit

b. Least Sign Bit

c. Least Signal Bit

d. Least Sign Broad

10)

The MSB 0 represent the _____________ value

a. Positive Value

b. Negative Value

c. Single Value

d. Double Value

11)

The _____________ complement is slightly different from the signed magnitude number

a. 1s Complement

b. 2s Complement

c. 3s Complement

d. 4s Complement

12)

The _____________ Complement is asymmetric system with additional bit is required

a. 2s Complement

b. 1s Complement

c. 3s Complement

d. 4s Complement

13)

convert 100.26510 into binary

a. 1100100.0100

b. 11111.00000

c. 101010.0001

d. 111101.0000

14)

Convert 1A2C16 into Binary Value

a. 0001 1010 0010 11002

b. 0010 1011 0011 0001

c. 1000 0001 0101 0001

d. 1001 0001 1010 1010

15)

Convert 1A2C.3B4D16 into Binary Value

a. 0001 1010 0010 1100 . 0011 1011 0100 11012

b. 1001 0001 1010 1010 . 0011 1011 0100 11012

c. 1000 0001 0101 0001 . 0011 1011 0100 11012

d. 0010 1011 0011 0001 . 0011 1011 0100 11012

16)

The signed magnitude representation is one of the methods to represent the________ and _______ number in

binary system

a. Negative And Positive

b. Positive And Negative

c. Negative And Sign

d. All The Above

17)

All binary bits are complemented and resented along with the ___________ bit

a. Sign Bit

LOGIC DESIGN MCQ

b. Complement Bit

c. Positive Bit

d. Negative Bit

18)

This is a powerful yet simple technique which minimizes the hardware implementation of signed arithmetic

operations in a __________ machine.

a. Digital Machine

b. Analog Machine

c. Client Machine

d. Server Machine

19)

The 2N1 is often referred to as the ____________ for computing the excess representation of the number

a. Magic Number

b. Simple Number

c. Dynamic Number

d. Static Number

20)

Rules for determining significance (integers):

1. A nonzero digit is always significant

2. The digit '0' is significant if it lies between other significant digits

3. The digit '0' is never significant if it precedes all the nonzero digits

21)

22)

23)

24)

25)

a. 1 and 2

b. 1 and 3

c. 2 and 3

d. 1 2 3

The range of values represented by an 8-bit binary number is _____.

a. 0 to 255.

b. 0 to 155

c. 0 to 156

d. 0 to 256

The result of 7 2 using 1s complement notation is

a. (144)8

b. (154)8

c. (169)8

d. (123)8

The bit pattern 1011 in 1s complement notation is

a. (0.0100)2

b. (154)8

c. (169)8

d. (123)8

The bit pattern 1110 in 2s complement notation is

a. 0100

b. 1100

c. 1111

d. 10101

The significant digits of 0012340 are _______.

LOGIC DESIGN MCQ

26)

27)

28)

29)

30)

31)

32)

33)

a. 0101

b. 1101

c. 1110

d. 1010

The bit pattern 1101 Excess Number converted value is ________.

a. 2

b. -1

c. -3

d. -4

The digit _________ is never significant if it precedes all the nonzero digits

a. 0

b. 1

c. 2

d. 3

Decimal means base __________.

a. 10

b. 8

c. 2

d. 16

The decimal value of the bit pattern 11111111 is _________.

a. 255

b. 263

c. 155

d. 235

This concept becomes important when we address the IEEE Single Precision __________ standard

a. Floating-Point standard.

b. Binary Number Standard

c. Decimal Number Standard

d. Hexa Decimal standard

Unit -2

Any basic ____________ units can be used to construct the digital circuits

a. 2 States

b. 1 States

c. 3 States

d. 4 States

The Boolean sum operator is represented by + _________

a. OR

b. AND

c. EX-OR

d. EX- NOR

The Boolean product operator is represented by or _________

a. AND

b. OR

c. Ex-OR

d. EX-NOR

LOGIC DESIGN MCQ

34)

35)

36)

37)

38)

39)

40)

41)

42)

0 + 0 = _________

a. 0

b. 1

c. 2

d. 3

0 + 1 = ________

a. 1

b. 0

c. 2

d. 3

1 1 + (0 + 1)= ___________________

a. 1

b. 0

c. 10

d. 11

(a')' = a _____________ Law

a. Involution Law

b. Idempotent Laws

c. Identity Laws

d. Dominance Laws

a + a' = _______ Complementarity

a. 1

b. 0

c. 2

d. 3

a + a = a ___________ Laws

a. Idempotent Laws

b. Identity Laws

c. Dominance Laws

d. Involution Law

a a' = ______________

a. 0

b. 1

c. 2

d. 3

a a =_____________

a. a

b. 0

c. 1

d. B

a + 0 = a _______________ Laws

a. Identity

b. Idempotent

c. Dominance

d. Involution

LOGIC DESIGN MCQ

43)

44)

45)

46)

47)

48)

49)

50)

51)

a 1 = __________

a. 1

b. A

c. 0

d. a

a + 1 = 1______________ Laws

a. Identity

b. Idempotent

c. Dominance

d. Involution

a 0 = ___________

a. 1

b. 0

c. A

d. B

a + b = b + a ______________ Laws

a. Commutative

b. Idempotent

c. Dominance

d. Involution

a + (b + c) = (a + b) + c ________________ Laws

a. Associative

b. Idempotent

c. Dominance

d. Involution

a + bb = (a + b)(a + c) ______________ Laws

a. Distributive

b. Idempotent

c. Dominance

d. Involution

(ab)' = a' + b' ____________ Laws

a. DeMorgans

b. Idempotent

c. Dominance

d. Involution

(a + b)' = __________

a. Ab

b. Ab

c. Ab

d. Ab

a + (ab) = a ________________ Laws

a. Absorption

b. Idempotent

c. Dominance

d. Involution

LOGIC DESIGN MCQ

52)

53)

54)

55)

56)

57)

58)

59)

60)

a(a + b) = ______________

a. a

b. 0

c. 1

d. B

a + a'b = a + b _______________ Laws

a. Redundancy

b. Idempotent

c. Dominance

d. Involution

a(a' + b) = ____________

a. ab

b. ba

c. ab

d. ab

ab + a'c + bc = ab + a'c ________________ Laws

a. Consensus

b. Idempotent

c. Dominance

d. Involution

A Boolean product m1, m2, m3mn is said to be a ___________of Boolean variables

a. Minterm

b. Maxterm

c. Midiumterm

d. Singleterm

Find Out the min term of this value 0 0 0 ______________

a. a'b'c'

b. abc

c. abc

d. abc

Find Out the min term of this value 0 0 1 ______________

a. a'b'c'

b. abc

c. abc

d. abc

The Boolean system is said to be closed with respect to a given ____________ operator

a. Binary

b. Float

c. Decimal

d. Hexa

The logical AND operation is represented by the symbol ______________

a. .

b. +

c.

d. *

LOGIC DESIGN MCQ

61)

62)

63)

64)

65)

66)

67)

68)

69)

The symbol __________ is dropped when the single letter variable names are used

a. .

b. +

c.

d. *

X (Y + Z) = _________________

a. (X Y) + (X Z)

b. (X + Y) + (X Z)

c. (X + Y) (X + Z)

d. (X Y) (X Z)

(XY)Z =_____________

a. X(YZ)

b. X+(YZ)

c. X(Y+Z)

d. X(Y+Z)

(X + Y) = _____________

a. X Y

b. X Y

c. X Y

d. X Y

(X Y) = ___________

a. X + Y

b. X + Y

c. X + Y

d. X + Y

X + XY = _____________

a. X

b. Y

c. X

d. Y

X (X + Y) = __________

a. X

b. Y

c. X

d. Y

e. X

X + XY = ________________

a. X+Y

b. X + Y

c. X + Y

d. X + Y

X (X + Y) = __________________

a. XY

b. XY

LOGIC DESIGN MCQ

c. XY

d. XY

70)

71)

72)

(X+Y) (X + Y) =_____________

a. Y

b. Y

c. X

d. X

X + X = _______________

a. 1

b. 0

c. A

d. A

What Is The name of This gates

a.

b.

c.

d.

Nand

And

Or

Ex-or

73) The functional completeness of the _____________ gate has be taken as advantage while

constructing logic circuits in digital systems

a. Nand

b. And

c. Or

d. Ex- or

74)

_________________ gate followed by an inverter can be used to implement OR gate

a. NOR

b. OR

c. NAND

d. NOT

75)

NOR is a ___________ complete operation

a. Functionally

b. Logically

c. Dynamically

d. Broadly

LOGIC DESIGN MCQ

76)

77)

78)

79)

If

either one of the input is HIGH, then the output will be _________ Ex Or Gates

a. Low

b. High

c. Middle

d. All the above

The XNOR gate is a digital logic gate whose function is the inverse of the exclusive __________ gate

a. OR

b. NOT

c. NAND

d. EX OR

The XOR or Mod-2 addition operation is defined by the equation is_________.

a. A B AB AB

b. A B AB AB

c. A B AB AB

d. A B AB AB

The NOR Gate output for input values 1 and 0 is _______.

a. 0

b. 1

c. A

d. A

80)

Exclusive NOR is defined as __________.

a. NOT

b. AND

c. OR

d. NAND

UNIT 3

81)

In a digital system, there are two voltage levels of electrical signals i.e., __________ and ___________

a. 0v and 5v

b. 1v and 6v

c. 3v and 8v

d. 4v and 9v

82)

An algebra developed in the nineteenth century by ________________

a. George Boole

b. Bill Gates

c. Denis Ritche

d.

83)

______________ is a variable which can have either 0 or 1 as its value

a. Boolean variable

b. Float Variable

c. Double Variable

d. Integer Variable

84)

A _______________is an expression using Boolean variables {X1, X2,.Xn} and the operations of a

Boolean algebra

LOGIC DESIGN MCQ

85)

86)

87)

a. Boolean expression

b. Logical Expression

c. Dynamic Expression

d. Binary Expression

A Boolean product m1, m2, m3mn is said to be a ___________

a. Minterm

b. Maxterm

c. MediumTerm

d. LongTerm

One way to determine the smaller set is by using _________ law

a. DeMorgans

b. Idempotent

c. Dominance

d. Involution

f = x'y'z' + x'y'z + x'yz' + x'yz + xyz' + xyz What is the Output

a. x' + y

b. x' + y

c. x'+ y

d. x + y

88)

If x and y is 0 and 1, the Boolean function xy+xy result is ____.

a. 0

b. 1

c. A

d. A

89)

________________a telecommunication engineer has invented Karnaugh Maps.

a. Maurice Karnaugh

b. George Boole

c. Bill Gates

d. Denis Ritche

e.

90)

In ___________ the Karnaugh map has been developed in Bell Labs while studying

a. 1953

b. 1957

c. 1856

d. 1756

91)

_________________ are generally used in simplification of two, three or four variables Boolean

function

a. K-maps

b. Gates

c. Flip Flop

d. Counter

92)

The simple functions in Boolean function are known as _________________

a. product function

b. Function

LOGIC DESIGN MCQ

c. Variable

d. Data

93)

An ______________ of a function is a product term that is included in the function

a. Implicant

b. Explicant

c. Extra

d. Inter

94)

A ___________of a function is an implicant of the function that is not included in any other implicant

of the function

a. prime implicant

b. Implicant

c. Explecant

d. Non Implement

95)

Implicants that cover as many cells of the map as possible are called __________.

a. Prime implicants

b. Implicant

c. Explecant

d. Private

96)

A Karnaugh map is a _______ representation of the truth table for a Boolean Function

a. 2-dimensional

b. 1-dimensional

c. 3-dimensional

d. 4-dimensional

97)

Match The Following

XYZ

1)0 0 0

2)0 0 1

3) 0 1 0

a.

b.

c.

d.

98)

MinTerm

a) a'b'c'

b) a'b'c

c) a'bc'

1-> a 2 -> b 3 -> c

1-> c 2 -> b 3 -> a

1-> a 2 -> c 3 -> b

1-> c 2 -> b 3 -> a

Match The Following

XYZ

1)0 0 0

2)0 0 1

3) 0 1 0

a. 1-> a 2 -> b 3 -> c

b. 1-> c 2 -> b 3 -> a

c. 1-> a 2 -> c 3 -> b

MaxTerm

a) a+b+c

b) a+b+c'

c) a+b'+c

LOGIC DESIGN MCQ

d. 1-> c 2 -> b 3 -> a

99)

Find The Following Equeation Output

xyz

000

001

010

011

x^y

0

1

1

1

(x^y)^z

0

0

1

0

100) We could define a ________ operator "|"

a. Nand

b. OR

c. NOT

d. Ex-OR

101) A minterm expansion can be simplified using the identities and laws of Boolean algebra

a. TRUE

b. FALSE

102) K-maps get cumbersome and other techniques like _____________ Method is used

a. Tabular Method

b. Simple Method

c. Mathematic Method

d. Logical Method

103) The Boolean expressions will not be equivalent to the _____________ product function

a. k-maps

b. Gates

c. Counter

d. Flip Flop

104) _____________is represented by one product block and the other product represents y.

a. x

b. x

c. 0

d. 1

105) A horizontal _____________ can be done for 3-variable map, horizontal

a. wrap around

b. Around

c. Simple

d. Long

106) The ___________ groups are used to obtain the simplest form

a. largest size

b. Small Size

c. Medium Size

d. Short Size

107) LSI Stands For_________

LOGIC DESIGN MCQ

a.

b.

c.

d.

Large Scale Integration

Large Scan Integration

Large State Integration

Large Scale Inititu

108) ELSI Stands For_________

a. Extra-large scale integrated

b. Extra-large scale integrated

c. Extra scale integrated

d. Extra-loaded scale integrated

109) VLSI Stands For_________

a. Very Large Scale Integration

b. Very Load Scale Integration

c. Very Large State Integration

d. Very Large Stand Integration

110) PLD Stands For_________

a. programmable logic devices

b. programmable logic Define

c. programmable logic Define

d. programmable logic decode

111) Minimal cost- it may be cheaper to use certain components as opposed to others

a. True

b. False

112) Minimised number of gates - one interpretation of the ___________ solution,

a. 'simplest'

b. Largets

c. Short

d. Long

113) Minimised number of _______________ interconnections, which are a source of unreliability

a. chip-to-chip

b. Register To Register

c. Memory To Memory

d. Counter To Counter

114) Minimal propagation delay- in cases where the very fastest __________ operation is required

a. Circuit

b. Register

c. Counter

d. Ram

Unit- 4

115) _________ operations is known as combinational circuits

a. Boolean

b. Gates

c. Counter

d. Register

LOGIC DESIGN MCQ

116) Combinational circuits are used to construct the computers _________

a. CPU

b. Ram

c. HDD

d. Register

117) A _______________ can be implemented by using above Boolean functions

a. half-adder

b. Full Adder

c. Adder

d. 3addre

118) ABCin + ABCin + ABCin + ABCin= ________________________

a. A (XOR) B (XOR) C

b. A (XOR) B (NOR) C

c. A (OR) B (XOR) C

d. A (OR) B (XNOR) C

119) ______________to Seven segment decoder is the combination circuit which is used very commonly

a. BCD

b. Binary

c. Decimal

d. Hexa

120) Counting as we have been taught since kindergarten is based on the _____________ number

system

a. Decimal

b. Binary

c. Octal

d. Hexa

Unit-4

121) This Combinational Gates Are Represented In

_____________ Adder

a. Half Adder

b. Full Adder

c. Adder

d. Multiplexer

122) A __________ adder circuit adds the carry in C along with the two inputs A and B

LOGIC DESIGN MCQ

a. Full

b. Half

c. Adder

d. All the Above

123) ___________gate there is only one discrepancy when inputs are, therefore without changing the

resulting logic

a. XOR

b. NAND

c. AND

d. OR

124) The approach used for designing an adder can be used to design a ____________

a. substractor

b. Adder

c. Full Adder

d. Half Adder

125) Comparators can be used in a _________________

a. CPU

b. RAM

c. REGISTER

d. COUNTER

126) A __________________ is a digital device which decodes the original information from the encoded

inputs

a. Decoder

b. Encoder

c. Multiplexer

d. De-Multiplexer

127) A digital comparator is a hardware electronic device that compares two numbers in _______form

and generates

a. Binary

b. Decimal

c. Hexa

d. Octal

128) An _____________is a device used to change a signal (such as a bitstream) or data into a code

a. Encoder

b. Decoder

c. Multiplexer

d. Mux

129) A ______________ encoder is such that if two or more inputs are given at the same time

a. Priority

b. Assign

c. Decode

d. Encode

130) Priority encoders can be easily connected in arrays to make _______________ encoders

a. Larger

b. Small

LOGIC DESIGN MCQ

c. Medium

d. Short

131) In electronics, multiplexing of many signals is performed by the device known as ________

a. Multiplexer

b. Demultiplexer

c. Adder

d. Half Adder

132) Many ___________ And ___________signals can be given as input signals for the multiplexer

a. analog And digital

b. Degital or digital

c. analog or Anlog

d. analog or decode

133) A multiplexer is a switch that has multiple inputs and ______________ output

a. Single

b. Multiple

c. A and B

d. Not An above

134) In _____________ circuit design, the values given for the selection line will be either zero or one.

a. Digital

b. Logical

c. Analog

d. Decode

135) In larger _______________ , using n selection pins 2n input signals can be multiplexed

a. Multiplexers

b. Demultiplexer

c. Adder

d. Half Adder

136) In electronics, a _____________ is a device which separates the input signal to multiple output

signals

a. Demultiplexer

b. Multiplexer

c. Curcuit

d. Logic

137) At the receiving end demultiplexer can be used as a complementary to the multiplexer

a. True

b. Flase

138) A _______________ is a function G(i) of the integers i, that for each integer N 0is one-to-one

a. Gray code

b. Binary Code

c. Hexa Code

d. Decimal Code

139) ________________code is most commonly used technique in constructing digital systems

a. Gray

b. Binary Code

c. Hexa Code

LOGIC DESIGN MCQ

d. Decimal Code

140) The __________________ of i with i=2 performed to generate the Gray code

a. Bitwise exclusive or (XOR)

b. Exclusive or (OR)

c. Nor

d. NOT

141) The Gray codes are named after Frank Gray who patented the idea of using Gray codes in shaft

encoders

a. True

b. False

142) An algorithm or a circuit which translates back the __________________ to integer is required

a. Gray code

b. Binary Code

c. Hexa Code

d. Decimal Code

143) In digital system, decimal numbers are encoded to binary sequence using ______________technique

a. binary coded decimal

b. Binary

c. Hexa

d. Decimal

144) The advantage of the BCD encoding is that the conversion of ______________ sequence to decimal

digits

a. Binary

b. Decimal

c. Hexa

d. Logical

145) The drawbacks of the BCD encoding are the complexity of the ________circuits which are used to

implement the

a. Digital

b. Logical

c. Analog

d. Degit

146) Thus, the BCD encoding for the number 256 would be

a. 0010 0101 0110

b. 0010 0101 0111

c. 0010 0101 1111

d. 0010 1111 0110

147) By mapping each __________ to a different character

a. Nibble

b. Bytes

c. Bits

d. Broad

148) Than binary encoded numbers ___________ encoded numbers can be easily displayed

a. BCD

b. Binary

LOGIC DESIGN MCQ

149)

150)

151)

152)

153)

154)

155)

156)

157)

c. Degital

d. Logital

Generally, integer ___________ And _____________ operation are involved in conversion of binary

a. Multiplication And Division

b. Multiplication or Addition

c. Multiplication or Subtraction

d. Multiplication or Addition

In packed BCD encoding two digits are placed in a ______________ byte

a. Single

b. Multiple

c. Long

d. Binary

Packed ______________ encoding is also known as simply packed decimal

a. BCD

b. Binary

c. Digital

d. Logical

An ______________ system uses Zoned decimal to representing numeric digits

a. IBM mainframe

b. Microsoft

c. Iball

d. BCD

In this encoding, the digit is stored in lower four __________________ of the byte.

a. Bits

b. Bytes

c. Logical

d. Degital

________________ systems use a zone value of 1111 (hex F); this yields bytes in the range F0 to F9

a. EBCDIC

b. ASCII

c. EBCDIC

d. Binary

The ____________________ bits are called the zone bits

a. Upper

b. Lower

c. Midium

d. Extent

The EBCDIC codes for the characters ____________ through ____________

a. 0 to 9

b. 0 16

c. 0 to 2

d. 0 to 8

_____________ systems use a zone value of 0011 (hex 3), giving character codes 30 to 39 (hex).

a. ASCII

b. EBCDIC

LOGIC DESIGN MCQ

c. EBDC

d. ADC

158) The current IBM databases and processors still use ___________________ data

a. BCD

b. Binary

c. Decimal

d. Hexa

159) ___________ is done by adding the nines' complement plus 1

a. Subtraction

b. Adder

c. Half Adder

d. Full Adder

160) It is a way to represent values with a balanced number of ________ And ____________ numbers

a. positive and negative

b. Adder and Subtraction

c. Substraction and negative

d. Degital And Logical

161) The ________________ binary number represents the smallest value

a. Smallest

b. Longest

c. Degital

d. Logical

162) The logic design using traditional methods have been superseded largely by the _________ and

_______circuits

a. MSI and LSI

b. VLSI AND LSI

c. ELSI AND LSI

d. LSI AND LSI

163) Then the Boolean function is implemented in ________________ circuits after minimizing it

a. SSI

b. LSI

c. VLSI

d. ELSI

164) Adding sufficient pins on an _______________package to access each gate in a chip is not

economical.

a. IC

b. Register

c. Memory

d. RAM

Unit -5

165) William Eccles and F.W.Jordan invented the first flip flop

a. True

b. False

166) A powerful model is required to build a complex ___________ system

a. Digital

LOGIC DESIGN MCQ

b. Analog

c. Decode

d. Encode

167) combinational circuits such as universal gates and memory such as __________________and flip

flops

a. latches

b. Flip Flop

c. Register

d. Counter

168) Both the inputs to an NOR gate are low, the output will be_____________.

a. High

b. Low

c. Midium

d. Largest

169) Where S stands for set and R stands for reset

a. True

b. False

170) As the circuit has ________________stable states

a. Two

b. One

c. Multiple

d. Single

171) Causing of wrong output because of the timing dependencies is known as __________

a. Hazard

b. Latch

c. Multiplexer

d. Gates

172) One way to do that is to interpose AND gates between the S and R inputs and the ___________

circuit.

a. Latch

b. Hazards

c. Gates

d. Multiplexer

173) The idea of clocking is applied to S-R latch, the problem of what should happen when __________

a. S=R=1

b. S=r+1

c. S=r-1

d. S=r *1

174) The concept of a D latch, where the bit to be stored is applied to the S input of a latch

a. True

b. Fale

175) The two basic flip flops in __________devices make the circuit insensitive

a. Master Slave

b. Z K

c. S R

LOGIC DESIGN MCQ

d. Letch

176) This circuit might have asynchronous __________ Or ___________which changes

a. Reset or Set

b. Set And Reset

c. A And B

d. Not In ABove

177) The circuit which is capable of remembering the applied input is called a __________

a. flip flop.

b. Gates

c. Cercuit

d. Multiplexer

178) Two __________ And __________ gates can be used to construct a flip flop

a. NOR And NAND

b. Nand And Nor

c. Or And Nor

d. Not and Nand

179) The functionality of the flip flop can be explained using cross coupled two NOR gates or NAND

gates.

a. True

b. False

180) The current state of the output is determined by the feeding back the ___________ states

a. Previous

b. Next

c. Middle

d. Last

181) This kind of outputs is inconsistent logically and also the circuit will be in ________ state

a. Unstable

b. Stable

c. Fixed

d. Unfix

182) The circuit which stores a single bit is described by a keyword ________

a. latch.

b. Flip Flop

c. Decoder

d. Mux

183) Usually the master slave devices are implemented using _____________ flip flops

a. Clocked

b. S R

c. Z K

d. Latch

184) Find Out The Output Of This Truth Table

S

1

0

0

0

LOGIC DESIGN MCQ

0

0

a.

b.

c.

d.

1

0

Q= 1 1 0 0 Q=0 0 1 1

Q= 1 1 0 0 Q=0 0 1 0

Q= 1 1 0 0 Q=1 1 1 1

Q= 1 1 1 1 Q=0 0 1 1

185) SR latch is the fundamental latch in _________ circuits

a. Digital

b. Logical

c. Dynamic

d. Static

186) the JK flip flop circuit symbol, the clock input is given for ______________

a. >

b. +

c.

d. .

187) The symbol of _________ flip flop

a. D Flip Flop

b. Z K Flip Flop

c. S R Flip Flop

d. Master Slave Flip Flop

188) The ______________ does not have the master slave properties.

a. edge-triggered

b. Z K Flip Flop

c. D Flip Flop

d. Master Slave Flip Flop

189) A synchronous sequential _____________ is made up of flip-flops and combinational gates

a. Circuit

b. Register

c. Flip Flop

d. Gates

190) By connecting two gated D latches in series a ___________

a. Master-Slave

LOGIC DESIGN MCQ

b. Z K Flip Flop

c. D Flip Flop

d. S R Flip Flop

191) A negative _____________ flip flop can be determined by removing the left most inverter

a. Edge Triggered

b. Z K Flip Flop

c. D Flip Flop

d. S R Flip Flop

192) An __________ gate is used to connect the data input to the S input of an S-R latch

a. AND

b. NOT

c. NAND

d. OR

193) As the second flip flop responds for the changes from first flip flop (master) this circuit is called

_______

a. Master Slave

b. J K Flip Flop

c. S R Flip Flop

d. Clock Flip Flop

194) The input variables are Q0, Q1, and x; the outputs are the variables J0, K0, J1 and K1

a. True

b. False

195) An important application of flip-flops is in the design digital __________

a. Counters

b. Register

c. Flip Flop

d. Letch

196) The number of _____________is determined from the number of states needed in the circuit

a. Flip Flops

b. Gates

c. Counter

d. Letch

197) At the same time, the enable to the slave will be changed from low to high and the signal

a. True

b. False

198) ____________flip flop responds during the negative edge of the enable input.

a. Master Slave

b. Z K

c. S R

d. D

199) The value at input X is shifted to the leftmost position in 3 clock cycles.

a. True

b. False

200) This circuit might have asynchronous reset or set which changes the present value of the output

irrespective of ___

LOGIC DESIGN MCQ

a.

b.

c.

d.

201)

202)

203)

204)

205)

206)

207)

208)

clock signal

Data Signal

Pulse

Signal

Unit 6

Shift registers are typically used as converters between __________ and _____________ devices

a. serial and parallel

b. Dynamic And Static

c. Logical And Paralal

d. Logical And Serial

We can think of __________as delay elements

a. shift registers

b. Register

c. Counter

d. Synchronous Counter

The answer was again moved back to one of the shift register, generally known as the _______

a. Accumulator

b. Program Counter

c. Register

d. MAR

SISO stands For__________

a. Serial Input Serial Output

b. Serial Input Serial Out

c. Serial In Serial Output

d. Serial Inter Serial Output

SIPO Stands For____________

a. Serial Input Parallel Output

b. Serial Input Serial Out

c. Serial Input Sampl Output

d. Serial Input PArtionall Output

PISO Stands For ________________

a. Parallel Input Serial Output

b. Parallel Input Serial Put

c. Parallel In Serial Output

d. Parallel Internal Serial Output

PIPO Stands For ______________

a. Parallel Input Parallel Output

b. Parallel Input Parallel Out

c. Parallel In Parallel Output

d. Parallel Input Parallel put

If we connect inputs and outputs of a _____________shift register, we get so called circular shift

a. serial-in serial-out

b. Serial Input Parallel Output

c. Parallel Input Serial Output

d. Parallel Input Parallel Output

LOGIC DESIGN MCQ

209) Let us call this ___________________ line

a. Read/Write

b. Write/Write

c. Read/Read

210) The __________register is mainly used to shift a given set of bits and present it to the next stage as

illustrated below

a. PIPO

b. SISO

c. SIPO

d. SISA

211) Additional control pins may be provided for changing the direction of the ______________

a. data shift

b. Register Shift

c. Curcuit Shift

d. Memory Shift

212) The previously loaded data may be ________by one bit position if LD/SH'=0 for the succeeding

negative going clock edges

a. shifted right

b. shifted Left

c. shifted Down

d. shifted Up

213) We need to shift left, the FFs need to be rewired. Compare to the previous __________

a. right shifter

b. Left shifter

c. Down shifter

d. Up shifter

214) As long as the same data is present it will be re-loaded on succeeding _____________

a. Clocks

b. Pulse

c. Signal

d. Register

215) This problem is remedied in the _________ by the addition of another AND gate to the multiplexer

a. 74ALS299

b. 74ALS285

c. 74ALS125

d. 74ALS741

216) The buffers shown are necessary for real physical ___________

a. IC

b. Register

c. Counter

d. Memory

217) The 74LS395 IC resembles very much like our theoretical ______________register

a. PIPO shift

b. SISO shift

c. PISO shift

LOGIC DESIGN MCQ

d. PIIO shift

218) The AND-OR _________________ at the data input to the FF's

a. Multiplexer

b. Demultiplexer

c. Decoder

d. Encoder

219) In this "real part", __________ must be low if the data needs to be available at the actual output

pins

a. OC

b. AC

c. QC

d. DC

220) _______ AND _________ have been reversed

a. SI And SO

b. OI And OD

c. DI And SI

d. SI And DI

221) This problem is remedied in the 74ALS299 by the addition of another __________gate to the

multiplexer

a. AND

b. OR

c. NAND

d. NOT

222) If SH/LD' is changed to SH/LD'=1, the AND gates labeled __________

a. load

b. Wait

c. Running

d. Executing

223) The next clock CLK will clock the data to _________And ________ And _________

a. QA QB QC

b. QD QF QC

c. QI QB QC

d. QF QD QC

224) A data pattern is presented to inputs DA

a. DB DC DD

b. DB DC DS

c. DA DB DD

d. DB DF DD

225) The shift register works much like a SISO register and D1 acts like

a. Data In line

b. Data Out line

c. Data line

LOGIC DESIGN MCQ

d. Data Put line

226) The first few cycles, the number of which is equal to number of _____________in the register

a. flip-flops

b. Logic Gates

c. Curcuit

d. Register

227) Input for shifting can be loaded into the register in ______________

a. Parallel

b. Serial

c. Sequence

d. Unsequence

228) To switch between data-input and data-shift mode, we use a signal______________.

a. Write/Shift

b. Read/Shift

c. Write/Store (W/S)

d. Write/Loaded (W/S)

229) Input for shifting can be loaded into the register in __________and the shifted output

a. Parallel

b. Serial

c. Sequence

d. LOaded

230) ____________leaves on the SO connection, where it could cascade to another shifter SI

a. QA

b. DA

c. IA

d. QD

UNIT 7

231) This trigger is usually supplied to a counter in the form of a signal called

a. Clock

b. Pulse

c. Signal

d. Data

232) _______________ counter these show increase of count value

a. Up counters

b. Down Conter

c. Ripple Counter

d. Decade counters

233) ______________ these show decrease of count value

a. Down counters

b. Ripple Counter

c. Decade counters

d. Up counters

234) ______________counters are realized by connecting output of a SISO

a. Ring counters

LOGIC DESIGN MCQ

b. Ripple Counter

c. Decade counters

d. Up counters

235) A ________________counter is constructed using serial-in and serial-out (SISO)

a. Johnson

b. Ripple

c. Decade

d. Up

e.

236) DAC stands For _____________

a. digital-to-analog converters

b. digital-to- Digital converters

c. digital-to-Decode converters

d. digital-to-Analogy converters

237) Many user applications require counter outputs in the form of decimal digits in place of

________format.

a. Binary

b. Heaxa

c. Decimal

d. Octal

238) The counting sequence is known as ____________sequence

a. Johnsons

b. Ripple

c. Decade

d. UP

239) An _________________counter, which counts from 0 to 7

a. Octal

b. Decimal

c. Hexa

d. Binary

240) A ___________counter can be constructed using a SISO(serial-in serial-out) shift register

a. Ring

b. Ripple

c. Decade

d. UP

241) MNC stands for _____________

a. Modulo N counter

b. Module N counter

c. Mod N counter

d. Modern N counter

242) The ___________ counter has two external input channels which corresponds to the count

a. Modulo N

b. Ripple

c. Decade

d. UP

LOGIC DESIGN MCQ

243) Output of each stage is fed to the S (set) input of next stage after _________

a. AND

b. OR

c. NAND

d. NOR

244) The _________form of flip-flops FF1 through FF4 in response to the clock signal

a. Wave

b. Signal

c. Loaded

d. Pulse

245) This is a Johnson counter implemented using 5 bit ________ shift register

a. SISO

b. SISS

c. PISO

d. SIPO

246) The commercial CMOS integrated circuits that implement this are __________________

a. CD 4017 and 4022

b. CD 4017 and 4023

c. CD 4014 and 4022

d. CD 4015 and 4022

247) In a 5 bit Johnson counter only ten out of ____________ states are actually used

a. 32

b. 45

c. 20

d. 8

248) Now the question is what if the counter flip-flops show an ___________ state

a. Invalid

b. Not valid

c. Correct

d. Not correct

249) Once can also assign any _________ state which is out of Johnson sequence

a. Illegal

b. Legal

c. Logical

d. Dynamic

250) This is the output of ____________ and ____________gates which in turn take inputs from flip-flops

a. AND And NOR

b. NAND and NOR

c. NOT and NOR

d. NOR and NOR

251) D flip-flops and hence the circuit is ________________

a. Synchronous.

b. Asynchronous.

c. Squencial

LOGIC DESIGN MCQ

d. Logical

252) The __________ input is asynchronous

a. RESET

b. SET

c. Clock

d. Decode

253) All but one flip-flop in a ____________counter will be in the same state which could be either 0 or 1

a. Ring

b. Ripple

c. Decade

d. UP

254) The counter itself increases or resets the output value on demand

a. True

b. False

255) To allow ___________implementations based on master-slave flipflops

a. Hardware

b. Software

c. Logical

d. Phycal

256) Each specification describes a bit-slice of the counter and could be implemented by a

_________flip-flop

a. Master-Slave

b. D

c. Z K

d. S R

257) The ____________ counter has two external input channels which corresponds to the count

a. Modulo N

b. Ripple

c. Decade

d. UP

e.

258) The signal received on the second input line which corresponds

a. True

b. False

259) with a suitable modification of the feedback it is possible to achieve an odd-numbered cycle

a. True

b. False

260) Possible 4 bit ring counter sequences are ______ ___________ __________ _________

a. 0001, 0010, 0100, 1000

b. 0001, 0010, 0100, 1111

c. 0001, 0010, 0100, 1101

d. 1001, 0010, 0100, 1000

Unit-8

261) The implementation can be done using digital ____________

LOGIC DESIGN MCQ

a. IC

b. Register

c. Counter

d. Memory

262) The design is generic and can be customized to suit different type of road junctions with minor

changes

a. True

b. False

263) The ________ bit counter IC2 is wired in such a way that it works like a ______ bit counter

a. 4 And 3

b. 8 And 16

c. 16 And 32

d. 32 and 64

264) In applications where __________ switching options are required

a. Multiple

b. Single

c. Two

d. Ten

265) Depending on the power that is switched, size and ____________ nature

a. Physical

b. Logical

c. Dynamic

d. Local

266) A switch can be considered to be a __________ which either allows or disallows certain entity

a. gate

b. Flip Flop

c. Register

d. Counter

267) The mechanical or electromechanical part which helps the contacts to physically touch and

separate are called _____

a. Actuators

b. Register

c. Counter

d. Mux

268) The nomenclatures are normally used in logic and wiring diagrams

a. True

b. False

269) A switch with both types of contacts is called a changeover switch or "make-before-break"

a. True

b. False

270) Alternatively, small __________displays may be provided on each of the input units to display

a. LED

b. CRT

c. LCD

271) __________scoring equipment keeps track of the points, games

LOGIC DESIGN MCQ

272)

273)

274)

275)

a. Electronic

b. Megnatic

c. Logical

d. All the Above

A jumper on the input of the ___________allows the use

a. DS2438

b. DS2444

c. DS2489

d. DS2487

Press = _________ * Vad + intercept

a. Slope

b. Vad

c. Interept

d. Logical

A fixed resistor could replace the variable _________

a. Resistor

b. Counter

c. Memory

d. Gatway

Another possibility is to use several DS2406 ______________

a. 1-wire switches

b. 2-wire switches

c. 3-wire switches

d. 4-wire switches

276) Once its set, put the ______________ in the A-B position to read pressure

a. Jumper

b. Pin

c. Code

d. Coax

277) An Excel spreadsheet can be used to calculate intermediate values.

a. True

b. False

278) The dart includes a barcode card reader that permits identification of league

a. True

b. False

279) Inter-game communication within an establishment is provided either by ____________the dart

a. Hardwiring

b. Softwareing

c. Technical

d. Dynamic

280) The operating range will be from _____________ To ____________

a. 28.00 inHg to 32.00 inHg

b. 28.00 inHg to 52.00 inHg

LOGIC DESIGN MCQ

c. 68.00 inHg to 32.00 inHg

d. 28.00 inHg to 50.00 inHg

281) Resolution will be greater than .01 inHg from sea level to ________ feet

a. 10,000

b. 50,000

c. 20,000

d. 30,000

282) The interface will be standard Dallas ________________ 1-wire.

a. Semiconductor

b. Flip Flop

c. Curcuit

d. Register

283) Because the unit will be designed for indoor operation, it can be externally powered.

a. True

b. False

284) This table calculates the station pressure for both the minimum _________ and the maximum

________

a. 28.00 and 32.00

b. 58.00 and 42.00

c. 68.00 and 32.00

d. 28.00 and 52.00

285) The station pressure is then converted to ___________ pressure sensor volts

a. MPX4115A

b. MPX4116A

c. MPX4117A

d. MPX4118A

286) The gain of 30 was chosen to allow maximum output voltage swing for all altitudes

a. True

b. False

287) The resulting op amp output voltages are listed in _________ Output column

a. OA

b. QA

c. DA

d. TA

288) The __________ ohm resistor sets the gain to 10

a. 40.2K

b. 44.2K

c. 46.2K

d. 47.2K

289) The variable resistor allows adjustment of the offset voltage from ____________ to _________

a. 2.0v to 4.0v.

b. 2.0v to 6.0v.

c. 2.0v to 9.0v.

d. 2.0v to 7.0v.

290) The user to edit the file to fine-tune the calibration if desired

LOGIC DESIGN MCQ

a. True

b. False

Unit -9

291) In __________ George Stibitz connected a New Hampshire teletype to a computer system in New

York

a. 1940

b. 1947

c. 1856

d. 1999

292) ________ maintained a monopoly in the US for many years by letting

a. AT&T

b. IBM

c. Microsoft

d. Linux

293) PSK stands for___________

a. phase-shift keying

b. phase-shifted key

c. protocol -shift keying

d. phase-short keying

294) Call originators transmitting at _________ or _________

a. 1070 or 1270 Hz

b. 1070 or 1289 Hz

c. 1076 or 1270 Hz

d. 1085 or 1270 Hz

295) DVD stands for_____________________________

a. Digital Versatile Disc

b. Digital Ventiled Disc

c. Digital Venod Disc

d. Digital Ver Disc

296) Most _____________s are of the same dimensions as compact discs

a. DVD

b. CD

c. LCD

d. DSD

297) Modem which stands for ________________

a. Modulator-Demodulator

b. Modulator-Decode

c. Modulator-demod

d. modulator-demod

298) POTS Stands For___________

a. Plain Old Telephone Systems

b. Plain Old Telephone Synchronise

c. Plain Old Telephone Slot

d. Plain Over Telephone Systems

299) A modem that switches it state _________ times/sec

LOGIC DESIGN MCQ

300)

301)

302)

303)

304)

305)

306)

307)

308)

a. 600

b. 500

c. 100

d. 200

Each baud if it transmits 4 bits, it is said to be a _____ bit/sec modem

a. 2400

b. 4500

c. 6400

d. 2890

Cable modems and _____________modems are some faster modems used by internet users daily

a. ADSL

b. DSL

c. BroadBand

d. Logical

___________modems use optical fibers to transmit data

a. Optical

b. Logical

c. Dynamic

d. Static

Smartmodem introduced by Hayes Communications in ___________

a. 1981

b. 1970

c. 1990

d. 1451

Using Smartmodem, computer can directly dial the phone using corresponding commands

a. True

b. False

BBS stands For_________

a. Bulletin board systems

b. Bulletin broadband systems

c. Bulletin boarding systems (BBSs)

d. Broadcase board systems (BBSs)

GeoPort modem released by ___________was similar one

a. Apple

b. Samsung

c. Nokia

d. Karbon

Computer can convert an image into _________format which is then sent through modem

a. Fax

b. Data

c. Image

d. Signal

Modems that are used currently are composed of an _________ part and a digital part

a. Analog

b. Degital

LOGIC DESIGN MCQ

309)

310)

311)

312)

313)

314)

315)

316)

317)

c. Signal

d. Pulse

Only for the operations which work at ___________ bps

a. 300

b. 500

c. 600

d. 700

In ________ to send the data using 300bps modems

a. Order

b. Out Of Bound

c. In Order

d. Un Order

In Bell 103 system, __________ and _________ Hz tones are played to send

a. 1070 Hz and 1270

b. 1170 Hz and 1270

c. 1270 Hz and 1270

d. 1370 Hz and 1270

______________is used in the systems whose speed is equal to or more than 1200bps

a. Phase shift keying

b. TSM

c. TTM

d. TTL

In _________ Gottfried Ungerboeck from IBM Zurich Research Laboratory applied

a. 1980

b. 1989

c. 1990

d. 1998

An _________modem manufactured to conform to the V.34 protocol

a. ISA

b. VISA

c. EISA

d. ISP

V.34 modems once the standard was ratified __________

a. 1994

b. 1999

c. 1956

d. 1999

In the late 1990s Rockwell and U.S. Robotics introduced new technology

a. True

b. False

The standard digital transmission in modern networks is _____________ kbit/s

a. 64

b. 90

c. 60

d. 30

LOGIC DESIGN MCQ

318) The digital ______technique was applied to increase the upload speed to a maximum of 48 kbit/s

a. PCM

b. DCM

c. VBM

d. DRF

319) ISP Stands For__________________

a. Internet Service Provider

b. Internal Service Provider

c. Increase Service Provider

d. Instrument Service Provider

320) Direct broadcast satellite, WiFi, and mobile phones all use modems

a. True

b. False

Unit ->10

321) ADC Stands for__________

a. analog-to-digital

b. analog-to-digit

c. analogical - to-digital

d. analog-to-descrive

322) An _________ takes in analog continuous signal that is to be transformed

a. ADC

b. DAC

c. ADS

d. DRF

323) Reference voltage measurement range = ________ to ________ volts

a. 0 to 7

b. 0 to 9

c. 0 to 16

d. 0 to 26

324) Even though ___________ to ________ conversion process is a non-linear process

a. analog-to-digital

b. Degital to Analog

325) the ________ stands for the linear relationship

a. ADC

b. DAC

c. SDF

d. DFS

326) PDF stands for _______________

a. probability density function

b. probability dens Fundation

c. probability density Faber

d. prility density function

327) CDF stands For_________________

a. cumulative distribution function

b. cumulative distributed function

LOGIC DESIGN MCQ

328)

329)

330)

331)

332)

333)

334)

335)

336)

337)

c. cum distribution function

d. cumve distribution function

____________ implementation imperfections cause all the ADCs

a. Physical

b. Logical

c. Dynamic

d. Static

___________ conversion has to convert the flow of continuous analog in time into digital values

a. ADC

b. DAC

c. DSC

d. FDC

Sampling input signals at regular intervals of time, is the way ADCs work

a. True

b. False

DAC performance are enhanced using dithers as discussed previously i.e.

a. True

b. False

LSB Stands for_________

a. Least Significant Bit

b. Last Sigtnificant Bit

c. Lose Significant Bit

The errors which are occurred due to physical imperfections are known as __________ errors

a. Nonlinearity

b. Linier

c. Logical

d. System

The output of _________ is given as input to DAC.

a. Up-down

b. Down

c. Up

d. Ripple

Undesired deviation of clock value from the periodic signal is known as ___________.

a. Clock jitter

b. Clock

c. Pulse

d. Signal

__________combines above techniques in a single implementation

a. Hybrid DACs

b. Dynamic

c. Logical

d. Static

_______________combines binary weighted principle for the LSBs

a. Segmented DAC

b. Segmented ADC

LOGIC DESIGN MCQ

c. Segmented DAS

d. Segmented DFD

338) In order to reproduce signals of frequency ___________kHz

a. 30

b. 40

c. 50

d. 60

339) ________________ is the simplest type of DAC

a. Pulse Width Modulator

b. TDM

c. TTM

d. TTL

340) _____________port came up digital inputs started dominating

a. HDMI

b. PS

c. COMPORT

d. SERIAL

Das könnte Ihnen auch gefallen

- Microprocessor MCQ: For 4th Sem MCQ: For 6th Sem MCQDokument24 SeitenMicroprocessor MCQ: For 4th Sem MCQ: For 6th Sem MCQKiran RajputNoch keine Bewertungen

- Unit 4 MCQDokument12 SeitenUnit 4 MCQTHIRUNEELAKANDAN100% (1)

- Multiple Choice Questions (MCQ) : Operating System (KCS401)Dokument51 SeitenMultiple Choice Questions (MCQ) : Operating System (KCS401)Larry Wheels0% (1)

- Internet of Things (IoT) Solved MCQs (Set-3)Dokument5 SeitenInternet of Things (IoT) Solved MCQs (Set-3)Shweta KachawarNoch keine Bewertungen

- MIS MCQ'sDokument14 SeitenMIS MCQ'sumaimaNoch keine Bewertungen

- 200 Multiple Choice Questions in C Programming MCQsDokument37 Seiten200 Multiple Choice Questions in C Programming MCQsAdil RazaNoch keine Bewertungen

- MCQ - MPMCDokument9 SeitenMCQ - MPMCRanganayaki RamkumarNoch keine Bewertungen

- Bca 501 Computer NetworksDokument19 SeitenBca 501 Computer NetworksManuja Maniyan100% (1)

- Coa Unit 4,5 MCQDokument26 SeitenCoa Unit 4,5 MCQManish Singh RajputNoch keine Bewertungen

- (1 Mark Each) : Programming in CDokument12 Seiten(1 Mark Each) : Programming in CMaheNoch keine Bewertungen

- C++ Questions & Answers JECRC UniversityDokument31 SeitenC++ Questions & Answers JECRC UniversityAnonymous BOreSF0% (1)

- Java Script-McqDokument31 SeitenJava Script-McqSatish Kumar100% (1)

- MPMCDokument11 SeitenMPMCDEEPNoch keine Bewertungen

- PPSC Lecturer Computer Science Questions & AnswersDokument14 SeitenPPSC Lecturer Computer Science Questions & AnswersMuhammad Sikandar DarNoch keine Bewertungen

- Digital Electronics MCQ Objective QuestionsDokument23 SeitenDigital Electronics MCQ Objective QuestionsMs. Bhavini KumawatNoch keine Bewertungen

- Computer Organisation and Architecture MCQ Part 1Dokument5 SeitenComputer Organisation and Architecture MCQ Part 1Vimeno DolieNoch keine Bewertungen

- IT430 Ecommerce Mcqs VuabidDokument6 SeitenIT430 Ecommerce Mcqs Vuabidsaeedsjaan100% (1)

- Microprocessor Question BankDokument67 SeitenMicroprocessor Question BankArpit SNoch keine Bewertungen

- Algorithm and Programming Language MCQ'SDokument25 SeitenAlgorithm and Programming Language MCQ'SGuruKPO100% (3)

- Com113 Exams Ques 2023Dokument4 SeitenCom113 Exams Ques 2023ISYAKU KABIRU ALFANoch keine Bewertungen

- DLF 2 Mark Question BanksDokument5 SeitenDLF 2 Mark Question Banksmeenakshisankar2013100% (1)

- MCQ Computer Network PDFDokument3 SeitenMCQ Computer Network PDFMeenal GuptaNoch keine Bewertungen

- PPSC Computer Science Lecturer 2015 (68 Question With Answer)Dokument9 SeitenPPSC Computer Science Lecturer 2015 (68 Question With Answer)farwa jabinNoch keine Bewertungen

- Networking QuestionsDokument1.074 SeitenNetworking QuestionsAshar ShaikhNoch keine Bewertungen

- All McqsDokument52 SeitenAll McqsimranNoch keine Bewertungen

- Data Structure Questions and Answers - Stack OperationsDokument10 SeitenData Structure Questions and Answers - Stack OperationsM Naveed ShakirNoch keine Bewertungen

- C_LANGUAGE_MCQDokument18 SeitenC_LANGUAGE_MCQYesudasNoch keine Bewertungen

- MCQ's On CDokument20 SeitenMCQ's On CJashmitha Sai KakavakamNoch keine Bewertungen

- Computer Graphics MCQDokument23 SeitenComputer Graphics MCQBobby DeolNoch keine Bewertungen

- B. To Reduce The Size of Data To Save SpaceDokument25 SeitenB. To Reduce The Size of Data To Save SpaceAashi Neha100% (1)

- Computer Architecture McqsDokument10 SeitenComputer Architecture McqsSatsshhNoch keine Bewertungen

- 6102 C Language Mca MCQDokument93 Seiten6102 C Language Mca MCQNISHANTNoch keine Bewertungen

- Controllers and Automation Systems ExplainedDokument11 SeitenControllers and Automation Systems ExplainedravihbtiNoch keine Bewertungen

- 100 TOP COMPUTER NETWORKS Multiple Choice Questions and Answers COMPUTER NETWORKS Questions and Answers PDFDokument21 Seiten100 TOP COMPUTER NETWORKS Multiple Choice Questions and Answers COMPUTER NETWORKS Questions and Answers PDFvaraprasad_ganjiNoch keine Bewertungen

- Cs601 700SolvedMCqsDokument128 SeitenCs601 700SolvedMCqsLincolnNoch keine Bewertungen

- COA Chapter 1 NotesDokument14 SeitenCOA Chapter 1 NotesAmitesh ki class For engineeringNoch keine Bewertungen

- Compiler Mcqs (Org)Dokument39 SeitenCompiler Mcqs (Org)M ShahidNoch keine Bewertungen

- Multiple Choice QuestionsDokument10 SeitenMultiple Choice QuestionsSanjeev Chaudhary100% (1)

- Operating Systems (MCQ)Dokument26 SeitenOperating Systems (MCQ)Mian Hasham Azhar AZHARNoch keine Bewertungen

- Network Fundamentals Quiz with AnswersDokument9 SeitenNetwork Fundamentals Quiz with AnswersShenbaga VengatNoch keine Bewertungen

- MCQ 2Dokument122 SeitenMCQ 2laxmi bagade100% (1)

- STET - 2019: Important Question Based On Exam PatternDokument42 SeitenSTET - 2019: Important Question Based On Exam PatternAtul Prakash DwivediNoch keine Bewertungen

- Css MCQDokument55 SeitenCss MCQShrajit GuptaNoch keine Bewertungen

- Microprocessor MCQ CS 2nd YearDokument80 SeitenMicroprocessor MCQ CS 2nd YearMohit SinghNoch keine Bewertungen

- C FILE I/O and Preprocessor Objective QuestionsDokument12 SeitenC FILE I/O and Preprocessor Objective QuestionsPraveer SrivastavaNoch keine Bewertungen

- Typical Questions & AnswersDokument82 SeitenTypical Questions & AnswersSudip PaulNoch keine Bewertungen

- C LanguageDokument3 SeitenC Languageabhizz dwivediNoch keine Bewertungen

- DS ALL MCQsDokument196 SeitenDS ALL MCQsnilesh gagareNoch keine Bewertungen

- Private constructor ensures single instanceDokument7 SeitenPrivate constructor ensures single instanceAnonymous E8ETvFNoch keine Bewertungen

- Home AutomationDokument27 SeitenHome AutomationK.anirudh SinghNoch keine Bewertungen

- DLD McqsDokument36 SeitenDLD Mcqspunjabiangem100% (2)

- Ch-3- QuestionsDokument6 SeitenCh-3- QuestionsSal FozilovNoch keine Bewertungen

- Final Revision LogicDokument66 SeitenFinal Revision LogicKirillus MaherNoch keine Bewertungen

- MCQ Questions For Chapter 1 in Digital DesignDokument10 SeitenMCQ Questions For Chapter 1 in Digital DesignRasha SamourNoch keine Bewertungen

- Ahmed Abdi Kosar Exam ResultsDokument2 SeitenAhmed Abdi Kosar Exam Resultsali teneg100% (1)

- Digital Hardware HW2Dokument4 SeitenDigital Hardware HW2Thamer MohammedNoch keine Bewertungen

- Digital Electronics MCQ by Ratnesh SirDokument13 SeitenDigital Electronics MCQ by Ratnesh SirAyush Gupta 4-Year B.Tech. Electrical EngineeringNoch keine Bewertungen

- Screenshot 2023-05-23Dokument6 SeitenScreenshot 2023-05-23Nidhi NarayanNoch keine Bewertungen

- Model Question Paper Subject Code: BC0036 Subject Name: Digital Systems Credits: 4 Marks: 140 Part A (One Mark Questions)Dokument16 SeitenModel Question Paper Subject Code: BC0036 Subject Name: Digital Systems Credits: 4 Marks: 140 Part A (One Mark Questions)velmuruganNoch keine Bewertungen

- QA New 2Dokument37 SeitenQA New 2truong nguyenNoch keine Bewertungen

- Egnosi Regi.Dokument2 SeitenEgnosi Regi.niraliNoch keine Bewertungen

- Pro-E - CreoDokument4 SeitenPro-E - CreoNIRALINoch keine Bewertungen

- Acknowledgment Receipt 1408009474 PDFDokument1 SeiteAcknowledgment Receipt 1408009474 PDFNIRALINoch keine Bewertungen

- Impact of gender composition on team processes and performanceDokument9 SeitenImpact of gender composition on team processes and performanceNIRALINoch keine Bewertungen

- Programming in HTML 5 With Javascript and Css 3: Duration: 2 MNTH FEES: 10000Dokument1 SeiteProgramming in HTML 5 With Javascript and Css 3: Duration: 2 MNTH FEES: 10000NIRALINoch keine Bewertungen

- Software Developer ResumeDokument3 SeitenSoftware Developer ResumeNIRALINoch keine Bewertungen

- Candidate Examination Attendance SheetDokument2 SeitenCandidate Examination Attendance SheetNIRALI100% (1)

- Advanced Web DesignDokument9 SeitenAdvanced Web DesignNIRALINoch keine Bewertungen

- 6th Central Pay Commission Salary CalculatorDokument15 Seiten6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Standardized SOP Process Benefits Fortune SolutionsDokument3 SeitenStandardized SOP Process Benefits Fortune SolutionsNIRALINoch keine Bewertungen

- SPRING 2016 Mba - Sem 3 MB0050 Research Methodology B1700 4 60Dokument2 SeitenSPRING 2016 Mba - Sem 3 MB0050 Research Methodology B1700 4 60NIRALINoch keine Bewertungen

- Advanced Web DesignDokument9 SeitenAdvanced Web DesignNIRALINoch keine Bewertungen

- AYAZ A Study of Rural Banking in IndiaDokument5 SeitenAYAZ A Study of Rural Banking in IndiaNIRALINoch keine Bewertungen

- PHP Basic To Advanced ContentDokument5 SeitenPHP Basic To Advanced ContentNIRALINoch keine Bewertungen

- Project Synopsis Guide FormDokument3 SeitenProject Synopsis Guide FormNIRALINoch keine Bewertungen

- C++ Programming CONTENT (TCJ) : Batch Time: Batch Start DT.: Faculty: Batch End Dt.Dokument1 SeiteC++ Programming CONTENT (TCJ) : Batch Time: Batch Start DT.: Faculty: Batch End Dt.NIRALINoch keine Bewertungen

- Programming in HTML 5 With Javascript and Css 3: Duration: 2 MNTH FEES: 10000Dokument1 SeiteProgramming in HTML 5 With Javascript and Css 3: Duration: 2 MNTH FEES: 10000NIRALINoch keine Bewertungen

- Conm MCQDokument21 SeitenConm MCQNIRALINoch keine Bewertungen

- Company LetterDokument4 SeitenCompany LetterNIRALINoch keine Bewertungen

- Bcgeu 19 Placement Part Time or Lower Classn PositionDokument3 SeitenBcgeu 19 Placement Part Time or Lower Classn PositionnajiNoch keine Bewertungen

- C Programming CONTENT (TCJ) : Srno. DAY Course Date Remar K UNIT-1Dokument2 SeitenC Programming CONTENT (TCJ) : Srno. DAY Course Date Remar K UNIT-1NIRALINoch keine Bewertungen

- C Programming CONTENT (TCJ) : Srno. DAY Course Date Remar K UNIT-1Dokument2 SeitenC Programming CONTENT (TCJ) : Srno. DAY Course Date Remar K UNIT-1NIRALINoch keine Bewertungen

- BBA Project GuidelinesDokument32 SeitenBBA Project GuidelinesManish KumarNoch keine Bewertungen

- Fundamental of ITDokument22 SeitenFundamental of ITNIRALINoch keine Bewertungen

- C++ Programming CONTENT (TCJ) : Batch Time: Batch Start DT.: Faculty: Batch End Dt.Dokument1 SeiteC++ Programming CONTENT (TCJ) : Batch Time: Batch Start DT.: Faculty: Batch End Dt.NIRALINoch keine Bewertungen

- Bca 1st Sem. MathsDokument54 SeitenBca 1st Sem. MathsNIRALI50% (16)

- BIT Baroda Institute of Technology: Creo (Pro/ENGINEER) Training atDokument4 SeitenBIT Baroda Institute of Technology: Creo (Pro/ENGINEER) Training atNIRALINoch keine Bewertungen

- Finance MNGT (Tejas Sir New)Dokument29 SeitenFinance MNGT (Tejas Sir New)niraliNoch keine Bewertungen

- Zen Er DiodeDokument2 SeitenZen Er DiodeRanjan KumarNoch keine Bewertungen

- Question Bank - Digital Logic CircuitDokument14 SeitenQuestion Bank - Digital Logic CircuitthamizmaniNoch keine Bewertungen

- Version 2.1a, 11 Jan 2012: Never Stop ThinkingDokument34 SeitenVersion 2.1a, 11 Jan 2012: Never Stop ThinkingDaniel DominguezNoch keine Bewertungen

- Power Filter Options For The FPD-Link Interfaces in TRAVEO™ T2G FamilyDokument15 SeitenPower Filter Options For The FPD-Link Interfaces in TRAVEO™ T2G Familygshgeje hehjwjeNoch keine Bewertungen

- 8-Channel Dac With PLL and Differential Outputs, 192 KHZ, 24 BitsDokument28 Seiten8-Channel Dac With PLL and Differential Outputs, 192 KHZ, 24 BitsIvan AlyaevNoch keine Bewertungen

- Chapter6b-Combinational Logic Design PracticesDokument38 SeitenChapter6b-Combinational Logic Design PracticesZulkarnineNoch keine Bewertungen

- 01 ECE621 F17 IntroductionDokument24 Seiten01 ECE621 F17 IntroductionAhmed MaGdyNoch keine Bewertungen

- ECE364 Lab Manual Spring 2020Dokument15 SeitenECE364 Lab Manual Spring 2020Rʌʜɘɘɭ AŋsʌʀɩNoch keine Bewertungen

- Pojacalo ManualDokument4 SeitenPojacalo ManualServis ChipoNoch keine Bewertungen

- Power Reduction in Vlsi Systems by Using Multi Bit Flip FlopsDokument12 SeitenPower Reduction in Vlsi Systems by Using Multi Bit Flip FlopsIJMTERNoch keine Bewertungen

- A New Level-Up Shifter For High Speed and Wide Range Interface in Ultra Deep Sub-MicronDokument3 SeitenA New Level-Up Shifter For High Speed and Wide Range Interface in Ultra Deep Sub-MicronXavier DannyNoch keine Bewertungen

- Methods of Analysis - Kirchoff's LawDokument26 SeitenMethods of Analysis - Kirchoff's LawDaniel SetiawanNoch keine Bewertungen

- FPGA-Arch CPLD Design April2012Dokument112 SeitenFPGA-Arch CPLD Design April2012Moazzam HussainNoch keine Bewertungen

- 8086 and Memory Interfacing - FinalDokument28 Seiten8086 and Memory Interfacing - FinalAnushkaSinha100% (2)

- P2003EVG Niko-Sem: P-Channel Logic Level EnhancementDokument5 SeitenP2003EVG Niko-Sem: P-Channel Logic Level EnhancementNeto CunhaNoch keine Bewertungen

- Cmos Vlsi Design - 2019 Syllabus, Course OutcomesDokument1 SeiteCmos Vlsi Design - 2019 Syllabus, Course OutcomesDinesh GaikotiNoch keine Bewertungen

- Adrv 9002Dokument92 SeitenAdrv 9002rajNoch keine Bewertungen

- Hef4066bf 4 Bilateral SwitchDokument9 SeitenHef4066bf 4 Bilateral SwitchhuvillamilNoch keine Bewertungen

- FM Receiver Circuit DesignDokument26 SeitenFM Receiver Circuit DesignVs Varun Sardana100% (4)

- Plugin LF351Dokument8 SeitenPlugin LF351mark777markNoch keine Bewertungen

- KH Distributors - Electronic Components - PriceListJan2009Dokument30 SeitenKH Distributors - Electronic Components - PriceListJan2009ryan780926Noch keine Bewertungen

- PAMDokument11 SeitenPAMMarco Alejandro Teran AguilarNoch keine Bewertungen

- Análise Nodal e de MalhasDokument13 SeitenAnálise Nodal e de MalhasYu YanNoch keine Bewertungen

- Electronic A Digital Integrated Circuits - M.C. SharmaDokument116 SeitenElectronic A Digital Integrated Circuits - M.C. SharmaEnya Andrea Ribba Hernandez100% (1)

- Design of High Speed & Power Optimized Sense Amplifier Using Deep Nano CMOS VLSI TechnologyDokument8 SeitenDesign of High Speed & Power Optimized Sense Amplifier Using Deep Nano CMOS VLSI TechnologyIJRASETPublicationsNoch keine Bewertungen

- UNIT3Dokument41 SeitenUNIT3Azliana Mohd TaibNoch keine Bewertungen

- Digital Letter Box Project ReportDokument7 SeitenDigital Letter Box Project ReportMoyammir HaiderNoch keine Bewertungen

- Transistor Level STA With NanoTimeDokument10 SeitenTransistor Level STA With NanoTimeStudentNoch keine Bewertungen

- ELE629 Assignment#1Dokument2 SeitenELE629 Assignment#1dean07Noch keine Bewertungen