Beruflich Dokumente

Kultur Dokumente

Sistema transmisión digital

Hochgeladen von

Daniel LindoOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Sistema transmisión digital

Hochgeladen von

Daniel LindoCopyright:

Verfügbare Formate

LOGO

Redes de Telecomunicaciones

Unidad 3 Sistema de Transmisin Digital

Parte 1

UNIVERSIDAD NACIONAL DE INGENIERIA

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

DEPARTAMENTO DE SISTEMAS DIGITALES Y TELECOMUNICACIONES

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Objetivo

Reconocer la aplicabilidad

de los diversos medios de

acceso a las redes de

comunicaciones

las tcnicas de

codificacin

multiplexacin digital

consecuencias entre

utilizar un mtodo u otro.

servicios

telecomunicaciones

fijos y mviles

banda base y banda

ancha

Usando tecnologas ms

adecuada

Identificar los elementos

y tecnologas utilizadas en

el sistema de transmisin

digital

Sistema de Transmisin Digital

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Contenido

La red de transporte

Multiplexacin de Canales

Sistema de Multiplexacin PCM de orden superior

La red de acceso

Sistema de Transmisin Digital

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

La red de transporte

Sistema de Transmisin Digital

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

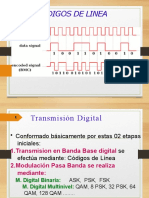

La Red de Transporte

Modulacin

de Cdigo

de Pulso

(PCM)

Codificacin

de Lnea

Sistema de Transmisin Digital

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Modulacin de Pulsos Codificados (PCM)

Tcnica utilizada en un sistema de

transmisin digital.

Sistema de Transmisin Digital

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Velocidad de Transmisin PCM

PCM se lleva a cabo

en dos pasos:

Ocurre un error de

cuantificacin

La seal analgica es muestreada 8,000 veces por

segundo.

La altura de pulso es convertida a un valor digital.

Diferencias entre el valor real y el cuantificado.

La velocidad de

muestreo basada en

Nyquist

La mxima frecuencia de la seal es 4000 Hz x 2

= 8000 Hz.

Velocidad de

Transmisin

8,000 muestras por segundo x 8 bits por muestra

= 64,000 bps.

Se conoce como DS-0 (Digital Signal Level Zero)

Sistema de Transmisin Digital

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Codificador PCM

Sistema de Transmisin Digital

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Decodificador PCM

Sistema de Transmisin Digital

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

DPCM: Modulacin Delta

Es un caso especial de conversin de seales analgicas en el cual

solo se utiliza un bit por muestreo con la diferencia de la seal.

Requiere un muestreo mayor que PCM.

Un problema que se puede presentar cuando existen cambios rpidos

en la entrada y la seal de salida digital no puede seguir estos

cambios.

Sistema de Transmisin Digital

10

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

CODIFICACIN DEL LNEA

Sistema de Transmisin Digital

11

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Codificacin Digital NRZ

Non Return to Zero: El voltaje permanece constante (no

regresa a cero) durante el tiempo en que un bit es

transmitido.

Manteniendo la seal sin cambios no facilita la sincronizacin

entre el dispositivo transmisor y el receptor.

Sistema de Transmisin Digital

12

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Codificacin Manchester

Usa cambios de seal para mantener el dispositivo

receptor y el transmisor sincronizados.

O = Cambio de alto a bajo y 1 = Cambio de bajo a alto

Sistema de Transmisin Digital

13

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Codificacin Manchester Diferencial

Similar al Manchester, pero el valor de 0 y 1 se define al inicio

del intervalo.

O = Complemento de seal al inicio del intervalo y 1 = Se

mantiene la seal al inicio del intervalo.

Evita problemas ocasionados al invertir la conexin de cables.

No se debe indicar cual es el cable de alto voltaje y esto hace

el cable menos caro.

Sistema de Transmisin Digital

14

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Codificacin AMI

AMI (Alternate Mark Inversion): Se traduce como Inversin

de Marcas Alternadas y es utilizado en portadoras T1.

En este sistema de codificacin bipolar, O (space) =

Ausencia de pulso y 1 (mark) = pulsos que se van alternando.

Evita problemas ocasionados al invertir la conexin de cables.

No se debe indicar cual es el cable de alto voltaje y esto hace

el cable menos caro.

Sistema de Transmisin Digital

15

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Ventajas de Codificacin AMI

Elimina la energa CD (corriente directa).

Fuerte presencia de seal de reloj

Detection de error.

Requerimientos segn ANSI T1.403

La seal del reloj es recuperada si hay suficiente densidad de unos. No

pueden haber ms de 15 ceros consecutivos.

Al menos N unos en cada ventana de 8*(N+1) intervalos de tiempo

(donde N puede ser 1-23)

El mtodo mas comn para asegurar un promedio de

densidad de unos aceptables es el Bipolar con Sustiticin

de 8 ceros (B8ZS, Bipolar with Eight Zero Substitution).

Sistema de Transmisin Digital

16

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Codificacin B8ZS

Si el pulso precediendo 8 ceros es positivo, el B8ZS enva 0 0 0 + - 0 +. Si el pulso precediendo 8 ceros es negativo, el B8ZS enva 0 0 0 - +

0 + -.

La deteccin de este cdigo es detectando un cdigo de 8 bits con dos

violaciones bipolares.

Sistema de Transmisin Digital

17

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Codificacin HDB3

Mtodo de codificacin recomendado para portadoras E1 (CCITT), llamado

HDB3 (High Density Bipolar order 3 substitution). No permite ms de tres ceros

consecutivos.

Cada 4 ceros consecutivos es reemplazado por 000V (V=pulso violando reglas

AMI) cuando el nmero de pulsos despus de la ltima violacin de reglas es

impar y B00V (B=pulso siguiendo reglas AMI) cuando el nmero de pulsos es

par.

Sistema de Transmisin Digital

18

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Multiplexacin de Canales

Sistema de Transmisin Digital

19

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

SISTEMAS DE MULTIPLEXACIN

Diseados para manejar seales PCM de alta

velocidad.

Sistema de Portadora T1 y E1

PCM de Orden Superior

SONET, Red ptica Sncrona de ANSI

SDH, Jerarqua Digital Sncrona de ITU

Sistema de Transmisin Digital

20

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Sistema de Portadora T1

Es un sistema, tambin referido como DS1, capaz de transmitir una seal digital

a velocidad de hasta 1.544 Mbps (Usado en Norte Amrica y Japn)

Un marco contiene 24 canales DS0 que se repite 8000 veces en un segundo que

es la frecuencia de muestreo de PCM.

Cada marco contiene un bit de

sincronizacin.

(24 canales * 8 bits + 1 bit) *8,000 = 193 bit en un marco x 8,000 = 1,544 Kbps

Cada canal produce 7 bits de datos y 1 bit de control por muestra, por lo tanto hay

7 x 8000 = 56,000 bps de datos por canal y 56K x 24 = 1.344 Mbps en total.

Sistema de Transmisin Digital

21

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Diagrama Simplificado de un Codec PCM T1

Sistema de Transmisin Digital

22

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Sistema de Portadora E1

Es un sistema recomendado por la CCITT capaz de transmitir una

seal digital a velocidad de hasta 2.048 Mbps. (Usado en Europa e

Internacionalmente)

Sistema de Transmisin Digital

23

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Estructura de Portadora E1

Un marco contiene 32 canales que se repite 8000 veces en un

segundo que es la frecuencia de muestreo de PCM. Cada

marco contiene un canal de sincronizacin y otro de

sealizacin.

(32 canales * 8 bits) *8,000 = 256 bit en un marco x 8,000 = 2,048 Kbps

Solo 30 canales son utilizados para datos, por lo tanto hay

8 x 8000=64,000 bps de datos por canal y 64K x 30 = 1.92 Mbps en total.

Sistema de Transmisin Digital

24

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Secuencia de Tramas E1

Sistema de Transmisin Digital

25

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Estructura de multitramas (2.048 Mbps)

Sistema de Transmisin Digital

26

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Sistema de Multiplexacin PCM de orden

superior

Sistema de Transmisin Digital

27

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Jerarquas de Orden Superior

La jerarqua PCM es desarrollada basada en 24 o 30 grupos de canales, los

cuales son llamados nivel 1. Niveles siguientes han sido desarrollados

Sistema de Transmisin Digital

28

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

PCM de Orden Superior (PDH)

En la tabla se muestra y compara estos niveles de multiplexacin:

Norteamrica

Nivel

Circuitos

Mbit/s

Europa

Denom

inacin

Circuito

s

Japn

Mbit/s

Denomi

nacin

Circuitos

Mbit/s

Deno

minac

in

24

1,544

(T1)

30

2,048

(E1)

24

1,544

(J1)

96

6,312

(T2)

120

8,448

(E2)

96

6,312

(J2)

672

44,736

(T3)

480

34,368

(E3)

480

32,064

(J3)

4032

274,176

(T4)

1920

139,264

(E4)

1440

97,728

(J4)

Por simple multiplicacin se puede ver que la velocidad de orden

superior es un mltiplo de la velocidad inferior ms algunos bits.

Estos bits adicionales son para sincronizacin y enmarcado (relleno

de bits).

PDH: Jerarqua Digital Pleosncrona

Sistema de Tran22smisin Digital

29

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Jerarqua PCM Norte Americana

Nivel

Sistema de Transmisin Digital

Norteamrica

Circuitos

Mbit/s

Denominacin

24

1,544

(T1)

96

6,312

(T2)

672

44,736

(T3)

4032

274,176

(T4)

30

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Jerarqua PCM Internacional

Nivel

Circuitos

Mbit/s

Denominacin

30

2,048

(E1)

120

8,448

(E2)

480

34,368

(E3)

1920

139,264

(E4)

Sistema de Transmisin Digital

31

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Drop-Insert

En un sistema

de transmisin de varios

canales, drop-insert es un

proceso que

por ejemplo, en una

ranura de tiempo o banda

de frecuencia, antes

ocupado por la

seal desviada.

se desva (drops) una

porcin de la seal

multiplexada agregada en

un punto intermedio, e

introduce (Insert) una

seal diferente para su

posterior transmisin en

la misma posicin,

Sistema de Transmisin Digital

32

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Proceso de Drop/Insert en PDH

ETL Equipo

Terminal de Lnea

Sistema de Transmisin Digital

33

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Jerarqua Digital Sncrona

SONET: Synchronous Optical Network (USA y Canada)

SDH: Synchronous Digital Hierarchy (resto del mundo)

Las tramas tributarias de las seales de lnea pueden ser subdivididas para acomodar

cargas pleosincronas, trfico ATM o unidades de menor orden.

Esto supone mezclar trfico de distinto tipo dando lugar a redes flexibles y ms fcil

administracin .

Sistema de Transmisin Digital

34

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

SONET

Define las caractersticas y funcionabilidad de un sistema de

transporte basados en los principios de multiplexacin sincrnica.

Es capaz de transportar todas las seales tributarias que han sido

definidas en las redes digitales actuales.

Sistema de Transmisin Digital

35

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

SONET Estructura de STS-1

SONET consiste en una estructura bsica llamada STS-1 (seal sncrona de

transporte) organizada en una estructura de marcos.

En la estructura de 9 filas por 90 columnas, las tres columnas de la izquierda

son utilizadas para el encabezado de transporte restando un rea de 9 filas por

87 columnas para carga til.

Sistema de Transmisin Digital

36

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Estructura del SONET

La carga til a la vez contiene tres columnas, una para el encabezado

de comunicacin (para comunicar varias piezas de informacin) y dos

de relleno de bits

Sistema de Transmisin Digital

37

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Relleno de bits (bit stuffing)

Qu es?

Es el proceso de cambiar la velocidad de una seal digital de una manera

controlada de forma que pueda ir acorde con una velocidad diferente de su

propia velocidad original sin prdida de informacin, generalmente.

Por qu es necesario?

debido a que se deben multiplexar diferentes seales (o tributarios) con relojes

de transmisin diferentes (dentro de un determinado grado de tolerancia).

Cmo se implementa?

Se suman ranuras de tiempo a cada seal en suficiente cantidades para hacer

que la seal opere a una precisa velocidad operada por un reloj comn.

Pulsos son insertados (o rellenados) en estas ranuras sin informacin alguna.

Cmo se eliminan estos bits en el otro extremo?

Se codifica la seal de tal manera que esos bits de informacin nula puedan

ser reconocidos y removidos en la otra terminal (de-multiplexados)

Sistema de Transmisin Digital

38

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Tributarios Virtuales

Cuatro tamaos para acomodar sub-velocidades STS-1 como

T1 y E1.

Un STS-1 puede acomodar hasta 21 seales E1 y 28 seales

T1.

Sistema de Transmisin Digital

39

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Proceso de Ensamblaje y Desemsamblaje

La capacidad de carga til es siempre mayor que lo que requiere el

tributario, entonces el mapeo necesario para sincronizar la velocidad

del tributario con la capacidad de la carga til se logra sumando bits

de relleno.

Sistema de Transmisin Digital

40

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

SDH

SDH fue un desarrollo Europeo (CCITT) con una velocidad bsica de transmisin llamada

STM-1 (155.52 Mbps) equivalente al STS-3 de SONET.

STM (Mdulo de Transporte Sncrono) es la estructura de informacin que soporte SDH.

STM-1 = 8000 * (270 octetos * 9 filas * 8 bits)= 155 Mbps

STM-4 = 4 * 8000 * (270 octetos * 9 filas * 8 bits)= 622 Mbps

STM-16 = 16 * 8000 * (270 octetos * 9 filas * 8 bits)= 2.5 Gbps

STM-64 = 64 * 8000 * (270 octetos * 9 filas * 8 bits)= 10 Gbps

STM-256 = 256 * 8000 * (270 octetos * 9 filas * 8 bits)= 40 Gbps

Sistema de Transmisin Digital

2-41

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Drop-Insert en SDH

Proceso que SDH utiliza

para agregar informacin a las

tramas

Este mecanismo examina las tramas y tiene la funcionalidad

de retirar o insertar informacin de ellas.

Sistema de Transmisin Digital

42

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Estructura bsica SDH y Drop/Insert

Sistema de Transmisin Digital

Redes

Telecomunicacione

s

2-43

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Multiplexaje Sncrono

VC: Contenedor

Virtual

TU: Unidad de

Tributario

TUG: Grupo de

unidades

tributarias.

AU: Unidad

Administrativa

AUG: Grupo de

unidades

administrativas

Sistema de Transmisin Digital

44

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Ventajas de SDH

El proceso de

multiplexacin

es mucho ms

directo.

Sistema de Transmisin Digital

Las tramas

tributarias de las

seales de lnea,

denominadas

contenedores

virtuales (VC)

pueden ser

subdividas para

acomodar cargas

plesicronas,

trfico ATM.

El procesamiento

de la seal se

lleva a cabo a

nivel de STM-1

45

Compatibilidad

elctrica y ptica

entre los equipos

de los distintos

suministradores

Redes Telecomunicaciones

FACULTAD DE ELECTROTECNIA Y COMPUTACIN

Clase Prctica Transmisin Digital

Cuntos T1 adicionales pueden ser transportados por una

seal STS-1 que ya est transportando cinco seales E1?

Justifique mostrando todos los clculos necesarios.

Cuntos E1 adicionales pueden

ser transportados por una

seal STS-1 que ya est transportando seis seales T1?

Justifique mostrando todos los clculos necesarios.

Mencione que ventaja tiene el proceso de Drop/Insert de

SDH con respecto a PDH.

LOGO

Das könnte Ihnen auch gefallen

- Prácticas de redes de datos e industrialesVon EverandPrácticas de redes de datos e industrialesBewertung: 4 von 5 Sternen4/5 (5)

- Tema 6Dokument20 SeitenTema 6lagarto_dNoch keine Bewertungen

- UF1874 - Mantenimiento de la infraestructura de la red de comunicacionesVon EverandUF1874 - Mantenimiento de la infraestructura de la red de comunicacionesNoch keine Bewertungen

- Curso: Telecomunicaciones III FundamentosDokument72 SeitenCurso: Telecomunicaciones III FundamentoscarmenNoch keine Bewertungen

- Telecomunicaciones. Tecnologías, Redes y Servicios. 2ª Edición actualizadaVon EverandTelecomunicaciones. Tecnologías, Redes y Servicios. 2ª Edición actualizadaBewertung: 4.5 von 5 Sternen4.5/5 (3)

- PCMDokument10 SeitenPCMAntito PotterNoch keine Bewertungen

- Estructura de La PSTNDokument32 SeitenEstructura de La PSTNleloma50% (2)

- Teleprocesamiento Transmision DigitalDokument13 SeitenTeleprocesamiento Transmision DigitalSergio HerreraNoch keine Bewertungen

- Curso Enlaces DigitalesDokument130 SeitenCurso Enlaces Digitalesprueba100Noch keine Bewertungen

- 68 ManchesterDokument1 Seite68 ManchesterEduardo FloresNoch keine Bewertungen

- Comunicaciones de Datos: Elementos, Transmisión y TecnologíasDokument73 SeitenComunicaciones de Datos: Elementos, Transmisión y Tecnologíasmesi leonelNoch keine Bewertungen

- Telefonia Rpuebas1234Dokument16 SeitenTelefonia Rpuebas1234Denn RualesNoch keine Bewertungen

- Códigos de línea digitales optimizados para transmisiónDokument70 SeitenCódigos de línea digitales optimizados para transmisiónFreddy BarbosaNoch keine Bewertungen

- Sistemas de Telecomunicación Analógicos y DigitalesDokument136 SeitenSistemas de Telecomunicación Analógicos y Digitalesisrael_zamora6389Noch keine Bewertungen

- PDH y SDHDokument53 SeitenPDH y SDHGlendaCernaNoch keine Bewertungen

- Codificación Banda Base, Detección y Corección de ErrorDokument42 SeitenCodificación Banda Base, Detección y Corección de ErrorRonald Vasquez CarocaNoch keine Bewertungen

- TDMoIP, tecnología para el transporte de tráfico TDM sobre IPDokument14 SeitenTDMoIP, tecnología para el transporte de tráfico TDM sobre IPalbert_agelvizNoch keine Bewertungen

- CM CdmaDokument6 SeitenCM CdmaR Wiliam LMNoch keine Bewertungen

- Redes y Comunicaciones - Conceptos básicos de modulación y códigosDokument61 SeitenRedes y Comunicaciones - Conceptos básicos de modulación y códigoscdkueaNoch keine Bewertungen

- PDH y SDH: Transmisión Plesiócrona y SíncronaDokument59 SeitenPDH y SDH: Transmisión Plesiócrona y SíncronaRosa Ch100% (2)

- Circuito T-Carrier y E-CarrierDokument13 SeitenCircuito T-Carrier y E-CarrierRichard Alberto Llanos CortezNoch keine Bewertungen

- Comunica C I On SerialDokument39 SeitenComunica C I On SerialMabel Lorena Ochoa ContrerasNoch keine Bewertungen

- Curso básico SDH menos deDokument193 SeitenCurso básico SDH menos deLuis Angel GRNoch keine Bewertungen

- Redes de Transporte - sdh.V5 R2Dokument96 SeitenRedes de Transporte - sdh.V5 R2Vinny MalizaNoch keine Bewertungen

- Tecnologias WAN TDMDokument41 SeitenTecnologias WAN TDMJoel AguileraNoch keine Bewertungen

- Modulacion Digital FSK, PSK y QAM Este 3333333Dokument264 SeitenModulacion Digital FSK, PSK y QAM Este 3333333Sergio Granados QuezadaNoch keine Bewertungen

- Comunicación serie: introducción a estándares, interfaces y conexionesDokument38 SeitenComunicación serie: introducción a estándares, interfaces y conexionespereira26Noch keine Bewertungen

- 1 Fundamentos de Los Sistemas de Telecomunicaciones 1Dokument36 Seiten1 Fundamentos de Los Sistemas de Telecomunicaciones 1edison matiasNoch keine Bewertungen

- Generador de CodigoDokument7 SeitenGenerador de CodigoJAVIER GOMEZNoch keine Bewertungen

- Guia de Estucio U4Dokument7 SeitenGuia de Estucio U4carlos noelNoch keine Bewertungen

- Transmisión Digital y CódigosDokument51 SeitenTransmisión Digital y CódigosfrancofoNoch keine Bewertungen

- parctica 6 sistema de comunicacionDokument10 Seitenparctica 6 sistema de comunicacionDairy FuentesNoch keine Bewertungen

- Técnicas MIC (Modulacion de Impulsos Codificados)Dokument12 SeitenTécnicas MIC (Modulacion de Impulsos Codificados)_laguardiaNoch keine Bewertungen

- 3 0 0 Tecbared Introcom 01 2023 - 1Dokument61 Seiten3 0 0 Tecbared Introcom 01 2023 - 1Patricia Lorena SandovalNoch keine Bewertungen

- 4 El Puerto Serie USART PICDokument39 Seiten4 El Puerto Serie USART PICjpazmiño_25Noch keine Bewertungen

- Indigitalprotocolss 6Dokument51 SeitenIndigitalprotocolss 6Aaron VllarrealNoch keine Bewertungen

- Codigo ManchesterDokument4 SeitenCodigo ManchesterBanis SolloyNoch keine Bewertungen

- SEÑALESDokument33 SeitenSEÑALESLUISA FERNANDA GELVEZ HERNANDEZNoch keine Bewertungen

- Capitulo IVDokument9 SeitenCapitulo IVGeovanny GabrielNoch keine Bewertungen

- Laboratorio 4 de Sistemas de Comunicación Digital IDokument8 SeitenLaboratorio 4 de Sistemas de Comunicación Digital IAndrésEduardoMartinezNoch keine Bewertungen

- Redes Convergentes Semana 11 - 2020Dokument63 SeitenRedes Convergentes Semana 11 - 2020Luis Almiron CcasaniNoch keine Bewertungen

- U4.U5.U6.Transmisión Digital y Mux. BorrarDokument53 SeitenU4.U5.U6.Transmisión Digital y Mux. BorrarYael RiveroNoch keine Bewertungen

- Trabajo Escrito TransmisoresDokument66 SeitenTrabajo Escrito TransmisoresSamuel Arizmendi MartínezNoch keine Bewertungen

- 2B3Q 4B3Q TelecomunicacionesDokument6 Seiten2B3Q 4B3Q TelecomunicacionesandresNoch keine Bewertungen

- Onda Portadora PDFDokument14 SeitenOnda Portadora PDFjazz217Noch keine Bewertungen

- PDH SDH UnsaacDokument98 SeitenPDH SDH UnsaacAlexander ChecyaNoch keine Bewertungen

- Lecture 9 Codificación de Línea y PSDDokument65 SeitenLecture 9 Codificación de Línea y PSDisrael_zamora6389Noch keine Bewertungen

- Transmicion de DatosDokument17 SeitenTransmicion de DatosBen DerNoch keine Bewertungen

- Alarcon Reyes Jeferson-2017043863Dokument3 SeitenAlarcon Reyes Jeferson-2017043863Nagib FernándezNoch keine Bewertungen

- Medios Alambricos y PSTNDokument39 SeitenMedios Alambricos y PSTNpatycillarNoch keine Bewertungen

- Circuitos T-Carrier y E-Carrier para transmisión de vozDokument13 SeitenCircuitos T-Carrier y E-Carrier para transmisión de vozjorgeNoch keine Bewertungen

- PAR - UT3 - Medios Físicos de TransmisiónDokument60 SeitenPAR - UT3 - Medios Físicos de TransmisiónmapazazelNoch keine Bewertungen

- Grupo41 Tarea4Dokument20 SeitenGrupo41 Tarea4Ever Castañeda50% (2)

- Codigos de LineaDokument5 SeitenCodigos de LineaErnesto Pinedo CastilloNoch keine Bewertungen

- 2 InstrumentaciónDokument45 Seiten2 InstrumentaciónPaul RiveraNoch keine Bewertungen

- Compuertas Logicas y Decodificador 7 SegmentosDokument11 SeitenCompuertas Logicas y Decodificador 7 SegmentossulmargaritaNoch keine Bewertungen

- Codificador Y DecodificadorDokument8 SeitenCodificador Y Decodificadorjairo alfonsoNoch keine Bewertungen

- Codificador Y DecodificadorDokument8 SeitenCodificador Y Decodificadorjairo alfonso0% (1)

- Tema 8Dokument12 SeitenTema 8David Lopez DelgadoNoch keine Bewertungen

- Codificadores de LíneaDokument22 SeitenCodificadores de LíneaMariela EspinozaNoch keine Bewertungen

- EjerciciosTema1 2 ResueltosDokument4 SeitenEjerciciosTema1 2 ResueltosMayte MerchanNoch keine Bewertungen

- ExamDokument3 SeitenExamadoNoch keine Bewertungen

- Gráfica Interactiva SIA: 1000075Dokument3 SeitenGráfica Interactiva SIA: 1000075Maria Camila Diaz SanchezNoch keine Bewertungen

- 2019-06-26-OFERTA NEGOCIOS v7 Nva PDFDokument61 Seiten2019-06-26-OFERTA NEGOCIOS v7 Nva PDFramiro leonNoch keine Bewertungen

- Prácticas Probadas de IBM Cognos IBM Cognos 8 Como Fuente de Datos para TransformerDokument20 SeitenPrácticas Probadas de IBM Cognos IBM Cognos 8 Como Fuente de Datos para TransformerRoberto BenitezNoch keine Bewertungen

- Instructivo para Elaboracion de Informe de Practica ProfesionalDokument13 SeitenInstructivo para Elaboracion de Informe de Practica Profesionalleec2067% (3)

- Cam WinncDokument11 SeitenCam WinncdavidNoch keine Bewertungen

- Modulo Introduccion Al Sonido en Vivo PDFDokument120 SeitenModulo Introduccion Al Sonido en Vivo PDFFabian Andres GonzalezNoch keine Bewertungen

- Aportes Didácticos para El Trabajo Con La Calculadora en Los Tres Ciclos de La EgbDokument29 SeitenAportes Didácticos para El Trabajo Con La Calculadora en Los Tres Ciclos de La Egbprof_elia@Noch keine Bewertungen

- Cobit - 20160048Dokument1 SeiteCobit - 20160048Gregory FernandezNoch keine Bewertungen

- Mentoria EmprendimientoDokument2 SeitenMentoria EmprendimientopepeNoch keine Bewertungen

- Formatos Basicos de MantenimientoDokument23 SeitenFormatos Basicos de Mantenimientojavierr mendozaNoch keine Bewertungen

- Teorema de Bolzano PDFDokument4 SeitenTeorema de Bolzano PDFAlejandro yumpiriNoch keine Bewertungen

- Lab04 - Transistor TroubleshootingDokument9 SeitenLab04 - Transistor TroubleshootingWanderley Pacco CabreraNoch keine Bewertungen

- Control Presupuestario (FM/BCS)Dokument338 SeitenControl Presupuestario (FM/BCS)Rafael Campo100% (2)

- Silabo de TopografiaDokument6 SeitenSilabo de TopografiaHieremy Ponte MorilloNoch keine Bewertungen

- FASE 2 - Grupo - 8Dokument28 SeitenFASE 2 - Grupo - 8ELIANA DEL CARMEN ASSIA MADERANoch keine Bewertungen

- Blockchain Smartcontracts y Arbitraje ODRDokument45 SeitenBlockchain Smartcontracts y Arbitraje ODRDiego e Rodríguez MurciaNoch keine Bewertungen

- Proyecto 4 Primer GradoDokument70 SeitenProyecto 4 Primer GradoFireXXXNoch keine Bewertungen

- Actividad 2 1Dokument4 SeitenActividad 2 1javier florezNoch keine Bewertungen

- Diseño y Prototipado de Una Incubadora de Huevos de ReptilDokument93 SeitenDiseño y Prototipado de Una Incubadora de Huevos de Reptilchutini0% (1)

- Códigos ConvolucionalesDokument4 SeitenCódigos ConvolucionalesČ Põmã KârîmNoch keine Bewertungen

- P.O.N en Caso de Movimiento TeluricoDokument2 SeitenP.O.N en Caso de Movimiento TeluricoSandra Patricia Castro CarvajalNoch keine Bewertungen

- Loor Cabrera Leonor - Proyecto de GradoDokument26 SeitenLoor Cabrera Leonor - Proyecto de GradoDaniela Dennysse Vega BenavidesNoch keine Bewertungen

- Guia de Instalacion - Acceso DirectoDokument8 SeitenGuia de Instalacion - Acceso DirectoEnrique Isaac Porras PuquioNoch keine Bewertungen

- Descargas Step 7 Varias OpcionesDokument3 SeitenDescargas Step 7 Varias OpcionesFrancisco MartinezNoch keine Bewertungen

- Lab 1 - Redes de ComputadorasDokument35 SeitenLab 1 - Redes de ComputadorasCarmen Esther Mora AvalosNoch keine Bewertungen

- AyDOO-GRADY BOOCHDokument24 SeitenAyDOO-GRADY BOOCHoverhousesNoch keine Bewertungen

- RptBingoBNC 20240126095345-1Dokument1 SeiteRptBingoBNC 20240126095345-1guidmar mendezNoch keine Bewertungen

- 1.2 Permiso de Trabajo en AlturasDokument2 Seiten1.2 Permiso de Trabajo en AlturasMaria Fernanda Saenz PerezNoch keine Bewertungen