Beruflich Dokumente

Kultur Dokumente

74F181

Hochgeladen von

Alejandro Borrego DominguezCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

74F181

Hochgeladen von

Alejandro Borrego DominguezCopyright:

Verfügbare Formate

Revised September 2000

74F181

4-Bit Arithmetic Logic Unit

General Description

Features

The 74F181 is a 4-bit Arithmetic logic Unit (ALU) which can

perform all the possible 16 logic operations on two variables and a variety of arithmetic operations. It is 40% faster

than the Schottky ALU and only consumes 30% as much

power.

Full lookahead for high-speed arithmetic operation on

long words

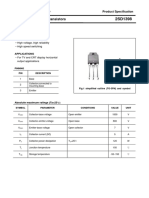

Ordering Code:

Order Number

74F181SC

Package Number

M24B

Package Description

24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

74F181PC

N24A

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-011, 0.600 Wide

74F181SPC

N24C

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter X to the ordering code.

Logic Symbols

Connection Diagram

Active-HIGH Operands

Active-LOW Operands

IEEE/IEC

2000 Fairchild Semiconductor Corporation

DS009491

www.fairchildsemi.com

74F181 4-Bit Arithmetic Logic Unit

April 1988

74F181

Unit Loading/Fan Out

Pin Names

U.L.

Input IIH/IIL

HIGH/LOW

Output IOH/IOL

1.0/3.0

20 A/1.8 mA

Description

A0A3

A Operand Inputs (Active LOW)

B0B3

B Operand Inputs (Active LOW)

1.0/3.0

20 A/1.8 mA

S0S3

Function Select Inputs

1.0/4.0

20 A/2.4 mA

Mode Control Input

1.0/1.0

20 A/0.6 mA

Cn

Carry Input

1.0/5.0

20 A/3.0 mA

50/33.3

1 mA/20 mA

OC (Note 1)/33.3

(Note 1)/20 mA

Carry Generate Output (Active LOW)

50/33.3

1 mA/20 mA

Carry Propagate Output (Active LOW)

50/33.3

1 mA/20 mA

Carry Output

50/33.3

1 mA/20 mA

F0F3

Function Outputs (Active LOW)

A=B

Comparator Output

G

P

Cn + 4

Note 1: OC-Open Collector

Functional Description

devices. Carry lookahead can be provided at various levels

and offers high speed capability over extremely long word

lengths.

The 74F181 is a 4-bit high-speed parallel Arithmetic Logic

Unit (ALU). Controlled by the four Function Select inputs

(S0S3) and the Mode Control input (M), it can perform all

the 16 possible logic operations or 16 different arithmetic

operations on Active HIGH or Active LOW operands. The

Function Table lists these operations.

The A = B output from the device goes HIGH when all four

F outputs are HIGH and can be used to indicate logic

equivalence over four bits when the unit is in the Subtract

mode. The A = B output is open collector and can be wired

AND with other A = B outputs to give a comparison for

more than four bits. The A = B signal can also be used with

the Cn+4 signal to indicate A > B and A < B.

When the Mode Control input (M) is HIGH, all internal carries are inhibited and the device performs logic operations

on the individual bits as listed. When the Mode Control

input is LOW, the carries are enabled and the device performs arithmetic operations on the two 4-bit words. The

device incorporates full internal carry lookahead and provides for either ripple carry between devices using the

Cn + 4 output, or for carry lookahead between packages

using the signals P (Carry Propagate) and G (Carry Generate). In the Add mode, P indicates that F is 15 or more,

while G indicates that F is 16 or more. In the Subtract mode

P indicates that F is zero or less, while G indicates that F is

less than zero. P and G are not affected by carry in. When

speed requirements are not stringent, the 74F181 can be

used in a simple Ripple Carry mode by connecting the

Carry output (Cn+4) signal to the Carry input (Cn) of the

next unit. For high speed operation the device is used in

conjunction with a carry lookahead circuit. One carry lookahead package is required for each group of four 74F181

www.fairchildsemi.com

The Function Table lists the arithmetic operations that are

performed without a carry in. An incoming carry adds a one

to each operation. Thus, select code LHHL generates A

minus B minus 1 (2s complement notation) without a carry

in and generates A minus B when a carry is applied.

Because subtraction is actually performed by complementary addition (1s complement), a carry out means borrow;

thus a carry is generated when there is no underflow and

no carry is generated when there is underflow. As indicated, this device can be used with either active LOW

inputs producing active LOW outputs or with active HIGH

inputs producing active HIGH outputs. For either case the

table lists the operations that are performed to the operands labeled inside the logic symbol.

S0

a. All Input Data Inverted

b. All Input Data True

S1

S2

S3

Logic

Arithmetic

Arithmetic

(M=H)

(M=L, C0=Inactive)

(M=L, C0=Active)

A minus 1

AB

A B minus 1

AB

A+B

A B minus 1

AB

Logic 1 minus 1 (2s comp.)

A+B

Zero

A plus (A + B)

A plus (A + B) plus 1

A B plus (A + B)

A B plus (A + B) plus 1

AB

A minus B minus 1

A minus B

A+B

A+B

A + B plus 1

A plus (A + B plus 1

AB

A plus (A + B)

A B

A plus B

A plus B plus 1

A B plus (A + B)

A B plus (A + B) plus 1

A+B

A+B

A + B plus 1

Logic 0

A plus A (2 A)

A plus A (2 A) plus 1

AB

A plus A B

A plus A B plus 1

AB

A plus A B

A plus A B plus 1

A plus 1

A plus 1

A+B

A+B

A + B plus 1

AB

A+B

A + B plus 1

Logic 0 minus 1 (2s comp.)

AB

Zero

A plus (A B)

A plus A B plus 1

A B plus (A + B)

A B plus (A + B) plus 1

AB

A minus B minus 1

A minus B

AB

A B minus 1

AB

A+B

A plus A B

A plus A B plus 1

A B

A plus B

A plus B plus 1

A B plus (A + B)

A B plus (A + B) plus 1

AB

A B minus 1

AB

Logic 1

A plus A (2 A)

A plus A (2 A) plus 1

A+B

A plus (A + B)

A plus (A+B) plus 1

A+B

A plus (A + B)

A plus (A+B) plus 1

A minus 1

www.fairchildsemi.com

74F181

Operation Table

74F181

Operation Table

(Continued)

S0

c. A All Input Data Inverted; B Input Data True

d. A Input Data True; B Input Date Inverted

www.fairchildsemi.com

S1

S2

S3

Logic

Arithmetic

Arithmetic

(M=H)

(M=L, C0=Inactive)

(M=L, C0=Active)

A minus 1

A+B

A B minus 1

AB

AB

A B minus 1

AB

Logic 1 minus 1 (2s comp.)

Zero

AB

A plus (A + B)

A plus (A + B) plus 1

A B plus (A + B)

A B plus (A + B) plus 1

AB

A plus B

A plus B plus 1

A+B

A+B

A + B plus 1

A+B

A plus (A + B)

A plus (A + B) plus 1

A B

A minus B minus 1

A minus B

A B plus (A + B)

A B plus (A + B) plus 1

A+B

A+B

A + B plus 1

Logic 0

A plus A (2 A)

A plus A (2 A) plus 1

AB

A plus A B

A plus A B plus 1

AB

A plus A B

A plus A B plus 1

A plus 1

A plus 1

AB

A+B

A + B plus 1

A+B

A+B

A + B plus 1

Logic 0 minus 1 (2s comp.)

Zero

A+B

A plus A B

A plus A B plus 1

A B plus (A + B)

A B plus (A + B) plus 1

AB

A plus B

A plus B plus 1

AB

A B minus 1

AB

AB

A plus A B

A plus A B plus 1

A B

A minus B minus 1

A minus B

A B plus (A + B)

A B plus (A + B) plus 1

AB

A B minus 1

AB

Logic 1

A plus A (2 A)

A plus A (2 A) plus 1

A+B

A plus (A + B)

A plus (A+B) plus 1

A+B

A plus (A + B)

A plus (A+B) plus 1

A minus 1

74F181

Logic Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.fairchildsemi.com

74F181

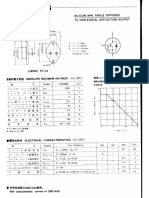

Absolute Maximum Ratings(Note 2)

Recommended Operating

Conditions

Storage Temperature

65C to +150 C

Ambient Temperature under Bias

55C to +125 C

Free Air Ambient Temperature

Junction Temperature under Bias

55C to +150 C

Supply Voltage

0C to +70C

+4.5V to +5.5V

0.5V to +7.0V

VCC Pin Potential to Ground Pin

Input Voltage (Note 3)

0.5V to +7.0V

Input Current (Note 3)

30 mA to +5.0 mA

Voltage Applied to Output

in HIGH State (with VCC = 0V)

Standard Output

0.5V to VCC

3-STATE Output

0.5V to +5.5V

Note 2: Absolute maximum ratings are values beyond which the device

may be damaged or have its useful life impaired. Functional operation

under these conditions is not implied.

Current Applied to Output

in LOW State (Max)

Note 3: Either voltage limit or current limit is sufficient to protect inputs.

twice the rated IOL (mA)

ESD Last Passing Voltage (Min)

4000V

DC Electrical Characteristics

Symbol

Parameter

Min

Typ

Max

Input HIGH Voltage

VIL

Input LOW Voltage

0.8

VCD

Input Clamp Diode Voltage

1.2

VOH

Output HIGH

Voltage

VOL

Output LOW

2.0

Units

VIH

10% VCC

2.5

5% VCC

2.7

10% VCC

0.5

Voltage

IIH

Input HIGH

5.0

Current

IBVI

Input HIGH Current

7.0

Breakdown Test

ICEX

Output HIGH

50

Leakage Current

VID

Input Leakage

Test

IOD

4.75

Output Leakage

3.75

Circuit Current

IIL

VCC

Recognized as a LOW Signal

Min

1.8

Min

Min

IOL = 20 mA

Max

VIN = 2.7V

Max

VIN = 7.0V

Max

VOUT = VCC (Fn, G, P, Cn+4)

0.0

0.0

IOHC

Open Collector, Output

60

OFF Leakage Test

IID = 1.9 A

All Other Pins Grounded

VIOD = 150 mV

All Other Pins Grounded

VIN = 0.5V (M)

VIN = 0.5V (A0, A1, A3, B0, B1, B3)

Max

150

mA

Max

VOUT = 0V (Fn, G, P, Cn+4)

250

Min

VO = VCC (A = B)

3.0

Output Short-Circuit Current

IOH = 1 mA

mA

2.4

IOS

IIN = 18 mA

IOH = 1 mA

0.6

Input LOW Current

Conditions

Recognized as a HIGH Signal

VIN = 0.5V (Sn, A2, B2)

VIN = 0.5V (Cn)

ICCH

Power Supply Current

43

65.0

mA

Max

VO = HIGH

ICCL

Power Supply Current

43

65.0

mA

Max

VO = LOW

www.fairchildsemi.com

74F181

AC Electrical Characteristics

Symbol

Parameter

Path

TA = 55C to +125C

TA = 0C to +70C

VCC = +5.0V

VCC = +5.0V

CL = 50 pF

CL = 50 pF

CL = 50 pF

Min

Typ

Max

Min

Max

Min

Max

tPLH

Propagation Delay

3.0

6.4

8.5

3.0

10.0

3.0

9.5

tPHL

Cn to Cn + 4

3.0

6.1

8.0

3.0

9.5

3.0

9.0

5.0

10.0

13.0

5.0

15.5

5.0

14.0

4.0

9.4

12.0

3.5

16.5

4.0

13.0

5.0

10.8

14.0

5.0

17.0

5.0

15.0

5.0

10.0

13.0

4.0

15.0

5.0

14.0

3.0

6.7

8.5

2.5

16.0

3.0

9.5

3.0

6.5

8.5

2.5

12.0

3.0

9.5

3.0

5.7

7.5

2.5

9.0

3.0

8.5

3.0

5.8

7.5

2.5

9.5

3.0

8.5

3.0

6.5

8.5

2.5

11.5

3.0

9.5

3.0

7.3

9.5

2.5

11.0

3.0

10.5

3.0

5.0

7.0

2.5

8.5

3.0

8.0

3.0

5.5

7.5

3.0

9.5

3.0

8.5

3.0

5.8

7.5

2.5

11.0

3.0

8.5

4.0

6.5

8.5

3.0

11.0

4.0

9.5

3.0

7.0

9.0

3.0

14.5

3.0

10.0

3.0

7.2

10.0

3.0

14.5

3.0

10.0

3.0

8.2

11.0

3.0

17.5

3.0

12.0

3.0

5.0

11.0

3.0

14.5

3.0

12.0

4.0

8.0

10.5

3.5

16.5

4.0

11.5

4.0

7.8

10.0

4.0

13.5

4.0

11.0

4.5

9.4

12.0

3.5

17.5

4.5

13.0

3.5

9.4

12.0

3.0

14.0

3.5

13.0

4.0

6.0

9.0

3.5

14.5

4.0

10.0

4.0

6.0

10.0

3.0

15.5

4.0

11.0

11.0

18.5

27.0

8.0

35.0

11.0

29.0

6.0

9.8

12.5

5.5

21.0

6.0

13.5

tPLH

Propagation Delay

tPHL

A or B to Cn + 4

tPLH

Propagation Delay

tPHL

A or B to Cn + 4

tPLH

Propagation Delay

tPHL

Cn to F

tPLH

Propagation Delay

tPHL

A or B or G

tPLH

Propagation Delay

tPHL

A or B to G

tPLH

Propagation Delay

tPHL

A or B to P

tPLH

Propagation Delay

tPHL

A or B to P

tPLH

Propagation Delay

tPHL

Ai or Bi to Fi

tPLH

Propagation Delay

tPHL

Ai or Bi to Fi

tPLH

Propagation Delay

tPHL

Any A or B to Any F

tPLH

Propagation Delay

tPHL

Any A or B to Any F

tPLH

Propagation Delay

tPHL

A or B to F

tPLH

Propagation Delay

tPHL

A or B to A = B

Mode

TA = +25C

VCC = +5.0V

Sum

Dif

Any

Sum

Dif

Sum

Dif

Sum

Dif

Sum

Dif

Logic

Dif

Units

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

www.fairchildsemi.com

74F181

Physical Dimensions inches (millimeters) unless otherwise noted

24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide

Package Number M24B

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-011, 0.600 Wide

Package Number N24A

www.fairchildsemi.com

74F181 4-Bit Arithmetic Logic Unit

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Package Number N24C

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and

Fairchild reserves the right at any time without notice to change said circuitry and specifications.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

2. A critical component in any component of a life support

device or system whose failure to perform can be reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the

user.

www.fairchildsemi.com

www.fairchildsemi.com

Das könnte Ihnen auch gefallen

- 3630 CompressorDokument5 Seiten3630 CompressorAlejandro Borrego DominguezNoch keine Bewertungen

- VP603 High-Performance Video Output ModuleDokument8 SeitenVP603 High-Performance Video Output ModuleAlejandro Borrego DominguezNoch keine Bewertungen

- 74F181 PDFDokument9 Seiten74F181 PDFAlejandro Borrego DominguezNoch keine Bewertungen

- Damper Diode For Ultrahigh-Definition Display Applications: DD52RCDokument3 SeitenDamper Diode For Ultrahigh-Definition Display Applications: DD52RCAlejandro Borrego DominguezNoch keine Bewertungen

- Horizontal Deflection Output For Super High Resolution Display, Color TV For Multi Media & HDTV High Speed Switching ApplicationsDokument6 SeitenHorizontal Deflection Output For Super High Resolution Display, Color TV For Multi Media & HDTV High Speed Switching ApplicationsAlejandro Borrego DominguezNoch keine Bewertungen

- VP603 High-Performance Video Output ModuleDokument8 SeitenVP603 High-Performance Video Output ModuleAlejandro Borrego DominguezNoch keine Bewertungen

- 固电半导体 Inchange Semiconductor: Silicon NPN Power TransistorsDokument3 Seiten固电半导体 Inchange Semiconductor: Silicon NPN Power TransistorsAlejandro Borrego DominguezNoch keine Bewertungen

- DTV32 PDFDokument4 SeitenDTV32 PDFAlejandro Borrego DominguezNoch keine Bewertungen

- DiodoDokument4 SeitenDiododibaladaNoch keine Bewertungen

- Vishay Dual Schottky Barrier Rectifiers 30V and 40V, 16ADokument4 SeitenVishay Dual Schottky Barrier Rectifiers 30V and 40V, 16AAlejandro Borrego DominguezNoch keine Bewertungen

- EGP30ADokument2 SeitenEGP30AAlejandro Borrego DominguezNoch keine Bewertungen

- Byv143-40m Byv143-45m Byv143-40am Byv143-45am Byv143-40rm Byv143-45rmDokument3 SeitenByv143-40m Byv143-45m Byv143-40am Byv143-45am Byv143-40rm Byv143-45rmAlejandro Borrego DominguezNoch keine Bewertungen

- 2SD1398Dokument3 Seiten2SD1398Alejandro Borrego DominguezNoch keine Bewertungen

- 2SC5717Dokument6 Seiten2SC5717Alejandro Borrego DominguezNoch keine Bewertungen

- Horizontal Deflection Output For Super High Resolution Display, Color TV For Multi Media & HDTV High Speed Switching ApplicationsDokument6 SeitenHorizontal Deflection Output For Super High Resolution Display, Color TV For Multi Media & HDTV High Speed Switching ApplicationsAlejandro Borrego DominguezNoch keine Bewertungen

- BU2525DFDokument8 SeitenBU2525DFAlejandro Borrego DominguezNoch keine Bewertungen

- TOSHIBA Transistor 2SC5695 for High Voltage Horizontal DeflectionDokument6 SeitenTOSHIBA Transistor 2SC5695 for High Voltage Horizontal DeflectionAlejandro Borrego DominguezNoch keine Bewertungen

- 2SD200Dokument3 Seiten2SD200Alejandro Borrego DominguezNoch keine Bewertungen

- 2SD1577 Silicon Diffused Power Transistor: General DescriptionDokument2 Seiten2SD1577 Silicon Diffused Power Transistor: General DescriptionAlejandro Borrego DominguezNoch keine Bewertungen

- 2SD898BDokument2 Seiten2SD898BAlejandro Borrego DominguezNoch keine Bewertungen

- 2SD1426Dokument4 Seiten2SD1426Alejandro Borrego DominguezNoch keine Bewertungen

- 2SD869Dokument4 Seiten2SD869Alejandro Borrego DominguezNoch keine Bewertungen

- 2SD1577 Silicon Diffused Power Transistor: General DescriptionDokument2 Seiten2SD1577 Silicon Diffused Power Transistor: General DescriptionAlejandro Borrego DominguezNoch keine Bewertungen

- BU2520AFDokument9 SeitenBU2520AFLuis Arturo Leiva MonjarasNoch keine Bewertungen

- 2SD1650Dokument3 Seiten2SD1650Alejandro Borrego DominguezNoch keine Bewertungen

- Dataheet Toshiba c5359Dokument6 SeitenDataheet Toshiba c5359Silvia MoralesNoch keine Bewertungen

- 2SD1910Dokument3 Seiten2SD1910Alejandro Borrego DominguezNoch keine Bewertungen

- Horizontal Deflection Output For High Resolution Display, Color TV High Speed Switching ApplicationsDokument6 SeitenHorizontal Deflection Output For High Resolution Display, Color TV High Speed Switching ApplicationsAlejandro Borrego DominguezNoch keine Bewertungen

- TT2140 PDFDokument4 SeitenTT2140 PDFAsallimitNoch keine Bewertungen

- Horizontal Deflection Output For High Resolution Display, Color TV High Speed Switching ApplicationsDokument6 SeitenHorizontal Deflection Output For High Resolution Display, Color TV High Speed Switching ApplicationsAlejandro Borrego DominguezNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5783)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- SN74LVC541ARGYRG4 Texas InstrumentsDokument23 SeitenSN74LVC541ARGYRG4 Texas InstrumentsOlga PlohotnichenkoNoch keine Bewertungen

- Circuitos FinalDokument12 SeitenCircuitos Finalalvaro barreraNoch keine Bewertungen

- Opax350 High-Speed, Single-Supply, Rail-To-Rail Operational Amplifiers Microamplifier SeriesDokument43 SeitenOpax350 High-Speed, Single-Supply, Rail-To-Rail Operational Amplifiers Microamplifier SeriesLuis J. Gonzalez LugoNoch keine Bewertungen

- Opa 1677Dokument51 SeitenOpa 1677Swarnim man DangolNoch keine Bewertungen

- 25AA640A/25LC640A: 64K SPI Bus Serial EEPROMDokument36 Seiten25AA640A/25LC640A: 64K SPI Bus Serial EEPROMmarino246Noch keine Bewertungen

- 1 MHZ Bandwidth, Galvanically Isolated Current Sensor Ic in Small Footprint Soic8 PackageDokument26 Seiten1 MHZ Bandwidth, Galvanically Isolated Current Sensor Ic in Small Footprint Soic8 PackageRicardo UrioNoch keine Bewertungen

- PCB Part B (3rd Sem)Dokument22 SeitenPCB Part B (3rd Sem)jayant kumarNoch keine Bewertungen

- Ci SMD Isl6700Dokument8 SeitenCi SMD Isl6700DJALMA MOREIRANoch keine Bewertungen

- 74LS05Dokument6 Seiten74LS05Tammy WashingtonNoch keine Bewertungen

- 7420 Datasheet PDFDokument4 Seiten7420 Datasheet PDFOMAR ALEJANDRO LONGORIA VAZQUEZNoch keine Bewertungen

- 7404 - Inversor GatesDokument2 Seiten7404 - Inversor GatesRONALD FSNoch keine Bewertungen

- Autonomous CarDokument20 SeitenAutonomous CaratomNoch keine Bewertungen

- Atmel DatasheetDokument26 SeitenAtmel DatasheetManurung Edward Jr.Noch keine Bewertungen

- 8K Microwire Compatible Serial EEPROM: 93AA76A/B/C, 93LC76A/B/C, 93C76A/B/CDokument26 Seiten8K Microwire Compatible Serial EEPROM: 93AA76A/B/C, 93LC76A/B/C, 93C76A/B/CΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣ100% (1)

- FairchildDokument89 SeitenFairchildflorinescu61Noch keine Bewertungen

- 74F08 Quad 2-Input AND Gate: General DescriptionDokument5 Seiten74F08 Quad 2-Input AND Gate: General DescriptionSeptian D ChandraNoch keine Bewertungen

- Features: Spi Serial EepromDokument21 SeitenFeatures: Spi Serial EepromChinotzcuintle ChiclosoNoch keine Bewertungen

- M48T35AY M48T35AV: 5.0 or 3.3V, 256 Kbit (32 KB x8) TIMEKEEPER SramDokument26 SeitenM48T35AY M48T35AV: 5.0 or 3.3V, 256 Kbit (32 KB x8) TIMEKEEPER SramDawood AhmedNoch keine Bewertungen

- CD4069UB CMOS Hex Inverter: 1 Features 3 DescriptionDokument32 SeitenCD4069UB CMOS Hex Inverter: 1 Features 3 DescriptionGaston TaboadaNoch keine Bewertungen

- Logic Guide Texas InstrumentsDokument20 SeitenLogic Guide Texas InstrumentsCristian RoblesNoch keine Bewertungen

- MC 14541Dokument8 SeitenMC 14541boba78Noch keine Bewertungen

- Industry-Standard Dual Operational Amplifiers: 1 Features 3 DescriptionDokument56 SeitenIndustry-Standard Dual Operational Amplifiers: 1 Features 3 DescriptionBhupender SiwachNoch keine Bewertungen

- 78 hct14Dokument16 Seiten78 hct14Bruno AlvesNoch keine Bewertungen

- Automotive MCUs and MPUs 8 16 e 32 Bits Devices FreescaleDokument2 SeitenAutomotive MCUs and MPUs 8 16 e 32 Bits Devices FreescaleJoão JoséNoch keine Bewertungen

- Samsung Q45 TORINO II Notebook Computer SMDokument160 SeitenSamsung Q45 TORINO II Notebook Computer SMRoger Martínez BermúdezNoch keine Bewertungen

- 74HC4066 PDFDokument25 Seiten74HC4066 PDFEdson CostaNoch keine Bewertungen

- Analog Devices 2014 RFIC Selection GuideDokument40 SeitenAnalog Devices 2014 RFIC Selection Guidespeedybits100% (2)

- QML 38535 17aDokument702 SeitenQML 38535 17agem1144aaNoch keine Bewertungen

- FlashcatUSB ManualDokument39 SeitenFlashcatUSB ManualAnh ĐườngNoch keine Bewertungen

- Samsung LExxA45xDokument318 SeitenSamsung LExxA45xm_tOmNoch keine Bewertungen