Beruflich Dokumente

Kultur Dokumente

Low Complexity Digit Serial Fir Filter by Multiple Constant Multiplication Algorithms

Hochgeladen von

esatjournalsCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Low Complexity Digit Serial Fir Filter by Multiple Constant Multiplication Algorithms

Hochgeladen von

esatjournalsCopyright:

Verfügbare Formate

IJRET: International Journal of Research in Engineering and Technology

eISSN: 2319-1163 | pISSN: 2321-7308

LOW COMPLEXITY DIGIT SERIAL FIR FILTER BY MULTIPLE

CONSTANT MULTIPLICATION ALGORITHMS

A. Hema Malini1, C.Srimathi2

1

Assistant Professor, Electronics and Communication Engineering, Saveetha Engineering College, Tamil Nadu, India

2

PG Scholar, Electronics and Communication Engineering, Saveetha Engineering College, Tamil Nadu, India

Abstract

Serial input data is multiplied with constant pair to produce constant multiplication called Multiple Constant Multiplications (MCM).

In order to reduce number of shifting, an addition/subtraction operation, Graph Based (GB) algorithm is taken as a proposed

algorithm to construct multiplier for transposed form of digit serial FIR (Finite Impulse Response) filter design 4-tap digit serial FIR

filter with digit size d=2,4,8. To analyze low complexity Digit based recoding algorithm and CSE (Common Subexpression

Elimination) algorithm simulation compared with GB algorithm based on the performance of area utilization and delay report in

Xilinx ise design suite12.1software. Finally this FIR filter is implemented in FPGA spartan3 hardware for real time implementation.

Keywords: Multiple Constant Multiplication, Digit size, Low complexity, GB algorithm

--------------------------------------------------------------------***---------------------------------------------------------------------1. INTRODUCTION

MCM is involved to produce constant multiplication in Digital

Signal Processing (DSP) systems, MIMO (Multiple Input

Multiple Output) systems, Error correcting codes, Frequency

multiplication, Graphics and Control applications.

In such applications full fledge of multipliers are not needed.

Since coefficients are constant to produce constant

multiplication. Once the MCM architecture is constructed, it

can be called as many times it required.

Constant multiplication either can be done by digit parallel

design or digit serial design. Digit parallel design of constant

multiplier needs external wire for shifting. It requires more area

while implementation takes place in FPGA or any other ASIC.

Hence digit serial design overcomes area constrain with

acceptable delay timing.

Multiplication with constant is called constant multiplication.

This process is used in filter operation. There are two types of

constant multiplication.

FIR filter output can be obtained by multiplication of input and

impulse response. Direct and transposed form implementations

are two forms of FIR filter implementations. Rather than direct

form, transposed form is most effective and realizable

structure. Multiplication operation takes place in multiplier

block. These transposed form multiplier blocks in FIR filter

will replace by MCM architecture also known as shift and add

architecture.

FIR filter gives guaranteed feed forward, stable and linear

phase response. For FIR filter impulse response is equal to the

number of coefficients. But it is not the case in Infinite Impulse

Response (IIR) filters. Hence this FIR filter implementation is

sometimes called as multiplierless digit based recoding

method.

1.1 Objective

Main objective is to eliminate multiplier block and introducing

MCM architecture in digit serial FIR filter for the reduction of

multiplication in the form of shift and add operations.

One is Single Constant Multiplication (SCM) and other is

Multiple Constant Multiplication. Input is multiplied with

single specific coefficient to produce output is called SCM.

Canonical Signed Digit (CSD) number representation is used to

implement SCM multipliers.

Fig 1 MCM operation

Input is multiplied with multiple numbers of specific

coefficients to produce multiple outputs is called MCM.

Multiplication is a process of shifting and addition operation.

Constant multiplier consists of number of adder, subtractor and

shifter according to the coefficient pair.

In Fig.1 X denotes input, 1 and 2 are filter coefficients, Y1

and Y2 are the outputs.

__________________________________________________________________________________________

Volume: 03 Issue: 04 | Apr-2014, Available @ http://www.ijret.org

222

IJRET: International Journal of Research in Engineering and Technology

An operation with the same input is to be multiplied by a set of

coefficients is said to be MCM. Serial input data is multiplied

with two pair of coefficients and produces Y1, Y2 outputs.

eISSN: 2319-1163 | pISSN: 2321-7308

2. PROPOSED WORK

To design MCM architecture without partial product sharing

algorithm (Digit based recoding), Common Sub-expression

Elimination (CSE) algorithm [5]-[6] is used in existing

methods. In proposed method, Graph Based (GB) [10]-[11]

algorithm is used for this purpose.

Four constants are taken as taken as coefficient pair. According

to MCM principle constant multiplication is performed by

number of shifting and addition operation. For this purpose

compare with other algorithms, GB algorithm is used to find

number of shifting and addition operation.

Consider the first coefficient pair as 29x and 43x.For this pair,

without partial product sharing algorithm requires six addition

and six shifting operations and CSE algorithm requires four

additions and four shifting operations. But GB algorithm

requires only one subtractor, two adders and three shifting

operation.

Fig 2 Digit Serial operation

Bit serial and Digit serial are the two cases for serial addition.

Compared to bit serial operation, Fig.2 explains that Digit

Serial operation needs less number of delay elements such as

flip flop for addition or subtraction.

Fig 4 GB algorithm for 29,43,59,89 coefficients

Consider the second coefficient pair as59x and 89x.For this

pair, without partial product sharing algorithm requires four

addition, one subtraction and five shifting operations and CSE

algorithm requires four subtractions and four shifting

operations. But GB algorithm requires only two subtraction,

one addition and three shifting operation.

2.1 FIR Filter [4 TAP] with MCM

Fig 3 flow map for proposed system design

Fig.3 gives the flow map for proposed system design.

Fig 5 Four tap FIR filter with MCM architecture

__________________________________________________________________________________________

Volume: 03 Issue: 04 | Apr-2014, Available @ http://www.ijret.org

223

IJRET: International Journal of Research in Engineering and Technology

Steps of GB algorithm can be applied for any coefficient pair

combinations. Hence GB algorithm is used and number of

operation is reduced drastically than other algorithms.

eISSN: 2319-1163 | pISSN: 2321-7308

Fig.8 displays 4 tap filter with GB algorithm. This simulation

result was displayed by modelsim software. These are the

simulation results displayed by modelsim software.

Fig 6 Output for FIR filter with digit based recoding algorithm

Four filter coefficient 29,43,59,89 values are taken for digit

serial FIR filter design. X(n) is taken as a input sequence and

Y(n) is taken as output sequence.

Fig 9 RTL schematic view of FIR filter

After completion of simulation process in Modelsim tool,

synthesis process is takes place to calculate gate count and

delay report. Fig.9 shows the RTL schematic view of FIR filter

with MCM architecture.

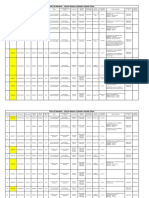

3. FIR FILTER DEVICE UTILIZATION REPORT

Fig 7 Output for FIR filter with CSE algorithm

Fig.6 shows 4 tap FIR filter with without partial product

sharing (Digit based recoding) algorithm and Fig.7 displays 4

tap filter with CSE algorithm.

Fig 10 Device utilization report

Fig 8 Output for FIR filter with GB algorithm

FIR filter with digit size d=2, 4, 8 was synthesized separately

for device utilization in terms of gate count with each different

algorithms. Fig 10 shows the device utilization report of FIR

filter with GB algorithm. Table-1 explains that the FIR filter

__________________________________________________________________________________________

Volume: 03 Issue: 04 | Apr-2014, Available @ http://www.ijret.org

224

IJRET: International Journal of Research in Engineering and Technology

with GB algorithm utilized less number of gate count than

other two algorithms.

Table -1: Gate Count Comparison

FIR filter

digit size

WPS

CSE

GB

d=2

790

635

578

d=4

1157

1132

707

d=8

2048

1994

1902

eISSN: 2319-1163 | pISSN: 2321-7308

5. CONCLUSIONS

Thus the implementation of digit serial FIR filter was

implemented with low complexity MCM architectures for digit

sizes d=2, 4, 8. Device utilization and delay values are

compared for hardware implementation. Hence this MCM

approach drastically reduces the system complexity, area and

delay and FPGA hardware real time implementation has

performed with spartan3 version. Future enhancement of this

paper is to design MCM architecture with more coefficient

pairs for FIR filter implementation.

REFERENCES

4. FIR FILTER DELAY SYNTHESIS REPORT

[1]

[2]

[3]

[4]

[5]

Fig 11 Delay synthesis report

FIR filter with digit size d=2, 4, 8 was synthesized separately

for delay comparison. Fig.9 shows the delay synthesis report of

FIR filter with GB algorithm. Table-2 explains that the FIR

filter with GB algorithm has less delay time than other two

algorithms.

[6]

[7]

Table-2: Delay comparison

FIR filter

digit size

WPS

CSE

GB

d=2

18.884ns

11.91ns

11.885ns

d=4

16.078ns

15.384ns

17.165ns

d=8

28.759ns

19.988ns

19.476ns

[8]

[9]

Kenny Johansson, Oscar Gustafsson, Andrew G. D.,

and Lars Wanhammar, Algorithm to reduce the

number of shifts and additions in multiplier blocks

using serial arithmetic IEEE MELECON, pp. 197200, 2004.

Levent Aksoy, Cristiano Lazzari, Eduardo Costa,Paulo

Flores, Jos Monteiro., Efficient shift-adds design of

digit-serial

multiple

constant

multiplications

GLSVLSI11,2011.

Levent Aksoy, Cristiano Lazzari Eduardo Costa,Paulo

Flores, Jos Monteiro, Design of digit-serial FIR

filters: algorithms, architectures, and a CAD tool

IEEE Trans. on Very Large Scale Integration (VLSI)

Systems, Vol. 21, No. 3, pp 498-511, 2013.

Levent Aksoy, Eduardo.D.Costa, Paulo Flores, Jos

Monteiro., Exact and approximate algorithms for the

optimization of area and delay in multiple constant

multiplications IEEE Transactions on ComputerAided Design of Integrated Circuits And Systems, Vol.

27, No. 6, pp. 1013-1026, 2008.

Miodrag potkonjak, Mani.B.S., Anantha.P.C.,Multiple

constant multiplications efficient and versatile

framework and algorithms for exploring common

subexpression elimination IEEE Trans. Computer

Aided-Design of Integrated Circuits and Systems,

VOL.15,NO.2, pp 151-165, 1996.

Yuen H.A.H., Chi U.L., Hing-K.K.,Ngai Wong,

Global optimization of common subexpressions for

multiplierless synthesis of multiple constant

multiplications IEEE Explore,pp.119-124, 2008.

R. Hartley, Subexpression sharing in filters using

canonic signed digit multipliers, IEEE Trans. Circuits

Syst. II, Exp. Briefs, vol. 43, no. 10,pp. 677688, Oct.

1996.

I.-C. Park and H.-J. Kang, Digital filter synthesis

based on minimal signed digit representation, in Proc.

DAC, pp. 468473, 2001.

A. Dempster, M. Macleod, Use of minimum-adder

multiplier blocks in FIR digital filters, IEEE Trans.

Circuits Syst. II, Exp. Briefs, vol. 42, no. 9, pp. 569

577, Sep. 1995.

__________________________________________________________________________________________

Volume: 03 Issue: 04 | Apr-2014, Available @ http://www.ijret.org

225

IJRET: International Journal of Research in Engineering and Technology

[10]

[11]

eISSN: 2319-1163 | pISSN: 2321-7308

Y. Voronenko, M. Pschel, Multiplierless multiple

constant multiplication, ACM Trans. Algor., vol. 3,

no. 2, pp. 139, May, 2007.

L. Aksoy, E. Gunes, and P. Flores, Search algorithms

for the multiple constant multiplications problem:

Exact and approximate, J. Microprocess. Microsyst.,

vol. 34, no. 5, pp. 151162, Aug. 2010.

BIOGRAPHIES

A. Hema Malini received the B.Tech degree

in

Electronics

and

Communication

Engineering and M.Tech degree in Wireless

Communication. Currently, She is working as

Assistant Professor in the Department of

Electronics and Communication Engineering,

Saveetha Engineering College, Chennai. Specialized in

Wireless Communication. Having 6 years of teaching

experience. Area of interest includes Mobile Communication

and Adhoc Networks.

C. Srimathi received the B.E. degree in

Electronics and Communication Engineering

in the year 2012 and pursuing M.E.degree in

VLSI Design from Saveetha Engineering

College. Her area of interests includes VLSI

Signal Processing and VLSI Design.

__________________________________________________________________________________________

Volume: 03 Issue: 04 | Apr-2014, Available @ http://www.ijret.org

226

Das könnte Ihnen auch gefallen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Analytical Assessment On Progressive Collapse Potential of New Reinforced Concrete Framed Structure PDFDokument5 SeitenAnalytical Assessment On Progressive Collapse Potential of New Reinforced Concrete Framed Structure PDFesatjournalsNoch keine Bewertungen

- A Review On Fake Biometric Detection System For Various ApplicationsDokument4 SeitenA Review On Fake Biometric Detection System For Various ApplicationsesatjournalsNoch keine Bewertungen

- PTE 3 Week Study ScheduleDokument3 SeitenPTE 3 Week Study ScheduleesatjournalsNoch keine Bewertungen

- An Improved Geo-Encryption Algorithm in Location Based Services PDFDokument4 SeitenAn Improved Geo-Encryption Algorithm in Location Based Services PDFesatjournalsNoch keine Bewertungen

- A Research On Significance of Kalman Filter-Approach As Applied in Electrical Power SystemDokument8 SeitenA Research On Significance of Kalman Filter-Approach As Applied in Electrical Power SystemesatjournalsNoch keine Bewertungen

- Analysis and Optimization of Sand Casting Defects With The Help of Artificial Neural Network PDFDokument6 SeitenAnalysis and Optimization of Sand Casting Defects With The Help of Artificial Neural Network PDFesatjournalsNoch keine Bewertungen

- Analysis and Characterization of Dendrite Structures From Microstructure Images of Material PDFDokument5 SeitenAnalysis and Characterization of Dendrite Structures From Microstructure Images of Material PDFesatjournalsNoch keine Bewertungen

- An Efficient Information Retrieval Ontology System Based Indexing For Context PDFDokument7 SeitenAn Efficient Information Retrieval Ontology System Based Indexing For Context PDFesatjournalsNoch keine Bewertungen

- Analysis of Outrigger System For Tall Vertical Irregularites Structures Subjected To Lateral Loads PDFDokument5 SeitenAnalysis of Outrigger System For Tall Vertical Irregularites Structures Subjected To Lateral Loads PDFesatjournalsNoch keine Bewertungen

- Analysis of Cylindrical Shell Structure With Varying Parameters PDFDokument6 SeitenAnalysis of Cylindrical Shell Structure With Varying Parameters PDFesatjournalsNoch keine Bewertungen

- An Octa-Core Processor With Shared Memory and Message-Passing PDFDokument10 SeitenAn Octa-Core Processor With Shared Memory and Message-Passing PDFesatjournalsNoch keine Bewertungen

- A Servey On Wireless Mesh Networking ModuleDokument5 SeitenA Servey On Wireless Mesh Networking ModuleesatjournalsNoch keine Bewertungen

- Analysis and Optimization of Electrodes For Improving The Performance of Ring Laser Gyro PDFDokument4 SeitenAnalysis and Optimization of Electrodes For Improving The Performance of Ring Laser Gyro PDFesatjournalsNoch keine Bewertungen

- Analysis and Design of A Multi Compartment Central Cone Cement Storing Silo PDFDokument7 SeitenAnalysis and Design of A Multi Compartment Central Cone Cement Storing Silo PDFesatjournalsNoch keine Bewertungen

- A Review Paper On Smart Health Care System Using Internet of ThingsDokument5 SeitenA Review Paper On Smart Health Care System Using Internet of ThingsesatjournalsNoch keine Bewertungen

- A Study and Survey On Various Progressive Duplicate Detection MechanismsDokument3 SeitenA Study and Survey On Various Progressive Duplicate Detection MechanismsesatjournalsNoch keine Bewertungen

- A Critical Review On Experimental Studies of Strength and Durability Properties of Fibre Reinforced Concrete Composite PDFDokument7 SeitenA Critical Review On Experimental Studies of Strength and Durability Properties of Fibre Reinforced Concrete Composite PDFesatjournalsNoch keine Bewertungen

- A New Type of Single-Mode Lma Photonic Crystal Fiber Based On Index-Matching Coupling PDFDokument8 SeitenA New Type of Single-Mode Lma Photonic Crystal Fiber Based On Index-Matching Coupling PDFesatjournalsNoch keine Bewertungen

- A Review Paper On Smart Health Care System Using Internet of ThingsDokument5 SeitenA Review Paper On Smart Health Care System Using Internet of ThingsesatjournalsNoch keine Bewertungen

- I JR Et 20160503007dfceDokument5 SeitenI JR Et 20160503007dfcegtarun22guptaNoch keine Bewertungen

- A Comparative Investigation On Physical and Mechanical Properties of MMC Reinforced With Waste Materials PDFDokument7 SeitenA Comparative Investigation On Physical and Mechanical Properties of MMC Reinforced With Waste Materials PDFesatjournalsNoch keine Bewertungen

- I JR Et 20160503007dfceDokument5 SeitenI JR Et 20160503007dfcegtarun22guptaNoch keine Bewertungen

- A Survey On Identification of Ranking Fraud For Mobile ApplicationsDokument6 SeitenA Survey On Identification of Ranking Fraud For Mobile ApplicationsesatjournalsNoch keine Bewertungen

- A Research On Significance of Kalman Filter-Approach As Applied in Electrical Power SystemDokument8 SeitenA Research On Significance of Kalman Filter-Approach As Applied in Electrical Power SystemesatjournalsNoch keine Bewertungen

- A Servey On Wireless Mesh Networking ModuleDokument5 SeitenA Servey On Wireless Mesh Networking ModuleesatjournalsNoch keine Bewertungen

- A Review On Fake Biometric Detection System For Various ApplicationsDokument4 SeitenA Review On Fake Biometric Detection System For Various ApplicationsesatjournalsNoch keine Bewertungen

- A Women Secure Mobile App For Emergency Usage (Go Safe App)Dokument3 SeitenA Women Secure Mobile App For Emergency Usage (Go Safe App)esatjournalsNoch keine Bewertungen

- A Survey On Identification of Ranking Fraud For Mobile ApplicationsDokument6 SeitenA Survey On Identification of Ranking Fraud For Mobile ApplicationsesatjournalsNoch keine Bewertungen

- Ad Hoc Based Vehcular Networking and ComputationDokument3 SeitenAd Hoc Based Vehcular Networking and ComputationesatjournalsNoch keine Bewertungen

- A Three-Level Disposal Site Selection Criteria System For Toxic and Hazardous Wastes in The PhilippinesDokument9 SeitenA Three-Level Disposal Site Selection Criteria System For Toxic and Hazardous Wastes in The PhilippinesesatjournalsNoch keine Bewertungen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Sewage Pumping StationDokument35 SeitenSewage Pumping StationOrchie DavidNoch keine Bewertungen

- SEG Newsletter 65 2006 AprilDokument48 SeitenSEG Newsletter 65 2006 AprilMilton Agustin GonzagaNoch keine Bewertungen

- Marketing Plan for Monuro Clothing Store Expansion into CroatiaDokument35 SeitenMarketing Plan for Monuro Clothing Store Expansion into CroatiaMuamer ĆimićNoch keine Bewertungen

- Orc & Goblins VII - 2000pts - New ABDokument1 SeiteOrc & Goblins VII - 2000pts - New ABDave KnattNoch keine Bewertungen

- TheEconomist 2023 04 01Dokument297 SeitenTheEconomist 2023 04 01Sh FNoch keine Bewertungen

- TWP10Dokument100 SeitenTWP10ed9481Noch keine Bewertungen

- Unit 1 TQM NotesDokument26 SeitenUnit 1 TQM NotesHarishNoch keine Bewertungen

- Evaluating Sources IB Style: Social 20ib Opvl NotesDokument7 SeitenEvaluating Sources IB Style: Social 20ib Opvl NotesRobert ZhangNoch keine Bewertungen

- FX15Dokument32 SeitenFX15Jeferson MarceloNoch keine Bewertungen

- Lifespan Development Canadian 6th Edition Boyd Test BankDokument57 SeitenLifespan Development Canadian 6th Edition Boyd Test Bankshamekascoles2528zNoch keine Bewertungen

- CMC Ready ReckonerxlsxDokument3 SeitenCMC Ready ReckonerxlsxShalaniNoch keine Bewertungen

- ConductorsDokument4 SeitenConductorsJohn Carlo BautistaNoch keine Bewertungen

- 1.2 - Venn Diagram and Complement of A SetDokument6 Seiten1.2 - Venn Diagram and Complement of A SetKaden YeoNoch keine Bewertungen

- Bluetooth TutorialDokument349 SeitenBluetooth Tutorialjohn bougsNoch keine Bewertungen

- Exp 8 - GPG - D12B - 74 PDFDokument4 SeitenExp 8 - GPG - D12B - 74 PDFPRATIKSHA WADIBHASMENoch keine Bewertungen

- Software Requirements Specification: Chaitanya Bharathi Institute of TechnologyDokument20 SeitenSoftware Requirements Specification: Chaitanya Bharathi Institute of TechnologyHima Bindhu BusireddyNoch keine Bewertungen

- 3 - Performance Measurement of Mining Equipments by Utilizing OEEDokument8 Seiten3 - Performance Measurement of Mining Equipments by Utilizing OEEGonzalo GarciaNoch keine Bewertungen

- Controle de Abastecimento e ManutençãoDokument409 SeitenControle de Abastecimento e ManutençãoHAROLDO LAGE VIEIRANoch keine Bewertungen

- Radio Frequency Transmitter Type 1: System OperationDokument2 SeitenRadio Frequency Transmitter Type 1: System OperationAnonymous qjoKrp0oNoch keine Bewertungen

- Photographing Shadow and Light by Joey L. - ExcerptDokument9 SeitenPhotographing Shadow and Light by Joey L. - ExcerptCrown Publishing Group75% (4)

- TOGAF 9 Foundation Part 1 Exam Preparation GuideDokument114 SeitenTOGAF 9 Foundation Part 1 Exam Preparation GuideRodrigo Maia100% (3)

- Trading As A BusinessDokument169 SeitenTrading As A Businesspetefader100% (1)

- Music 7: Music of Lowlands of LuzonDokument14 SeitenMusic 7: Music of Lowlands of LuzonGhia Cressida HernandezNoch keine Bewertungen

- Onan Service Manual MDJA MDJB MDJC MDJE MDJF Marine Diesel Genset Engines 974-0750Dokument92 SeitenOnan Service Manual MDJA MDJB MDJC MDJE MDJF Marine Diesel Genset Engines 974-0750GreenMountainGenerators80% (10)

- To Introduce BgjgjgmyselfDokument2 SeitenTo Introduce Bgjgjgmyselflikith333Noch keine Bewertungen

- Three-D Failure Criteria Based on Hoek-BrownDokument5 SeitenThree-D Failure Criteria Based on Hoek-BrownLuis Alonso SANoch keine Bewertungen

- Fernandez ArmestoDokument10 SeitenFernandez Armestosrodriguezlorenzo3288Noch keine Bewertungen

- Steam Turbine Theory and Practice by Kearton PDF 35Dokument4 SeitenSteam Turbine Theory and Practice by Kearton PDF 35KKDhNoch keine Bewertungen

- AgentScope: A Flexible Yet Robust Multi-Agent PlatformDokument24 SeitenAgentScope: A Flexible Yet Robust Multi-Agent PlatformRijalNoch keine Bewertungen

- Case StudyDokument2 SeitenCase StudyBunga Larangan73% (11)