Beruflich Dokumente

Kultur Dokumente

Analog Devices - Integrated, High Power Solutions For Xilinx FPGAs

Hochgeladen von

monsOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Analog Devices - Integrated, High Power Solutions For Xilinx FPGAs

Hochgeladen von

monsCopyright:

Verfügbare Formate

Integrated, High Power

Solutions for Xilinx FPGAs

Modern, high performance, FPGA-based systems require an increasing number of dedicated rails supplying core, I/O, memory,

PLL, and precision analog voltages. Typical FPGA-based systems today make use of standalone switching regulators and LDOs,

but as board area continues to shrink as end product form factors shrink, this complicates the task of designing more efficient

power management solutions for powering FPGAs. Combining multiple switching regulators and LDOs into a single package

enables very small, flexible, highly efficient power management solutions for powering FPGAs and precision analog components

with the highest system reliability.

Ultrasmall 12 V/5 V Quad Buck in LFCSP

5V/12V

ADP5054 Solution Size Only 41 mm 20 mm

ADP5054

6A BUCK

VCCINT

6A BUCK

2.5A BUCK

VCCAUX

2.5A BUCK

VCCO_1V2

ADP5054

XILINX

UltraScale

KINTEX/VIRTEX

6A BUCK

VCCO_1V5

6A BUCK

MGTAVCC

2.5A BUCK

MGTAVTT

2.5A BUCK

VCCO_3V3

Fixed and Adjustable Output Voltages

Wide Range of Switching Frequency

Operation (250 kHz to 2 MHz)

Resistor Programmable Current Limit

on Buck 1 and Buck 2 (6 A, 4 A, 2 A )

Simple Power Supply Sequencing

Frequency Synchronization

Input or Output

Parallel Operation on Buck 1 and

Buck 2, and Buck 3 and Buck 4

analog.com/multioutput-regulators

ADP5054 Supply for Xilinx UltraScale Kintex/Virtex

ADP5054 #1

INPUT SAMPLE:

4.5V TO 15.5V

XILINX UltraScale

KINTEX/VIRTEX

PVIN1A

C1

10F

PVIN1B

BST1

PVIN1C

VREG

EN1

C2

VREG

PVIN2A

PVIN2B

R8

DL2

BST2

PVIN3

BST3

C8

BUCK 1/BUCK 2 INTERLEAVED

CONNECTION UP TO 12A

VREG

VCCBATT

VAUX

C10

L3 = 4.7H

BUCK 3

2.5A

EN3

VCCBRAM

L2 = 1.2H

FB2

COMP3

C6

100F

S2

D2

SW3

C11 R11

C5

100F

Q2

SW2C

COMP2

EN2

C4

100F

VCCINT_IO

G2

SW2B

BUCK 2

6A

C9

10F

VCCINT

S1

PGND R4

SW2A

PVIN2C

VCCINT

Q1

G1

DL1

VREG

0.90V TO 0.95V

D1

SW1C

CFG12

L1 = 1.2H

SW1B

VREG

C7

10F

R2

SW1A

BUCK 1

6A

COMP1

C3 R3

R1

FB1

FB3

R9

PGND3

R10

1.8V

VCCAUX

C12

47F

VCCAUX_IO

VCCO_1V8

CFG34

BST4

PVIN4

C14

SW4

C13

10F

BUCK 4

2.5A

COMP4

VCCAUX

VREG

VDD

C17

VCCO_1V2

C16

47F

R13

PGND4

EN4

1.2V

R12

FB4

C15 R14

VREG

L4 = 4.7H

PWRGD R16

PG

INT

REG

GPO1

SYNC/MODE

RT

OSC

R17

C18

VREG

EXP PAD

R18

ADP5054 #2

VDD

VREG

C19

VREG

PWRGD R19

PG

INT

REG

RT

R20

C20

PVIN1A

C21

10F

VCCAUX

PVIN1B

COMP1

BST1

PGND R24

VREG

R28

PVIN2B

BUCK 2

6A

COMP3

C33 R31

VDDR

G2

C25

100F

VCCO_1V5

1.5V

S2

Q2

D2

SW2B

SW2C

L6 = 1.2H

1.0V

VCCO_1

MGTAVCC

R25

C28

BST2

C29

100F

R26

FB2

EN2

EXTERNAL DDR3

VTT DRV

C24

100F

S1

SW2A

PVIN3

C31

10F

DL2

Q1

G1

DL1

VREG

COMP2

MGTAVCC

L5 = 1.2H

D1

SW1C

PVIN2A

C27 R27

VREG

C22

SW1B

EN1

CFG12

VTT

R22

SW1A

BUCK 1

6A

VREG

PVIN2C

R21

FB1

PVIN1C

C23 R23

C26

10F

GPO2

SYNC/MODE

OSC

C30

100F

BST3

C32

SW3

L7 = 4.7H

BUCK 3

2.5A

EN3

VREG

FB3

R29

PGND3

R30

1.20V

VCCAUX_IO

MGTAVTTRCAL

VCCAUX

MGTAVTT

C34

47F

CFG34

ADP121

VMGTVCCAUX

BST4

PVIN4

VCCAUX

C36

SW4

C35

10F

COMP4

C37 R34

BUCK 4

2.5A

EN4

L8 = 4.7H

FB4

R32

PGND4

R33

3.3V

MGTAVCC

VCCO_3V3

C38

47F

EXP PAD

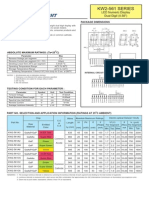

Part

Number

ADP5050

ADP5051

ADP5052

ADP5053

ADP5054

Number of

Outputs

2 4 A1 bucks

2 1.2 A bucks

1 200 mA LDO

2 4 A1 bucks

2 1.2 A bucks

2 4 A1 bucks

2 1.2 A bucks

1 200 mA LDO

2 4 A1 bucks

2 1.2 A bucks

2 6 A2 bucks

2 2.5 A bucks

VIN (V)

4.5 to 15

1.7 to 5.5

4.5 to 15

4.5 to 15

1.7 to 5.5

4.5 to 15

4.5 to 15.5

VOUT (V)

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.5 to 4.75

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.5 to 4.75

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

Max Output

Current (A)

1.2/2.5/41

1.2

200 mA

1.2/2.5/41

1.2

1.2/2.5/41

1.2

200 mA

1.2/2.5/41

1.2

6/4/22

2.5

Resistor programmable current limit (4 A, 2.5 A, or 1.2 A).

2

Resistor programmable current limit (6 A, 4 A, or 2 A).

1

| Integrated, High Power Solutions for Xilinx FPGAs

2

Switching Frequency

Range

250 kHz to 1.4 MHz

I2C

Reset Trip

Min Reset

Typ Watchdog

Threshold (V) Timeout (ms) Timeout (ms)

Yes

Yes

0.5 (adj)

1, 20, 140,

1120

250 kHz to 1.4 MHz

0.5 (adj)

1, 20, 140,

1120

250 kHz to 2 MHz

Package

Price 1k

List ($U.S.)

48-lead LFCSP

4.39

6.3, 102, 1600,

48-lead LFCSP

25,600

4.59

250 kHz to 1.4 MHz

250 kHz to 1.4 MHz

48-lead LFCSP

3.59

6.3, 102, 1600,

48-lead LFCSP

25,600

3.79

48-lead LFCSP

4.29

Xilinx Power Estimator (XPE)Use Cases for Xilinx UltraScale Kintex/Virtex

Bill of Materials for the ADP5054 Powering Xilinx UltraScale Kintex/Virtex

Reference

Quantity

Value

Part Number

Vendor

Footprint (mm)

U1, U2

4-channel micro PMU

ADP5054ACPZ

ADI

C17, C18, C19, C20

C2, C8, C10, C14, C22, C28, C32,

C36

C1, C7, C9, C13, C21, C26, C31, C35

1 F, X5R, 6.3 V

GRM155R60J105KE19D

Murata

7.0 7.0 0.75 QFN

0402

0.1 F, X5R, 16 V

GRM155R61C104KA88D

Murata

0402

C4, C5, C6, C24, C25

C12, C16, C29, C30,

C34, C38

C3, C11, C15,C23, C27, C33, C37

Q1(Q2), Q3(Q4)

L1, L2, L5, L6

10 F, X5R, 25 V

GRM219R61E106KA12

Murata

0805

100 F, X5R, 6.3 V

GRM31CR60J107ME39

Murata

1206

47 F, X5R, 6.3 V

GRM21BR60J476ME15

Murata

0805

2.2 nF, X5R, 25 V

GRM155R61E222KA01D

Murata

0402

Dual N-FETs, 20 V, 25 A, 16 m

Si7232DN

Vishay

3.3 3.3 1.0 QFN

2

4

Dual N-FETs, 30 V, 10 A, 20 m

IRFHM8364

IR

3.3 3.3 0.9 QFN

1.2 H, 22 A, 6.8 m

XAL6030-122ME

Coilcraft

6.0 6.0 3.0

1.3 H, 8.2 A, 16 m

NRS6045-1R3NMGK

Taiyo Yuden

6.0 6.0 4.5

4.7 H, 2.7 A, 57 m

XFL4020-472ME

Coilcraft

4.0 4.0 2.0

4.7 H, 2.0 A, 70 m

NRS4018T-4R7MDGJ

L3, L4, L7, L8

Taiyo Yuden

4.0 4.0 1.8

R17, R20

38.4 k, resistor, 1%

Various

0402

R4, R8, R24, R28

R1, R2, R3, R9, R10, R11, R12, R13,

R14, R21, R22, R23, R25, R26, R27,

R29, R30, R31, R32, R33, R34

R16, R18

22 k, resistor, 5%

Various

0402

21

Resistor, 1%

Various

0402

10 k, resistor, 5%

Various

0402

Notes

Values depend on output

voltage setting

Simplified Application Diagram for the ADP5054 Powering Xilinx UltraScale Kintex/Virtex

VIN = 4.5V TO 15.5V

BUCK 1

BUCK 2

BUCK 3

ADP5054

QUAD BUCK

(6A, 6A, 2.5A, 2.5A)

BUCK 4

VCCINT AND VCCBRAM

VCCAUX AND VCCBATT

XILINX UltraScale

KINTEX/VIRTEX

VCCO_1V2

BUCK 2

VCCO_1V5

BUCK 3

MGTAVCC

BUCK 4

MGTAVTT

ADP5054

QUAD BUCK

(6A, 6A, 2.5A, 2.5A)

BUCK 1

VCCO_xx

MEMORY

DDR2

analog.com/multioutput-regulators

| 3

ADP5050 Supply for Xilinx Zynq

ADP5054

INPUT SAMPLE:

4.5V TO 15.5V

PVIN1A

C1

10F

BST1

PVIN1C

ON

OFF

EN1

VREG

VREG

EN3

VREG

VCCO_1.5V/1.8V

1.5V/1.8V

VDDR

C8

47F

R6

EXTERNAL DDR2/DDR3

VTT DRV

C10

VTT

VAUX

L3 = 4.7H

FB3

R9

PGND3

R10

1.8V

VCCAUX

C12

47F

VCCPAUX

VCCPO_MIO1

CFG34

VCCBATT

BST4

VCCADC

PVIN4

C14

SW4

C13

10F

BUCK 4

2.5A

COMP4

C16 R14

ON

EN4

L4 = 4.7H

3.3V

R12

FB4

VCCO_xx

VCCPO_MIO0

C15

47F

R13

PGND4

OFF

VREG

VDD

VREG

C20

VCCO_DDR

R5

C6

SW3

BUCK 3

2.5A

VCCBRAM

VIO

BST3

COMP3

VCCPINT

C24

47F

L2 = 4.7H

FB2

C9

10F

C11 R11

D2

BST2

EN2

VCCINT

S2

Q2

SW2C

PVIN3

OFF

G2

SW2B

BUCK 2

6A

PVIN2C

COMP2

ON

R8

DL2

C4

47F

S1

PGND R4

SW2A

PVIN2B

0.87V TO 1.03V

Q1

G1

DL1

PVIN2A

ON

L1 = 1H

D1

SW1C

CFG12

C7 R7

OFF

C2

SW1B

VREG

C5

10F

R2

SW1A

BUCK 1

6A

COMP1

C3 R3

XILINX ZYNQ

R1

FB1

PVIN1B

INT

REG

PWRGD R16

PG

GPO1

SYNC/MODE

GPO2

RT

OSC

R21

C19

EXP PAD

ADP223

1.14V TO 1.26V

R25

LDO 1

C23

R22

R23

LDO 2

VCCPLL

C21

1.25V

VREFP

C22

VREFN

R24

ENLD01

ENLD02

Part

Number

ADP5050

ADP5051

ADP5052

ADP5053

ADP5054

Number of

Outputs

2 4 A1 bucks

2 1.2 A bucks

1 200 mA LDO

2 4 A1 bucks

2 1.2 A bucks

2 4 A1 bucks

2 1.2 A bucks

1 200 mA LDO

2 4 A1 bucks

2 1.2 A bucks

2 6 A2 bucks

2 2.5 A bucks

VIN (V)

4.5 to 15

1.7 to 5.5

4.5 to 15

4.5 to 15

1.7 to 5.5

4.5 to 15

4.5 to 15.5

VOUT (V)

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.5 to 4.75

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.5 to 4.75

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

Max Output

Current (A)

1.2/2.5/41

1.2

200 mA

1.2/2.5/41

1.2

1.2/2.5/41

1.2

200 mA

1.2/2.5/41

1.2

6/4/22

2.5

Resistor programmable current limit (4 A, 2.5 A, or 1.2 A).

2 Resistor programmable current limit (6 A, 4 A, or 2 A).

1

| Integrated, High Power Solutions for Xilinx FPGAs

4

Switching Frequency

Range

250 kHz to 1.4 MHz

I2C

Reset Trip

Min Reset

Typ Watchdog

Threshold (V) Timeout (ms) Timeout (ms)

Yes

Yes

0.5 (adj)

1, 20, 140,

1120

250 kHz to 1.4 MHz

0.5 (adj)

1, 20, 140,

1120

250 kHz to 2 MHz

Package

Price 1k

List ($U.S.)

48-lead LFCSP

4.39

6.3, 102, 1600,

48-lead LFCSP

25,600

4.59

250 kHz to 1.4 MHz

250 kHz to 1.4 MHz

48-lead LFCSP

3.59

6.3, 102, 1600,

48-lead LFCSP

25,600

3.79

48-lead LFCSP

4.29

XPE Power EstimationUse Cases for Xilinx Zynq

Note 1: Estimation derived from Xilinx XPE 14.3 Quick Estimate tool.

Note 2: Assumes two A9 cores clocked at 200 MHz and DDR3 memory interface.

Bill of Materials for the ADP5054 Powering Xilinx Zynq

Reference

Quantity

Value

Part Number

Vendor

Footprint (mm)

U1

4-channel micro PMU

ADP5054ACPZ

ADI

7.0 7.0 0.75 QFN

U2

Dual 300 mA LDO

ADP223ACPZ

ADI

2.0 2.0 0.55 QFN

C17, C18, C21, C22, C23

1 F, X5R, 6.3 V

GRM155R60J105KE19D

Murata

0402

C2, C6, C10, C14

0.1 F, X5R, 16 V

GRM155R61C104KA88D

Murata

0402

C1, C5, C9, C13

10 F, X5R, 25 V

GRM219R61E106KA12

Murata

0805

C4, C8, C24

100 F, X5R, 6.3 V

GRM31CR60J107ME39

Murata

1206

C12, C15

47 F, X5R, 6.3 V

GRM21BR60J476ME15

Murata

0805

C3, C7, C11, C16

2.2 nF, X5R, 25V

GRM155R61E222KA01D

Murata

0402

Dual N-FETs, 20 V, 5 A, 54 m

FDMA1024NZ

Fairchild

2.0 2.0 0.8 QFN

Dual N-FETs, 20 V, 4.5 A, 46 m

SIA906EDJ

Vishay

2.0 2.0 0.8 QFN

6.0 6.0 3.0

Q1 (Q2)

L1

1.2 H, 22 A, 6.8 m

XAL6030-122ME

Coilcraft

1.3 H, 8.2 A, 16 m

NRS6045-1R3NMGK

Taiyo Yuden

6.0 6.0 4.5

4.7 H, 2.7 A, 57 m

XFL4020-472ME

Coilcraft

4.0 4.0 2.0

4.7 H, 2.0 A, 70 m

NRS4018T-4R7MDGJ

L2, L3, L4

Taiyo Yuden

4.0 4.0 1.8

R17

38.4 k, resistor, 1%

Various

0402

R4

22 k, resistor, 5%

Various

0402

R8

R1, R2, R3, R5, R6, R7, R9,

R10, R11, R12, R13, R14,

R22, R23, R24, R25

R16

47 k, resistor, 5%

Various

0402

16

Resistor, 1%

Various

0402

10 k, resistor, 5%

Various

0402

Notes

Values depend on output

voltage setting

Simplified Application Diagram for the ADP5054 Powering Xilinx Zynq

VIN = 4.5V TO 15.5V

BUCK 1

VCCINT

BUCK 2

VCCO_xx

BUCK 3

VCCAUX

ADP5054

QUAD BUCK

(6A, 6A, 2.5A, 2.5A)

BUCK 4

ADP223

DUAL LDO

XILINX

ZYNQ

VCCO_xx

VCCPLL

VREFP/VREFN

analog.com/multioutput-regulators

| 5

ADP5054 Supply for Xilinx Virtex-7

ADP5054 #1

INPUT SAMPLE:

4.5V TO 15.5V

PVIN1A

C1

10F

BST1

PVIN1C

C3 R3

ON

OFF

VREG

VREG

R8

DL2

G2

SW2C

COMP2

PVIN3

BUCK 1/BUCK 2 INTERLEAVED

CONNECTION UP TO 12A

L3 = 4.7H

BUCK 3

2.5A

VREG

VCCBATT

VAUX

C10

SW3

EN3

VCCBRAM

S2

BST3

COMP3

C6

100F

L2 = 1.2H

FB2

C9

10F

C5

100F

C8

BST2

EN2

C4

100F

Q2

D2

SW2B

BUCK 2

6A

PVIN2C

OFF

S1

PGND R4

SW2A

PVIN2B

0.87V TO 1.03V

VCCINT

Q1

G1

DL1

VREG

PVIN2A

C11 R11

L1 = 1.2H

D1

SW1C

CFG12

ON

C2

SW1B

EN1

C7

10F

R2

SW1A

BUCK 1

6A

COMP1

XILINX VIRTEX-7

R1

FB1

PVIN1B

FB3

R9

PGND3

R10

1.8V

VCCAUX

C12

47F

VMGTVCCAUX

VCCADC

CFG34

BST4

PVIN4

C14

SW4

C13

10F

BUCK 4

2.5A

COMP4

C15 R14

ON

FB4

VCCAUX_IO

C16

47F

R13

PGND4

EN4

2.0V

R12

OFF

VREG

VDD

VREG

C17

L4 = 4.7H

PWRGD R16

PG

INT

REG

GPO1

SYNC/MODE

RT

OSC

R17

C18

VREG

EXP PAD

R18

ADP5054 #2

VDD

VREG

C19

VREG

PWRGD R19

PG

INT

REG

RT

R20

C20

PVIN1A

C21

10F

PVIN1B

BST1

SW1B

VREG

BUCK 2

6A

COMP2

C27 R27

ON

EN2

OFF

EXTERNAL DDR2/DDR3

VTT DRV

VDDR

R28

G2

C24

100F

C25

100F

C29

47F

C30

47F

S2

Q2

D2

SW2B

SW2C

L6 = 1.2H

0.97V TO 1.08V

VCCO_1

MGTAVCC

R25

C28

R26

BST3

C31

10F

ON

S1

FB2

PVIN3

C33 R31

DL2

BST2

OFF

COMP3

Q1

G1

PGND R24

SW2A

PVIN2B

L5 = 1.2H

D1

DL1

VREG

PVIN2A

PVIN2C

C22

SW1C

CFG12

VTT

R22

SW1A

BUCK 1

6A

C23 R23

EN1

OFF

VREG

C26

10F

R21

FB1

PVIN1C

COMP1

ON

GPO2

SYNC/MODE

OSC

C32

SW3

MGTRREF

L7 = 4.7H

BUCK 3

2.5A

EN3

VREG

FB3

R29

PGND3

R30

1.14V TO 1.26V

100

VCCAUX_IO

MGTAVTTRCAL

VCCAUX

MGTAVTT

C34

47F

CFG34

BST4

PVIN4

COMP4

C37 R34

ON

C36

SW4

C35

10F

OFF

BUCK 4

2.5A

EN4

L8 = 4.7H

FB4

R32

PGND4

R33

1.5V

MGTAVCC

VCCO_xx

C38

47F

EXP PAD

Part

Number

ADP5050

ADP5051

ADP5052

ADP5053

ADP5054

Number of

Outputs

2 4 A1 bucks

2 1.2 A bucks

1 200 mA LDO

2 4 A1 bucks

2 1.2 A bucks

2 4 A1 bucks

2 1.2 A bucks

1 200 mA LDO

2 4 A1 bucks

2 1.2 A bucks

2 6 A2 bucks

2 2.5 A bucks

VIN (V)

4.5 to 15

1.7 to 5.5

4.5 to 15

4.5 to 15

1.7 to 5.5

4.5 to 15

4.5 to 15.5

VOUT (V)

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.5 to 4.75

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.5 to 4.75

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

Max Output

Current (A)

1.2/2.5/41

1.2

200 mA

1.2/2.5/41

1.2

1.2/2.5/41

1.2

200 mA

1.2/2.5/41

1.2

6/4/22

2.5

Resistor programmable current limit (4 A, 2.5 A, or 1.2 A).

2

Resistor programmable current limit (6 A, 4 A, or 2 A).

1

| Integrated, High Power Solutions for Xilinx FPGAs

6

Switching Frequency

Range

250 kHz to 1.4 MHz

I2C

Reset Trip

Min Reset

Typ Watchdog

Threshold (V) Timeout (ms) Timeout (ms)

Yes

Yes

0.5 (adj)

1, 20, 140,

1120

250 kHz to 1.4 MHz

0.5 (adj)

1, 20, 140,

1120

250 kHz to 2 MHz

Package

Price 1k

List ($U.S.)

48-lead LFCSP

4.39

6.3, 102, 1600,

48-lead LFCSP

25,600

4.59

250 kHz to 1.4 MHz

250 kHz to 1.4 MHz

48-lead LFCSP

3.59

6.3, 102, 1600,

48-lead LFCSP

25,600

3.79

48-lead LFCSP

4.29

XPE Power EstimationUse Cases for Xilinx Virtex-7

Xilinx FPGA

Selection

Family

Logic

Elements

Virtex-7

978 k

Power Estimation ConditionsXilinx XPower v14.31

Low Speed

High Speed

Clock Low

Toggle

Clock High

Toggle

Logic Used

Logic Used

Speed (MHz)

Rate (%) Speed (MHz)

Rate (%)

(%)

(%)

100

40

25.00

600

10.00

12.50

DSP/

Slices

BRAM

Blocks

RAM

Clock

(MHz)

Outputs

1000 @

400 MHz

1500

400

200

XCVR

I/O Toggle Out Load

XCVR

Channels

(pF)

Rate (MHz)

Frequency

(GHz)

100

10

10

FPGA Power Consumption Derived from Spreadsheet

ICCINT2

7.65 A (@ 1.0 V)

ICCIO_1V5 (DDR3 Support)

0.1 A (@ 1.5 V)

ICCAUX, ICCO_1V8

0.32 A (@ 1.8 V)

IMGT_AVTT

IMGT_AVCC3

1 A (@ 1.05 V)

0.36 A (@ 1.2 V)

1 Power requirement derived from Xilinx XPE 14.3the spreadsheet assumes at least 50% of resources occupation.

2 4 A to 8 A core current requirement can be achieved by connecting the ADP505x Buck 1 and Buck 2 in interleaved configuration (see Virtex-7 application diagram).

3 Assumes 1.8 V I/O domain and DDR3 control interface, assumes external DDR3 VTT termination driver.

Bill of Materials for the ADP5054 Powering Xilinx Virtex-7

Reference

Quantity

Value

Part Number

Vendor

Footprint (mm)

U1, U2

4-channel micro PMU

ADP5054ACPZ

ADI

C17, C18, C19, C20

C2, C8, C10, C14, C22,

C28, C32, C36

C1, C7, C9, C13, C21, C26,

C31, C35

C4, C5, C6, C24, C25

C12, C16, C29, C30,

C34, C38

C3, C11, C15,C23, C27,

C33, C37

1 F, X5R, 6.3 V

GRM155R60J105KE19D

Murata

7.0 7.0 0.75 QFN

0402

0.1 F, X5R, 16 V

GRM155R61C104KA88D

Murata

0402

Q1(Q2), Q3(Q4)

L1, L2, L5, L6

10 F, X5R, 25 V

GRM219R61E106KA12

Murata

0805

100 F, X5R, 6.3 V

GRM31CR60J107ME39

Murata

1206

47 F, X5R, 6.3 V

GRM21BR60J476ME15

Murata

0805

2.2 nF, X5R, 25 V

GRM155R61E222KA01D

Murata

0402

Dual N-FETs, 20 V, 25 A, 16 m

Si7232DN

Vishay

3.3 3.3 1.0 QFN

7

2

4

Dual N-FETs, 30 V, 23 A, 25 m

IRFHM8364

IR

3.3 3.3 0.9 QFN

2.2 H, 15.9 A, 12.7 m

XAL6030-222ME

Coilcraft

6.0 6.0 3.0

2.3 H, 6.4 A, 22 m

NRS6045-2R3NMGK

Taiyo Yuden

6.0 6.0 4.5

4.7 H, 2.7 A, 57 m

XFL4020-472ME

Coilcraft

4.0 4.0 2.0

4.7 H, 2.0 A, 70 m

NRS4018T-4R7MDGJ

Taiyo Yuden

4.0 4.0 1.8

L3, L4, L7, L8

R17, R20

38.4 k, resistor, 1%

Various

0402

R4, R8, R24, R28

R1, R2, R3, R9, R10, R11,

R12, R13, R14, R21, R22,

R23, R25, R26, R27, R29,

R30, R31, R32, R33, R34

R16, R18

22 k, resistor, 5%

Various

0402

21

Resistor, 1%

Various

0402

10 k, resistor, 5%

Various

0402

Notes

Values depend on output

voltage setting

Simplified Application Diagram for the ADP5054 Powering Xilinx Virtex-7

VIN = 4.5V TO 15.5V

BUCK 1

BUCK 2

BUCK 3

VCCINT AND VCCBRAM

VCCAUX AND VCCBATT

ADP5054

QUAD BUCK

(6A, 6A, 2.5A, 2.5A)

XILINX VIRTEX-7

BUCK 4

VCCAUX_IO

BUCK 2

MGTAVTT

BUCK 3

MGTAVTTRCAL AND GMTAVTT

BUCK 4

VCCO_xx

ADP5054

QUAD BUCK

(6A, 6A, 2.5A, 2.5A)

BUCK 1

MEMORY

DDR2

analog.com/multioutput-regulators

| 7

ADP5054 Supply for Xilinx Artix-7/Kintex-7

ADP5054

INPUT SAMPLE:

4.5V TO 15.5V

C1

10F

PVIN1B

BST1

EN1

VREG

PVIN2A

VTT DRV

Q2

D2

L2 = 2.2H

C8

47F

R6

SW3

BUCK 3

2.5A

EN3

VREG

1.5V

VCCO_1

R5

C6

C10

EXTERNAL DDR3

VDDR

VIO

BST3

COMP3

OFF

VTT

S2

FB2

PVIN3

ON

G2

BST2

C9

10F

C11 R11

R8

DL2

SW2C

EN2

VCCINT

C24

47F

C4

47F

S1

PGND R4

SW2B

BUCK 2

6A

PVIN2C

0.87V TO 1.03V

Q1

SW2A

PVIN2B

COMP2

ON

L1 = 2.2H

G1

DL1

VREG

VCCBRAM

D1

SW1C

CFG12

C7 R7

OFF

C2

SW1B

VREG

C5

10F

R2

SW1A

BUCK 1

6A

COMP1

OFF

R1

FB1

PVIN1C

C3 R3

ON

XILINX

ARTIX-7/KINTEX-7

PVIN1A

C25

47F

VCCO_1V8B

VCCBATT

VAUX

L3 = 4.7H

FB3

R9

PGND3

R10

1.8V

VCCAUX_IO

C12

47F

VCCAUX

VMGTVCCAUX

CFG34

VCCADC

BST4

PVIN4

C14

SW4

C13

10F

BUCK 4

2.5A

COMP4

C16 R14

ON

OFF

EN4

FB4

R12

PGND4

R13

0.97V TO 1.08V

MGTAVCC

C15

47F

VREG

VDD

VREG

C20

L4 = 4.7H

INT

REG

PWRGD R16

PG

GPO1

SYNC/MODE

GPO2

RT

OSC

R21

C19

EXP PAD

MGTRREF

ADP223

1.14V TO 1.26V

R25

LDO 1

C23

R23

MGTAVTT

C21

R22

LDO 2

100

1.25V

MGTAVTTRCAL

VREFP

C22

R24

ENLD01

ENLD02

Part

Number

ADP5050

ADP5051

ADP5052

ADP5053

ADP5054

Number of

Outputs

2 4 A1 bucks

2 1.2 A bucks

1 200 mA LDO

2 4 A1 bucks

2 1.2 A bucks

2 4 A1 bucks

2 1.2 A bucks

1 200 mA LDO

2 4 A1 bucks

2 1.2 A bucks

2 6 A2 bucks

2 2.5 A bucks

VIN (V)

4.5 to 15

1.7 to 5.5

4.5 to 15

4.5 to 15

1.7 to 5.5

4.5 to 15

4.5 to 15.5

VOUT (V)

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.5 to 4.75

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.5 to 4.75

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

Max Output

Current (A)

1.2/2.5/41

1.2

200 mA

1.2/2.5/41

1.2

1.2/2.5/41

1.2

200 mA

1.2/2.5/41

1.2

6/4/22

2.5

Resistor programmable current limit (4 A, 2.5 A, or 1.2 A).

2

Resistor programmable current limit (6 A, 4 A, or 2 A).

1

| Integrated, High Power Solutions for Xilinx FPGAs

8

Switching Frequency

Range

250 kHz to 1.4 MHz

I2C

Reset Trip

Min Reset

Typ Watchdog

Threshold (V) Timeout (ms) Timeout (ms)

Yes

Yes

0.5 (adj)

1, 20, 140,

1120

250 kHz to 1.4 MHz

0.5 (adj)

1, 20, 140,

1120

250 kHz to 2 MHz

Package

Price 1k

List ($U.S.)

48-lead LFCSP

4.39

6.3, 102, 1600,

48-lead LFCSP

25,600

4.59

250 kHz to 1.4 MHz

250 kHz to 1.4 MHz

48-lead LFCSP

3.59

6.3, 102, 1600,

48-lead LFCSP

25,600

3.79

48-lead LFCSP

4.29

XPE Power EstimationUse Cases for Xilinx Artix-7/Kintex-7

Xilinx FPGA Selection

Power Estimation ConditionsXilinx XPower v14.31

Low Speed

High Speed

Clock Low

Toggle

Clock High

Toggle

Logic Used

Logic Used

Speed (MHz)

Rate (%) Speed (MHz)

Rate (%)

(%)

(%)

Family

Logic

Elements

Kintex-7

326 k

100

40

25.00

600

15.00

12.50

Kintex-7

478 k

100

35

25.00

600

10.00

12.50

Virtex-7

978 k

100

40

25.00

600

10.00

12.50

DSP/

Slices

BRAM

Blocks

RAM

Clock

(MHz)

Outputs

XCVR

I/O Toggle Out Load

XCVR

Channels

(pF)

Rate (MHz)

Frequency

(GHz)

500 @

400 MHz

1000 @

400 MHz

1000 @

400 MHz

500

400

200

100

10

1000

400

200

100

10

1500

400

200

100

10

10

FPGA Power Consumption Derived from Spreadsheet

ICCINT2

3.15 A (@ 1.2 V)

4.23 A (@ 1.0 V)

7.65 A (@ 1.0 V)

ICCIO_1V5 (DDR3 Support)

0.1 A (@ 1.5 V)

0.1 A (@ 1.5 V)

0.1 A (@ 1.5 V)

ICCAUX, ICCO_1V83

0.32 A (@ 1.8 V)

0.32 A (@ 1.8 V)

0.32 A (@ 1.8 V)

IMGT_AVCC

IMGT_AVTT

0.511 A (@ 1.0 V)

0.57 A (@ 1.0 V)

1 A (@ 1.05 V)

0.36 A (@ 1.2 V)

0.31 A (@ 1.2 V)

0.36 A (@ 1.2 V)

1 Power requirement derived from Xilinx XPE 14.3the spreadsheet assumes at least 50% of resources occupation.

2 4 A to 8 A core current requirement can be achieved by connecting the ADP505x Buck 1 and Buck 2 in interleaved configuration (see Artix-7/Kintex-7 application diagram).

3 Assumes 1.8 V I/O domain and DDR3 control interface, assumes external DDR3 VTT termination driver.

Bill of Materials for the ADP5054 Powering Xilinx Artix-7/Kintex-7

Reference

Quantity

Value

Part Number

Vendor

Footprint (mm)

U1

4-channel micro PMU

ADP5054ACPZ

ADI

7.0 7.0 0.75 QFN

2.0 2.0 0.55 QFN

U2

Dual 300 mA LDO

ADP223ACPZ

ADI

C17, C18, C21, C22, C23

1 F, X5R, 6.3 V

GRM155R60J105KE19D

Murata

0402

C2, C6, C10, C14

0.1 F, X5R, 16 V

GRM155R61C104KA88D

Murata

0402

C1, C5, C9, C13

10 F, X5R, 25 V

GRM219R61E106KA12

Murata

0805

C4, C8, C24, C25

100 F, X5R, 6.3 V

GRM31CR60J107ME39

Murata

1206

C12, C15

47 F, X5R, 6.3 V

GRM21BR60J476ME15

Murata

0805

C3, C7, C11, C16

2.2 nF, X5R, 25 V

GRM155R61E222KA01D

Murata

0402

Dual N-FETs, 20 V, 25 A, 16 m

Si7232DN

Vishay

3.3 3.3 1.0 QFN

Q1 (Q2)

L1, L2

1

2

Dual N-FETs, 30 V, 10 A, 20 m

IRFHM8364

IR

3.3 3.3 0.9 QFN

2.2 H, 15.9 A, 12.7 m

XAL6030-222ME

Coilcraft

6.0 6.0 3.0

2.3 H, 6.4 A, 22 m

NRS6045-2R3NMGK

Taiyo Yuden

6.0 6.0 4.5

4.7 H, 2.7 A, 57 m

XFL4020-472ME

Coilcraft

4.0 4.0 2.0

4.7 H, 2.0 A, 70 m

NRS4018T-4R7MDGJ

Taiyo Yuden

4.0 4.0 1.8

L3, L4

R17

38.4 k, resistor, 1%

Various

0402

R4, R8

R1, R2, R3, R5, R6, R7, R9,

R10, R11, R12, R13, R14,

R22, R23, R24, R25

R16

22 k, resistor, 5%

Various

0402

16

Resistor, 1%

Various

0402

10 k, resistor, 5%

Various

0402

Notes

Values depend on output

voltage setting

Simplified Application Diagram for the ADP5054 Powering Xilinx Artix-7/Kintex-7

VIN = 4.5V TO 15.5V

BUCK 1

VCCINT

BUCK 2

VCCO_1

BUCK 3

VCCAUX

ADP5054

QUAD BUCK

(6A, 6A, 2.5A, 2.5A)

BUCK 4

ADP223

DUAL LDO

XILINX

ARTIX-7/KINTEX-7

MGTAVCC

MGTAVTT

VREFP

analog.com/multioutput-regulators

| 9

ADP5054 Supply for Xilinx Spartan-6

ADP5054

INPUT SAMPLE:

4.5V TO 15.5V

PVIN1A

C1

10F

BST1

PVIN1C

COMP1

C3 R3

ON

OFF

EN1

VREG

PVIN2A

COMP2

G2

S2

D2

L2 = 2.2H

PVIN3

BST3

C10

COMP3

BUCK 3

2.5A

EN3

VREG

VCCO_1

C8

47F

R6

SW3

1.2V TO 2.5V

R5

C6

FB2

OFF

VCCINT

VIO

Q2

BST2

EN2

OFF

R8

DL2

SW2C

C9

10F

ON

PGND R4

SW2B

BUCK 2

6A

PVIN2C

0.8V TO 1.2V

C4

47F

S1

SW2A

PVIN2B

C11 R11

Q1

G1

DL1

VREG

ON

L1 = 2.2H

D1

SW1C

CFG12

C7 R7

C2

SW1B

VREG

C5

10F

R2

SW1A

BUCK 1

6A

XILINX SPARTAN-6

R1

FB1

PVIN1B

VAUX

L3 = 4.7H

FB3

R9

PGND3

R10

2.5V

VCCAUX

C12

47F

CFG34

BST4

PVIN4

C14

SW4

C13

10F

BUCK 4

2.5A

COMP4

C16 R14

ON

OFF

VDD

Part

Number

Number of

Outputs

2 4 A1 bucks

ADP5050

2 1.2 A bucks

1 200 mA LDO

ADP5051

2 4 A1 bucks

2 1.2 A bucks

2 4 A1 bucks

ADP5052

2 1.2 A bucks

1 200 mA LDO

ADP5053

ADP5054

2 4 A1 bucks

2 1.2 A bucks

2 6 A2 bucks

2 2.5 A bucks

C15

47F

R13

PGND4

MEMORY

(DDR, SRAM, FLASH)

VREG

VREG

C20

1.5V, 1.8V, 3.3V

R12

FB4

EN4

L4 = 4.7H

INT

REG

PWRGD R16

PG

GPO1

SYNC/MODE

GPO2

RT

OSC

R21

C19

EXP PAD

VIN (V)

4.5 to 15

1.7 to 5.5

4.5 to 15

4.5 to 15

1.7 to 5.5

4.5 to 15

4.5 to 15.5

VOUT (V)

Max Output

Current (A)

0.8 to 0.85 VIN

1.2/2.5/41

0.8 to 0.85 VIN

1.2

0.5 to 4.75

200 mA

0.8 to 0.85 VIN

1.2/2.5/41

0.8 to 0.85 VIN

1.2

0.8 to 0.85 VIN

1.2/2.5/41

0.8 to 0.85 VIN

1.2

0.5 to 4.75

200 mA

0.8 to 0.85 VIN

1.2/2.5/41

0.8 to 0.85 VIN

1.2

0.8 to 0.85 VIN

6/4/22

0.8 to 0.85 VIN

2.5

Resistor programmable current limit (4 A, 2.5 A, or 1.2 A).

Resistor programmable current limit (6 A, 4 A, or 2 A).

1

2

10 | Integrated, High Power Solutions for Xilinx FPGAs

Switching Frequency

Range

250 kHz to 1.4 MHz

I2C

Reset Trip

Min Reset

Typ Watchdog

Threshold (V) Timeout (ms) Timeout (ms)

Yes

Yes

0.5 (adj)

1, 20, 140,

1120

250 kHz to 1.4 MHz

0.5 (adj)

1, 20, 140,

1120

250 kHz to 2 MHz

Package

Price 1k

List ($U.S.)

48-lead LFCSP

4.39

6.3, 102, 1600,

48-lead LFCSP

25,600

4.59

250 kHz to 1.4 MHz

250 kHz to 1.4 MHz

48-lead LFCSP

3.59

6.3, 102, 1600,

48-lead LFCSP

25,600

3.79

48-lead LFCSP

4.29

XPE Power EstimationUsage Case for Spartan-6

Xilinx FPGA

Selection

Power Estimation1

Low Speed

Logic

Clock Low

Logic Used

Elements Speed (MHz)

(%)

Family

Spartan-6

<150 k

100

40

Spartan-6

with XCVR

<150 k

100

40

RAM

Toggle Clock High

High Speed

Toggle

DSP/

RAM

I/O Toggle Out Load

XCVR

XCVR

Clock Outputs

(pF)

Rate (%) Speed (MHz) Logic Used (%) Rate (%) Instances Blocks

Rate (MHz)

Frequency Channels

(MHz)

36 36

12.50

600

15.00

12.50

150

100

150

50

30

N/A

N/A

mult/80

36 36

12.50

600

15.00

12.50

150

300

150

50

30

4

1.25 GHz

mult/80

FPGA Power Consumption Derived from Spreadsheet 2

ICCINT + ICC

1.658 A (@ 1.2 V)

1.82 A (@ 1.2 V)

ICCIO + ICCPO + ICCPO

0.039 A (@ 2.5 V)

0.039 A (@ 2.5 V)

ICCAUX

MGT_VCC_PLL

MGT_Tx_Rx

0.051 A (@ 2.5 V)

0.066 A (@ 2.5 V)

N/A

0.29 A (@ 1.2 V)

N/A

0.18 A (@ 1.2 V)

1 Power requirement derived from Xilinx XPE 13.3the spreadsheet assumes at least 50% of resources occupation with 12.5% toggle rate. The core current is kept below the maximum driving capability of the suggested micro PMU.

2 The proposed micro PMU supplies three FPGA rails: VCCINT, VCCO, and VCCAUX from Buck 1, Buck 2, and Buck 3, respectively. Buck 2 and Buck 3 have spare power to power external peripheral devices and static or low power DDR

memories. Only one I/O supply voltage is considered, and multiple I/O banks with different voltage levels can be supported.

Bill of Materials for the ADP5054 Powering Xilinx Spartan-6

Reference

Quantity

Value

Part Number

Vendor

Footprint (mm)

U1

4-channel micro PMU

ADP5054ACPZ

ADI

7.0 7.0 0.75 QFN

C17, C18

1 F, X5R, 6.3 V

GRM155R60J105KE19D

Murata

0402

C2, C6, C10, C14

0.1 F, X5R, 16 V

GRM155R61C104KA88D

Murata

0402

C1, C5, C9, C13

10 F, X5R, 25 V

GRM219R61E106KA12

Murata

0805

C4, C8

100 F, X5R, 6.3 V

GRM31CR60J107ME39

Murata

1206

C12, C15

47 F, X5R, 6.3 V

GRM21BR60J476ME15

Murata

0805

C3, C11, C16

2.2 nF, X5R, 25 V

GRM155R61E222KA01D

Murata

0402

Dual N-FETs, 20 V, 5 A, 54 m

FDMA1024NZ

Fairchild

2.0 2.0 0.8 QFN

Q1 (Q2)

L1, L2

Dual N-FETs, 20 V, 3.4 A, 45 m

IRLHS6276

IR

2.0 2.0 0.8 QFN

Dual N-FETs, 20 V, 4.5 A, 46 m

SIA906EDJ

Vishay

2.0 2.0 0.8 QFN

2.2 H, 3.7 A, 21 m

XFL4020-222ME

Coilcraft

4.0 4.0 2.0

2.2 H, 3.0 A, 42 m

NRS4018T-2R2MDGJ

Taiyo Yuden

4.0 4.0 1.8

4.7 H, 2.7 A, 57 m

XFL4020-472ME

Coilcraft

4.0 4.0 2.0

4.7 H, 2.0 A, 70 m

NRS4018T-4R7MDGJ

Taiyo Yuden

4.0 4.0 1.8

L3, L4

R17

38.4 k, resistor, 1%

Various

0402

R4, R8

R1, R2, R3, R9, R10, R11,

R12, R13, R14

R16

No assembly

Various

0402

Resistor, 1%

Various

0402

10 k, resistor, 5%

Various

0402

Notes

Values depend on output

voltage setting

Simplified Application Diagram for the ADP5054 Powering Xilinx Spartan-6

VIN = 4.5V TO 15.5V

BUCK 1

VCCINT

BUCK 2

VCCO_1

BUCK 3

VCCAUX

ADP5054

QUAD BUCK

(6A, 6A, 2.5A, 2.5A)

BUCK 4

XILINX SPARTAN-6

MEMORY

analog.com/multioutput-regulators

| 11

ADP5054 and ADP5050/ADP5051/ADP5052/ADP5053

ADP5054 Quad Buck Switching Regulator in LFCSP

Key Features

VIN

4.5V TO 15.5V

CH1/CH2: programmable 2 A/4 A/6 A sync

buck regulator with low-side FET driver

ADP5054

6A BUCK REG1

6A BUCK REG1

2.5A BUCK REG

2.5A BUCK REG

0.8V TO 0.85 VIN @ 6A

Parallel CH1/CH2 to deliver up to 12 A output

CH3/CH4: 2.5 A buck regulator

0.8V TO 0.85 VIN @ 6A

0.8V TO 0.85 VIN @ 2.5A

Parallel CH3/CH4 to deliver up to 5 A output

Wide input range: 4.5 V to 15.5 V

Resistor adjustable or fixed output voltage

0.8V TO 0.85 VIN @ 2.5A

250 kHz 2 MHz adjustable switching frequency

PWGRD

1/2 fSW selective for each channel

Precision enable on accurate 0.8 V threshold

Programmable current limit in CH1/CH2

Soft start timer programmable

1 Resistor programmable current limit (6 A, 4 A, or 2 A).

FPWM/PSM mode selection

Active output discharge switch

PWRGD flag on selective channels

Frequency synchronization input or output

Hiccup or latch-off for output short protection

UVLO, OCP, TSD

7 mm 7 mm, 48-lead LFCSP package

ADP5050/ADP5051/ADP5052/ADP5053 Quad Buck Switching Regulator with LDO or POR/WDI in LFCSP

ADP5050/

ADP5052

12V/5V

INPUT

OPTIONAL

I 2C

ADP5051/

ADP5053

4A BUCK REG1

1.2V

4A BUCK REG1

2.5V

1.2A BUCK REG

1.8V

1.2A BUCK REG

3.3V

12V/5V

INPUT

OPTIONAL

I 2C

200mA LDO

1.5V

PWRGD

MR

WDI

4A BUCK REG1

1.0V

4A BUCK REG1

2.5V

1.2A BUCK REG

1.8V

1.2A BUCK REG

3.3V

POWER-ON,

RESET, AND

WATCHDOG

VTHR

RESET

PWRGD

1 Resistor programmable current limit (4 A, 2.5 A, or 1.2 A).

Key Features

Wide input voltage range: 4.5 V to 15 V

1.5% output accuracy over full

temperature range

250 kHz to 1.4 MHz adjustable switching

frequency

Adjustable/fixed output options via factory

Pseudo DVS (dynamic voltage scaling)

I2C interface with interrupt supportive on fault

condition

CH1/CH2: programmable 1.2 A/2.5 A/4 A sync

buck regulator with low-side FET driver

CH3/CH4: 1.2 A sync buck regulator

CH5: 200 mA low dropout LDO or watchdog

timer and power-on reset

Precision enable on 0.8 V accurate threshold

12 | Integrated, High Power Solutions for Xilinx FPGAs

Active output discharge switch

FPWM/PSM mode selection

Frequency synchronization input or output

Power-good flag on selective channels

Startup with the precharged output

7 mm 7 mm, 48-lead LFCSP package

40C to +125C junction temperature

I2C functionality

Low Power, Spartan-6 Integrated Power Solutions

ADP5135: Triple, 1.8 A, 3 MHz Buck Regulator

in LFCSP

ADP5135

XILINX SPARTAN-6

3.0V TO 5.5V

Key Features

AVIN

C7

0.1F

AGND

HOUSEKEEPING

Main input voltage range 3.0 V to 5.5 V

Three 1800 mA buck regulators

ON

SW1 L1 1H

EN1

1.8A

BUCK 1

OFF

4 mm 4 mm, 24-lead LFCSP package

Regulator accuracy of 1.8%

Individual, dedicated buck, power-good pins

VIN2

3 MHz buck operation with forced PWM and

automatic PWM/PSM modes

ON

EN2

1.8A

BUCK 2

Buck output voltage range from 0.8 V to 3.8 V

ON

R2

MODE

FPWM

AUTO

GPOx

VEN3

FB2

R3

PGND2

R4

VCCO_1

C4

22F

VOUT3

VIN3

C5

10F

Power for processors, application specific integrated

circuits (ASICs), field programmable gate arrays (FPGAs),

and radio frequency (RF) chipsets

PGND1

VCCINT

C2

22F

SW2 L2 1H

OFF

Applications

R1

FB1

VOUT2

C3

10F

Precision enable pins for easier power sequencing

VDDIO/

TO VEN2

VOUT1

VIN1

C1

10F

SW3 L3 1H

1.8A

BUCK 3

EN3

R5

FB3

PGND3

VCCAUX

C6

22F

R6

OFF

VDDIO

POWER

GOOD

R7

PG1

PG2

R8

R9

GPIx

PG3

AGND

ADP5134: Dual, 3 MHz, 1.2 A Buck Regulator with Two

300 mA LDOs with Precision Enable and a Power Good

in LFCSP

Key Features

ADP5134

XILINX SPARTAN-6

VIN

2.5V TO 5.5V

VIN1

ON

4 mm 4 mm, 24-lead LFCSP package

C3

4.7F

Factory programmable or external adjustable VOUTx

ON

Precision enable pin for easier power sequencing

EN2

C5

0.1F

VINLDO1

1.7V TO 5.5V

PGND1

R2

MODE

FPWM

AUTO

VCCINT

C2

10F

GPOx

FB2

R3

PGND2

R4

VCCO_1

C4

10F

ON

VINLDO2

1.7V TO 5.5V

HOUSEKEEPING

VIN3

C6

1F

OFF

EN3

VOUT3

LDO 1

300mA

R5

FB3

R6

VMEM

C7

1F

VIN4

C8

1F

LDO 1/LDO 2: input voltage range from 1.7 V to 5.5 V

R1

SW2 L2 1H

1.2A

BUCK 2

AVIN

Buck 1/Buck 2: output voltage range from 0.8 V to 3.8 V

Power for processors, application specific integrated

circuits (ASICs), field programmable gate arrays (FPGAs),

and radio frequency (RF) chipsets

L1 1H

FB1

OFF

Factory selectable power-good pin

Applications

VDDIO

VOUT2

VIN2

Regulator accuracy of 1.8%

LDO 1/LDO 2: high PSRR and low output noise

EN1

1.2A

BUCK 1

OFF

Two 1200 mA buck regulators and

two 300 mA LDO regulators

LDO 1/LDO 2: output voltage range of 0.8 V to 5.2 V

SW1

C1

4.7F

Main input voltage range 2.5 V to 5.5 V

3 MHz buck operation with forced PWM and

automatic PWM/PSM modes

VOUT1

ON

EN4

LDO 2

300mA

VOUT4

FB4

R7

R8

OFF

POWER

GOOD

PG

VCCAUX

C9

1F

VDDIO

R1

100k

GPIx

AGND

analog.com/multioutput-regulators

| 13

14 | Integrated, High Power Solutions for Xilinx FPGAs

2 buck

1 LDO

2 buck

1 LDO

Adj (0.8 to 3.8)

Adj (0.8 to 5.2)

Buck: 2.3 to 5.5

LDO: 1.7 to 5.5

Dual, 3 MHz buck regulator

with dual LDO

Dual, 3 MHz buck regulator

Dual, 3 MHz buck regulator

with dual LDO

Triple, 3 MHz buck regulator

Dual, 3 MHz, 800 mA

buck regulator with dual

300 mA LDO

3 MHz buck regulator

with dual LDO

3 MHz buck regulator with

dual LDO, supervisor, and

watchdog timer

ADP5034

ADP5133 New

ADP5134 New

ADP5135 New

ADP5037

ADP5040

ADP5041

Triple, 200 mA LDO

Triple, 200 mA LDO

Quad buck regulator

with LDO with I2C

Quad buck regulator, POR,

and WDI with I2C

Quad buck

regulator with LDO

Quad buck regulator

with POR and WDI

Quad buck regulator

ADP322

ADP323

ADP5050 New

ADP5051 New

ADP5052 New

ADP5053 New

ADP5054 New

1 Resistor programmable current limit (4 A, 2.5 A, or 1.2 A).

2 Resistor programmable current limit (6 A, 4 A, or 2 A).

Triple, 200 mA LDO

ADP320

ADP5071 New

Dual dc-to-dc with boost

and inverter outputs for

generating VPOS and VNEG

Dual dc-to-dc with boost

and inverter outputs for

generating VPOS and VNEG

Dual, 3 MHz buck

regulator with dual LDO

ADP5033

ADP5070 New

Buck: 3.0 to 5.5

Dual, 1.2 A buck

with 300 mA LDO

ADP5024

2 buck

2 LDO

Adj (0.8 to 5.2)

2 LDO

LDO: 1.7 to 5.5

LDO1: 3.3; LDO2: 1.8, 3.3; LDO3: 1.5

0.5 to 4.75

LDO: 1.7 to 5.5

Buck: 4.5 to 15.5

0.8 to 0.85 VIN

0.8 to 0.85 VIN

0.8 to 0.85 VIN

Buck: 4.5 to 15

Buck: 4.5 to 15

0.8 to 0.85 VIN

0.5 to 4.75

LDO: 1.7 to 5.5

Buck: 4.5 to 15

0.8 to 0.85 VIN

LDO1: 3.3, 2.8, 2.5; LDO2: 2.8, 2.5, 1.8; LDO3: 1.8,

1.5, 1.2

Adj (0.5 to 5)

Buck: 4.5 to 15

1.8 to 5.5

1.8 to 5.5

1.8 to 5.5

Boost/inverter:

2.85 to 15

Boost/inverter:

2.85 to 15

1200

40001

2 buck

200

40001

1200

60002

2500

1 LDO

2 buck

2 buck

2 buck

2 buck

1200

40001

2 buck

2 buck

2 buck

200

1200

1 LDO

2 buck

Yes

Yes

0.5 (adj)

0.5 (adj)

1, 20, 140, 1120

1, 20, 140, 1120

6.3, 102, 1600,

25,600

6.3, 102, 1600,

25,600

Individual precision enable

pins with power good

Individual precision enable

pins with power good

Individual precision enable

pins with power good

I2C interface with individual precision

enable pins and power good

I2C interface with individual precision

enable pins and power good

40001

Fixed VOUT options

Individual enable pins, adjustable

outputs, soft start and slew rate

Individual enable pins, adjustable

outputs, soft start and slew rate

Individual enable pins

and supervisor, WDI,

mode pin, and MR pin

Individual enable pins,

mode pin

48-lead LFCSP

48-lead LFCSP

48-lead LFCSP

48-lead LFCSP

48-lead LFCSP

16-lead LFCSP

16-lead LFCSP

16-lead LFCSP

20-lead LFCSP

20-lead TSSOP

20-lead LFCSP

20-lead TSSOP

20-lead LFCSP

20-lead LFCSP

24-lead LFCSP

24-lead LFCSP

Precision enable pins

and power-good pins

Mode pin,

individual enable pins

24-lead LFCSP

16-ball WLCSP

28-lead TSSOP

24-lead LFCSP

16-ball WLCSP

24-lead LFCSP

24-lead LFCSP

16-ball WLCSP

Package

Precision enable pins

and power-good pins

Adjustable and fixed outputs

Mode pin, individual enable pins

Mode pin, two enable pins

Mode pin, individual enable pins

Mode pin, individual enable pins

Mode pin, individual enable pins

Key Features

2 buck

102, 1600

Typ Watchdog

Timeout (ms)

Fixed VOUT options

20, 140

Min Reset

Timeout (ms)

Adjustable VOUT options

0.5 (adj)

Reset Trip

Threshold (V)

200

I2C

200

200

Input current limit:

boost: 1 A,

inverter: 0.6 A

Input current limit:

boost: 2 A,

inverter: 1.2 A

300

1200

300

1200

300

800

1800

300

1200

800

300

1200

300

800

300

1200

300

800

150

600

Output

Current (mA)

3 LDO

3 LDO

3 LDO

1 boost

1 buck

Adj (0.8 to 3.8)

Buck: 2.3 to 5.5

1 inverter

2 LDO

LDO: 1.7 to 5.5

Boost: VIN to 39

1 buck

Adj (0.8 to 3.8)

Adj (0.8 to 5.2)

Buck: 2.3 to 5.5

Inverter: 0.5 V to 39 V below VIN

2 LDO

Adj (0.8 to 5.2)

LDO: 1.7 to 5.5

1 boost

2 buck

Adj (0.8 to 3.8)

Buck: 2.3 to 5.5

1 inverter

3 buck

Adj (0.8 to 3.8)

Inverter: 0.5 V to 39 V below VIN

2 LDO

Adj (0.8 to 5.2)

Boost: VIN to 39

2 buck

Adj (0.8 to 5.2)

LDO: 1.7 to 5.5

Buck: 2.5 to 5.5

Buck: 2.3 to 5.5

2 buck

2 LDO

2 buck

Buck: 3.3, 3.0, 2.8, 2.5, 2.3, 2.0, 1.8,

1.6, 1.5, 1.4, 1.3, 1.2, 1.1, 1.0, 0.9

LDO: 3.3, 3.0, 2.8, 2.5, 2.25, 2.0, 1.8,

1.7, 1.6, 1.5, 1.2, 1.1, 1.0, 0.9, 0.8

Adj (0.8 to 3.8)

Adj (0.8 to 3.8) or 3.3, 3.0, 2.8, 2.5, 2.3, 2.0, 1.8,

1.6, 1.5, 1.4, 1.3, 1.2, 1.1, 1.0, 0.9

Adj (0.8 to 3.8)

LDO: 1.7 to 5.5

Buck: 2.3 to 5.5

LDO: 1.7 to 5.5

Buck: 2.3 to 5.5

Buck: 2.3 to 5.5

1 LDO

Adj (0.8 to 5.2)

Dual, 800 mA buck

with 300 mA LDO

LDO: 1.7 to 5.5

ADP5023

Buck: 2.3 to 5.5

2 buck

Number of

Outputs

LDO: 1.7 to 5.5

VOUT (V)

Buck: 3.3, 3.0, 2.8, 2.5, 2.3, 2.0, 1.82, 1.8, 1.6, 1.5,

1.3, 1.2, 1.1, 1.0, 0.9, 0.8

LDO: 3.3, 3.0, 2.9, 2.8, 2.775, 2.5, 2.0, 1.875, 1.8, 1.75,

1.7, 1.65, 1.6, 1.55, 1.5, 1.2

Adj (0.8 to 3.8)

VIN (V)

Dual, 3 MHz buck

with 150 mA LDO

Product Description

ADP5022

Part Number

Integrated Power Management Solutions (Micro PMUs)

4.29

3.79

3.59

4.59

4.39

0.54

0.54

0.54

2.39

2.19

1.79

1.39

1.69

1.69

2.09

1.29

1.99

1.90

1.79

1.59

1.80

Price

1k List

($U.S.)

ADIsim Power Design CenterSelect, Design, and Simulate with ADIsimPower Tools

ADP505x Design Tool

ADIsimPower now supports the ADP505x family of multichannel high voltage

PMUs. This new family of parts supports four or five channels from inputs up to

15 V and with load current up to 4 A per channel. Users can optimize the design

by taking into account the thermal contributions of each channel by cascading

channels, and even by placing the high current channels in parallel to create

an 8 A rail. With the advanced features, users can specify independently

each channels performance from ripple and transient to switching frequency

selection from the channels that support half the master frequency. As with all

the other tools, evaluation boards are available by requests directly from the

tool. Download at download.analog.com/PMP/ADP505x_BuckDesigner.zip.

Step 1:

Step 2:

Optimize for size, cost,

or efficiency

Specify each channels operating

conditions, including do not use

analog.com/ADIsimPower

analog.com/ADIsimPE

analog.com/multioutput-regulators

| 15

Analog Devices, Inc.

Worldwide Headquarters

Analog Devices, Inc.

One Technology Way

P.O. Box 9106

Norwood, MA 02062-9106

U.S.A.

Tel: 781.329.4700

(800.262.5643,

U.S.A. only)

Fax: 781.461.3113

Analog Devices, Inc.

Europe Headquarters

Analog Devices, Inc.

Wilhelm-Wagenfeld-Str. 6

80807 Munich

Germany

Tel: 49.89.76903.0

Fax: 49.89.76903.157

Analog Devices, Inc.

Japan Headquarters

Analog Devices, KK

New Pier Takeshiba

South Tower Building

1-16-1 Kaigan, Minato-ku,

Tokyo, 105-6891

Japan

Tel: 813.5402.8200

Fax: 813.5402.1064

Analog Devices, Inc.

Asia Pacific Headquarters

Analog Devices

5F, Sandhill Plaza

2290 Zuchongzhi Road

Zhangjiang Hi-Tech Park

Pudong New District

Shanghai, China 201203

Tel: 86.21.2320.8000

Fax: 86.21.2320.8222

2015 Analog Devices, Inc. All rights reserved.

Trademarks and registered trademarks are the

property of their respective owners.

BR10508-0-2/15(B)

analog.com/multioutput-regulators

Das könnte Ihnen auch gefallen

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsVon EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNoch keine Bewertungen

- PVI-3.8/4.6-I-OUTD 3.8 To 4.6 KW: ABB String InvertersDokument4 SeitenPVI-3.8/4.6-I-OUTD 3.8 To 4.6 KW: ABB String InvertersRicho DeepNoch keine Bewertungen

- Op Amps: Design, Application, and TroubleshootingVon EverandOp Amps: Design, Application, and TroubleshootingBewertung: 5 von 5 Sternen5/5 (2)

- Huong Dan Ket Noi S7-200Dokument9 SeitenHuong Dan Ket Noi S7-200duyphuocNoch keine Bewertungen

- PVI-10.0/12.5-TL-OUTD 10 To 12.5 KW: ABB String InvertersDokument4 SeitenPVI-10.0/12.5-TL-OUTD 10 To 12.5 KW: ABB String InvertersVarazhdinecNoch keine Bewertungen

- Industrial Signal ChainDokument24 SeitenIndustrial Signal ChainprocyonstNoch keine Bewertungen

- OPTOCOUPLER 817cDokument7 SeitenOPTOCOUPLER 817cJose Luis MamaniNoch keine Bewertungen

- Data SH Power Supplies Mixed Signal MaximDokument23 SeitenData SH Power Supplies Mixed Signal MaximbmmostefaNoch keine Bewertungen

- DAC08Dokument20 SeitenDAC08Severiano Jaramillo QuintanarNoch keine Bewertungen

- 5 5 7 Single Color Alingap Dot Matrix Led Displays: Ltp-2057A/2157A SeriesDokument3 Seiten5 5 7 Single Color Alingap Dot Matrix Led Displays: Ltp-2057A/2157A SeriesSandro GamarraNoch keine Bewertungen

- Omron Auxiliary RelayDokument14 SeitenOmron Auxiliary RelayNima MahmoudpourNoch keine Bewertungen

- Data Sheet: TDA1558QDokument11 SeitenData Sheet: TDA1558QMarco Tulio Da SilvaNoch keine Bewertungen

- 300mA LDO REGULATOR RP114x SERIES DATA SHEETDokument28 Seiten300mA LDO REGULATOR RP114x SERIES DATA SHEETSol De GabrielNoch keine Bewertungen

- ADF7012Dokument28 SeitenADF7012Filip ZalioNoch keine Bewertungen

- Ad 844Dokument12 SeitenAd 844Marciel DervansokiNoch keine Bewertungen

- Series: Output Power S1500 S2000 S3000 S4000 S6000 S3004 S4004 S4044 S6004 S6044 Weight DepthDokument2 SeitenSeries: Output Power S1500 S2000 S3000 S4000 S6000 S3004 S4004 S4044 S6004 S6044 Weight DepthАлексей АндрияшNoch keine Bewertungen

- DAC0808 DatasheetDokument12 SeitenDAC0808 DatasheetRicky CoxNoch keine Bewertungen

- A8504 Datasheet PDFDokument19 SeitenA8504 Datasheet PDFChemaArellanoDiazNoch keine Bewertungen

- 38C44YMDokument11 Seiten38C44YMbehzadNoch keine Bewertungen

- White LED Driver With Wide PWM Dimming Range Features: FN6264.3 Data Sheet March 7, 2008Dokument10 SeitenWhite LED Driver With Wide PWM Dimming Range Features: FN6264.3 Data Sheet March 7, 2008ram12krishnaNoch keine Bewertungen

- 3 V/5 V, 1 MW 2-/3-Channel 16-Bit, Sigma-Delta Adcs: A MaxDokument32 Seiten3 V/5 V, 1 MW 2-/3-Channel 16-Bit, Sigma-Delta Adcs: A Maxmeroka2000Noch keine Bewertungen

- Sonora 4SATPL-T DIRECTV Slimline Polarity LockerDokument5 SeitenSonora 4SATPL-T DIRECTV Slimline Polarity LockerDavid WardNoch keine Bewertungen

- Audio Circuits Using The NE5532/34Dokument11 SeitenAudio Circuits Using The NE5532/34Jose Simon Bolivar MoranNoch keine Bewertungen

- ABB Inverter SpecificationsDokument4 SeitenABB Inverter SpecificationsPatanjali PamidighantamNoch keine Bewertungen

- High-output 4-channel car audio amplifier with protection circuitsDokument9 SeitenHigh-output 4-channel car audio amplifier with protection circuitsban4444Noch keine Bewertungen

- LTM 4628Dokument36 SeitenLTM 4628Nelson LauNoch keine Bewertungen

- TDA1554Q 44W Audio AmplifierDokument11 SeitenTDA1554Q 44W Audio Amplifiersava7698Noch keine Bewertungen

- 0773 SNAP Digital Input Modules Data SheetDokument13 Seiten0773 SNAP Digital Input Modules Data Sheetbaron_tailNoch keine Bewertungen

- Broadband Distribution Passives EnglishDokument12 SeitenBroadband Distribution Passives EnglishbvlahovicyuNoch keine Bewertungen

- Sonora SD-PI-6S-T DIRECTV Slimline Polarity Locker and Power InserterDokument5 SeitenSonora SD-PI-6S-T DIRECTV Slimline Polarity Locker and Power InserterDavid WardNoch keine Bewertungen

- ADF4351 DatasheetDokument28 SeitenADF4351 DatasheetpravinrautrautNoch keine Bewertungen

- RT8802ADokument29 SeitenRT8802Anishatiwari82Noch keine Bewertungen

- VC1611 SeriesDokument30 SeitenVC1611 SeriesShakti SinghNoch keine Bewertungen

- Ca3306 (A, C)Dokument17 SeitenCa3306 (A, C)notaden1849Noch keine Bewertungen

- Microchip MCU Product SelectorDokument47 SeitenMicrochip MCU Product SelectorkavnaranganNoch keine Bewertungen

- LA76818A Monolithic Linear IC for PAL/NTSC Color TVDokument44 SeitenLA76818A Monolithic Linear IC for PAL/NTSC Color TVGonzales JavierNoch keine Bewertungen

- Capacitor Contactors Benedict JägerDokument12 SeitenCapacitor Contactors Benedict Jägermv1970Noch keine Bewertungen

- The Ovation E-Amp: A 180 W High-Fidelity Audio Power AmplifierDokument61 SeitenThe Ovation E-Amp: A 180 W High-Fidelity Audio Power AmplifierNini Farribas100% (1)

- 06 Pomocni Sklopnici I RelejiDokument55 Seiten06 Pomocni Sklopnici I Relejiaksiom007Noch keine Bewertungen

- AD8541Dokument20 SeitenAD8541gliga vasileNoch keine Bewertungen

- Schneider GV2 Motor Circuit BreakerDokument19 SeitenSchneider GV2 Motor Circuit BreakercatalinccNoch keine Bewertungen

- Velleman Pcsu200 Usb Oszi GeneratorDokument18 SeitenVelleman Pcsu200 Usb Oszi Generatorsandro2009Noch keine Bewertungen

- Contactores GEDokument2 SeitenContactores GEPapi CruzNoch keine Bewertungen

- ADA MN3007 Rev5 Jan2010 Documentation Rev20120225Dokument12 SeitenADA MN3007 Rev5 Jan2010 Documentation Rev20120225ismaelsleiferNoch keine Bewertungen

- RF Transistor Specifications and Selection GuideDokument5 SeitenRF Transistor Specifications and Selection Guideeduardo acostaNoch keine Bewertungen

- Service Manual: XM-2165GTXDokument24 SeitenService Manual: XM-2165GTXkodenNoch keine Bewertungen

- XR-215 PLLDokument32 SeitenXR-215 PLLJ Jesús Villanueva GarcíaNoch keine Bewertungen

- List IC CampurDokument17 SeitenList IC CampurFudin Safudin100% (2)

- LC Mos High Speed 4-And 8-Channel 8-Bit Adcs Ad7824/Ad7828Dokument16 SeitenLC Mos High Speed 4-And 8-Channel 8-Bit Adcs Ad7824/Ad7828meroka2000Noch keine Bewertungen

- Up To 6 GHZ Low Noise Silicon Bipolar Transistor Chip: Technical DataDokument5 SeitenUp To 6 GHZ Low Noise Silicon Bipolar Transistor Chip: Technical DataPrathamesh MestryNoch keine Bewertungen

- LM 4755Dokument18 SeitenLM 4755Ovidio RiosNoch keine Bewertungen

- C 011 AredDokument21 SeitenC 011 AredreidashmanNoch keine Bewertungen

- KW2-561 SERIES: Description: Package DimensionsDokument1 SeiteKW2-561 SERIES: Description: Package DimensionsValdivia FranciscoNoch keine Bewertungen

- Altivar ATV61HU55N4 CatalogueDokument4 SeitenAltivar ATV61HU55N4 CatalogueEugen Marius BadescuNoch keine Bewertungen

- Data Sheet: MGA-425P8Dokument15 SeitenData Sheet: MGA-425P8Aparna BhardwajNoch keine Bewertungen

- IC E 92AD Service ManualDokument60 SeitenIC E 92AD Service Manualvk4tuxNoch keine Bewertungen

- T Te Esstt S Se Ett C CM MC C2 25 56 6: Unique Test Sets From The Technology LeaderDokument6 SeitenT Te Esstt S Se Ett C CM MC C2 25 56 6: Unique Test Sets From The Technology Leaderhalitates21Noch keine Bewertungen

- Panasonic Inverter ManualDokument8 SeitenPanasonic Inverter Manualsamernet2100% (1)

- MAX2038Dokument24 SeitenMAX2038Fabio NevesNoch keine Bewertungen

- Mic 4424Dokument13 SeitenMic 4424Adrian MargescuNoch keine Bewertungen

- Recolored Image Detection Via A Deep Discriminative Model: P.Yugandhar Sharma 1304-21-862-024Dokument67 SeitenRecolored Image Detection Via A Deep Discriminative Model: P.Yugandhar Sharma 1304-21-862-024yugandhar sharmaNoch keine Bewertungen

- SmartBus G4 IR Emitter (Data Sheet)Dokument2 SeitenSmartBus G4 IR Emitter (Data Sheet)Smart-G4Noch keine Bewertungen

- RBAC Framework IntroductionDokument32 SeitenRBAC Framework IntroductionΑλέξιος ΠηλίδηςNoch keine Bewertungen

- Iface SDK ManualDokument86 SeitenIface SDK ManualSergio Dominguez100% (1)

- TP45 HP/TP43 HP Setup ManualDokument65 SeitenTP45 HP/TP43 HP Setup Manualpeter_basti_lpNoch keine Bewertungen

- TC-508 Service ManualDokument79 SeitenTC-508 Service ManualgilbertopkrNoch keine Bewertungen

- Sony HDR-CX330 CX330E PJ330E PJ340 PJ340E PJ350 PJ350E Lev2Dokument19 SeitenSony HDR-CX330 CX330E PJ330E PJ340 PJ340E PJ350 PJ350E Lev2Rafael LehmkuhlNoch keine Bewertungen

- VBA Error CodesDokument4 SeitenVBA Error CodesLuisNoch keine Bewertungen

- Application Performance Analysis - Sharkfest - WiresharkDokument58 SeitenApplication Performance Analysis - Sharkfest - WiresharktaicyberNoch keine Bewertungen

- Java Exp AllDokument34 SeitenJava Exp AllNishant SawantNoch keine Bewertungen

- Microprocessor Lab1Dokument17 SeitenMicroprocessor Lab1Abdul HadiNoch keine Bewertungen

- db2 ApplicationDokument452 Seitendb2 ApplicationMangalagowri Akuleti100% (1)

- Making Symbian Development Easier With FShell: A Console Environment For The Symbian PlatformDokument13 SeitenMaking Symbian Development Easier With FShell: A Console Environment For The Symbian PlatformSEE2010 Platform Developer TrackNoch keine Bewertungen

- Preload InstallerDokument2 SeitenPreload InstallerAlex SanchezNoch keine Bewertungen

- Service Manual For TOSHIBA Satellite L300Dokument174 SeitenService Manual For TOSHIBA Satellite L300c1-1zNoch keine Bewertungen

- Bitdefender GravityZone Business Security Premium Datasheet enDokument2 SeitenBitdefender GravityZone Business Security Premium Datasheet enHalaNoch keine Bewertungen

- Ejemplo Cronograma Del Proyecto Según Pud RupDokument2 SeitenEjemplo Cronograma Del Proyecto Según Pud RupNair Estefani Hancco CruzNoch keine Bewertungen

- Cubot X9 CeDokument4 SeitenCubot X9 CeSaqib HussainNoch keine Bewertungen

- Verbose logging startedDokument35 SeitenVerbose logging startedemartemm1503Noch keine Bewertungen

- Electricity Mangement SystemDokument27 SeitenElectricity Mangement SystemAjith MathewNoch keine Bewertungen

- Toshiba e Studio163 203 165 205 Printer Brochure PDFDokument2 SeitenToshiba e Studio163 203 165 205 Printer Brochure PDFMohamed ZayedNoch keine Bewertungen

- PACS Server Components: Merge Healthcare - ConfidentialDokument26 SeitenPACS Server Components: Merge Healthcare - ConfidentialPrashantNoch keine Bewertungen

- CRC Modeling:: Bridging The Communication Gap Between Developers and UsersDokument18 SeitenCRC Modeling:: Bridging The Communication Gap Between Developers and UsersSridhar GundavarapuNoch keine Bewertungen

- MC SIMOTION D410 Operating Manual PDFDokument101 SeitenMC SIMOTION D410 Operating Manual PDFramon nava100% (1)

- C++ Intro Chapter 1: Learn Programming FundamentalsDokument37 SeitenC++ Intro Chapter 1: Learn Programming FundamentalsdzikrydsNoch keine Bewertungen

- 3gpp - SIM Application ToolkitDokument157 Seiten3gpp - SIM Application ToolkitGuru BalaguruNoch keine Bewertungen

- Chapter 3 and 4 - Reliability, Maintainability, and Availability of Facilities and The Assessment and Control of Product Reliability - 2019Dokument35 SeitenChapter 3 and 4 - Reliability, Maintainability, and Availability of Facilities and The Assessment and Control of Product Reliability - 2019endalkachewNoch keine Bewertungen

- Employee Management System: # Rule NameDokument9 SeitenEmployee Management System: # Rule NameSavitha KrishnaswamyNoch keine Bewertungen

- CV Vaibhav Shete PDFDokument5 SeitenCV Vaibhav Shete PDFVaibh RamaNoch keine Bewertungen