Beruflich Dokumente

Kultur Dokumente

Case Study On: Time Division Multiplexing and Demultiplexing BY K.Sahi (1230414128)

Hochgeladen von

sahi_kolukuluri99Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Case Study On: Time Division Multiplexing and Demultiplexing BY K.Sahi (1230414128)

Hochgeladen von

sahi_kolukuluri99Copyright:

Verfügbare Formate

CASE STUDY ON

Time Division

Multiplexing

And

Demultiplexing

BY

K.SAHI

(1230414128)

Page | 2

TIME DIVISION MULTIPLEXING DEMULTIPLEXING

AIM:

To generate the time division multiplexing and

demultiplexing wave forms.

APPARATUS:

1. MATLAB SOFTWARE

2. system

INTRODUCTION:

Time Division Multiplexing is the technique for

simultaneous transmission of more than one intelligence

signals on one channel and the single carrier by utilizing

the time scale without loss of identity of an individual

signal. SS LAB trainer DC-5 (5M & 5D) is a self sustained

kit for the demonstration of 2 Channel Time Division

Multiplexer & De-multiplexer system. This system provides

visual understanding of actual TDM concepts, and this

consists of:

Page | 3

1.TDM Multiplexer :

1. Regulated power supply.

2. Audio Frequency signal generators.

3. 2 channel TDM multiplexer.

4. Clock generator.

5. Logic source.

2. TDM De-Multiplexer :

1. Regulated power supply.

2. 2 channel TDM de-multiplexer.

3. Clock generator.

4. 2 nos of passive low pass filters.

5. 2 nos of audio amplifiers.

6. Logic source.

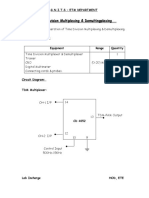

CIRCUIT DIAGRAM:

Page | 4

THEORY:

This consists of a bridge rectifier followed by

Capacitor filters and three terminal regulators 7805 and

7905 to provide regulated DC voltages of 5V @ 300 mA

Page | 5

to the on board circuits. These supplies have been

internally connected to the circuits, so no external

connections are required for operation.

Audio Frequency (AF) Signal generators :

Sine wave signals of 400 Hz & 200 Hz are generated

from AF generator-1 and AF generator -2 respectively to

use as a message signals to be transferred. These

generators are Op-Amp based Wein bridge Oscillators

using IC TL084. IC TL084 is a FET input general purpose

Operational Amplifier. Amplitude control is provided in the

circuit to vary the output amplitude of AF signal.

Clock generator :

A TTL compatible clock signal of variable frequency is

provided on board to use as a control (timing) signal to the

multiplexer & de-multiplexer circuits. This circuit has been

designed based on the application of CMOS integrated

circuits in linear mode. Here IC 4069 is used as an active

device. 4069 is a CMOS hex inverters integrated circuit.

Page | 6

Three inverters are used to form a oscillator and other

three are connected as a buffer to isolate oscillator from

output and to improve current capability.

Logic source :

As name indicates this provides logic signals i.e.

Logic1 (represents +5V) and Logic 0 (represents 0V).

This is a simple two way switch followed by a buffer circuit

and this is applicable in single step operation of

multiplexer & de-multiplexer circuits.

Low pass filters :

These are a series of simple RC networks provided

on board to reconstruct the message signals from PAM

signals i.e. output of the de-multiplexer. RC values are

chosen such that the cutoff frequency would be at 200 Hz.

Amplifiers :

Page | 7

These are Op-amp (IC TL084) based non-inverting

variable gain amplifiers provided on board to amplify the

recovered message singles i.e. output of the Low pass

filter to desired level.

Amplitude control is provided in

circuit to vary the gain of the amplifier between 0 and 10.

AC/DC Switch facilitates to couple the input signal through

capacitor or directly to the amplifier input.

2 Channel TDM multiplexer :

Figure 1:1 shows the TDM Multiplexer using 4052.

CD 4052 IC is a 4 channel analog multiplexer/demultiplexer and is used as an active component in this

circuit. One of the control signals (pin 9) of 4052 is

grounded so that 4052 will act as a two channel

multiplexer and other control input (pin 10) is being

terminated as control signal of TDM Multiplexer. The

message signals that are to be transmitted has to be

connected to CH1 and CH2 inputs of the CD 4052. TL084

has been used as a buffer at input of the CD4052 in order

to avoid loading effect on signal sources. For pin

Page | 8

configuration and other operating conditions of IC 4052

you can go through the data sheet provided along with

manual.

Operation:

When control signal is 1 i.e. control signal is logic high

(+5V), output of the 4052 is connected to CH1 and

whatever signal at CH1 is there, it will be passed on to

output. Similarly when control signal is 0 (0V), output of

the multiplexer (4052) is connected to CH2 and the signal

at this input will be passed on to output. In summary:

If control signal is 1.

CH1 will be connected to

the multiplexer output

If control signal is 0.

CH2 will be connected to

the multiplexer output.

When we drive this control signal with a clock signal

(square wave) of desired frequency the output of the

Page | 9

multiplexer

will

be

connected

to

CH1

and

CH2

automatically in sequence depend on clock signal

condition i.e. ON/OFF time. So multiplexer samples each

the input signals in sequence and transmits over a single

channel. If you make one of the input signal amplitude to

zero, output of the multiplexer is a simple natural top PAM

signal otherwise it is a Time Division Multiplexed PAM. In

the same way we can use any pulse modulation technique

(i.e. PWM, PPM, PCM) instead of PAM, here we have

selected PAM.

Output of the TDM multiplexer has been terminated with

RCA Socket which is useful to connect a cable (represents

actual transmission line) to transmit TDM-PAM signal to

de-multiplexer (DC-5D).

2 Channel TDM De-multiplexer :

Figure 1:2 shows the TDM De-multiplexer using 4052.

IC CD 4052 is a 4 channel analog multiplexer/demultiplexer and is used as an active component in this

Page | 10

circuit. One of the control signals (pin 9) of 4052 is

grounded so that 4052 will act as a two channel demultiplexer and other control input (pin 10) is being

terminated as control signal of TDM de-multiplexer. The

TDM signal that has to be de-multiplexed is connected to

a common input (pin 13). De-multiplexed outputs are

taken as CH1 (from pin 14) and CH2 (pin 12). Outputs of

the de-multiplexer can be connected to low pass filters

for smoothing the output. TL084 has been used as a buffer

at input of the CD4052 in order to avoid loading effect on

signal sources. For pin configuration and other operating

conditions of IC 4052 you can go through the data sheet

provided along with manual.

Operation:

When control signal is 1 i.e. control signal is logic

high (+5V), input of the 4052 is connected to CH1 output

and the signal which is at input will be passed on to

output. Similarly when control signal is 0 (0V), input of the

multiplexer (4052) is connected to CH2 output and the

Page | 11

signal at the input will be passed on to output. In

summary:

If control signal is 1.De-multiplexer Input will be

connected to CH1output.

If control signal is 0De-multiplexer Input will be

connected to CH2 output.

When we drive this control signal with a clock signal

(square wave) of desired frequency the input of the demultiplexer will be connected to CH1 output and CH2

output automatically in sequence depend on clock signal

condition i.e. ON/OFF time. So a part of the TDM-PAM

signal will be passed on to CH1 and CH2 in sequence

depend on clock signal condition i.e. to CH1 during ON

time and to CH2 during OFF time. Output of CH1 and CH2

are simple natural top PAM signals. The original AF

signals can be recovered from these PAM signal by

smoothening with low pass filters. These recovered AF

Page | 12

signals can be amplified with the help of amplifiers

provided on board if desired.

Synchronization:

De-multiplexer at the receiver should be operate in

synchronize with the multiplexer which is at transmitter in

order to recover the original signals without any loss. In

actual communication system a synch signal will be added

to the TDM signal and the clock generator at receiver will

be triggered with the synch signal. In general these synch

signals will be a over sized in amplitude or in width

depends on the modulation technique which we adapts. In

this trainer synch signal is not added in TDM, any facility

has been provided to study the effect of synchronization

on recovered signal. For this a clock generator (which

represents a local oscillator) is provided in de-multiplexer

kit , and we can use the same clock which is used at

transmitter .

Page | 13

PROCEDURE:

Page | 14

Page | 15

Page | 16

Page | 17

Page | 18

Page | 19

Page | 20

Page | 21

Page | 22

Page | 23

Page | 24

Das könnte Ihnen auch gefallen

- Rəqəmsal SistemlərDokument30 SeitenRəqəmsal SistemlərAsgeriNoch keine Bewertungen

- 5.2 PWM 7 Mac 2017Dokument34 Seiten5.2 PWM 7 Mac 2017Elawarasi Nadarajan100% (1)

- Counter& State MachinesDokument55 SeitenCounter& State MachinesFahim MahmudNoch keine Bewertungen

- Time Division Multiplexing & DemultiplexingDokument11 SeitenTime Division Multiplexing & Demultiplexingaeganajith9Noch keine Bewertungen

- Digital Communications Laboratory List of ExpermentsDokument70 SeitenDigital Communications Laboratory List of ExpermentsElectronics & communication engineering AstcNoch keine Bewertungen

- Lab Manual Me CsDokument109 SeitenLab Manual Me CschitraselvakumarNoch keine Bewertungen

- DC Lab-MinDokument71 SeitenDC Lab-MinKiran U NNoch keine Bewertungen

- Digital Communications Lab MannualDokument74 SeitenDigital Communications Lab MannualwizardvenkatNoch keine Bewertungen

- New DC Lab ManualDokument53 SeitenNew DC Lab Manualsriram128Noch keine Bewertungen

- Digital Communications: Lab Manual (Student Copy)Dokument78 SeitenDigital Communications: Lab Manual (Student Copy)dhileepan DilipNoch keine Bewertungen

- DCLabDokument31 SeitenDCLabani rohiraNoch keine Bewertungen

- Bapatla Engineering College Digital Communications Lab EC-451Dokument30 SeitenBapatla Engineering College Digital Communications Lab EC-451nithyamnvNoch keine Bewertungen

- Time Division Multiplexing & DemultingplexingDokument5 SeitenTime Division Multiplexing & Demultingplexingneha yarrapothuNoch keine Bewertungen

- DC Lab ManualDokument12 SeitenDC Lab ManualHarikrishnan Manakara RadhakrishnanNoch keine Bewertungen

- UG - EC303 DSP Part-6 On-Chip Peripherals-Print PDFDokument20 SeitenUG - EC303 DSP Part-6 On-Chip Peripherals-Print PDFapuurvaNoch keine Bewertungen

- SRP9100 Service ManualDokument70 SeitenSRP9100 Service ManualGeovane BarbosaNoch keine Bewertungen

- Digital Signal FormatsDokument25 SeitenDigital Signal Formatsبلال الحمودىNoch keine Bewertungen

- Digital Communications Lab: List of ExperimentsDokument50 SeitenDigital Communications Lab: List of ExperimentsNeel SarkarNoch keine Bewertungen

- DTMF Based ProjectDokument21 SeitenDTMF Based ProjectABHIJEET MOHARANANoch keine Bewertungen

- Communication II Lab (EELE 4170)Dokument6 SeitenCommunication II Lab (EELE 4170)Fahim MunawarNoch keine Bewertungen

- Ec8561 Communication SystemDokument77 SeitenEc8561 Communication SystemMariyaNoch keine Bewertungen

- DTMF BasedDokument22 SeitenDTMF BasedABHIJEET MOHARANANoch keine Bewertungen

- 41 Mobile100 TechnicalDokument107 Seiten41 Mobile100 TechnicalCauVong JustinNoch keine Bewertungen

- Communciation Lab ReportDokument12 SeitenCommunciation Lab ReportNur NadhirahNoch keine Bewertungen

- Protection Coupler Learning 8.3.13 PDFDokument79 SeitenProtection Coupler Learning 8.3.13 PDFcrazy1021Noch keine Bewertungen

- Communciation Lab ReportDokument12 SeitenCommunciation Lab ReportNur NadhirahNoch keine Bewertungen

- Single-Chip Modem Provides Low-Cost Data Communication: National Semiconductor Application Note 444 Wesley Lee July 1986Dokument16 SeitenSingle-Chip Modem Provides Low-Cost Data Communication: National Semiconductor Application Note 444 Wesley Lee July 1986Luis CarlosNoch keine Bewertungen

- Department of E.C.E.: Digital Communications Lab ManualDokument29 SeitenDepartment of E.C.E.: Digital Communications Lab Manualమొక్కపాటి మాధవిNoch keine Bewertungen

- DC Lab ManualDokument54 SeitenDC Lab ManualAbhimanyu YadavNoch keine Bewertungen

- Low Power UART Design For Serial Data CommunicationDokument21 SeitenLow Power UART Design For Serial Data CommunicationSuman Gm100% (1)

- Tty To Rs232Dokument8 SeitenTty To Rs232sandeepverma8257100% (2)

- Tda 10021 DatasheetDokument17 SeitenTda 10021 DatasheetWilly DacoNoch keine Bewertungen

- Simple Digital To Analog Converter (DAC) : PWM V R CDokument4 SeitenSimple Digital To Analog Converter (DAC) : PWM V R CSaafirNoch keine Bewertungen

- Complete Notes On TSEXDokument16 SeitenComplete Notes On TSEXKasiSivaAnkamreddiNoch keine Bewertungen

- MC145151-2 and MC145152-2: PLL Frequency Synthesizers (CMOS)Dokument24 SeitenMC145151-2 and MC145152-2: PLL Frequency Synthesizers (CMOS)Willington Augusto ArizaNoch keine Bewertungen

- AN1207 For MC145170Dokument6 SeitenAN1207 For MC145170ftbenji123Noch keine Bewertungen

- Nec Corporation: November 30th, 2012Dokument7 SeitenNec Corporation: November 30th, 2012Thantoe AungNoch keine Bewertungen

- Nnew - DC Lab ManualDokument106 SeitenNnew - DC Lab ManualKalidindi TejasreeNoch keine Bewertungen

- JFBKL: ApplicationsDokument11 SeitenJFBKL: ApplicationsAnandha PadmanabhanNoch keine Bewertungen

- Lab Manual: Shree Ramchandra College of Engineering, Lonikand, Pune - 412 216Dokument20 SeitenLab Manual: Shree Ramchandra College of Engineering, Lonikand, Pune - 412 216divyang_pNoch keine Bewertungen

- TK 3107Dokument28 SeitenTK 3107Abe LimiNoch keine Bewertungen

- DC Lab ManualDokument24 SeitenDC Lab Manualvidyae100% (2)

- NSD 50&mcdDokument25 SeitenNSD 50&mcdkrishnamanikandanNoch keine Bewertungen

- Data Sheet: Radio Tuning PLL Frequency SynthesizerDokument13 SeitenData Sheet: Radio Tuning PLL Frequency SynthesizerElchat InternacionalNoch keine Bewertungen

- Design of Integer N Frequency Divider For High Performance PLL Using 180 NM CMOS TechnologyDokument8 SeitenDesign of Integer N Frequency Divider For High Performance PLL Using 180 NM CMOS Technology123abhijeetNoch keine Bewertungen

- Block Diagram:: Device Control Using Mobile PhoneDokument12 SeitenBlock Diagram:: Device Control Using Mobile PhoneNirosh KumarNoch keine Bewertungen

- LTE Data Rate CalculationDokument72 SeitenLTE Data Rate Calculationarslan arifNoch keine Bewertungen

- Codec ChipDokument11 SeitenCodec Chipbalachandra1234Noch keine Bewertungen

- Open Ended CS SolvedDokument17 SeitenOpen Ended CS SolvedMalik Ali BiadNoch keine Bewertungen

- Electronics & Communication EngineeringDokument41 SeitenElectronics & Communication EngineeringKrishna Chaitanya TNoch keine Bewertungen

- Delta Modulation For Voice Transmission: Application Note January 1997 AN607.1Dokument6 SeitenDelta Modulation For Voice Transmission: Application Note January 1997 AN607.1Mac AnciadoNoch keine Bewertungen

- Multi-Channel Digital Up/Down Converter For Wimax Systems: FeaturesDokument13 SeitenMulti-Channel Digital Up/Down Converter For Wimax Systems: FeaturesAmandeep GroverNoch keine Bewertungen

- PWM Outputs Enhance Sensor Signal ConditionersDokument5 SeitenPWM Outputs Enhance Sensor Signal Conditionersshabir faridiNoch keine Bewertungen

- Increase The Frequency Resolution of PWM ModulesDokument10 SeitenIncrease The Frequency Resolution of PWM Modulesxeratule100% (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Digital Signal Processing: Instant AccessVon EverandDigital Signal Processing: Instant AccessBewertung: 3.5 von 5 Sternen3.5/5 (2)

- High-Performance D/A-Converters: Application to Digital TransceiversVon EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Bewertung: 2.5 von 5 Sternen2.5/5 (3)

- Fundamentals of Electronics 3: Discrete-time Signals and Systems, and Quantized Level SystemsVon EverandFundamentals of Electronics 3: Discrete-time Signals and Systems, and Quantized Level SystemsNoch keine Bewertungen

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsVon EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsNoch keine Bewertungen

- Cs6201 Digital Principles and System Design: Unit IDokument19 SeitenCs6201 Digital Principles and System Design: Unit IUttam NeelapureddyNoch keine Bewertungen

- The Design of A Microcontroller Temperature Compensated Crystal Oscillator SPL Mu CTCXO and Automatic Compensation LineDokument8 SeitenThe Design of A Microcontroller Temperature Compensated Crystal Oscillator SPL Mu CTCXO and Automatic Compensation LineWagner CunhaNoch keine Bewertungen

- Todos Os CIsDokument44 SeitenTodos Os CIsTales VitorNoch keine Bewertungen

- List of 7400 Series Integrated Circuits-2003Dokument7 SeitenList of 7400 Series Integrated Circuits-2003Kalisetty SureshNoch keine Bewertungen

- Agilent 34970aDokument440 SeitenAgilent 34970ajulioga09Noch keine Bewertungen

- Verilog HDL: ModuleDokument9 SeitenVerilog HDL: ModuleM Usman RiazNoch keine Bewertungen

- Siemens FMX 5Dokument66 SeitenSiemens FMX 5Nicolaie Nicusor100% (1)

- Basic Digital ElectronicsDokument25 SeitenBasic Digital ElectronicsKshitij GurjarNoch keine Bewertungen

- Digital Systems Lab - Catalog DescriptionDokument3 SeitenDigital Systems Lab - Catalog Descriptionmani_vlsiNoch keine Bewertungen

- 74HC138 74HCT138: 1. General DescriptionDokument18 Seiten74HC138 74HCT138: 1. General DescriptionCADASEDANoch keine Bewertungen

- BSC It PDFDokument29 SeitenBSC It PDFKiran MurmuNoch keine Bewertungen

- Dexin Nds3106 Tunerinputmux 0Dokument3 SeitenDexin Nds3106 Tunerinputmux 0Igo FernandesNoch keine Bewertungen

- Co Assignment AnswersDokument14 SeitenCo Assignment AnswersSravani GunnuNoch keine Bewertungen

- De Lab ManualDokument71 SeitenDe Lab Manualbchaitanya_555Noch keine Bewertungen

- Workshop Week 4 PDFDokument4 SeitenWorkshop Week 4 PDFStevenRNoch keine Bewertungen

- Multiplexer, Decoder and Encoder PDFDokument37 SeitenMultiplexer, Decoder and Encoder PDFKishore Gurram100% (1)

- Mod 10 Up CounterDokument83 SeitenMod 10 Up CounterradhakrishnanNoch keine Bewertungen

- PIC18F4550: PLL Prescaler Selection BitsDokument6 SeitenPIC18F4550: PLL Prescaler Selection BitsFrancisco Javier García GarcíaNoch keine Bewertungen

- 74Ls Series: Lower Power Schottky Low Power SchottkyDokument1 Seite74Ls Series: Lower Power Schottky Low Power SchottkyFrancisco JuarezNoch keine Bewertungen

- 195421055-Electronics-Symbols-Cheat-Sheet 2 PDFDokument14 Seiten195421055-Electronics-Symbols-Cheat-Sheet 2 PDFfissionstarNoch keine Bewertungen

- 74 Ls 138Dokument3 Seiten74 Ls 138RushabhShahNoch keine Bewertungen

- (Cp1068 A) Digiac UkDokument12 Seiten(Cp1068 A) Digiac UkAlberto M FuentesNoch keine Bewertungen

- STLD Regular Jntu Question Papers 2008Dokument9 SeitenSTLD Regular Jntu Question Papers 2008anjaneyulud100% (1)

- I o ChannelsDokument7 SeitenI o ChannelsShakir KapraNoch keine Bewertungen

- Chip Design Easily Implement PLL Clock Switching For At-Speed Test by Ron Press & Jeff BoyerDokument13 SeitenChip Design Easily Implement PLL Clock Switching For At-Speed Test by Ron Press & Jeff BoyerraghudatheshgpNoch keine Bewertungen

- 1151CS104 Digitalelectronics SyllabusDokument2 Seiten1151CS104 Digitalelectronics Syllabusdogece8707Noch keine Bewertungen

- Mechatronics MCQDokument35 SeitenMechatronics MCQmech mech189% (19)

- @vtucode - In-Dd&c0 Question Bank With SolutionDokument31 Seiten@vtucode - In-Dd&c0 Question Bank With SolutionPraneethNoch keine Bewertungen