Beruflich Dokumente

Kultur Dokumente

Vinafix - VN E5-773 14277

Hochgeladen von

rasrozi5170Originalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Vinafix - VN E5-773 14277

Hochgeladen von

rasrozi5170Copyright:

Verfügbare Formate

5

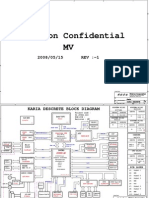

Wistron-SKLU Schematics

Brook_SLU

2015-06-29

REV : -1M

DY : None Installed

UMA: UMA only installed

DIS: DISCRTE OPTIMUS installed

Brook_SLU

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A3

Date:

Cover Page

Document Number

Brook_SLU

Monday, July 06, 2015

Sheet

1

Rev

1M

1

of

105

Project code:

Brook SL 17 --> 4PD058010001

PCB P/N:14277

Revision: SC

CHARGER

HPA02224RGRR-1-GP

INPUTS

OUTPUTS

AD+

44

DCBATOUT

BT+

SYSTEM DC/DC

RT6575D

INPUTS

3D3V_AUX_S5

5V_AUX_S5

DCBATOUT 5V_S5

3D3V_S5

VRAM

DDR3 900 4Gb

78-81

LCD

DDR3L 1333/1600 Channel A

eDPx4

55

DDR3

Intel CPU

HDMI 1.4b

GPU

N16-GT

DDR3L 1333/1600 Channel B

Skylake U

HDMI

57

Slot 1

12

Slot 2

46,47

ISL95813HRZ-GP

33

INPUTS

OUTPUTS

13

DCBATOUT VCC_CORE

DDR3L SUS

76-86

DPC

RTD2168

DDI

SKL PCH-LP

RT8231AGQW-GP

INPUTS

OUTPUTS

CRT PORT

56

56

USB2.0 x 2

IO PORT

0D675V_S0

6 USB 3.0 ports

USB2.0 x 2

USB3.0 x 1

USB3.0 x 1

35

High Definition Audio

66

CPU 1D0V_S5

USB Charger

TPS2544 36

RT8231AGQW-GP

INPUTS

OUTPUTS

3 SATA ports

USB2.0 x1

USB3.0 x 1

35

PCIe / USB2.0

LPC I/F

WLAN + BT

CPU 1.8V_S5

61

55

USB2.0 x 1

LAN

PCIe x 1

RTL8111G(S)

RJ45

31

38

USB3.0 x 1

CardReader

USB2.0 x1

RTS5170

mSATA

(NGFF)

SATA/ PCIe x 4

HDD

SATA x 2

SATA3.0

33

ODD

HDA

SPEAKER

29

HD Audio Codec

ALC255

SPI

63

60

OUTPUTS

1D8V_S5

1D8V_S0

5V_S5

5V_S0

3D3V_S5

3D3V_S0

1V_S5

1V_VCCIO

1V_VCCST

60

Touch PAD (PTP)

I2C

TPM

LPC BUS

NPCT650 91

65

PCB LAYER

29

SPI Flash

25

8MB

L1:Top

L2:VCC

L3:Signal

L4:Signal

L5:GND

L6:Signal

LPC debug port

68

CONBO JACK

40

INPUTS

27

53

DCBATOUT 1D8V_S5

32

Switches

3D Camera

(optional)

RT8068AZQWID-GP-U

INPUTS

OUTPUTS

ACPI 5.0

Camera

52

DCBATOUT 1D0V_S5

6 PCIE ports

USB3.0 x 1

51

DCBATOUT 1D35V_S3

10 USB 2.0/1.1 ports

USB2.0 x1

CPU Core Power

28W (UMA)

15W (DIS)

PCIe x 4, DDI

45

OUTPUTS

I2C

SPI

KBC

VD_IN

ENE9028,ENE9038

24

Thermistor

26

SMBus

29

Charger

29

KB BACKLIGHT

Keyboard

DMIC X2

65

HPA02224

44

65

25

FAN

Wistron Confidential document, Anyone can not

Duplicate, Modify, Forward or any other purpose

application without get Wistron permission

Brook_SLU

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

C

Date:

5

Block Diagram

Document Number

Brook_SLU

Monday, July 06, 2015

Sheet

Rev

1M

2

of

105

Main Func = CPU

HDMI

CRT

56

56

56

56

E55

F55

E58

F58

F53

G53

F56

G56

HDMI_DATA_CPU_N2

HDMI_DATA_CPU_P2

HDMI_DATA_CPU_N1

HDMI_DATA_CPU_P1

HDMI_DATA_CPU_N0

HDMI_DATA_CPU_P0

HDMI_DATA_CPU_N3

HDMI_DATA_CPU_P3

C50

D50

C52

D52

A50

B50

D51

C51

DDI_VGA_DATA_CPU_N0

DDI_VGA_DATA_CPU_P0

DDI_VGA_DATA_CPU_N1

DDI_VGA_DATA_CPU_P1

SKYLAKE_ULT

DDI1_TXN[0]

DDI1_TXP[0]

DDI1_TXN[1]

DDI1_TXP[1]

DDI1_TXN[2]

DDI1_TXP[2]

DDI1_TXN[3]

DDI1_TXP[3]

DDI2_TXN[0]

DDI2_TXP[0]

DDI2_TXN[1]

DDI2_TXP[1]

DDI2_TXN[2]

DDI2_TXP[2]

DDI2_TXN[3]

DDI2_TXP[3]

DDI

EDP_TXN[0]

EDP_TXP[0]

EDP_TXN[1]

EDP_TXP[1]

EDP_TXN[2]

EDP_TXP[2]

EDP_TXN[3]

EDP_TXP[3]

EDP

HDMI

L13

L12

14,57 HDMI_CLK_CPU

14,57 HDMI_DATA_CPU

N7

N8

6 DDPC_CDA

1V_VCCIO

14 DDPD_CDA

R301

1 24D9R2F-L-GP

2

N11

N12

E52

EDP_RCOMP

GPP_E18/DDPB_CTRLCLK

GPP_E19/DDPB_CTRLDATA

DDI1_AUXN

DDI1_AUXP

DDI2_AUXN

DDI2_AUXP

DDI3_AUXN

DDI3_AUXP

Strap

GPP_E20/DDPC_CTRLCLK

GPP_E21/DDPC_CTRLDATA

Strap

GPP_E22/DDPD_CTRLCLK

GPP_E23/DDPD_CTRLDATA

Strap

GPP_E13/DDPB_HPD0

GPP_E14/DDPC_HPD1

GPP_E15/DDPD_HPD2

GPP_E16/DDPE_HPD3

GPP_E17/EDP_HPD

EDP_BKLTEN

EDP_BKLTCTL

EDP_VDDEN

EDP_RCOMP

SKYLAKE-GP-U1

EDP_AUXN

EDP_AUXP

EDP_DISP_UTIL

DISPLAY SIDEBANDS

eDP

1 OF 20

CPU1A

57

57

57

57

57

57

57

57

C47

C46

D46

C45

A45

B45

A47

B47

eDP_TX_CPU_N0

eDP_TX_CPU_P0

eDP_TX_CPU_N1

eDP_TX_CPU_P1

eDP_TX_CPU_N2

eDP_TX_CPU_P2

eDP_TX_CPU_N3

eDP_TX_CPU_P3

E45

F45

55

55

55

55

55

55

55

55

20150209 SC Jack

eDP_AUX_CPU_N 55

eDP_AUX_CPU_P 55

3D3V_S5

B52

G50

F50

E48

F48

G46

F46

L9

L7

L6

N9

L10

R12

R11

U13

PCH_DPC_AUXN 56

PCH_DPC_AUXP 56

EC_SMI# 1

CRT

R302

10KR2F-L1-GP

2

DY

R303 move to RN602

EC_SMI#

EC_SCI#

HDMI_DET_CPU 57

DP_HPD_CPU 56

EC_SMI# 24

EC_SCI# 6,24

eDP_HPD_CPU 55

eDP

eDP_BLEN_CPU 24

eDP_BLCTRL_CPU 55

eDP_VDDEN_CPU 55

eDP_BLEN_CPU

R304

1 100KR2F-L3-GP

2

071.SKYLA.000U

(#543016) eDP_RCOMP Guideline

Signal

Trace

Width

Isolation

Spacing

Resistor

Value

eDP_RCOMP

20 mils

25 mils

24.9 1%

Length

Max = 100 mils

Design Guideline:

Skylake processor signal eDP_RCOMP should be connected to the VCCIO rail via a single 24.9 1% resistor.

Brook_SLU

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A3

Date:

5

CPU_(DISPLAY)

Document Number

Rev

Brook_SLU

Monday, July 06, 2015

Sheet

1

1M

3

of

105

Main Func = CPU

DDR3L ball type: Interleaved Type

D

2 OF 20

CPU1B

SKYLAKE_ULT

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

AL71

AL68

AN68

AN69

AL70

AL69

AN70

AN71

AR70

AR68

AU71

AU68

AR71

AR69

AU70

AU69

AF65

AF64

AK65

AK64

AF66

AF67

AK67

AK66

AF70

AF68

AH71

AH68

AF71

AF69

AH70

AH69

BB65

AW65

AW63

AY63

BA65

AY65

BA63

BB63

BA61

AW61

BB59

AW59

BB61

AY61

BA59

AY59

AT66

AU66

AP65

AN65

AN66

AP66

AT65

AU65

AT61

AU61

AP60

AN60

AN61

AP61

AT60

AU60

DDR0_DQ[0]

DDR0_DQ[1]

DDR0_DQ[2]

DDR0_DQ[3]

DDR0_DQ[4]

DDR0_DQ[5]

DDR0_DQ[6]

DDR0_DQ[7]

DDR0_DQ[8]

DDR0_DQ[9]

DDR0_DQ[10]

DDR0_DQ[11]

DDR0_DQ[12]

DDR0_DQ[13]

DDR0_DQ[14]

DDR0_DQ[15]

DDR1_DQ[0]/DDR0_DQ[8]

DDR1_DQ[1]/DDR0_DQ[9]

DDR1_DQ[2]/DDR0_DQ[10]

DDR1_DQ[3]/DDR0_DQ[11]

DDR1_DQ[4]/DDR0_DQ[12]

DDR1_DQ[5]/DDR0_DQ[13]

DDR1_DQ[6]/DDR0_DQ[14]

DDR1_DQ[7]/DDR0_DQ[15]

DDR1_DQ[8]/DDR0_DQ[24]

DDR1_DQ[9]/DDR0_DQ[25]

DDR1_DQ[10]/DDR0_DQ[26]

DDR1_DQ[11]/DDR0_DQ[27]

DDR1_DQ[12]/DDR0_DQ[28]

DDR1_DQ[13]/DDR0_DQ[29]

DDR1_DQ[14]/DDR0_DQ[30]

DDR1_DQ[15]/DDR0_DQ[31]

DDR0_DQ[16]/DDR0_DQ[32]

DDR0_DQ[17]/DDR0_DQ[33]

DDR0_DQ[18]/DDR0_DQ[34]

DDR0_DQ[19]/DDR0_DQ[35]

DDR0_DQ[20]/DDR0_DQ[36]

DDR0_DQ[21]/DDR0_DQ[37]

DDR0_DQ[22]/DDR0_DQ[38]

DDR0_DQ[23]/DDR0_DQ[39]

DDR0_DQ[24]/DDR0_DQ[40]

DDR0_DQ[25]/DDR0_DQ[41]

DDR0_DQ[26]/DDR0_DQ[42]

DDR0_DQ[27]/DDR0_DQ[43]

DDR0_DQ[28]/DDR0_DQ[44]

DDR0_DQ[29]/DDR0_DQ[45]

DDR0_DQ[30]/DDR0_DQ[46]

DDR0_DQ[31]/DDR0_DQ[47]

DDR1_DQ[16]/DDR0_DQ[48]

DDR1_DQ[17]/DDR0_DQ[49]

DDR1_DQ[18]/DDR0_DQ[50]

DDR1_DQ[19]/DDR0_DQ[51]

DDR1_DQ[20]/DDR0_DQ[52]

DDR1_DQ[21]/DDR0_DQ[53]

DDR1_DQ[22]/DDR0_DQ[54]

DDR1_DQ[23]/DDR0_DQ[55]

DDR1_DQ[24]/DDR0_DQ[56]

DDR1_DQ[25]/DDR0_DQ[57]

DDR1_DQ[26]/DDR0_DQ[58]

DDR1_DQ[27]/DDR0_DQ[59]

DDR1_DQ[28]/DDR0_DQ[60]

DDR1_DQ[29]/DDR0_DQ[61]

DDR1_DQ[30]/DDR0_DQ[62]

DDR1_DQ[31]/DDR0_DQ[63]

SKYLAKE-GP-U1

DDR0_CKN[0]

DDR0_CKP[0]

DDR0_CKN[1]

DDR0_CKP[1]

DDR0_CKE[0]

DDR0_CKE[1]

DDR0_CKE[2]

DDR0_CKE[3]

DDR0_CS#[0]

DDR0_CS#[1]

DDR0_ODT[0]

DDR0_ODT[1]

DDR0_MA[5]/DDR0_CAA[0]/DDR0_MA[5]

DDR0_MA[9]/DDR0_CAA[1]/DDR0_MA[9]

DDR0_MA[6]/DDR0_CAA[2]/DDR0_MA[6]

DDR0_MA[8]/DDR0_CAA[3]/DDR0_MA[8]

DDR0_MA[7]/DDR0_CAA[4]/DDR0_MA[7]

DDR0_BA[2]/DDR0_CAA[5]/DDR0_BG[0]

DDR0_MA[12]/DDR0_CAA[6]/DDR0_MA[12]

DDR0_MA[11]/DDR0_CAA[7]/DDR0_MA[11]

DDR0_MA[15]/DDR0_CAA[8]/DDR0_ACT#

DDR0_MA[14]/DDR0_CAA[9]/DDR0_BG[1]

DDR0_MA[13]/DDR0_CAB[0]/DDR0_MA[13]

DDR0_CAS#/DDR0_CAB[1]/DDR0_MA[15]

DDR0_WE#/DDR0_CAB[2]/DDR0_MA[14]

DDR0_RAS#/DDR0_CAB[3]/DDR0_MA[16]

DDR0_BA[0]/DDR0_CAB[4]/DDR0_BA[0]

DDR0_MA[2]/DDR0_CAB[5]/DDR0_MA[2]

DDR0_BA[1]/DDR0_CAB[6]/DDR0_BA[1]

DDR0_MA[10]/DDR0_CAB[7]/DDR0_MA[10]

DDR0_MA[1]/DDR0_CAB[8]/DDR0_MA[1]

DDR0_MA[0]/DDR0_CAB[9]/DDR0_MA[0]

DDR0_MA[3]

DDR0_MA[4]

DDR0_DQSN[0]

DDR0_DQSP[0]

DDR0_DQSN[1]

DDR0_DQSP[1]

DDR1_DQSN[0]/DDR0_DQ[2]

DDR1_DQSP[0]/DDR0_DQ[2]

DDR1_DQSN[1]/DDR0_DQ[3]

DDR1_DQSP[1]/DDR0_DQ[3]

DDR0_DQSN[2]/DDR0_DQSN[4]

DDR0_DQSP[2]/DDR0_DQSP[4]

DDR0_DQSN[3]/DDR0_DQSN[5]

DDR0_DQSP[3]/DDR0_DQSP[5]

DDR1_DQSN[2]/DDR0_DQSN[6]

DDR1_DQSP[2]/DDR0_DQSP[6]

DDR1_DQSN[3]/DDR0_DQSN[7]

DDR1_DQSP[3]/DDR0_DQSP[7]

DDR0_ALERT#

DDR0_PAR

DDR_VREF_CA

DDR0_VREF_DQ

DDR1_VREF_DQ

DDR CH - A

DDR_VTT_CNTL

AU53

AT53

AU55

AT55

M_A_CLK#0 12

M_A_CLK0 12

M_A_CLK#1 12

M_A_CLK1 12

BA56

BB56

AW56

AY56

M_A_CKE0 12

M_A_CKE1 12

AU45

AU43

AT45

AT43

M_A_CS#0 12

M_A_CS#1 12

M_A_DIMA_ODT0 12

M_A_DIMA_ODT1 12

BA51

BB54

BA52

AY52

AW52

AY55

AW54

BA54

BA55

AY54

M_A_A5

M_A_A9

M_A_A6

M_A_A8

M_A_A7

AU46

AU48

AT46

AU50

AU52

AY51

AT48

AT50

BB50

AY50

BA50

BB52

M_A_A13

AM70

AM69

AT69

AT70

AH66

AH65

AG69

AG70

BA64

AY64

AY60

BA60

AR66

AR65

AR61

AR60

M_A_DQS_DN0

M_A_DQS_DP0

M_A_DQS_DN1

M_A_DQS_DP1

M_B_DQS_DN0

M_B_DQS_DP0

M_B_DQS_DN1

M_B_DQS_DP1

M_A_DQS_DN2

M_A_DQS_DP2

M_A_DQS_DN3

M_A_DQS_DP3

M_B_DQS_DN2

M_B_DQS_DP2

M_B_DQS_DN3

M_B_DQS_DP3

M_A_A5 12

M_A_A9 12

M_A_A6 12

M_A_A8 12

M_A_A7 12

M_A_BS2 12

M_A_A12 12

M_A_A11 12

M_A_A15 12

M_A_A14 12

M_A_A12

M_A_A11

M_A_A15

M_A_A14

M_A_A13 12

M_A_CAS# 12

M_A_W E# 12

M_A_RAS# 12

M_A_BS0 12

M_A_A2 12

M_A_BS1 12

M_A_A10 12

M_A_A1 12

M_A_A0 12

M_A_A3 12

M_A_A4 12

M_A_A2

M_A_A10

M_A_A1

M_A_A0

M_A_A3

M_A_A4

M_A_DQS_DN0

M_A_DQS_DP0

M_A_DQS_DN1

M_A_DQS_DP1

M_B_DQS_DN0

M_B_DQS_DP0

M_B_DQS_DN1

M_B_DQS_DP1

M_A_DQS_DN2

M_A_DQS_DP2

M_A_DQS_DN3

M_A_DQS_DP3

M_B_DQS_DN2

M_B_DQS_DP2

M_B_DQS_DN3

M_B_DQS_DP3

12

12

12

12

13

13

13

13

12

12

12

12

13

13

13

13

AW50

AT52

AY67

AY68

BA67

AW67

V_SM_VREF_CNT 12

M_VREF_DQ_DIM0 12

M_VREF_DQ_DIM1 13

SM_PGCNTL

071.SKYLA.000U

3D3V_S0

1D35V_S3

R401

220KR2F-GP

<Core Design>

SM_PGCNTL

Wistron Corporation

DDR_PG_OUT 51

Q401

DMN5L06K-7-GP

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

84.05067.031

20141023 Jack

Size

A3

2nd = 084.00138.0A31

Date:

5

CPU_(DDR)

Document Number

Rev

Brook_SLU

Monday, July 06, 2015

Sheet

1

1M

4

of

105

Main Func = CPU

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AY39

AW39

AY37

AW37

BB39

BA39

BA37

BB37

AY35

AW35

AY33

AW33

BB35

BA35

BA33

BB33

AU40

AT40

AT37

AU37

AR40

AP40

AP37

AR37

AT33

AU33

AU30

AT30

AR33

AP33

AR30

AP30

AY31

AW31

AY29

AW29

BB31

BA31

BA29

BB29

AY27

AW27

AY25

AW25

BB27

BA27

BA25

BB25

AU27

AT27

AT25

AU25

AP27

AN27

AN25

AP25

AT22

AU22

AU21

AT21

AN22

AP22

AP21

AN21

DDR0_DQ[32]/DDR1_DQ[0]

DDR0_DQ[33]/DDR1_DQ[1]

DDR0_DQ[34]/DDR1_DQ[2]

DDR0_DQ[35]/DDR1_DQ[3]

DDR0_DQ[36]/DDR1_DQ[4]

DDR0_DQ[37]/DDR1_DQ[5]

DDR0_DQ[38]/DDR1_DQ[6]

DDR0_DQ[39]/DDR1_DQ[7]

DDR0_DQ[40]/DDR1_DQ[8]

DDR0_DQ[41]/DDR1_DQ[9]

DDR0_DQ[42]/DDR1_DQ[10]

DDR0_DQ[43]/DDR1_DQ[11]

DDR0_DQ[44]/DDR1_DQ[12]

DDR0_DQ[45]/DDR1_DQ[13]

DDR0_DQ[46]/DDR1_DQ[14]

DDR0_DQ[47]/DDR1_DQ[15]

DDR1_DQ[32]/DDR1_DQ[16]

DDR1_DQ[33]/DDR1_DQ[17]

DDR1_DQ[34]/DDR1_DQ[18]

DDR1_DQ[35]/DDR1_DQ[19]

DDR1_DQ[36]/DDR1_DQ[20]

DDR1_DQ[37]/DDR1_DQ[21]

DDR1_DQ[38]/DDR1_DQ[22]

DDR1_DQ[39]/DDR1_DQ[23]

DDR1_DQ[40]/DDR1_DQ[24]

DDR1_DQ[41]/DDR1_DQ[25]

DDR1_DQ[42]/DDR1_DQ[26]

DDR1_DQ[43]/DDR1_DQ[27]

DDR1_DQ[44]/DDR1_DQ[28]

DDR1_DQ[45]/DDR1_DQ[29]

DDR1_DQ[46]/DDR1_DQ[30]

DDR1_DQ[47]/DDR1_DQ[31]

DDR0_DQ[48]/DDR1_DQ[32]

DDR0_DQ[49]/DDR1_DQ[33]

DDR0_DQ[50]/DDR1_DQ[34]

DDR0_DQ[51]/DDR1_DQ[35]

DDR0_DQ[52]/DDR1_DQ[36]

DDR0_DQ[53]/DDR1_DQ[37]

DDR0_DQ[54]/DDR1_DQ[38]

DDR0_DQ[55]/DDR1_DQ[39]

DDR0_DQ[56]/DDR1_DQ[40]

DDR0_DQ[57]/DDR1_DQ[41]

DDR0_DQ[58]/DDR1_DQ[42]

DDR0_DQ[59]/DDR1_DQ[43]

DDR0_DQ[60]/DDR1_DQ[44]

DDR0_DQ[61]/DDR1_DQ[45]

DDR0_DQ[62]/DDR1_DQ[46]

DDR0_DQ[63]/DDR1_DQ[47]

DDR1_DQ[48]

DDR1_DQ[49]

DDR1_DQ[50]

DDR1_DQ[51]

DDR1_DQ[52]

DDR1_DQ[53]

DDR1_DQ[54]

DDR1_DQ[55]

DDR1_DQ[56]

DDR1_DQ[57]

DDR1_DQ[58]

DDR1_DQ[59]

DDR1_DQ[60]

DDR1_DQ[61]

DDR1_DQ[62]

DDR1_DQ[63]

DDR1_CKN[0]

DDR1_CKN[1]

DDR1_CKP[0]

DDR1_CKP[1]

DDR1_CKE[0]

DDR1_CKE[1]

DDR1_CKE[2]

DDR1_CKE[3]

DDR1_CS#[0]

DDR1_CS#[1]

DDR1_ODT[0]

DDR1_ODT[1]

DDR1_MA[5]/DDR1_CAA[0]/DDR1_MA[5]

DDR1_MA[9]/DDR1_CAA[1]/DDR1_MA[9]

DDR1_MA[6]/DDR1_CAA[2]/DDR1_MA[6]

DDR1_MA[8]/DDR1_CAA[3]/DDR1_MA[8]

DDR1_MA[7]/DDR1_CAA[4]/DDR1_MA[7]

DDR1_BA[2]/DDR1_CAA[5]/DDR1_BG[0]

DDR1_MA[12]/DDR1_CAA[6]/DDR1_MA[12]

DDR1_MA[11]/DDR1_CAA[7]/DDR1_MA[11]

DDR1_MA[15]/DDR1_CAA[8]/DDR1_ACT#

DDR1_MA[14]/DDR1_CAA[9]/DDR1_BG[1]

DDR1_MA[13]/DDR1_CAB[0]/DDR1_MA[13]

DDR1_CAS#/DDR1_CAB[1]/DDR1_MA[15]

DDR1_WE#/DDR1_CAB[2]/DDR1_MA[14]

DDR1_RAS#/DDR1_CAB[3]/DDR1_MA[16]

DDR1_BA[0]/DDR1_CAB[4]/DDR1_BA[0]

DDR1_MA[2]/DDR1_CAB[5]/DDR1_MA[2]

DDR1_BA[1]/DDR1_CAB[6]/DDR1_BA[1]

DDR1_MA[10]/DDR1_CAB[7]/DDR1_MA[10]

DDR1_MA[1]/DDR1_CAB[8]/DDR1_MA[1]

DDR1_MA[0]/DDR1_CAB[9]/DDR1_MA[0]

DDR1_MA[3]

DDR1_MA[4]

DDR0_DQSN[4]/DDR1_DQSN[0]

DDR0_DQSP[4]/DDR1_DQSP[0]

DDR0_DQSN[5]/DDR1_DQSN[1]

DDR0_DQSP[5]/DDR1_DQSP[1]

DDR1_DQSN[4]/DDR1_DQSN[2]

DDR1_DQSP[4]/DDR1_DQSP[2]

DDR1_DQSN[5]/DDR1_DQSN[3]

DDR1_DQSP[5]/DDR1_DQSP[3]

DDR0_DQSN[6]/DDR1_DQSN[4]

DDR0_DQSP[6]/DDR1_DQSP[4]

DDR0_DQSN[7]/DDR1_DQSN[5]

DDR0_DQSP[7]/DDR1_DQSP[5]

DDR1_DQSN[6]

DDR1_DQSP[6]

DDR1_DQSN[7]

DDR1_DQSP[7]

DDR1_ALERT#

DDR1_PAR

DRAM_RESET#

DDR_RCOMP[0]

DDR_RCOMP[1]

DDR_RCOMP[2]

AN45

AN46

AP45

AP46

M_B_CLK#0 13

M_B_CLK#1 13

M_B_CLK0 13

M_B_CLK1 13

AN56

AP55

AN55

AP53

M_B_CKE0 13

M_B_CKE1 13

BB42

AY42

BA42

AW42

M_B_CS#0 13

M_B_CS#1 13

M_B_DIMB_ODT0 13

M_B_DIMB_ODT1 13

AY48

AP50

BA48

BB48

AP48

AP52

AN50

AN48

AN53

AN52

M_B_A5

M_B_A9

M_B_A6

M_B_A8

M_B_A7

BA43

AY43

AY44

AW44

BB44

AY47

BA44

AW46

AY46

BA46

BB46

BA47

M_B_A13

BA38

AY38

AY34

BA34

AT38

AR38

AT32

AR32

BA30

AY30

AY26

BA26

AR25

AR27

AR22

AR21

AN43

AP43

AT13

AR18

AT18

AU18

M_B_A12

M_B_A11

M_B_A15

M_B_A14

M_B_A2

M_B_A10

M_B_A1

M_B_A0

M_B_A3

M_B_A4

M_B_A5 13

M_B_A9 13

M_B_A6 13

M_B_A8 13

M_B_A7 13

M_B_BS2 13

M_B_A12 13

M_B_A11 13

M_B_A15 13

M_B_A14 13

M_B_A13 13

M_B_CAS# 13

M_B_W E# 13

M_B_RAS# 13

M_B_BS0 13

M_B_A2 13

M_B_BS1 13

M_B_A10 13

M_B_A1 13

M_B_A0 13

M_B_A3 13

M_B_A4 13

M_A_DQS_DN4

M_A_DQS_DP4

M_A_DQS_DN5

M_A_DQS_DP5

M_B_DQS_DN4

M_B_DQS_DP4

M_B_DQS_DN5

M_B_DQS_DP5

M_A_DQS_DN6

M_A_DQS_DP6

M_A_DQS_DN7

M_A_DQS_DP7

M_B_DQS_DN6

M_B_DQS_DP6

M_B_DQS_DN7

M_B_DQS_DP7

M_A_DQS_DN4

M_A_DQS_DP4

M_A_DQS_DN5

M_A_DQS_DP5

M_B_DQS_DN4

M_B_DQS_DP4

M_B_DQS_DN5

M_B_DQS_DP5

M_A_DQS_DN6

M_A_DQS_DP6

M_A_DQS_DN7

M_A_DQS_DP7

M_B_DQS_DN6

M_B_DQS_DP6

M_B_DQS_DN7

M_B_DQS_DP7

12

12

12

12

13

13

13

13

12

12

12

12

13

13

13

13

DDR3 COMPENSATION AND RESET SIGNALS

1D35V_S3

R506

470R2F-GP

20140922

B

SM_DRAMRST#

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

1 R501

1 R502

1 R503

2 121R2F-GP

2 80D6R2F-L-GP

2 100R2F-L3-GP

1 R504

2

0R0402-PAD-1-GP

DDR3_DRAMRST#

12,13

SM_DRAMRST#

DDR CH - B

#543016

071.SKYLA.000U

DY

SC10P50V2JN-L1-GP

EC501

SKYLAKE-GP-U1

SKYLAKE_ULT

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

13

3 OF 20

CPU1C

Layout Note:

Design Guideline:

SM_RCOMP keep routing length less than 500 mils.

20141126 Jack

Brook_SLU

A

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A3

Date:

5

CPU_(DDR)

Document Number

Rev

Brook_SLU

Monday, July 06, 2015

Sheet

1

of

105

1M

Main Func = PCH

3D3V_S0

RN602

1

2

3

4

DDPC_CDA

EC_SCI#

TOUCH_DET#

PSW _CLR#

8

7

6

5

SRN2K2J-4-GP

PSW _CLR#

20150302 SC Jack

Pass Word Clear

R604

10KR2F-L1-GP

2

1

TOUCH_S_RST#

G601

GAP-OPEN

DY

20150302 SC Jack

22,76,79 DGPU_HOLD_RST#

6 OF 20

CPU1F

LPSS

3D3V_S5

EC_SCI# 3,24

ISH

DDPC_CDA

SKYLAKE_ULT

1

2

RN601

4

3

55 TOUCH_DET#

38 CCD_PW R_EN#

RTC_DET#

GPU_EVENT#

14 GPP_B18/GSPI0_MOSI

SRN10KJ-L-GP

2 R603

1

CCD_PW R_ENR

0R0402-PAD-1-GP

GPP_B18/GSPI0_MOSI

AN8

AP7

AP8

AR7

RTC_DET#

PSW _CLR#

DGPU_PW R_EN#

GPP_B22/GSPI1_MOSI

AM5

AN7

AP5

AN5

R602

1 ODD_PW R_EN_N

0R2J-L-GP

AB1

AB2

W4

AB3

25 RTC_DET#

86 DGPU_PW R_EN#

14 GPP_B22/GSPI1_MOSI

1

2

C

RN603

4

3

DGPU_PW R_EN#

DGPU_HOLD_RST#

24,60 ODD_PW R_EN

DY

SRN10KJ-L-GP

20150302 SC Jack

20150302 SC Jack

LPSS_UART2_RXD

LPSS_UART2_TXD

LPSS_UART2_RTS#

LPSS_UART2_CTS#

20141119 Jack

Touch Panel

55 I2C0_DATA_CPU

55 I2C0_CLK_CPU

AH9

AH10

3D3V_S0

1

2

3

4

RN609

U7

U6

U8

U9

65 I2C1_DATA_CPU

65 I2C1_CLK_CPU

Touch Pad

AD1

AD2

AD3

AD4

AH11

AH12

8

7

6

5

I2C0_DATA_CPU

I2C0_CLK_CPU

I2C1_DATA_CPU

I2C1_CLK_CPU

AF11

AF12

GPP_B15/GSPI0_CS#

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_D9/ISH_SPI_CS#

GPP_D10/ISH_SPI_CLK

GPP_D11/ISH_SPI_MISO

GPP_D12/ISH_SPI_MOSI

Strap

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

Strap

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_C8/UART0_RXD

GPP_C9/UART0_TXD

GPP_C10/UART0_RTS#

GPP_C11/UART0_CTS#

GPP_F10/I2C5_SDA/ISH_I2C2_SDA

GPP_F11/I2C5_SCL/ISH_I2C2_SCL

GPP_C20/UART2_RXD

GPP_C21/UART2_TXD

GPP_C22/UART2_RTS#

GPP_C23/UART2_CTS#

GPP_D13/ISH_UART0_RXD/SML0BDATA

GPP_D14/ISH_UART0_TXD/SML0BCLK

GPP_D15/ISH_UART0_RTS#

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

TOUCH_S_RST# 55

M4

N3

N1

N2

AD11

AD12

C

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

GPP_C16/I2C0_SDA

GPP_C17/I2C0_SCL

GPP_C18/I2C1_SDA

GPP_C19/I2C1_SCL

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

GPP_A12/BM_BUSY#/ISH_GP6

GPP_F4/I2C2_SDA

GPP_F5/I2C2_SCL

GPP_F6/I2C3_SDA

GPP_F7/I2C3_SCL

U1

U2

U3

U4

AC1

AC2

AC3

AB4

AY8

BA8

BB7

BA7

AY7

AW7

AP13

20141027 Jack

DGPU_DUAL2

DGPU_PRESENT

MIC_DET

GPU_EVENT#

GC6_FB_EN_MCP

R605 1

GSENSOR_INT# 69

20150225 SC Jack

GPU_EVENT# 79

GC6_FB_EN 79,86

0R0402-PAD-1-GP

GPP_F8/I2C4_SDA

GPP_F9/I2C4_SCL

SKYLAKE-GP-U1

SRN2K2J-4-GP

P2

P3

P4

P1

20141021 Jack

071.SKYLA.000U

3D3V_S0

B

SINGLE

R606

10KR2F-L1-GP

UMA

DY

2

3

4

R608

10KR2F-L1-GP

940_DAUL RANK

DGPU_PRESENT

DGPU_DUAL2

R615

10KR2F-L1-GP

R607

10KR2F-L1-GP

DUAL

PX

DGPU_PRESENT

H:UMA

L:DIS

MIC_DET

1

DB2

5V_S5

R609

10KR2F-L1-GP

940_SINGLE RANK

2

20.F1897.004

20150225 SC Jack

LPSS_UART2_TXD

LPSS_UART2_RXD

MIC_DET

H:SINGLE MIC

L:DUAL MIC

N16S-GT 940 VBIOS (DGPU_DUAL2)

H:DAUL RANK

L:SINGLE RANK

R614

10KR2F-L1-GP

DY

DY

3D3V_S0

3D3V_S0

3D3V_S0

LPSS_UART2_RXD

LPSS_UART2_TXD

LPSS_UART2_RTS#

LPSS_UART2_CTS#

1

2

149K9R2F-L-GP

2

149K9R2F-L-GP

2

DY

149K9R2F-L-GP

2

DY

49K9R2F-L-GP

R610

R611

R612

R613

20141022 Jack

20150202 SC Jack

ACES-CON4-37-GP

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

20141121 Jack

Title

Size

A3

Date:

5

CPU_(LPSS/ISH)

Brook_SLU

Document Number

Monday, July 06, 2015

Sheet

1

Rev

1M

of

105

Main Func = CPU

1V_CPU_CORE

CPU POWER 1 OF 4

AK32

AB62

P62

V62

H63

G61

AC63

AE63

AE62

AG62

AL63

AJ62

VCC_G32

VCC_G33

VCC_G35

VCC_G37

VCC_G38

VCC_G40

VCC_G42

VCC_J30

VCC_J33

VCC_J37

VCC_J40

VCC_K33

VCC_K35

VCC_K37

VCC_K38

VCC_K40

VCC_K42

VCC_K43

SKYLAKE_ULT

VCCG0

VCC_SENSE

VSS_SENSE

VCCG1

VIDALERT#

VIDSCK

VIDSOUT

VCCOPC_AB62

VCCOPC_P62

VCCOPC_V62

VCCSTG_G20

VCC_OPC_1P8_H63

G32

G33

G35

G37

G38

G40

G42

J30

J33

J37

J40

K33

K35

K37

K38

K40

K42

K43

1V_CPU_CORE

RN703

E32

E33

VCC_SENSE

VSS_SENSE

VCC_SENSE 46

VSS_SENSE 46

B63 VIDALERT#_CPU

A63 VIDSCK_CPU

D64 VIDSOUT_CPU

2

1

3

4

R1

K32

VCC_A30

VCC_A34

VCC_A39

VCC_A44

VCC_AK33

VCC_AK35

VCC_AK37

VCC_AK38

VCC_AK40

VCC_AL33

VCC_AL37

VCC_AL40

VCC_AM32

VCC_AM33

VCC_AM35

VCC_AM37

VCC_AM38

VCC_G30

R2

A30

A34

A39

A44

AK33

AK35

AK37

AK38

AK40

AL33

AL37

AL40

AM32

AM33

AM35

AM37

AM38

G30

12 OF 20

CPU1L

1V_CPU_CORE

SRN100F-1-GP

20150302 SC Jack

1V_VCCSTG

G20

Layout Note:

1. Place close to CPU

2. VCC_SENSE/ VSS_SENSE

impedance=50 ohm

3. Length match<25mil

VCCSTG(ICCMAX.=0.04A)

VCC_OPC_1P8_G61

VCCOPC_SENSE

VSSOPC_SENSE

VCCEOPIO

VCCEOPIO

VCCEOPIO_SENSE

VSSEOPIO_SENSE

SKYLAKE-GP-U1

1V_VCCIO

1V_VCCSTG

1 R709

2

0R0402-PAD-1-GP

071.SKYLA.000U

1V_VCCST

1 R727

DY1

R732

2 R726

256R2J-L1-GP

254D9R2F-L1-GP

1100R2F-L3-GP

VIDALERT#_CPU_R

VIDSCK_CPU_R

VIDSOUT_CPU_R

VIDALERT#_CPU

1 R728

2 220R2J-L2-GP

VIDSCK_CPU

1 R729

2 0R0402-PAD-1-GP

VIDSCK_CPU_R

VIDSOUT_CPU

1 R730

2 0R0402-PAD-1-GP

VIDSOUT_CPU_R

VIDALERT#_CPU_R

46

46

46

CLOSE CPU

SVID_543016:

Brook_SLU

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A2

Date:

5

CPU_POWER1

Document Number

Rev

Brook_SLU

Monday, July 06, 2015

Sheet

1

1M

7

of

105

Main Func = CPU

13 OF 20

CPU1M

1V_VCCGT

A48

A53

A58

A62

A66

AA63

AA64

AA66

AA67

AA69

AA70

AA71

AC64

AC65

AC66

AC67

AC68

AC69

AC70

AC71

J43

J45

J46

J48

J50

J52

J53

J55

J56

J58

J60

K48

K50

K52

K53

K55

K56

K58

K60

L62

L63

L64

L65

L66

L67

L68

L69

L70

L71

M62

N63

N64

N66

N67

N69

J70

J69

46 VCCGT_SENSE

46 VSSGT_SENSE

1V_VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

1V_VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

VCCGT

SKYLAKE_ULT

VCCGTX_AK42

VCCGTX_AK43

VCCGTX_AK45

VCCGTX_AK46

VCCGTX_AK48

VCCGTX_AK50

VCCGTX_AK52

VCCGTX_AK53

VCCGTX_AK55

VCCGTX_AK56

VCCGTX_AK58

VCCGTX_AK60

VCCGTX_AK70

VCCGTX_AL43

VCCGTX_AL46

VCCGTX_AL50

VCCGTX_AL53

VCCGTX_AL56

VCCGTX_AL60

VCCGTX_AM48

VCCGTX_AM50

VCCGTX_AM52

VCCGTX_AM53

VCCGTX_AM56

VCCGTX_AM58

VCCGTX_AU58

VCCGTX_AU63

VCCGTX_BB57

VCCGTX_BB66

VCCGT_SENSE

VSSGT_SENSE

SKYLAKE-GP-U1

1V_VCCIO

CPU POWER 2 OF 4

VCCGTX_SENSE

VSSGTX_SENSE

1D35V_S3

N70

N71

R63

R64

R65

R66

R67

R68

R69

R70

R71

T62

U65

U68

U71

W63

W64

W65

W66

W67

W68

W69

W70

W71

Y62

14 OF 20

CPU1N

CPU POWER 3 OF 4

AU23

AU28

AU35

AU42

BB23

BB32

BB41

BB47

BB51

1D35V_S3

20150306 SC Jack

SKYLAKE_ULT

1V_VCCSTG

A18

1D35V_S3

A22

1V_VCCSFR

AL23

K20

K21

1 R808

2

0R0402-PAD-1-GP

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

VCCSA

1V_VCCST

AM40

1V_VCCST

VDDQ_AU23

VDDQ_AU28

VDDQ_AU35

VDDQ_AU42

VDDQ_BB23

VDDQ_BB32

VDDQ_BB41

VDDQ_BB47

VDDQ_BB51

VDDQC

VCCST

VCCSTG_A22

VCCPLL_OC

VCCPLL_K20

VCCPLL_K21

VCCIO_SENSE

VSSIO_SENSE

AK42

AK43

AK45

AK46

AK48

AK50

AK52

AK53

AK55

AK56

AK58

AK60

AK70

AL43

AL46

AL50

AL53

AL56

AL60

AM48

AM50

AM52

AM53

AM56

AM58

AU58

AU63

BB57

BB66

VSSSA_SENSE

VCCSA_SENSE

SKYLAKE-GP-U1

AK28

AK30

AL30

AL42

AM28

AM30

AM42

1V_VCCSA

AK23

AK25

G23

G25

G27

G28

J22

J23

J27

K23

K25

K27

K28

K30

AM23

AM22

20141118 Jack

H21

H20

VSSSA_SENSE 46

VCCSA_SENSE 46

C

071.SKYLA.000U

1V_VCCSA

RN805

4

3

1

2

R1

R2

VCCSA_SENSE

VSSSA_SENSE

SRN100F-1-GP

20150325 SC

AK62

AL61

071.SKYLA.000U

RN804

4

3

R1

R2

1

2

VCCGT_SENSE

VSSGT_SENSE

SRN100F-1-GP

Brook_SLU

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A3

Date:

5

CPU_POWER1

Document Number

Rev

Brook_SLU

Monday, July 06, 2015

Sheet

1

1M

8

of

105

Main Func = PCH

3D3V_1D8V_VCCPGPPA

Imax 8.28A

1D0V_S5

15 OF 20

CPU1O

CPU POWER 4 OF 4

AB19

AB20

P18

2.57A

1V_DCPDSW

1D0V_S5

AF18

AF19

V20

V21

AL1

3.6A

K17

L1

N15

N16

N17

P15

P16

K15

L15

V15

AB17

Y18

3D3V_S5

0.09A

C

0.2A

3D3V_S5

3D3V_S5

1D0V_S5

AJ19

0.1A

AJ16

3.5A

AF20

AF21

T19

T20

1D0V_S5

20141201 SB Jack

AD17

AD18

AJ17

AJ21

AK20

N18

VCCPRIM_1P0

VCCPRIM_1P0

VCCPRIM_1P0

VCCPRIM_CORE

VCCPRIM_CORE

VCCPRIM_CORE

VCCPRIM_CORE

1.8V Only

DCPDSW_1P0

VCCPGPPA

VCCPGPPB

VCCPGPPC

VCCPGPPD

VCCPGPPE

VCCPGPPF

VCCPGPPG

VCCPRIM_3P3_V19

VCCMPHYAON_1P0

VCCMPHYAON_1P0

VCCPRIM_1P0_T1

VCCATS_1P8

VCCMPHYGT_1P0_N15

VCCMPHYGT_1P0_N16

VCCMPHYGT_1P0_N17

VCCMPHYGT_1P0_P15

VCCMPHYGT_1P0_P16

VCCRTCPRIM_3P3

VCCRTC_AK19

VCCRTC_BB14

VCCAMPHYPLL_1P0

VCCAMPHYPLL_1P0

DCPRTC

VCCCLK1

VCCAPLL_1P0

VCCCLK2

VCCPRIM_1P0_AB17

VCCPRIM_1P0_Y18

VCCCLK3

VCCDSW_3P3_AD17

VCCDSW_3P3_AD18

VCCDSW_3P3_AJ17

VCCCLK4

VCCHDA

VCCCLK6

VCCSPI

2

R901 1

0R0402-PAD-1-GP

ESPI

SKYLAKE_ULT

VCCCLK5

GPP_B0/CORE_VID0

GPP_B1/CORE_VID1

AK15

AG15

Y16

Y15

T16

AF16

AD15

3D3V_1D8V_VCCPGPPA

3D3V_S5

1D8V_S5

3D3V_S5

V19

AA1

1D0V_S5

0.27A

1D8V_S5

AK17

3D3V_S5

AK19

BB14

3D3V_RTC_AUX

BB10

DCPRTC

A14

K19

20150415 -1

eSPI_508740:

3D3V_S5

T1

3D3V_S5

1D0V_S5

0.1A

L21

N20

0.1A

L19

0.1A

A10

AN11

AN13

V0.85A_VID0

V0.85A_VID1

1

1

TP2101

TP2102

VCCSRAM_1P0

VCCSRAM_1P0

VCCSRAM_1P0

VCCSRAM_1P0

VCCPRIM_3P3_AJ21

VCCPRIM_1P0_AK20

VCCAPLLEBB

SKYLAKE-GP-U1

071.SKYLA.000U

Brook_SLU

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A3

Date:

5

CPU_(POWER1)

Brook_SLU

Document Number

Monday, July 06, 2015

Sheet

1

Rev

1M

of

105

Main Func = CPU

1V_CPU_CORE

2

1

2

1

2

1

C1010

2

1

2

1

2

C1013

SC22U6D3V5MX-L3-GP

C1012

SC22U6D3V5MX-L3-GP

C1011

SC22U6D3V5MX-L3-GP

SCD1U16V2KX-L-GP

SCD1U16V2KX-L-GP

EC1002

C1009

1V_CPU_CORE

C

EC1001

1

1

DY

C1008

2

2

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

DY

C1007

SC22U6D3V5MX-L3-GP

PC1024

SC22U6D3V5MX-L3-GP

1

SC22U6D3V5MX-L3-GP

PC1023

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

PC1022

PC1021

PC1020

PC1019

PC1018

SC22U6D3V5MX-L3-GP

PC1017

C1006

SC1U10V2KX-L1-GP

PC1016

C1005

SC1U10V2KX-L1-GP

PC1015

C1004

SC1U10V2KX-L1-GP

PC1014

SC1U10V2KX-L1-GP

PC1013

C1003

C1002

C1001

1

2

1

2

PC1012

SC22U6D3V5MX-L3-GP

1

2

PC1011

SC22U6D3V5MX-L3-GP

1

2

PC1010

SC22U6D3V5MX-L3-GP

1

2

SC22U6D3V5MX-L3-GP

1

2

SC22U6D3V5MX-L3-GP

1

2

SC22U6D3V5MX-L3-GP

1

2

SC22U6D3V5MX-L3-GP

1

2

SC22U6D3V5MX-L3-GP

PC1009

SC10U6D3V3MX-L-GP

PC1008

SC10U6D3V3MX-L-GP

SC22U6D3V5MX-L3-GP

PC1007

SC10U6D3V3MX-L-GP

PC1006

SC10U6D3V3MX-L-GP

PC1005

SC10U6D3V3MX-L-GP

PC1004

IccMax current = 3.5 A

SC10U6D3V3MX-L-GP

SC22U6D3V5MX-L3-GP

PC1003

SC22U6D3V5MX-L3-GP

PC1002

SC22U6D3V5MX-L3-GP

PC1001

1D35V_S3

22U 0805 x 22

IccMax current = 28 A

20150616 -1M

1

2

1

2

C1028

C1029

SC1U10V2KX-L1-GP

C1027

SC1U10V2KX-L1-GP

C1026

SC1U10V2KX-L1-GP

C1025

SC1U10V2KX-L1-GP

C1024

SC1U10V2KX-L1-GP

C1023

SC1U10V2KX-L1-GP

C1022

SC1U10V2KX-L1-GP

C1021

SC1U10V2KX-L1-GP

C1020

SC10U6D3V3MX-L-GP

CLOSE CPU AL23

C1019

IccMax = 2.73 A

1V_VCCIO

SC10U6D3V3MX-L-GP

CLOSE CPU A22

C1018

1V_VCCSFR

C1017

1V_VCCSTG

IccMax = 0.12 A

SC1U10V2KX-L1-GP

1D35V_S3

SC1U10V2KX-L1-GP

CLOSE CPU A18

IccMax = 0.26 A

SC1U10V2KX-L1-GP

CLOSE CPU AM40

C1016

SC1U10V2KX-L1-GP

C1015

SC1U10V2KX-L1-GP

SC10U6D3V3MX-L-GP

C1014

1V_VCCST

IccMax = 0.04 A

IccMax = 0.04 A

1D35V_S3

Brook_SLU

CLOSE CPU K20,K21

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A3

Date:

5

CPU_(Power CAP1)

Document Number

Rev

Brook_SLU

Monday, July 06, 2015

Sheet

1

1M

10

of

105

Main Func = CPU

VCCSA

1V_VCCSA

IccMax current = 31 A

20141203 SB Jack

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

PC1152

1

1

EC1101

EC1103

EC1104

DY

1

2

20141203 SB Jack

EC1102

PC1128

20141203 SB Jack

PC1151

PC1153

SC22U6D3V5MX-L3-GP

1

2

1

2

1V_VCCGT

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

PC1157

DY

SCD1U16V2KX-L-GP

DY

PC1150

20150616 -1M

SCD1U16V2KX-L-GP

1

2

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

PC1127

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

2

2

SC22U6D3V5MX-L3-GP

PC1126

PC1125

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

2

2

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

2

2

PC1124

2

1

2

1

2

1

PC1123

PC1120

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

PC1119

PC1118

SC22U6D3V5MX-L3-GP

PC1117

PC1116

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

SC10U6D3V3MX-L-GP

PC1115

PC1114

SC22U6D3V5MX-L3-GP

SC22U6D3V5MX-L3-GP

2

1

PC1113

SC22U6D3V5MX-L3-GP

2

1

PC1112

PC1122

PC1149

SCD1U16V2KX-L-GP

PC1111

PC1121

PC1148

SCD1U16V2KX-L-GP

1V_VCCSA

PC1110

SC22U6D3V3MX-1-GP

PC1109

SC22U6D3V5MX-L3-GP

PC1108

PC1107

PC1106

PC1105

ICCMAX.=5A

PC1104

PC1103

PC1102

PC1101

GT

1V_VCCGT

20150616 -1M

1D0V_S5

3D3V_S5

1

2

1

2

CLOSE CPU AL1

C1120

CLOSE CPU BB10

C1115

C1119

CLOSE CPU AK19

C1118

CLOSE CPU AK17

C1117

C1116

1

2

1

2

CLOSE CPU T16

CLOSE CPU A10

C1103

SC1U10V2KX-L1-GP

DY

SCD1U16V2KX-L-GP

CLOSE CPU Y16

C1114

SC1U10V2KX-L1-GP

DY

DY

1D8V_S5

SCD1U16V2KX-L-GP

CLOSE CPU AG15

C1113

C1121

3D3V_RTC_AUX

SC1U10V2KX-L1-GP

DY

CLOSE CPU N18

3D3V_S5

SC1U10V2KX-L1-GP

CLOSE CPU V19

C1112

SC1U10V2KX-L1-GP

DY

3D3V_S5

SC1U10V2KX-L1-GP

CLOSE CPU AJ19

C1110

SC1U10V2KX-L1-GP

C1108

3D3V_S5

3D3V_S5

SC1U10V2KX-L1-GP

3D3V_S5

CLOSE CPU AF20

C1111

1

1

2

1

2

1

2

1

2

CLOSE CPU K15

DY

SCD1U16V2KX-L-GP

DY

C1109

DCPRTC

SC1U10V2KX-L1-GP

DY

1V_DCPDSW

SC1U10V2KX-L1-GP

CLOSE CPU N15

C1107

C1106

1D0V_S5

SC1U10V2KX-L1-GP

CLOSE CPU K17

C1105

1D0V_S5

SC1U10V2KX-L1-GP

CLOSE CPU AF18

C1104

1D0V_S5

SC1U10V2KX-L1-GP

DY

SC22U6D3V5MX-L3-GP

CLOSE CPU AB19

C1102

SC1U10V2KX-L1-GP

DY

1D0V_S5

SC1U10V2KX-L1-GP

C1101

1D0V_S5

SC1U10V2KX-L1-GP

1D0V_S5

SC1U10V2KX-L1-GP

1D0V_S5

CLOSE CPU AA1

Brook_SLU

Wistron Corporation

21F, 88, Sec.1, Hsin Tai W u Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A3

Date:

5

CPU_(Power CAP2)

Document Number

Rev

Brook_SLU

Monday, July 06, 2015

Sheet

1

1M

11

of

105

Main Func = DDR SODIMM

DM1

DY

DY

DY

DY

C1230S

C1229S

C1228S

C1211S

C1210S

C1209S

C1208S

1

2

C1207S

DY

DY

DY

SA_DIMM_VREFDQ

Layout Note:

Place these Caps near DIMM1.

V_SM_VREF_CNT

1

1

R1221

24D9R2F-L-GP

C1247

SC22U6D3V5MX-L3-GP

2

DY

1D35V_S3

DY

C1221

SC1U10V2KX-L1-GP

1

2

C1220

SC1U10V2KX-L1-GP

2

1

1

2

1

2

C1216

SC1U10V2KX-L1-GP

DY

C1257

SCD022U16V2KX-3GP

R1219

1K8R2F-GP

0D675V_VREF_S0

DY

Layout Note:

R1212

1K8R2F-GP

2

Place these caps

close to VTT1 and

VTT2.

R1215

22R2F-GP 1

M_VREF_DQ_DIM0

R1213

1K8R2F-GP

M_VREF_DQ_DIMMA

C1256

SCD022U16V2KX-3GP

62.10024.S21

2nd = 62.10024.M31

4th = 62.10017.I31

R1214

24D9R2F-L-GP

2

R1220

1 2R2F-GP2

M_VREF_CA_DIMMA

3rd = 62.10024.Q61

C1204

SCD1U16V2KX-L-GP

R1218

1K8R2F-GP

DY

C1227

1

2

C1226

DY

C1223

C1224

C1225

C1219

C1213

1D35V_S3

C1212

+V_VREF_PATH1

close to dimm

VTT1

VTT2

SKT_DDR 204P SMD

DDR3-204P-262-GP-U

1D35V_S3

C1215

SC1U10V2KX-L1-GP

1

2

C1217

SCD1U16V2KX-L-GP

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

205

206

C1203

SCD1U16V2KX-L-GP

1D35V_S3

+V_VREF_PATH3

203

204

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

DY

C10U6D3V3MX-L-GP

RESET#

0D675V_VREF_S0

DY

77

122

125

SC1U10V2KX-L1-GP

M_VREF_DQ_DIMMA

VREF_CA

VREF_DQ

20140919

197

201

C10U6D3V3MX-L-GP

30

5,13 DDR3_DRAMRST#

ODT0

ODT1

TS#_DIMM0_1

199

SC1U10V2KX-L1-GP

126

1

198

3D3V_S0

DY

PCH_SMBDATA 13,18,69

PCH_SMBCLK 13,18,69

3D3V_S0

C10U6D3V3MX-L-GP

All VREF traces should

have width=20mil;

spacing=20 mil

116

120

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

R1211

10KR2F-L1-GP

1

2

TS#_DIMM0_1

200

202

SC1U10V2KX-L1-GP

Layout Note:

M_A_DIMA_ODT0

M_A_DIMA_ODT1

M_VREF_CA_DIMMA

M_VREF_DQ_DIMMA

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Thermal EVENT

C10U6D3V3MX-L-GP

4 M_A_DIMA_ODT0

4 M_A_DIMA_ODT1

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

20140919

SC1U10V2KX-L1-GP

20140926 JACK

12

29

47

64

137

154

171

188

NC#1

NC#2

NC#/TEST

M_A_CLK1 4

M_A_CLK#1 4

11

28

46

63

136

153

170

187

C10U6D3V3MX-L-GP

Place these caps

close to DM1 PIN126

M_A_DQS_DP0

M_A_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

SA0

SA1

102

104

SC1U10V2KX-L1-GP

M_A_DQS_DP0

M_A_DQS_DP1

M_A_DQS_DP2

M_A_DQS_DP3

M_A_DQS_DP4

M_A_DQS_DP5

M_A_DQS_DP6

M_A_DQS_DP7

10

27

45

62

135

152

169

186

EVENT#

VDDSPD

M_A_CLK0 4

M_A_CLK#0 4

C10U6D3V3MX-L-GP

4

4

4

4

5

5

5

5

M_A_DQS_DN0

M_A_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

SDA

SCL

M_A_CKE0 4

M_A_CKE1 4

101

103

SC1U10V2KX-L1-GP

C1201

SCD1U16V2KX-L-GP

M_A_DQS_DN0

M_A_DQS_DN1

M_A_DQS_DN2

M_A_DQS_DN3

M_A_DQS_DN4

M_A_DQS_DN5

M_A_DQS_DN6

M_A_DQS_DN7

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

M_A_CS#0 4

M_A_CS#1 4

73

74

C10U6D3V3MX-L-GP

4

4

4

4

5

5

5

5

CK1

CK1#

BA0

BA1

M_A_RAS# 4

M_A_WE# 4

M_A_CAS# 4

114

121

SC1U10V2KX-L1-GP

M_VREF_CA_DIMMA

CK0

CK0#

110

113

115

C10U6D3V3MX-L-GP

M_A_DQ5

M_A_DQ1

M_A_DQ7

M_A_DQ3

M_A_DQ0

M_A_DQ4

M_A_DQ2

M_A_DQ6

M_A_DQ13

M_A_DQ12

M_A_DQ14

M_A_DQ15

M_A_DQ8

M_A_DQ9

M_A_DQ11

M_A_DQ10

M_A_DQ16

M_A_DQ17

M_A_DQ19

M_A_DQ18

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ36

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ32

M_A_DQ37

M_A_DQ39

M_A_DQ38

M_A_DQ41

M_A_DQ40

M_A_DQ47

M_A_DQ46

M_A_DQ44

M_A_DQ45

M_A_DQ43

M_A_DQ42

M_A_DQ49

M_A_DQ53

M_A_DQ51

M_A_DQ55

M_A_DQ48

M_A_DQ52

M_A_DQ50

M_A_DQ54

M_A_DQ56

M_A_DQ57

M_A_DQ62

M_A_DQ63

M_A_DQ60

M_A_DQ61

M_A_DQ59

M_A_DQ58

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

CS0#

CS1#

CKE0

CKE1

NP1

NP2

SC1U10V2KX-L1-GP

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

M_A_DQ5

M_A_DQ1

M_A_DQ7

M_A_DQ3

M_A_DQ0

M_A_DQ4

M_A_DQ2

M_A_DQ6

M_A_DQ13

M_A_DQ12

M_A_DQ14

M_A_DQ15

M_A_DQ8

M_A_DQ9

M_A_DQ11

M_A_DQ10

M_A_DQ16

M_A_DQ17

M_A_DQ19

M_A_DQ18

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ36

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ32

M_A_DQ37

M_A_DQ39

M_A_DQ38

M_A_DQ41

M_A_DQ40

M_A_DQ47

M_A_DQ46

M_A_DQ44

M_A_DQ45

M_A_DQ43

M_A_DQ42

M_A_DQ49

M_A_DQ53

M_A_DQ51

M_A_DQ55

M_A_DQ48

M_A_DQ52

M_A_DQ50

M_A_DQ54

M_A_DQ56

M_A_DQ57

M_A_DQ62

M_A_DQ63

M_A_DQ60

M_A_DQ61

M_A_DQ59

M_A_DQ58

NP1

NP2

RAS#

WE#

CAS#

109

108

4 M_A_BS0

4 M_A_BS1

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15

A16/BA2

98

97

96

95

92

91

90

86

89

85

107

84

83

119

80

78

79

C1214

SC1U10V2KX-L1-GP

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

4 M_A_A0

4 M_A_A1

4 M_A_A2

4 M_A_A3

4 M_A_A4

4 M_A_A5

4 M_A_A6

4 M_A_A7

4 M_A_A8

4 M_A_A9

4 M_A_A10

4 M_A_A11

4 M_A_A12

4 M_A_A13

4 M_A_A14

4 M_A_A15

4 M_A_BS2

Note:

SA0 DIM0 = 0, SA1_DIM0 = 0

SO-DIMMA SPD Address is 0xA0

SO-DIMMA TS Address is 0x30

Place these caps

close to DM1 PIN1

A

20140926 JACK

Brook_SLU

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A2

Date:

5

DDR3-SODIMM1

Document Number

Rev

Brook_SLU

Monday, July 06, 2015

Sheet

1

1M

12

of

105

Main Func = DDR SODIMM

Note:

SO-DIMMB SPD Address is 0xA4

SO-DIMMB TS Address is 0x34

DM2

DY

DY

C1312

DY

C1335

C1330

DY

DY

C1336

1

2

C1334

C1333

C1318

1

2

DY

C1316

C1332

DY

C1329

C1331

C1317

C1314

C1315

DY

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

205

206

C1327

C1313

DY

Layout Note:

Place these Caps near DIMM2.

1

2

C1323

SC1U10V2KX-L1-GP

DY

DY

C1321

SC1U10V2KX-L1-GP

2

1

C1319

SC1U10V2KX-L1-GP

1

2

1

2

C1320

SC1U10V2KX-L1-GP

0D675V_VREF_S0

DY

C1303

SC22U6D3V5MX-L3-GP

DY

1D35V_S3

R1304

1K8R2F-GP

M_VREF_DQ_DIMMB

3rd = 62.10024.Q71

R1305

1

2R2F-GP

4th = 62.10017.I21

R1307

1K8R2F-GP

C1302

SCD1U16V2KX-L-GP

M_VREF_DQ_DIM1

2nd = 62.10024.M51

Place Close DIMM2

Layout Note:

close to dimm

62.10024.S61

C1328

SCD022U16V2KX-3GP

+V_VREF_PATH2

R1306

24D9R2F-L-GP

2

2

1

2

1D35V_S3

DY

C1322

SC1U10V2KX-L1-GP

1

2

DY

TS#_DIMM1_1

1D35V_S3

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

SC10U6D3V3MX-L-GP

C1301

SCD1U16V2KX-L-GP

VTT1

VTT2

SKT_DDR 204P SMD

DDR3-204P-263-GP-U

3D3V_S0

R1303

10KR2F-L1-GP

1

2

SC1U10V2KX-L1-GP

203

204

Layout Note:

Place these caps

close to DM2 PIN1

RESET#

0D675V_VREF_S0

20140919

Thermal EVENT

C1311

SCD1U16V2KX-L-GP

SC10U6D3V3MX-L-GP

M_VREF_DQ_DIMMB

VREF_CA

VREF_DQ

DY

SC1U10V2KX-L1-GP

30

5,12 DDR3_DRAMRST#

ODT0

ODT1

77

122

125

SA1_DIMB

SC10U6D3V3MX-L-GP

All VREF traces should

have width=20mil;

spacing=20 mil

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

20140919

199

197

201

PCH_SMBDATA 12,18,69

PCH_SMBCLK 12,18,69

3D3V_S0

TS#_DIMM1_1

SC1U10V2KX-L1-GP

Layout Note:

126

1

M_VREF_CA_DIMMA

M_VREF_DQ_DIMMB

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

198

SC10U6D3V3MX-L-GP

116

120

5 M_B_DIMB_ODT0

5 M_B_DIMB_ODT1

20140926 JACK

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

200

202

SC1U10V2KX-L1-GP

12

29

47

64

137

154

171

188

NC#1

NC#2

NC#/TEST

M_B_CLK1 5

M_B_CLK#1 5

11

28

46

63

136

153

170

187

SC10U6D3V3MX-L-GP

M_B_DQS_DP1

M_B_DQS_DP0

M_B_DQS_DP2

M_B_DQS_DP3

M_B_DQS_DP4

M_B_DQS_DP5

M_B_DQS_DP6

M_B_DQS_DP7

SA0

SA1

102

104

SA1_DIMB

SC1U10V2KX-L1-GP

M_B_DQS_DP1

M_B_DQS_DP0

M_B_DQS_DP2

M_B_DQS_DP3

M_B_DQS_DP4

M_B_DQS_DP5

M_B_DQS_DP6

M_B_DQS_DP7

10

27

45

62

135

152

169

186

VDDSPD

M_B_CLK0 5

M_B_CLK#0 5

SC10U6D3V3MX-L-GP

4

4

4

4

5

5

5

5

M_B_DQS_DN1

M_B_DQS_DN0

M_B_DQS_DN2

M_B_DQS_DN3

M_B_DQS_DN4

M_B_DQS_DN5

M_B_DQS_DN6

M_B_DQS_DN7

SDA

SCL

EVENT#

101

103

SC1U10V2KX-L1-GP

C1308

SCD1U16V2KX-L-GP

M_B_DQS_DN1

M_B_DQS_DN0

M_B_DQS_DN2

M_B_DQS_DN3

M_B_DQS_DN4

M_B_DQS_DN5

M_B_DQS_DN6

M_B_DQS_DN7

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

R1302

10KR2F-L1-GP

M_B_CKE0 5

M_B_CKE1 5

SC10U6D3V3MX-L-GP

Place these caps

close to DM2 PIN126

B

4

4

4

4

5

5

5

5

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

M_B_CS#0 5

M_B_CS#1 5

73

74

SC1U10V2KX-L1-GP

Layout Note:

CK1

CK1#

BA0

BA1

3D3V_S0

M_B_RAS# 5

M_B_WE# 5

M_B_CAS# 5

114

121

SC10U6D3V3MX-L-GP

M_VREF_CA_DIMMA

M_B_DQ8

M_B_DQ12

M_B_DQ10

M_B_DQ11

M_B_DQ9

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ4

M_B_DQ0

M_B_DQ6

M_B_DQ3

M_B_DQ5

M_B_DQ1

M_B_DQ7

M_B_DQ2

M_B_DQ20

M_B_DQ19

M_B_DQ17

M_B_DQ22

M_B_DQ18

M_B_DQ21

M_B_DQ23

M_B_DQ16

M_B_DQ29

M_B_DQ28

M_B_DQ30

M_B_DQ31

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ39

M_B_DQ33

M_B_DQ32

M_B_DQ34

M_B_DQ38

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ45

M_B_DQ44

M_B_DQ47

M_B_DQ46

M_B_DQ49

M_B_DQ51

M_B_DQ50

M_B_DQ55

M_B_DQ52

M_B_DQ53

M_B_DQ48

M_B_DQ54

M_B_DQ56

M_B_DQ58

M_B_DQ60

M_B_DQ59

M_B_DQ57

M_B_DQ61

M_B_DQ62

M_B_DQ63

CK0

CK0#

110

113

115

M_B_DQ8

M_B_DQ12

M_B_DQ10

M_B_DQ11

M_B_DQ9

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ4

M_B_DQ0

M_B_DQ6

M_B_DQ3

M_B_DQ5

M_B_DQ1

M_B_DQ7

M_B_DQ2

M_B_DQ20

M_B_DQ19

M_B_DQ17

M_B_DQ22

M_B_DQ18

M_B_DQ21

M_B_DQ23

M_B_DQ16

M_B_DQ29

M_B_DQ28

M_B_DQ30

M_B_DQ31

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ39

M_B_DQ33

M_B_DQ32

M_B_DQ34

M_B_DQ38

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ45

M_B_DQ44

M_B_DQ47

M_B_DQ46

M_B_DQ49

M_B_DQ51

M_B_DQ50

M_B_DQ55

M_B_DQ52

M_B_DQ53

M_B_DQ48

M_B_DQ54

M_B_DQ56

M_B_DQ58

M_B_DQ60

M_B_DQ59

M_B_DQ57

M_B_DQ61

M_B_DQ62

M_B_DQ63

CS0#

CS1#

CKE0

CKE1

NP1

NP2

SC1U10V2KX-L1-GP

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

NP1

NP2

RAS#

WE#

CAS#

109

108

5 M_B_BS0

5 M_B_BS1

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15

A16/BA2

98

97

96

95

92

91

90

86

89

85

107

84

83

119

80

78

79

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

5 M_B_A0

5 M_B_A1

5 M_B_A2

5 M_B_A3

5 M_B_A4

5 M_B_A5

5 M_B_A6

5 M_B_A7

5 M_B_A8

5 M_B_A9

5 M_B_A10

5 M_B_A11

5 M_B_A12

5 M_B_A13

5 M_B_A14

5 M_B_A15

5 M_B_BS2

Brook_SLU

20140926 JACK

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A2

Date:

5

DDR3-SODIMM2

Document Number

Rev

Brook_SLU

Monday, July 06, 2015

Sheet

1

1M

13

of

105

STRAP RESISTORS SHOULD BE PLACED CLOSE TO SOC

SHOULD BE PLACED OUTSIDE KOZ AREA

SSID = STRAP

Display Port

B Detected

Description

GPIO

GPP_E19

Display Port

C Detected

Reserved

GPP_E21

SPI0_MISO

Boot BIOS

strap bit BBS

No reboot

GPP_B18

Flash descriptor

security override

GPP_B22

Display Port

D Detected

HDA_SDO

GPP_E23

3D3V_S0

3D3V_S5

3D3V_S0

3D3V_S0

R1441

10KR2J-3-GP

1

R1407

1KR2J-L2-GP

R1408

1KR2J-L2-GP

R1443

10KR2J-3-GP

DY

DY

1

2

DY

2

DY

RN1401

SRN2K2J-5-GP

Schematic

4

3

3D3V_S0

SPI_SO_CPU

HDMI_DATA_CPU 3,57

HDMI_CLK_CPU 3,57

GPP_B18/GSPI0_MOSI

GPP_B22/GSPI1_MOSI

6

DDPD_CDA

High

Detected

Detected

Enable

LPC

Disable

Detected

Low

Not Detected

Not Detected

Disable

SPI

Enable

Not Detected

internal pull-down

internal pull-down

internal pull-down

eSPI or LPC

Reserved

TLS Confidentiality

SPI0_MOSI

SPI0_IO2

SPI0_IO3

GPP_C2

3D3V_S5

DY

GPP_B23

3D3V_S5

R1437

1KR2F-L1-GP

3D3V_S5

R1438

10KR2J-3-GP

R1439

10KR2J-3-GP

R1440

150KR2J-GP

DY

DY

DY

Schematic

R1436

1KR2F-L1-GP

R1435

10KR2J-3-GP

DY

GPP_C5

3D3V_S5

R1415

1KR2J-L2-GP

3D3V_S5

Reserved

3D3V_S5

2

3D3V_S0

Reserved

GPP_B14

Reserved

GPIO

internal pull-down

Top Swap

Override

Description

internal pull-up

internal pull-down

internal pull-down

18

20150112 SC Jack

HDA_SPKR

17,27

SPI_SI_CPU

18

SPI_WP_ROM_R

25

SPI_HOLD_ROM_R

25

GPP_C2/SMBALERT#

18

GPP_C5/SML0ALERT#

High

Enable

Enable

eSPI

Low

Disable

Disable

LPC

internal pull-down

internal pull-up

internal pull-up

internal pull-up

internal pull-down

internal pull-down

18

GPP_B23/SML1ALERT#

18

internal pull-down

<Core Design>

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Title

Size

A2

Date:

5

(Reserved)_SODIMM _SODIMM4

Rev

Brook_SLU

1M

Document Number

Monday, July 06, 2015

Sheet

1

14

of

105

Main Func = PCH

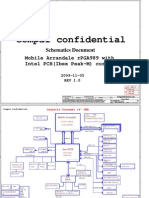

8 OF 20

CPU1H

SKYLAKE_ULT

SSIC / USB3

PCIE/USB3/SATA

dGPU

LAN

76 PEG_RX_CPU_N0

76 PEG_RX_CPU_P0

76 PEG_TX_CON_N0

76 PEG_TX_CON_P0

PX

PX

C1507

C1509

1

1

2 SCD22U10V2KX-L1-GP PEG_TX_CPU_N0

2 SCD22U10V2KX-L1-GP PEG_TX_CPU_P0

H13

G13

B17

A17

76

76

76

76

PEG_RX_CPU_N1

PEG_RX_CPU_P1

PEG_TX_CON_N1

PEG_TX_CON_P1

PX

PX

C1510

C1508

1

1

2 SCD22U10V2KX-L1-GP PEG_TX_CPU_N1

2 SCD22U10V2KX-L1-GP PEG_TX_CPU_P1

G11

F11

D16

C16

76 PEG_RX_CPU_N2

76 PEG_RX_CPU_P2

76 PEG_TX_CON_N2

76 PEG_TX_CON_P2

PX

PX

C1513

C1514

1

1

2 SCD22U10V2KX-L1-GP PEG_TX_CPU_N2

2 SCD22U10V2KX-L1-GP PEG_TX_CPU_P2

H16

G16

D17

C17

76

76

76

76

PEG_RX_CPU_N3

PEG_RX_CPU_P3

PEG_TX_CON_N3

PEG_TX_CON_P3

PX

PX

C1515

C1516

1

1

2 SCD22U10V2KX-L1-GP PEG_TX_CPU_N3

2 SCD22U10V2KX-L1-GP PEG_TX_CPU_P3

G15

F15

B19

A19

31

31

31

31

PCIE_RX_CPU_N5

PCIE_RX_CPU_P5

PCIE_TX_CPU_N5

PCIE_TX_CPU_P5

F16

E16

C19

D19

G18