Beruflich Dokumente

Kultur Dokumente

Design and Simulation of DAC On The Basis of Capacitor Array

Hochgeladen von

AmitOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Design and Simulation of DAC On The Basis of Capacitor Array

Hochgeladen von

AmitCopyright:

Verfügbare Formate

International Journal of Computer Applications (0975 8887)

International Conference on Quality Up-gradation in Engineering, Science and Technology (ICQUEST2015)

Design and Simulation of DAC on the basis of Capacitor

Array

Pranit G. Konde

R. N. Mandavgane

A. P. Bagade

M.Tech IVth sem. (VLSI),

B.D.C.E, Sevagram

Nagpur University

Associate professor & HOD.

E&TC Dept.B.D.C.E,

Sevagram

Nagpur University

Assistance professor

E&TC Dept.B.D.C.E,

Sevagram

Nagpur University

ABSTRACT

2. LITERATURE SURVEY

DAC can be basically design on the basis of capacitor array

by applying a specific amount of voltage and some circuitries

are also included for the proper functioning of the system. The

designing of DAC is performed on the basis of capacitor array

and the circuits will gives better results. When a DAC is used

to decode the binary digital signals, meaningful output

appears. The 10 bit digital signals and inverters are used for

the specific design and for the efficient and necessary results

the capacitors are used which are connected with inverters

which are further interconnected with each other to form the

final DAC output properly in order to give the better result for

the double-tail comparator. And similarly on the basis of this

result we can easily design the substitute module which is

necessary.

Brian P. Ginsburg developed a capacitive digital- to-analog

converter (DAC), a comparator, and control logic which is

called the SAR. To minimize the error between the digital

output signal and the analog input signal the control logic

switches the DAC using a binary search algorithm. The split

capacitor array and comparator, the two analog blocks are

design under 65nm CMOS technology. The conventional

DAC choice is a binary-weightedcapacitor array which is

insensitive to stray capacitance. However, the conventional

capacitor array uses charge inefficiently during aconversion

process. In order toexpress this, a conversion of a 2-bit

capacitor array is presented [4].

Keywords

DAC, digital-to-analog conversion, Inverter, Capacitors

Array.

1. INTRODUCTION

circuits that interface both analog and digital signals, which is

often determined by its Input-referred offset voltage, which is

essential for the resolution of high-performance DACs [3].

Digital-to-analog conversion is a process in which signals

having a few defined levels or states i.e. digital in nature

which are converted into the signals which having a

theoretically infinite number of states i.e. analog in nature. A

digital to analog conversion process is a function that converts

digital signal data into an analog signal either current or

voltage. Unlike analog signals, digital data can be transmitted,

Manipulated, and stored without degradation.

Basically, digital-to-analog conversion process is the opposite

of analog-to-digital conversion process. Comparator is

commonly used in flash as well as SAR-ADC and DAC

because of their decision making speed regarding to

equipments [1]. In most of the cases, if an analog-to-digital

converter (ADC) is placed in a communications circuit after a

DAC, the digital output signal is identical to the digital input

signal. Also, in most applications when a DAC is placed after

an ADC, the analog output signal is identical to the analog

input signal. Both the DAC and the ADC are of significance

in some applications of digital signal processing. Many high

speed DAC needs high-speed with small chip area [2]. The

intelligibility or fidelity of an analog signal can be mostly

improved by converting the analog input signal to digital form

using an ADC, then clarifying the obtained digital signal, and

finally converting the "cleaned-up" digital impulses back to

analog from using a DAC.

Chih-Wen Lu obtained novel resistor-floating-resistor- string

digital-to-analog converter (RFR-DAC) architecture with a

10-bit resolution for liquid crystal display (LCD) driver

applications. It contains shift registers, input registers, data

latches, level shifters, DACs and output buffers, within the

column driver. Among these components, DACs and output

buffers find out the speed, resolution, voltage swing, and

power dissipation of a column driver. Resistor-resistor-string

DACs (RRDACs) utilizing two cascaded resistor strings. The

first resistor string provides a little equal voltage segments

between two reference voltages. A voltage selector chooses

two coherent voltages and, then, sends them to the second

resistor string for extra fine voltage division. RFR-DAC

architecture capable of acquire high linearity and high

uniformity [5].

3. PURPOSE OF DAC

1. To convert digital values to analog voltages

2. Performs inverse operation of the Analog-toDigital Converter (ADC)

3. Vout Digital value.

Reference Voltage

Digital Value

DAC

Analog Voltage

Fig1:- Symbol of DAC

4. DESIGN TOOLS

DAC is fabricated in 90nm CMOS technology in the tanner

tool EDA software. Tanner Tools Pro is a software suite for

the design, layout and verification of analog, mixed-signal,

International Journal of Computer Applications (0975 8887)

International Conference on Quality Up-gradation in Engineering, Science and Technology (ICQUEST2015)

RF and MEMS ICs. Tanner Tools Pro consists of fullyintegrated front end and back end tools, from schematic

capture, circuit simulation, and waveform probing to physical

layout and verification.

6. DESIGNING OF DAC

L-Edit Pro is a comprehensive physical layout and verification

system that accelerates design cycles with high performance

and an extremely short learning curve. T-Spice Pro, Tanner

EDAs design entry and simulation system includes S-Edit for

schematic capture, T-Spice for circuit simulation and W-Edit

for waveform probing.

In this software we design the module in S-EDIT with the

help of given circuitry and the simulation waveform can be

check in T-SPICE and after that we can easily check the

output which showing different regions. After simulation in

T-SPICE the waveform is shown with the specific output with

respect to input and it gives the necessary result asrequired

and the conversion of digital signal to analog signal takes

place.

5. BLOCK DIAGRAM OF DAC

B9

Inverter

512pF

rrrrrrrr

rrInverter

256pF

B7

Inverter

128 pF

B6

Inverter

B5

Inverter

7. WORKING OF DAC

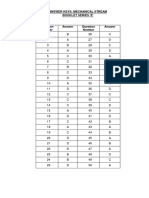

10 bit digital input signals from B0-B9 are used for

the designing of DAC and inverter gets connected to every

input bit. It brings into inversion process and gives analog

output which varies inversely. It means that if the input is low

then the output becomes high and on the other hand if the

input is high then the output becomes low which means that

output is inversely proportional with the input shows the

conditions given below.

I/P LOW = O/P HIGH

B8

Fig3:- Design of DAC in Tanner Tool

I/P HIGH = O/P LOW

64pF

32pF

B4

Inverter

16pF

B3

Inverter

8pF

B2

Inverter

DAC_out

Capacitor is used to balance the final output of the circuit and

output becomes varies with respect to input. The capacitors

are used according to the 10 digital input signals and the

ranging of capacitor is from 1pF-512pF. With every input bit

from descending order the value of capacitor increases with

each input signals. This condition shows that output is directly

proportional with the input.

The design of DAC using the capacitor array is important for

the double-tail comparator in order to provide the proper

supply voltage and also to achieve and optimized the

performance of the resulting parameters. Capacitor circuits are

used to provide accurate voltage gain. A switched capacitor is

an electronic circuit element used for discrete time signal

processing It works by moving charges into and out of

capacitors when switches are opened and closed. The use of

capacitor array in current design gives the stable output.

4pF

B1

B0

Inverter

Inverter

2pF

8. TABLE 1:

1pF

Fig2:- Block diagram of DAC

International Journal of Computer Applications (0975 8887)

International Conference on Quality Up-gradation in Engineering, Science and Technology (ICQUEST2015)

9. OUTPUT WAVEFORM

Fig 4:Output Waveform

10. CONVERSION CALCULATIONS

13. REFERENCES

Digital to Analog conversion involves transforming the

computers binary output in the form of 0s and 1s (1s

Typically = 5.0 volts) into an analog representation of the

binary data.If we are using a 10-bit converter, the

binaryrepresentation is 10-bit binary number which can take

on 29 or 512 different

values. If our voltage range is suppose to be 0 - 5 volts, then

[1] Samaneh Babayan-Mashhadi, and Reza Lotfi, Analysis

And Design of a Low-Voltage Low-Power Double-Tail

Comparator in. proc. IEEE. Int. Midwest Symp. Circuits

syst. papers, vol.22, pp.1063-8210, Feb.2014.

0000000000

Bit 9

MSB

0 VOLTS

Bit 0

LSBs

1111111111

5 VOLTS

Bit 9

MSB

Bit 0

LSB

11. RESULT

From the above output waveform of DAC, it is clear that the

digital signals are discrete in nature and the analog signals are

continuous in nature and the result is shown in the waveform.

The digital signals decreases from high to low value and at the

same time by using a capacitor array design the analog input

increases from low to high value which affect on the analog

output. This indicates that the output is stable with respect to

input.

12. CONCLUSION

We conclude that, the designing of DAC on the basis of

capacitor array is often easy and more efficient. This work

uses the capacitor array because it has both the lowest

switching energy and does not require an extra clock phase

that would limit high speed operation. It gives better result

while using capacitor array for the stable output which is

necessary for the circuit. This strategy gives high speed and

with increasing value of capacitor the output becomes more

stable.

[2] P. M. Figueiredo and J. C. Vital, Kickback noise

reduction technique For CMOS latched comapartors,

IEEE Trans. Circuits Syst. II, Exp.Briefs, vol. 53, no. 7,

pp. 541545, Jul. 2006.

[3] J. Li and U. Moon, High-speed pipelined ADC using

Time-shifted CDS technique, in Proc. IEEE Int. Symp.

Circuits Syst, vol. I May 2002, pp. 909912.

[4] Masaya Miyahara, Akira Matsuzava, A Low-Offset

Latched Comparator Using Zero-Static Power Dynamic

Offset Cancellation Technique,IEEE A Solid-state

Circuits, Vol. 56, no. 5, pp. 911-919, May 2009.

[5] Brian P. Ginsburg, and Anantha P. Chandrakasan,500MS/s 5-bit ADC In 65-nm CMOS with Split Capacitor

Array DAC, IEEE A Solid-state Circuits, vol. 42, no. 4,

pp. 0018-9200, April 2007.

[6] Chih-Wen Lu, Ping-Yeh Yin, and Ching-Min Hsiao,

A10-bit Resistor-Floating-Resistor-String DAC (RFRDAC) for High Color-Depth LCD Driver ICs, IEEE A

Solid-states Circuits, vol. 47, no. 10, October 2012.

[7] A. Ali and K. Nagaraj, Correction of operational

amplifier gain error in Pipelined A/D converters, in

Proc. IEEE Int. Symp. Circuits and Systems, vol. I, May

2001, pp. 568571.

[8] B. P. Ginsburg and A. P. Chandrakasan, An energyefficient charge recycling approach for a SAR converter

Withcapacitive DAC, in Proc.IEEE Int. Symp. Circuits

andSystems, 2005, vol. 1, pp. 184187.

[9] C.-H. Lin and K. Bult, A 10-b, 500-MSample/s CMOS

DAC in 0.6mm,IEEE J. Solid-State Circuits, vol. 33,

no. 12, pp. 19481958, Dec. 1998.

10

International Journal of Computer Applications (0975 8887)

International Conference on Quality Up-gradation in Engineering, Science and Technology (ICQUEST2015)

[10] G. Promitzer, 12-bit low-power fully differential

switched

capacitorNoncalibrating

successive

approximation ADC with 1 MS/s, IEEE J.Solid-State

Circuits, vol. 36, no.7, pp. 11381143, Jul. 2001.

[11] J.-K. Woo, D.-Y. Shin, D.-K. Jeong, and S. Kim, Highspeed 10-bitLCD column driver with a split DAC and a

Class-AB output buffer,IEEE Trans. Consum. Electron,

vol. 55, no. 3, pp. 14311438, Aug. 2009.

[12] M. J. Bell, An LCD column driver using a switch

Capacitor DAC,IEEE J. Solid-State Circuits, vol. 40,

IJCATM : www.ijcaonline.org

no.12, pp. 27562765, Dec. 2005

[13] C.-W. Lu, C.-C. Shen and W.-C. Chen, An areaefficient fully R-DAC-based TFT-LCD column driver,

IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 10,

pp. 25882601, Aug. 2010.

[14] Y.-C. Sung, S.-M. So, J.-K. Kim and O.-K. Kwon, 10

bit source Driver with resistor-resistor-string digital to

analog converter, in SIDInt. Symp., Seminar

&Exhibition Dig. Tech. Papers, May 2005, vol. 36, no.1,

pp. 10991101.

11

Das könnte Ihnen auch gefallen

- Design and Simulation of 1-Bit Sigma-Delta ADC Using Ngspice ToolDokument5 SeitenDesign and Simulation of 1-Bit Sigma-Delta ADC Using Ngspice ToolIjarcsee JournalNoch keine Bewertungen

- DLC LAB - 10 - Student - ManualDokument8 SeitenDLC LAB - 10 - Student - ManualImtiaj SajinNoch keine Bewertungen

- DAC ConverterDokument10 SeitenDAC ConverterAmarnath M DamodaranNoch keine Bewertungen

- Cadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyDokument6 SeitenCadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyUtsavNoch keine Bewertungen

- DLC Lab - 10Dokument7 SeitenDLC Lab - 10Didarul Alam AlifNoch keine Bewertungen

- Design of 16-Bit SAR ADC Using DTMOS Technique: Yarlagadda Archana, Kakarla Hari KishoreDokument9 SeitenDesign of 16-Bit SAR ADC Using DTMOS Technique: Yarlagadda Archana, Kakarla Hari KishoreBüşra AkyıldızNoch keine Bewertungen

- Experiment No. 4 ADC PDFDokument16 SeitenExperiment No. 4 ADC PDFRia Cordova0% (1)

- Dec Exp 6 Student ManualDokument5 SeitenDec Exp 6 Student ManualSakib MahmudNoch keine Bewertungen

- El Amraouiyine ImadDokument22 SeitenEl Amraouiyine ImadImad EL AmraouiyineNoch keine Bewertungen

- Design of A Pipelined 8b 10MSPS Analog To Digital Converter From System To OTADokument22 SeitenDesign of A Pipelined 8b 10MSPS Analog To Digital Converter From System To OTAZarion JacobsNoch keine Bewertungen

- Chapter 1 IntroductionDokument39 SeitenChapter 1 IntroductionNivedini KuttiNoch keine Bewertungen

- TI Data Converter GuideDokument16 SeitenTI Data Converter GuideDavid PostonNoch keine Bewertungen

- Icaet2017073 PDFDokument5 SeitenIcaet2017073 PDFKaushik YadiyalNoch keine Bewertungen

- Dac PDFDokument7 SeitenDac PDFsanthoshNoch keine Bewertungen

- REPORTFINALDokument21 SeitenREPORTFINALReal HumanityNoch keine Bewertungen

- Analog To Digital ConverterDokument14 SeitenAnalog To Digital Converterparth bhardwajNoch keine Bewertungen

- Digital-to-Analog Analog-to-Digital: Interface Part IV MicroprocessorDokument30 SeitenDigital-to-Analog Analog-to-Digital: Interface Part IV MicroprocessorVineeth KumarNoch keine Bewertungen

- Lab Manual DAC-SignedDokument10 SeitenLab Manual DAC-Signedabidrk_21789100% (2)

- DEC LAB REPORT-06Dokument9 SeitenDEC LAB REPORT-06anon_776365175Noch keine Bewertungen

- 06 Wireless ReportDokument17 Seiten06 Wireless ReportshastryNoch keine Bewertungen

- Design and Implementation of A 10 Bit SAR ADCDokument4 SeitenDesign and Implementation of A 10 Bit SAR ADCVipul ChauhanNoch keine Bewertungen

- 8 A-D ConverterDokument30 Seiten8 A-D Converterneoloader145Noch keine Bewertungen

- Thesis On Pipeline AdcsDokument6 SeitenThesis On Pipeline Adcsamyholmesmanchester100% (2)

- A High Performance 90 NM CMOS SAR ADC With HybridDokument8 SeitenA High Performance 90 NM CMOS SAR ADC With HybridSounakDuttaNoch keine Bewertungen

- P109 113 PDFDokument5 SeitenP109 113 PDFSuraj Kumar PrustyNoch keine Bewertungen

- Pipelined AdcDokument26 SeitenPipelined AdcKausar Fathima100% (1)

- DAQDokument34 SeitenDAQKhairul FahzanNoch keine Bewertungen

- Sar AdcDokument40 SeitenSar AdcNivedini KuttiNoch keine Bewertungen

- PresynopsisDokument26 SeitenPresynopsisSav ThaNoch keine Bewertungen

- Design of A High Speed 6 Bit Successive Approximate Register Analog To Digital Converter SAR ADC Using 45nm CMOS TechnologyDokument10 SeitenDesign of A High Speed 6 Bit Successive Approximate Register Analog To Digital Converter SAR ADC Using 45nm CMOS TechnologyTENS DeviceNoch keine Bewertungen

- A 12bit 250MSPS Pipeline ADC With 4 Gbps Serial Output InterfaceDokument11 SeitenA 12bit 250MSPS Pipeline ADC With 4 Gbps Serial Output InterfaceKasi BandlaNoch keine Bewertungen

- Flash ADC MidsemDokument9 SeitenFlash ADC MidsemBikashKumarMoharanaNoch keine Bewertungen

- 12EC62R20 Ramesh SynopsisDokument9 Seiten12EC62R20 Ramesh Synopsisprasad72207Noch keine Bewertungen

- International Journal of Engineering Research and DevelopmentDokument8 SeitenInternational Journal of Engineering Research and DevelopmentIJERDNoch keine Bewertungen

- ASSESSMENT 2: D/A and A/D convertersDokument7 SeitenASSESSMENT 2: D/A and A/D convertersRamesh RaamNoch keine Bewertungen

- Adc - DacDokument4 SeitenAdc - DacShaheer TariqNoch keine Bewertungen

- ADC DAC Loopback LinearityDokument15 SeitenADC DAC Loopback LinearityparrotpanduNoch keine Bewertungen

- Dac Interface To 8051 PDFDokument4 SeitenDac Interface To 8051 PDFRAVI100% (1)

- Applications of 8085 Microprocessor Dac InterfaceDokument4 SeitenApplications of 8085 Microprocessor Dac InterfaceSai PrakashNoch keine Bewertungen

- 3 Design and Simulation of First Order Sigma-Delta ModulatorDokument4 Seiten3 Design and Simulation of First Order Sigma-Delta Modulatorlim hyNoch keine Bewertungen

- Interfacing To The Analog WorldDokument47 SeitenInterfacing To The Analog WorldRM ZhaloNoch keine Bewertungen

- Analog To Digital ConverterDokument11 SeitenAnalog To Digital ConverterFf Fr100% (1)

- Oregon State OR 9733 I, USA: Jipeng Gil-Cho Ahn, Dong-Young Chang, and Un-Ku MoonDokument4 SeitenOregon State OR 9733 I, USA: Jipeng Gil-Cho Ahn, Dong-Young Chang, and Un-Ku MoonAlex WongNoch keine Bewertungen

- Modeling of Sigma Delta Modulator Non Idealities With Two Step Quantization in MATLAB SIMULINK PDFDokument6 SeitenModeling of Sigma Delta Modulator Non Idealities With Two Step Quantization in MATLAB SIMULINK PDFeditor_ijcatNoch keine Bewertungen

- Analog To Digital ConverterDokument4 SeitenAnalog To Digital Convertermuzamiru Kahise sayumweNoch keine Bewertungen

- Paper Single Slope ADCDokument4 SeitenPaper Single Slope ADCArdittoTrianggada100% (1)

- A D ConverterDokument20 SeitenA D ConverterRenu TyagiNoch keine Bewertungen

- Analog To Digital (ADC) and Digital To Analog (DAC) ConvertersDokument12 SeitenAnalog To Digital (ADC) and Digital To Analog (DAC) ConvertersIoana IoanaNoch keine Bewertungen

- Digital Control SystemDokument23 SeitenDigital Control SystemBHAVNA AGARWALNoch keine Bewertungen

- Data ConversionDokument4 SeitenData ConversionpauliNoch keine Bewertungen

- High-Performance D/A-Converters: Application to Digital TransceiversVon EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNoch keine Bewertungen

- ADC Design Guide MicrochipDokument0 SeitenADC Design Guide MicrochipOrlando MartínNoch keine Bewertungen

- Low Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron TechnologyDokument5 SeitenLow Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron Technologyeditor_ijtel100% (1)

- Nama: Refin Ananda NIM: 3.32.17.0.20 Kelas: EK-3A Individual Presentation 2 Analog To Digital Converter 1. The Meaning of ADCDokument4 SeitenNama: Refin Ananda NIM: 3.32.17.0.20 Kelas: EK-3A Individual Presentation 2 Analog To Digital Converter 1. The Meaning of ADCRifky Yoga PratamaNoch keine Bewertungen

- 5.g 133 - Efficient Fault Effect Extraction For An IntegratedDokument4 Seiten5.g 133 - Efficient Fault Effect Extraction For An IntegratedVančo LitovskiNoch keine Bewertungen

- Experiment No. 6: Objective: ApparatusDokument4 SeitenExperiment No. 6: Objective: ApparatusNioNoch keine Bewertungen

- Central University of Punjab: BhatindaDokument14 SeitenCentral University of Punjab: Bhatindaaayush tomarNoch keine Bewertungen

- Analog-To-Digital Conversion Btech IIIDokument50 SeitenAnalog-To-Digital Conversion Btech IIILisa BhagatNoch keine Bewertungen

- Analog To Digital & Digital To Analog ConvertersDokument66 SeitenAnalog To Digital & Digital To Analog ConvertersSai Krishna Kodali100% (1)

- 2nd Sem ResultDokument48 Seiten2nd Sem ResultAmitNoch keine Bewertungen

- UPSC Result 2015Dokument43 SeitenUPSC Result 2015Vishal KumarNoch keine Bewertungen

- B.Tech./M.Tech. (ECE) Dual Degree Scheme & SyllabusDokument117 SeitenB.Tech./M.Tech. (ECE) Dual Degree Scheme & SyllabusMansi JhambNoch keine Bewertungen

- Raspberry Pi (Beginners) - First Install and SetupDokument7 SeitenRaspberry Pi (Beginners) - First Install and SetupAmitNoch keine Bewertungen

- Lec7 PDFDokument21 SeitenLec7 PDFNaresh BirudalaNoch keine Bewertungen

- Root Causes of NaxalismDokument32 SeitenRoot Causes of NaxalismNeha Das100% (1)

- EYRCPlus-PS1#2271 Image Processing PDFDokument3 SeitenEYRCPlus-PS1#2271 Image Processing PDFAmitNoch keine Bewertungen

- Computer Vision with OpenCV + PythonDokument13 SeitenComputer Vision with OpenCV + PythonVishal ShettyNoch keine Bewertungen

- Synopsis 1Dokument3 SeitenSynopsis 1AmitNoch keine Bewertungen

- Work TheoryDokument258 SeitenWork TheoryP Venu Gopala RaoNoch keine Bewertungen

- Micro ControllerDokument46 SeitenMicro ControllerSundaram NatarajanNoch keine Bewertungen

- Strowger Step by StepDokument68 SeitenStrowger Step by Stepkksin990Noch keine Bewertungen

- 1 IntroductionDokument42 Seiten1 IntroductionramNoch keine Bewertungen

- WMC - Module 2Dokument71 SeitenWMC - Module 2praneesh reddyNoch keine Bewertungen

- Experiment-6 (Familiarization ofDokument3 SeitenExperiment-6 (Familiarization ofacehabiniNoch keine Bewertungen

- Snx5176B Differential Bus Transceivers: 1 Features 3 DescriptionDokument26 SeitenSnx5176B Differential Bus Transceivers: 1 Features 3 Descriptionwillame_nelson1945Noch keine Bewertungen

- MELNICENKO2 Patent WO2007035127A1 en Inventor AndreiDokument15 SeitenMELNICENKO2 Patent WO2007035127A1 en Inventor AndreiMihai DanielNoch keine Bewertungen

- Power Factor Improvement Using Dual Boost Converter: Miss. R. S. More, Prof .D.D.AhireDokument6 SeitenPower Factor Improvement Using Dual Boost Converter: Miss. R. S. More, Prof .D.D.Ahiresai charanNoch keine Bewertungen

- HP 15-B142DX Quanta U56 DA0U56MB6E0 RevE SchematicsDokument39 SeitenHP 15-B142DX Quanta U56 DA0U56MB6E0 RevE SchematicsAbnesis NesisNoch keine Bewertungen

- Goubau - 1981 - in Memoriam Dr. George GoubauDokument1 SeiteGoubau - 1981 - in Memoriam Dr. George GoubauAhmed AbdelraheemNoch keine Bewertungen

- 002.structured Cabling-Training DocumentsDokument18 Seiten002.structured Cabling-Training DocumentsSathiya Priya NatrajNoch keine Bewertungen

- EFM32 Zero Gecko Family EFM32ZG Data SheetDokument104 SeitenEFM32 Zero Gecko Family EFM32ZG Data SheetHans ClarinNoch keine Bewertungen

- CONDENSADORES Tascam m-308Dokument2 SeitenCONDENSADORES Tascam m-308salvaesNoch keine Bewertungen

- 9A10505 Principles of CommunicationsDokument4 Seiten9A10505 Principles of CommunicationssivabharathamurthyNoch keine Bewertungen

- 7 Inch Digital MicroscopeDokument4 Seiten7 Inch Digital MicroscopeHetal PatelNoch keine Bewertungen

- Lecture (Diode As Clamper)Dokument2 SeitenLecture (Diode As Clamper)Sheikh HarisNoch keine Bewertungen

- Aerohive HiveManager centralized WLAN managementDokument2 SeitenAerohive HiveManager centralized WLAN managementMichele BrunelliNoch keine Bewertungen

- Manual DVD USB Samsung SE-S184M PDFDokument28 SeitenManual DVD USB Samsung SE-S184M PDFcasperllNoch keine Bewertungen

- Instruction Manual: IL1700 Research Radiometer: Revised: 14-Aug-98 ADRDokument32 SeitenInstruction Manual: IL1700 Research Radiometer: Revised: 14-Aug-98 ADRcostis_bNoch keine Bewertungen

- STM32F4 Discovery Board Pinou Diagram Details, Features and ExamplesDokument11 SeitenSTM32F4 Discovery Board Pinou Diagram Details, Features and ExamplesJsi DevNoch keine Bewertungen

- FCC KDB v4Dokument42 SeitenFCC KDB v4caseyjamesnNoch keine Bewertungen

- Transmission MediaDokument23 SeitenTransmission Mediakhushboo NijhawanNoch keine Bewertungen

- 289206183 SID 409 B型 英文技术说明书 V1 42Dokument78 Seiten289206183 SID 409 B型 英文技术说明书 V1 42jayapalNoch keine Bewertungen

- Audio Post Production Specification FormDokument10 SeitenAudio Post Production Specification FormX Lucie LuNoch keine Bewertungen

- Eaget M880-User Manual v1.0.3Dokument44 SeitenEaget M880-User Manual v1.0.3NewNoch keine Bewertungen

- NetworkingDokument38 SeitenNetworkingSandhuSukhamNoch keine Bewertungen

- 1 1-ManualDokument2 Seiten1 1-ManualMiggy Ys33% (3)

- IrisGT DA TechRefDokument202 SeitenIrisGT DA TechRefwrwerNoch keine Bewertungen

- AFCAT Previous Year EKT Paper Answer KeysDokument6 SeitenAFCAT Previous Year EKT Paper Answer KeysdavidsangroyaNoch keine Bewertungen

- 2007 RAM 1500 3.7L V6 P0509 IAC Valve Circuit HighDokument4 Seiten2007 RAM 1500 3.7L V6 P0509 IAC Valve Circuit HighWillie AustineNoch keine Bewertungen

- LTspice Tutorial - The Complete CourseDokument2 SeitenLTspice Tutorial - The Complete CoursersfdtdNoch keine Bewertungen

- Eflash: Contractual Information For Partners: Phase-OutDokument2 SeitenEflash: Contractual Information For Partners: Phase-OutMoises ReznikNoch keine Bewertungen

- DP610SACB ManualDokument24 SeitenDP610SACB ManualChase SmytheNoch keine Bewertungen