Beruflich Dokumente

Kultur Dokumente

Shift Register

Hochgeladen von

Leo Marcelo VillalbaCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Shift Register

Hochgeladen von

Leo Marcelo VillalbaCopyright:

Verfügbare Formate

Shift Registers using Verilog HDL

with Quartus Prime

L.M.P.Villalba, C.B.Maghamil, A.J.W. Lomoya

Fourth Year, Bachelor of Science in Electrical Engineering

I. INTRODUCTION

II. OBJECTIVES

A register is a group of binary storage cells

capable of holding binary information. A group of

flip-flops constitutes a register, since each flip-flop

can work as binary cell. An n-bit register, has n flipflops and is capable of holding n-bits of information.

In addition to flip-flops a register can have a

combinational part that performs data-processing

tasks.

Various types of registers are available in MSI

circuits. The simplest possible register is one that

contains no external gates, and is constructed of only

flip flops. All flip-flops in a register has a common

clock pulse that enables all flip-flops at the same

instant so that the information available can be

transferred. The clock pulse transition is either edgetriggered type or the master-slave type. A group of

flip-flops sensitive to the pulse duration is

commonly called a gated latch. Latches are suitable

to temporarily store binary information that is to be

transferred to an external destination. They should

not be used in the design of sequential circuits that

have feedback connections.

A register capable of shifting its binary contents

either to the left or to the right is called a shift

register. The shift register permits the stored data to

move from a particular location to some other

location within the register. Registers can be

designed using discrete flip-flops such as S-R, J-K,

and D-type.

The data in a shift register can be shifted in two

possible ways, serial shifting or parallel shifting.

The serial shifting method shifts one bit at a time for

each clock pulse in a serial manner, beginning with

either LSB or MSB. On the other hand, in parallel

shifting operation, all the data, input or output, gets

shifted simultaneously during a single clock pulse.

Hence, we may say that parallel shifting operation is

much faster than serial shifting operation.

There are two ways to shift data into the register

and similarly, there are two ways to shift data out of

the register thus leading to four basic types of

registers. Serial in/Serial out, Serial in/Parallel out,

Parallel in/Serial out, Parallel in/Parallel out, this are

the four basic types of registers.[1]

In this experiment, we are going to use the

Serial in/Parallel out, shift right, shift register to be

coded in Verilog and synthesized and upload in the

DE-1 SoC board.

The objectives of this experiment are, first, to

be able to use the shift register megafunction,

second, to import and use previous codes to drive

hex display, third, to code and upload shift register

into the DE-1 SoC board.

III. CODE

Figure 1. Code Heirarchy.

Figure 2. Shift register top level code.

Figure 3. Shift register megafunction

Verilog code.

Figure 4. HEX display module.

IV. DATA AND RESULTS

Based on the codes above, we have compiled

and synthesized the following RTL below that

represents our logic circuit within the FPGA. It

consists of the individual modules that are in the top

level module. Each of the module is represented by

a box, while the I/O are represented by bullet sign.

We will also notice that the data bus q is connected

towards two hex displays where their bits is divided

into four each, [3:0] for hex 1 and [7:4] for hex 2.

The LEDR is assigned equivalent to the value of

each bit in the 8 bit register in order to keep track of

the data shifting. The hex module takes care of the

BCD to 7 segment display.

Figure 5. Register-Transfer Level of the shift

register code.

With the code compiled and uploaded, the

following figures are the result where in every high

state of the clock the data is shifted to the right as

displayed in the leds and the BCD as shown in the 7

segment display.

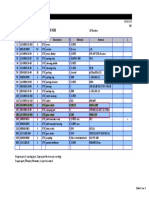

Figure 6. Shifting data from 01111111 to

00000000.

V. ANALYSIS AND CONCLUSION

A 8 bit serial in parallel out shift register is

divided into two parts. The first 4 bits from the first

input is directed towards the first hex display while

the other 4 bits is towards the second hex display.

We can see from figure 5 that we have a pushbutton

to simulate a clock pulse and a slide switch as an

input data. The data is fed towards the shift register

module as the first box and the output data bus q is

then used as an input to hex 1 and hex 2. In

accordance to this, LED is assigned the values of

each data bit in the shift register in order for the LED

to illuminate everytime the shift register shifts its

data to the right since each output is paralleled out.

As the push button is pressed, the state of the

slide switch is being used as an input data towards

the shift register. With either 0 or 1 in the slide

switch, as long as the clock pulse is in high state, the

data from the first bit is transferred in serial manner

to the right as we will see in the LED lights. The 4

bit data is displayed in the hex using binary coded

decimal equivalents.

Based on figure 6, our initial data in the shift

register is 01111111, where the 7 segment display

shows 7 and 0, 0 for hex 2 since we have default it

to 0 when it does not coincide within 0000 and 1001.

Inputting 0 everytime the clock pulse goes up, we

will see it change to 0011 1111, 0001 1111, 0000

1111, 0000 0111, 0000 0011, 0000 0001, and

00000000. Where the pair hexes displays (7,0),

(3,0), (1, 0), (0,0), (0,7), (0,3), (0,1), and (0,0).

In sum, using megafunctions makes coding

easier and neater. It also, provides simpler modeling

of the logic circuits where only the specifications

and the pins are required. Also, using modules and

importing it makes coding more organized. Lastly,

registers stores data and has a common clock that

shifts the data depending on the circuit as stated in

the four basic types above.

VI. REFERENCE

[1] Manna, N., & Saha, A. Digital Principles and

Logic Design. Infinity Science Press, MA,

2007.

Das könnte Ihnen auch gefallen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5795)

- Bat Name Echolocation Call Shape Echolocation Sonogram Specification Other RemarksDokument4 SeitenBat Name Echolocation Call Shape Echolocation Sonogram Specification Other RemarksLeo Marcelo VillalbaNoch keine Bewertungen

- Lab Report 5Dokument9 SeitenLab Report 5Leo Marcelo Villalba100% (1)

- Power Factor Corrector Calculation: System ParametersDokument1 SeitePower Factor Corrector Calculation: System ParametersLeo Marcelo VillalbaNoch keine Bewertungen

- Project Planner: 60 Plan Duration Actual Start % Complete Actual (Beyond Plan % Complete (Beyond Plan)Dokument1 SeiteProject Planner: 60 Plan Duration Actual Start % Complete Actual (Beyond Plan % Complete (Beyond Plan)Leo Marcelo VillalbaNoch keine Bewertungen

- Building Type: Hospital Building Area (Sq. M) : 797.2 Lighting Power Density (W/SQ.M) : 13 Lighting Power (W) : 10,364Dokument6 SeitenBuilding Type: Hospital Building Area (Sq. M) : 797.2 Lighting Power Density (W/SQ.M) : 13 Lighting Power (W) : 10,364Leo Marcelo VillalbaNoch keine Bewertungen

- Pre & Post EPIRA Implementation Impact To TheDokument8 SeitenPre & Post EPIRA Implementation Impact To TheLeo Marcelo Villalba100% (1)

- Parameters Unit Value Combination Number (#)Dokument7 SeitenParameters Unit Value Combination Number (#)Leo Marcelo VillalbaNoch keine Bewertungen

- Frequency Response of BJT AmplifierDokument9 SeitenFrequency Response of BJT AmplifierLeo Marcelo Villalba0% (1)

- Electronics Sample Lab ReportDokument10 SeitenElectronics Sample Lab ReportLeo Marcelo VillalbaNoch keine Bewertungen

- DC EXP4finaleDokument12 SeitenDC EXP4finaleLeo Marcelo VillalbaNoch keine Bewertungen

- Power Consumption RRLDokument6 SeitenPower Consumption RRLLeo Marcelo VillalbaNoch keine Bewertungen

- Different Shapes: Project in MathematicsDokument11 SeitenDifferent Shapes: Project in MathematicsLeo Marcelo VillalbaNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- 114 The Letter S: M 'TafontDokument9 Seiten114 The Letter S: M 'TafontHarry TLNoch keine Bewertungen

- HPE 3PAR StoreServ 20000 Storage Service and Upgrade Guide Service EditionDokument282 SeitenHPE 3PAR StoreServ 20000 Storage Service and Upgrade Guide Service Editionben boltNoch keine Bewertungen

- Ayushi Environment FinalDokument21 SeitenAyushi Environment FinalRishabh SinghNoch keine Bewertungen

- Vegetable Rates - 02-01-2021Dokument454 SeitenVegetable Rates - 02-01-2021Saurabh RajputNoch keine Bewertungen

- An Evaluation of The Strength of Slender Pillars G. S. Esterhuizen, NIOSH, Pittsburgh, PADokument7 SeitenAn Evaluation of The Strength of Slender Pillars G. S. Esterhuizen, NIOSH, Pittsburgh, PAvttrlcNoch keine Bewertungen

- Etl 213-1208.10 enDokument1 SeiteEtl 213-1208.10 enhossamNoch keine Bewertungen

- Neuropsychological Performance in Neurofibromatosis Type 1: Original ArticleDokument5 SeitenNeuropsychological Performance in Neurofibromatosis Type 1: Original ArticleRaquel DuarteNoch keine Bewertungen

- Bitsat Paper 5Dokument19 SeitenBitsat Paper 5pranka5240100% (1)

- Types of WinesDokument91 SeitenTypes of Winesrajanrld19880% (1)

- Moisture and Total Solids AnalysisDokument44 SeitenMoisture and Total Solids AnalysisNicholas BoampongNoch keine Bewertungen

- HACH LANGE Amino Acid F Reagent Powder (2353255)Dokument6 SeitenHACH LANGE Amino Acid F Reagent Powder (2353255)kerem__22Noch keine Bewertungen

- Nurtured Womb e BookDokument22 SeitenNurtured Womb e BookSteph's Desserts100% (1)

- BRASS Introduction 2012Dokument23 SeitenBRASS Introduction 20121234scr5678Noch keine Bewertungen

- Penetration Test & Softening PointDokument7 SeitenPenetration Test & Softening PointAli M. Chehadeh100% (4)

- Nissan 720 L4-2.0-Z20 1983-86 Manual PDFDokument641 SeitenNissan 720 L4-2.0-Z20 1983-86 Manual PDFEduardo Ariel JuarezNoch keine Bewertungen

- Lecture 1 - Reinforced Concrete - IntroductionDokument62 SeitenLecture 1 - Reinforced Concrete - IntroductionChristopher PaladioNoch keine Bewertungen

- Module 02 Connect Hardware Peripherals EndaleDokument49 SeitenModule 02 Connect Hardware Peripherals EndaleSoli Mondo100% (1)

- Chapter 1 - Part 1 Introduction To Organic ChemistryDokument43 SeitenChapter 1 - Part 1 Introduction To Organic ChemistryqilahmazlanNoch keine Bewertungen

- Sperm Count EvaluationDokument3 SeitenSperm Count EvaluationGarry Kin CamarilloNoch keine Bewertungen

- 3592 Operator GuideDokument103 Seiten3592 Operator GuideNaim GhattasNoch keine Bewertungen

- Wiring of The Distribution Board With RCD (Residual Current Devices) - Single Phase Home SupplyDokument14 SeitenWiring of The Distribution Board With RCD (Residual Current Devices) - Single Phase Home SupplyKadhir BoseNoch keine Bewertungen

- Syllabus (402050B) Finite Element Analysis (Elective IV)Dokument3 SeitenSyllabus (402050B) Finite Element Analysis (Elective IV)shekhusatavNoch keine Bewertungen

- Sandvik Saf 31803 Tube and Pipe, Seamless: DatasheetDokument9 SeitenSandvik Saf 31803 Tube and Pipe, Seamless: DatasheetPaul NeedhamNoch keine Bewertungen

- Thermobaric Effects Formed by Aluminum Foils Enveloping Cylindrical ChargesDokument10 SeitenThermobaric Effects Formed by Aluminum Foils Enveloping Cylindrical ChargesAnonymous QFUEsUAnNoch keine Bewertungen

- TXN Alarms 18022014Dokument12 SeitenTXN Alarms 18022014Sid GrgNoch keine Bewertungen

- Soccer Training DiaryDokument1 SeiteSoccer Training DiaryMark DeaconNoch keine Bewertungen

- Lecture 8Dokument22 SeitenLecture 8Ramil Jr. EntanaNoch keine Bewertungen

- Air Force To 32-1-101 Army TM 9 243 Navy m6290 Aj Man 1010 Marine Corp TM 10209 101 Technical Manual Use and Care of Hand Tools and Measuring Tools 14Dokument310 SeitenAir Force To 32-1-101 Army TM 9 243 Navy m6290 Aj Man 1010 Marine Corp TM 10209 101 Technical Manual Use and Care of Hand Tools and Measuring Tools 14Michael SmallNoch keine Bewertungen

- Product Specifications: MB3F-PSA4-19DEDokument2 SeitenProduct Specifications: MB3F-PSA4-19DEВадим ЧеховскийNoch keine Bewertungen

- Practical - 2: Preparation of The FixativeDokument14 SeitenPractical - 2: Preparation of The FixativeIseth ISethNoch keine Bewertungen