Beruflich Dokumente

Kultur Dokumente

A New Design 6T Full Adder Circuit Using Novel 2T XNOR Gates

Hochgeladen von

dycsteiznOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

A New Design 6T Full Adder Circuit Using Novel 2T XNOR Gates

Hochgeladen von

dycsteiznCopyright:

Verfügbare Formate

See

discussions, stats, and author profiles for this publication at: https://www.researchgate.net/publication/279954128

A new design 6T Full Adder Circuit using Novel

2T XNOR Gates

Article April 2015

DOI: 10.9790/4200-05316368

CITATIONS

READS

191

4 authors, including:

Rajeev Kumar

Dehradun Institute of Technology

15 PUBLICATIONS 6 CITATIONS

SEE PROFILE

All content following this page was uploaded by Rajeev Kumar on 10 July 2015.

The user has requested enhancement of the downloaded file. All in-text references underlined in blue are added to the original document

and are linked to publications on ResearchGate, letting you access and read them immediately.

IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)

Volume 5, Issue 3, Ver. I (May - Jun. 2015), PP 63-68

e-ISSN: 2319 4200, p-ISSN No. : 2319 4197

www.iosrjournals.org

A new design 6T Full Adder Circuit using Novel 2T XNOR Gates

Krishna Chandra1, Rajeev Kumar2, Shashank Uniyal3 ,Vishal Ramola4

M.Tech. Student of VLSI Design Department, UTU Dehradun, UK India1&4

Assist. Prof. Electronics Department UCST Dehradun, UK India 2

Assist. Prof. VLSI Design Department ,UTU , Dehradun, UK India 4

Abstract: Exclusive-NOR (XNOR) gates are important in digital circuits. This paper proposes the novel design

of 2T XNOR gate using pass transistor logic. The proposed circuit utilizes the least number of transistors and no

complementary input signals is used. The design has been compared with earlier designed XNOR gates and a

significant improvement in silicon area and power-delay product has been obtained against 3T XNOR gate.

Instead of cascading two two-input XNOR gates, we design a new structure of three-input function on the

transistor level in this paper. A 6 transistor full adder has been designed using the proposed two-transistor

XNOR gate. The performance has been investigated using 0.18m Technology and evaluated by the comparison

of the simulation result obtain from TSPICE.

Keywords: XNOR gate, Full adder, Delay, Power Delay Product.

I. INTRODUCTION

Since the battery technology available does not advance at the same rate as the microelectronics

technology, IC designers have encountered more constraints: high speed, small silicon area, and at the same

time, low power dissipation. Hence, the research of establishing high performance adder cells is becomes

feverish. The design of 1 bit full adders which forms the basic building blocks of all digital VLSI circuits has

been undergoing to minimizing the transistor, minimizing the power consumption and increasing the speed [612].

Circuit realization for low area has become an important issue with the growth of integrated circuit

towards very high integration density and high operating frequencies. Due to the important role played by

XNOR gate in various circuits especially in arithmetic circuits, optimized design XNOR circuit to achieve small

size and delay is needed. The primary concern to design XNOR gate is to obtain low power consumption and

delay in the critical path and full output voltage swing with low number of transistors to implement it. A survey

of literature reveals a wide spectrum of different types of XNOR gates that have been realized over the years.

The early designs of XNOR gates were based on either 4 transistors [3] or 3 transistors [4] that are

conventionally used in most designs.

The paper is organized as follows: in Section II, previous work is reviewed. Subsequently, in section

III, the proposed design of XNOR gate, three input XNOR gate and full adder are presented. In section IV, the

simulation results are given and discussed. The comparison and evaluation for proposed and existing designs are

carried out. Finally a conclusion will be made in the last section.

II.

PRELIMINARIES

(A) Logic Equations for the Proposed XNOR gate

The XNOR gate functions are shown in Table 1and denoted by this . The logic expression for XNOR is

A B A ' B ' AB

(1)

Table I. XNOR Gate Function

DOI: 10.9790/4200-05316368

www.iosrjournals.org

63 | Page

A new design 6T Full Adder Circuit using Novel 2T XNOR Gates

(B) Logic Equations for the Proposed Full Adders

The logical function of the 1 bit full adder operation equations presented below can be stated as follows:

given the inputs A, B and Cin which calculate two 1-bit outputs Sum, for sum and Cout, for carry out.

SUM A B C

(2)

Cout A( A B ) C ( A B )

(3)

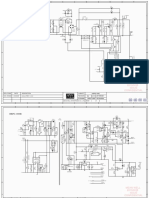

Jyh-Ming Wang at el [2] to design 4 transistor XNOR gate as shown in fig.1. This design no longer need

complementary signal inputs and only one poor signal level on output end. Author define the defect property of

a 4-transistor type is that the output level will be higher or lower than the normal case by the voltage |Vth|, the

threshold voltage of MOS. Under the condition of |Vth| value, this poor level can still drive the inverter and

make the inverter action correct.

Figure.1-4T XNOR Gate [2]

Hung Tien Bui at el [3] to design 4 transistor XNOR gate as shown in fig. 2 that is named Groundless, because

there is no ground and show the better performance previous design XNOR gate.

Figure.2-4T XNOR Gate [3]

J. Wang at el [5] to design 4 transistor XNOR gate as shown in fig 3. It is inverter base XNOR gate.

Fig.3 4T XNOR Gate [5]

Sreehari Veeramachaneni at el [4] to design XNOR gates using 3 transistors (3-T) shown in fig 3. 3 transistors

has a small delay of mere 1 transistor (1-T). However, for certain input combinations, they give bad output logic

levels. Author manipulates the (W/L) ratios of PMOS and NMOS transistors to solve this problem until an

acceptable logic level is restored.

DOI: 10.9790/4200-05316368

www.iosrjournals.org

64 | Page

A new design 6T Full Adder Circuit using Novel 2T XNOR Gates

Figure.4 3T XNOR Gate [4]

III.

Proposed Circuits

(A) 2T XNOR Gate

On the 2-transistor design, the new proposed structures require non-complementary inputs and their output

will be nearly perfect. The configurations are shown in Fig. 4. For the XNOR function, the output signal in the

case of AB = 00,01, 11 will be complete. While AB = 10, NMOS will be on and pass the poor HI signal level

to the output end.

The input combinations, they give bad output logic levels but we manipulate the (W/L) ratios of PMOS and

NMOS transistors to solve this problem until an acceptable logic level is restored..

Figure.5-Proposed 2T XNOR Gate

(B) The New Direct Design for Three-Input XNOR Function

The three-input XNOR function is usually implemented by cascading two two-input XNOR gates. Hence, the

performance of the two-input XNOR gate affects inherently the performance of the assembled three inputs

XNOR function very much. We design a new structure of three-input function on the transistor level as shown

in fig.6. The basic structure of the proposed three-input XNOR function utilizes the least number of transistors

and no complementary input signals are needed.

Figure.6 A new cascaded design of three-input XNOR function.

(C ) The Proposed Full Adders using 2T XNOR gate

As shown in Fig. 8, the 6-T full adder contains three modulestwo 3-T XNOR gates and a 2-transistor

multiplexer (2-T MUX) as shown in Fig. 7. The Sum and Cout can be obtained using (1) and (2) respectively.

Owing to the appealing traits of a small number of transistors and a mere 2-transistor (2-T) delay, it can work at

high speed with low power dissipation.

The sum output is basically obtained by a cascaded XNORing of the three inputs in accordance with equation 2.

The carry output is obtained in accordance with equation (3). The final sum of the products is obtained using a

wired XNOR logic. The W/L ratios of transistors M1-M3 are 70/.18 m as the corresponding in figure 7. The

W/L ratios of transistors M2 and M4 are same taken as 2/.90m. The W/L ratios of transistors M5 is taken as

4/.18 m and M6 is taken as 0.1/0.18 m It is quite evident from figure 6 that two stage delays are required to

obtain the sum output and at most two stage delays are required to obtain.

DOI: 10.9790/4200-05316368

www.iosrjournals.org

65 | Page

A new design 6T Full Adder Circuit using Novel 2T XNOR Gates

Figure 7. 6T full adder

IV Simulation Environment

The proposed 2T XNOR gates, three previous 4T, 3T XNOR gate, three input XNOR gate and 1-bit full adders

are simulated using Tspice in Tanner Tools. All the results are obtained in 180nm CMOS process technology

with a 5V supply voltage. In order to establish an impartial simulation circumstance, authors prefer the input

patterns in Fig. 8 and 9, which covers every possible inputs combination of A, B,

and Cin.

The delay has been measure between the time when the changing input reaches 50% of voltage level to the time

it output reaches 50% of voltage level for both rising and fall transition for Sum and Cout. The power delay

product (PDP) is measured as the product of the average delay and the average power. The output waveform of

the proposed circuit is shown in fig 7 and 8.

The comparison of the different XNOR gates and Full adders are shown in table.II according to their transistor

count, Propagation delay, power dissipation and power delay product.

Table.II: Comparison of existed XNOR gate with proposed one in terms of different.

DOI: 10.9790/4200-05316368

www.iosrjournals.org

66 | Page

A new design 6T Full Adder Circuit using Novel 2T XNOR Gates

Figure 7. Input and output waveforms of 2T XOR gate in 0.18m

Technology

Figure 8. Input and output waveforms of 6 T Full adder in 0.18m Technology

DOI: 10.9790/4200-05316368

www.iosrjournals.org

67 | Page

A new design 6T Full Adder Circuit using Novel 2T XNOR Gates

V

Conclusions

In this paper, we proposed the new design 2T XNOR gate circuit is based on the Pass Transistor Logic. The

performances of this circuit have been compared to earlier designed XNOR gate delay, power dissipation and

PDP. Also we proposed a new direct design for three-input XNOR function. The current work proposes the

design of a 6T full adder using a novel 2T XNOR gate. The newly designed full adder process the merits of

small delay, small Power-Delay product, and area saving due to lower transistor counts and special structures.

References

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

[9]

[10]

[11]

[12]

[13]

[14]

[15]

[16]

[17]

[18]

[19]

[20]

N. Weste and K. Eshraghian, Principles of CMOS VLSZ Design, Reading, MA: Addison-Wesley, 1985

W. Jyh Ming, F. Sung-Chuan, and F. Wu-Shiung, "New efficient designs for XOR and XNOR functions on the transistor level,"

Solid- State Circuits, IEEE Journal of, vol. 29, pp. 780-786, 1994.

H. T. Bui, A. K. Al-Sheraidah, and Y.Wang, New 4- transistor XOR and XNOR designs, Tech. Rep., Florida Atlantic Univ.,

Boca Raton, 1999.

Sreehari Veeramachaneni and Hyderabad, New improved 1-bit adder cells, CCECE/CCGEI, Niagara Falls. Canada, May 5-7

2008, pp. 735-738.

J. Wang, S. Fang, and W. Feng, New efficient designs for XOR and XNOR functions on the transistor level,IEEE J. Solid-State

Circuits, vol. 29, pp. 780786, July 1994

H.T. Bui, Y. Wang, Y. Jiang , Design and analysis of 10 -transistor full adders using novel XORXNOR gates, in Proc. 5th Int.

Conf. Signal Process., vol. 1, Aug. 2125, 2000, pp. 619622.

H. T. Bui, Y. Wang, and Y. Jiang, Design and analysis of low-power 10-transistor full adders using XOR-XNOR gates, IEEE

Trans. Circuit Syst. II, Analog Digit. Signal Process., vol. 49, no. 1, Jan. 2002, pp. 25 30.

A. M. Shams, T. K. Darwish, and M. A. Bayoumi, Performance analysis of low-power 1-bit CMOS full adder cells, IEEE Trans.

Very Large Scale Integr. (VLSI) Syst., vol. 10, no. 1, Feb. 2002, pp. 2029.

K.-H. Cheng and C.-S. Huang, The novel efficient design of XOR/XNOR function for adder applications,in Proc. IEEE Int.

Conf. Elect., Circuits Syst., vol. 1, Sep. 5 8, 1999, pp. 2932.

H. Lee and G. E. Sobelman, New low-voltage circuits for XOR and XNOR, in Proc. IEEE Southeastcon, Apr. 1214, 1997, pp.

225229.

M. Vesterbacka, A 14-transistor CMOS full adder with full voltage swing nodes, in Proc. IEEE Worksh. Signal Process. Syst.,

Oct. 2022, 1999, pp. 713722.

G.A. Ruiz, M. Granda, An area-efficient static CMOS carry-select adder based on a compact carry look-ahead unit,

Microelectronics Journal, Vol. 35, No. 12, 2004, pp. 939-944.

R. Zimmermann and W. Fichtner, Low-power logic styles: CMOS versus pass-transistor logic, IEEE J.Solid-State Circuits, vol.

32, July 1997, pp.107990.

N. Zhuang and H. Wu, A new design of the CMOS full adder, IEEE J. Solid-State Circuits, vol. 27, no. 5, May 1992, pp. 840

844.

E. Abu-Shama and M. Bayoumi, A new cell for low power adders, in Proc. Int. Midwest Symp. Circuits Syst., 1995, pp. 1014

1017.

A. M. Shams and M. Bayoumi, A novel high performance CMOS 1-bit full adder cell, IEEE Trans. Circuits Syst. II, Analog

Digit. Signal Process., vol. 47, no. 5, May 2000, pp. 478481.

R. Shalem, E. John, and L. K. John, A novel low-power Energy recovery full adder cell, in Proc. Great Lakes Symp. VLSI, Feb.

1999, pp. 380383.

S. Goel, M.A. Elgamel, M.A. Bayoumi, Y. Hanafy, Design Methodologies for high performance noise tolerant XOR- XNOR

circuits, IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 53, No. 4, 2006, pp. 867-878.

A. Fayed and M. Bayoumi, A low-power 10-transistor full adder cell for embedded architectures, in Proc. IEEE Symp. Circuits

Syst., Sydney, Australia, May 2001, pp. 226229

M. Vesterbacka, A 14-transistor CMOS full adder with full voltage swing nodes, in Proc. IEEE Worksh. Signal Process. Syst.,

Oct. 2022,1999, pp. 713722.

DOI: 10.9790/4200-05316368

View publication stats

www.iosrjournals.org

68 | Page

Das könnte Ihnen auch gefallen

- PIC Microcontrollers Have 10 BIT ADCDokument4 SeitenPIC Microcontrollers Have 10 BIT ADCveerakumarsNoch keine Bewertungen

- Quartus Tutorial 2 Simulation PDFDokument25 SeitenQuartus Tutorial 2 Simulation PDFBill GonzálezNoch keine Bewertungen

- HRPG 1000 R2 SchematicDokument5 SeitenHRPG 1000 R2 Schematic劉品賢Noch keine Bewertungen

- Lecture 6 Gajski Kuhn Y ChartDokument18 SeitenLecture 6 Gajski Kuhn Y ChartShiraz HusainNoch keine Bewertungen

- BLDC Sinusoidal ControlDokument6 SeitenBLDC Sinusoidal ControlOctavian MîrţiNoch keine Bewertungen

- Quartus SchematicDokument70 SeitenQuartus SchematicVítor WenzelNoch keine Bewertungen

- TC 300 Uc InglesDokument62 SeitenTC 300 Uc InglesTamo Activo MusicNoch keine Bewertungen

- 3 - CMOS InverterDokument32 Seiten3 - CMOS Inverterroxy8marie8chanNoch keine Bewertungen

- Dan Saks C++ in Embedded SystemsDokument24 SeitenDan Saks C++ in Embedded SystemsarunksahaNoch keine Bewertungen

- ECE 513 - PART1-Introduction To PIC16F84ADokument46 SeitenECE 513 - PART1-Introduction To PIC16F84AMitch100% (1)

- STDFDokument10 SeitenSTDFLionel RiviereNoch keine Bewertungen

- CMOS Translinear CellsDokument4 SeitenCMOS Translinear CellsSumitChoudharyNoch keine Bewertungen

- MTTCNDokument296 SeitenMTTCNCarlosNoch keine Bewertungen

- Chapter 2 Micro Processor and Computer in MeasurementDokument19 SeitenChapter 2 Micro Processor and Computer in MeasurementYared AssefaNoch keine Bewertungen

- Electronic Controls Handbook: DixellDokument41 SeitenElectronic Controls Handbook: DixellFran RodriguezNoch keine Bewertungen

- Design of High Speed & Power Optimized Sense Amplifier Using Deep Nano CMOS VLSI TechnologyDokument8 SeitenDesign of High Speed & Power Optimized Sense Amplifier Using Deep Nano CMOS VLSI TechnologyIJRASETPublicationsNoch keine Bewertungen

- Cd-5-Doc Quadcopter Batch No 30 PDFDokument51 SeitenCd-5-Doc Quadcopter Batch No 30 PDFjunaid 786Noch keine Bewertungen

- Programming The MCU 8051 PDFDokument48 SeitenProgramming The MCU 8051 PDFDK White LionNoch keine Bewertungen

- ADC Program For LPC2138Dokument8 SeitenADC Program For LPC2138hypernuclide100% (1)

- Line Following Robot in VerilogDokument12 SeitenLine Following Robot in VerilogAparna GopalNoch keine Bewertungen

- DEL ManualDokument94 SeitenDEL ManualAnand BongirNoch keine Bewertungen

- Laser Based Communication System PDFDokument3 SeitenLaser Based Communication System PDFPawan Kumar100% (1)

- MultiplexerDokument23 SeitenMultiplexeraanchal agarwalNoch keine Bewertungen

- DEC Report 4 (C)Dokument11 SeitenDEC Report 4 (C)S M Akash100% (1)

- Hardwired Control Unit: A Case-Study Report Submitted For The Requirement ofDokument23 SeitenHardwired Control Unit: A Case-Study Report Submitted For The Requirement ofShinde D PoojaNoch keine Bewertungen

- RP Jain Adc DacDokument27 SeitenRP Jain Adc DacAnand SinghNoch keine Bewertungen

- ATMega16 LCD Digital ClockDokument5 SeitenATMega16 LCD Digital Clockjamban48100% (1)

- DC Motor Bidirectional Speed Control Using PWM PDFDokument5 SeitenDC Motor Bidirectional Speed Control Using PWM PDFM Rameez Ur Rehman100% (1)

- Stucor CS3351-GKDokument269 SeitenStucor CS3351-GKNightdive StudiosNoch keine Bewertungen

- 8255 Ppi ExamplesDokument10 Seiten8255 Ppi Examplesvenky258100% (1)

- Push-Pull ConverterDokument3 SeitenPush-Pull ConverterBill YoungNoch keine Bewertungen

- Digital System Module 4 PDFDokument52 SeitenDigital System Module 4 PDFGeethanjali.pNoch keine Bewertungen

- PIC Timer 0 Calculation ExampleDokument3 SeitenPIC Timer 0 Calculation Examplef.last100% (1)

- 4 Bit BCD AdderDokument7 Seiten4 Bit BCD AdderJagnur SinghNoch keine Bewertungen

- Feedback 38-004Dokument15 SeitenFeedback 38-004aditya narayan shuklaNoch keine Bewertungen

- Laboratory Exercise 4Dokument14 SeitenLaboratory Exercise 4WalterYesidNoch keine Bewertungen

- Memory and Programmable LogicDokument47 SeitenMemory and Programmable Logicdewantosatrio50% (2)

- A New Chaotic System For Image EncryptionDokument5 SeitenA New Chaotic System For Image EncryptionMENANI ZineddineNoch keine Bewertungen

- Osciloscop ST16A 10MhzDokument5 SeitenOsciloscop ST16A 10Mhzflorindo1100% (1)

- Laser CommunicationDokument3 SeitenLaser CommunicationVishal KumarNoch keine Bewertungen

- Microsoft Word - INTRODUCTION TO PLC CONTROLLERSDokument115 SeitenMicrosoft Word - INTRODUCTION TO PLC CONTROLLERSMilan RakshitNoch keine Bewertungen

- What Are The Advantages and Disadvantages of The FinFET TechnologyDokument3 SeitenWhat Are The Advantages and Disadvantages of The FinFET TechnologySajan BeheraNoch keine Bewertungen

- Laser Communication SystemDokument4 SeitenLaser Communication Systemjose273Noch keine Bewertungen

- 8251A USART - Programmable Communication InterfaceDokument15 Seiten8251A USART - Programmable Communication InterfaceselvaNoch keine Bewertungen

- Automatic Load SharingDokument41 SeitenAutomatic Load SharingSaravanan ViswakarmaNoch keine Bewertungen

- Chirp Spread Spectrum (CSS) : Lora AllianceDokument14 SeitenChirp Spread Spectrum (CSS) : Lora AllianceMarko SimićNoch keine Bewertungen

- De Practical FileDokument140 SeitenDe Practical FileSahil BharalNoch keine Bewertungen

- Digital Logic Circuits Objective Questions PDFDokument9 SeitenDigital Logic Circuits Objective Questions PDFNoor AhmedNoch keine Bewertungen

- The D Flip FlopDokument7 SeitenThe D Flip FlopAlinChanNoch keine Bewertungen

- Getting Started With Intel Galileo and Intel Edison Using WyliodrinDokument179 SeitenGetting Started With Intel Galileo and Intel Edison Using WyliodrinoscarcmNoch keine Bewertungen

- Pass Transistor LogicDokument36 SeitenPass Transistor LogicMuneza NaeemNoch keine Bewertungen

- Lattice Diagram For ReflectionDokument11 SeitenLattice Diagram For ReflectionEarnest ArujNoch keine Bewertungen

- ECE 301 - Digital Electronics: Sequential Logic Circuits: FSM DesignDokument27 SeitenECE 301 - Digital Electronics: Sequential Logic Circuits: FSM DesignSuman BhardwajNoch keine Bewertungen

- Proiect TMCEP: Ianos Andrei Manoliu Andrei An IV GR 1.2 ETDokument9 SeitenProiect TMCEP: Ianos Andrei Manoliu Andrei An IV GR 1.2 ETAlinPypNoch keine Bewertungen

- C++ Project: BombermanDokument10 SeitenC++ Project: BombermanTsepo ShataNoch keine Bewertungen

- Single Bit Full Adder Design Using 8 Transistors With Novel 3 Transistors XNOR GateDokument13 SeitenSingle Bit Full Adder Design Using 8 Transistors With Novel 3 Transistors XNOR GateAnonymous e4UpOQEPNoch keine Bewertungen

- Speed and Energy Full Adder Design Restoring Logic: A High Using Complementary & Level CarryDokument4 SeitenSpeed and Energy Full Adder Design Restoring Logic: A High Using Complementary & Level CarryBappy DebnathNoch keine Bewertungen

- Low Power-Area Designs of 1bit Full Adder in Cadence Virtuoso PlatformDokument10 SeitenLow Power-Area Designs of 1bit Full Adder in Cadence Virtuoso PlatformAnonymous e4UpOQEPNoch keine Bewertungen

- A Novel High Speed and Energy Efficient 10 Transistor Full Adder DesignDokument20 SeitenA Novel High Speed and Energy Efficient 10 Transistor Full Adder Designneethusebastian1989Noch keine Bewertungen

- Ultra Low Power Vedic MultiplierDokument6 SeitenUltra Low Power Vedic MultiplierdycsteiznNoch keine Bewertungen

- Cmos Design Objective QuestionsDokument18 SeitenCmos Design Objective QuestionsdycsteiznNoch keine Bewertungen

- A 32 BIT MAC Unit Design Using Vedic MultiplierDokument6 SeitenA 32 BIT MAC Unit Design Using Vedic MultiplierdycsteiznNoch keine Bewertungen

- Questions Consolidated 11Dokument1 SeiteQuestions Consolidated 11dycsteiznNoch keine Bewertungen

- Linear: CMOS Voltage-to-Current ConverterDokument4 SeitenLinear: CMOS Voltage-to-Current ConverterdycsteiznNoch keine Bewertungen

- Bilotti 1966Dokument3 SeitenBilotti 1966dycsteiznNoch keine Bewertungen

- Vertically and Crosswise PDFDokument182 SeitenVertically and Crosswise PDFramdpc0% (1)

- Transistor 2021 Pag 3Dokument6 SeitenTransistor 2021 Pag 3StuxnetNoch keine Bewertungen

- C4 4Dokument2 SeitenC4 4Martin FrancoNoch keine Bewertungen

- IVRSDokument18 SeitenIVRSRaghvendra RaiNoch keine Bewertungen

- Waste Compactors For Roll-Off Trucks: High Efficiency and State-Of-The-Art TechniqueDokument2 SeitenWaste Compactors For Roll-Off Trucks: High Efficiency and State-Of-The-Art Techniqueshtou2Noch keine Bewertungen

- CS 530Dokument146 SeitenCS 530TruongAnNoch keine Bewertungen

- Energy Management in Textile IndustryDokument5 SeitenEnergy Management in Textile IndustryHameedullah AnsariNoch keine Bewertungen

- Battery Technology Comparison & ADVC Battery Test-R1.01-100302-LVDokument15 SeitenBattery Technology Comparison & ADVC Battery Test-R1.01-100302-LVLparejaMorenoNoch keine Bewertungen

- Power System Simulation Lab ManualDokument41 SeitenPower System Simulation Lab ManualMary Morse100% (1)

- Zero Sequence CT CatalogueDokument14 SeitenZero Sequence CT CatalogueRanjitKumarNoch keine Bewertungen

- 1.2 Day 1 - TESS VHF Training - Overview of Two Way VHF - UHF Radio NetworksDokument18 Seiten1.2 Day 1 - TESS VHF Training - Overview of Two Way VHF - UHF Radio NetworksOgunjimi Taofiki AdebisiNoch keine Bewertungen

- Gerak Gempur Physics Paper1Dokument30 SeitenGerak Gempur Physics Paper1Elly SayutiNoch keine Bewertungen

- PracticalElectronicsSeptember2022 PDFDokument76 SeitenPracticalElectronicsSeptember2022 PDFsameinsNoch keine Bewertungen

- Transient Over VoltagesDokument38 SeitenTransient Over Voltagesraghav4life8724Noch keine Bewertungen

- Inarc 400 IhDokument24 SeitenInarc 400 IhPascu AurelNoch keine Bewertungen

- Pressed PDFDokument22 SeitenPressed PDFSayan MukherjeeNoch keine Bewertungen

- Pirelli CablesDokument128 SeitenPirelli Cablesdetroit44Noch keine Bewertungen

- VLSI Design: Circuits & LayoutDokument48 SeitenVLSI Design: Circuits & Layoutchandanayadav8490Noch keine Bewertungen

- Leading and Lagging Cheat Sheet! Printable Reference - Electrical PE ReviewDokument10 SeitenLeading and Lagging Cheat Sheet! Printable Reference - Electrical PE ReviewDavid PruynNoch keine Bewertungen

- Service Manual: Accusync Lcd72VmDokument165 SeitenService Manual: Accusync Lcd72VmreyervNoch keine Bewertungen

- MTX Audio MTX Monitor Series Monitor60i Monitor6c Monitor5i Monitor600iDokument6 SeitenMTX Audio MTX Monitor Series Monitor60i Monitor6c Monitor5i Monitor600iAnonymous XgX8kTNoch keine Bewertungen

- Isolated and Regulated 5 WATT Modular DC/DC Converters: SeriesDokument3 SeitenIsolated and Regulated 5 WATT Modular DC/DC Converters: SeriesDiego SerranoNoch keine Bewertungen

- 2.TT Ref620Dokument21 Seiten2.TT Ref620Nermina MalićevićNoch keine Bewertungen

- GST IFP8 Prezentare 2015 1Dokument111 SeitenGST IFP8 Prezentare 2015 1Mohamed Abou El hassan100% (2)

- PCR Ev20mdtDokument27 SeitenPCR Ev20mdtiozsa cristianNoch keine Bewertungen

- Schedule of Loads Motor Layout: C1 C2 C3 C4 C5 C6Dokument1 SeiteSchedule of Loads Motor Layout: C1 C2 C3 C4 C5 C6John Michael Siao BolandresNoch keine Bewertungen

- Site Visit KlatccDokument25 SeitenSite Visit KlatccAmir SallehNoch keine Bewertungen

- DDN Apl Bluelog XM XC enDokument43 SeitenDDN Apl Bluelog XM XC enMinh ThànhNoch keine Bewertungen

- Bee Book by Gulzar AhmadDokument337 SeitenBee Book by Gulzar AhmadMegha Singh100% (1)

- Taizhou Kaihua Diesel Generator Sets Co., Ltd's Superior ServiceDokument2 SeitenTaizhou Kaihua Diesel Generator Sets Co., Ltd's Superior ServiceAbdulrahman Al HuribyNoch keine Bewertungen

- MS - Audio Visual System InstallationDokument9 SeitenMS - Audio Visual System InstallationDuel TimeNoch keine Bewertungen