Beruflich Dokumente

Kultur Dokumente

74HC HCT154 PDF

Hochgeladen von

neko1212121515123001Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

74HC HCT154 PDF

Hochgeladen von

neko1212121515123001Copyright:

Verfügbare Formate

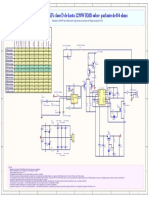

INTEGRATED CIRCUITS

DATA SHEET

For a complete data sheet, please also download:

The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

74HC/HCT154

4-to-16 line decoder/demultiplexer

Product specification

File under Integrated Circuits, IC06

September 1993

Philips Semiconductors

Product specification

4-to-16 line decoder/demultiplexer

74HC/HCT154

The 74HC/HCT154 decoders accept four active HIGH

binary address inputs and provide 16 mutually exclusive

active LOW outputs.

The 2-input enable gate can be used to strobe the decoder

to eliminate the normal decoding glitches on the outputs,

or it can be used for the expansion of the decoder.

FEATURES

16-line demultiplexing capability

Decodes 4 binary-coded inputs into one of 16 mutually

exclusive outputs

2-input enable gate for strobing or expansion

Output capability: standard

ICC category: MSI

The enable gate has two ANDed inputs which must be

LOW to enable the outputs.

GENERAL DESCRIPTION

The 154 can be used as a 1-to-16 demultiplexer by using

one of the enable inputs as the multiplexed data input.

When the other enable is LOW, the addressed output will

follow the state of the applied data.

The 74HC/HCT154 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

QUICK REFERENCE DATA

GND = 0 V; Tamb = 25 C; tr = tf = 6 ns

TYPICAL

SYMBOL

PARAMETER

tPHL/ tPLH

propagation delay An, En to Yn

CI

input capacitance

CPD

power dissipation capacitance per package

CONDITIONS

CL = 15 pF; VCC = 5 V

notes 1 and 2

Notes

1. CPD is used to determine the dynamic power dissipation (PD in W):

PD = CPD VCC2 fi + (CL VCC2 fo) where:

fi = input frequency in MHz

fo = output frequency in MHz

(CL VCC2 fo) = sum of outputs

CL = output load capacitance in pF

VCC = supply voltage in V

2. For HC the condition is VI = GND to VCC

For HCT the condition is VI = GND to VCC 1.5 V

ORDERING INFORMATION

See 74HC/HCT/HCU/HCMOS Logic Package Information.

September 1993

UNIT

HC

HCT

11

13

ns

3.5

3.5

pF

60

60

pF

Philips Semiconductors

Product specification

4-to-16 line decoder/demultiplexer

74HC/HCT154

PIN DESCRIPTION

PIN NO.

SYMBOL

NAME AND FUNCTION

1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 13, 14, 15, 16, 17

Y0 to Y15

outputs (active LOW)

18, 19

E0, E1

enable inputs (active LOW)

12

GND

ground (0 V)

23, 22, 21, 20

A0 to A3

address inputs

24

VCC

positive supply voltage

(a)

Fig.1 Pin configuration.

Fig.2 Logic symbol.

Fig.4 Functional diagram.

September 1993

(b)

Fig.3 IEC logic symbol.

Philips Semiconductors

Product specification

4-to-16 line decoder/demultiplexer

74HC/HCT154

FUNCTION TABLE

INPUTS

E0

E1

A0

H

H

L

H

L

H

X

X

X

L

L

L

L

L

L

L

L

L

L

L

L

A1

OUTPUTS

A2

A3

Y0

Y1

Y2

Y3

X

X

X

X

X

X

X

X

X

H

H

H

H

H

H

H

H

H

H

H

H

L

H

L

H

L

L

H

H

L

L

L

L

L

L

L

L

L

H

H

H

H

L

H

H

H

H

L

H

L

L

L

L

L

H

L

H

L

L

H

H

H

H

H

H

L

L

L

L

H

H

H

H

H

H

H

H

L

L

L

L

L

L

L

L

L

H

L

H

L

L

H

H

L

L

L

L

H

H

H

H

H

H

H

H

L

L

L

L

L

L

L

L

L

H

L

H

L

L

H

H

H

H

H

H

H

H

H

H

H

H

H

H

Y4

Y5

Y6

Y9

Y10 Y11 Y12 Y13 Y14 Y15

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

H

H

H

H

L

H

H

H

H

L

H

H

H

H

L

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

H

H

H

H

L

H

H

H

H

L

H

H

H

H

L

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

L

H

H

H

H

L

H

H

H

H

L

H

H

H

H

L

Note

1. H = HIGH voltage level

L = LOW voltage level

X = dont care

Fig.5 Logic diagram.

September 1993

Y7

Y8

Philips Semiconductors

Product specification

4-to-16 line decoder/demultiplexer

74HC/HCT154

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see 74HC/HCT/HCU/HCMOS Logic Family Specifications.

Output capability: standard

ICC category: MSI

AC CHARACTERISTICS FOR 74HC

GND = 0 V; tr = tf = 6 ns; CL = 50 pF

Tamb (C)

TEST CONDITIONS

74HC

SYMBOL PARAMETER

+25

min.

40 to +85

typ.

max.

min.

max.

40 to +125

min.

UNIT V

WAVEFORMS

CC

(V)

max.

tPHL/ tPLH

propagation delay

An to Yn

36

13

10

150

30

26

190

38

33

225

45

38

ns

2.0

4.5

6.0

Fig.6

tPHL/ tPLH

propagation delay

En to Yn

39

14

11

150

30

26

190

38

33

225

45

38

ns

2.0

4.5

6.0

Fig.7

tTHL/ tTLH

output transition time

19

7

6

75

15

13

95

19

16

110

22

19

ns

2.0

4.5

6.0

Figs 6 and 7

September 1993

Philips Semiconductors

Product specification

4-to-16 line decoder/demultiplexer

74HC/HCT154

DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see 74HC/HCT/HCU/HCMOS Logic Family Specifications.

Output capability: standard

ICC category: MSI

Note to HCT types

The value of additional quiescent supply current ( ICC) for a unit load of 1 is given in the family specifications.

To determine ICC per input, multiply this value by the unit load coefficient shown in the table below.

INPUT

UNIT LOAD COEFFICIENT

An

En

1.0

1.0

AC CHARACTERISTICS FOR 74HCT

GND = 0 V; tr = tf = 6 ns; CL = 50 pF

Tamb (C)

TEST CONDITIONS

74HCT

SYMBOL PARAMETER

+25

min.

40 to +85

typ.

max.

min. max.

40 to +125

min.

UNIT V

WAVEFORMS

CC

(V)

max.

tPHL/ tPLH

propagation delay

An to Yn

16

35

44

53

ns

4.5

Fig.6

tPHL/ tPLH

propagation delay

En to Yn

15

32

40

48

ns

4.5

Fig.7

tTHL/ tTLH

output transition time

15

19

22

ns

4.5

Figs 6 and 7

September 1993

Philips Semiconductors

Product specification

4-to-16 line decoder/demultiplexer

74HC/HCT154

AC WAVEFORMS

(1) HC : VM = 50%; VI = GND to VCC.

HCT: VM = 1.3 V; VI = GND to 3 V.

(1) HC : VM = 50%; VI = GND to VCC.

HCT: VM = 1.3 V; VI = GND to 3 V.

Fig.6

Fig.7

Waveforms showing the address input (An) to

output (Yn) propagation delays and the output

transition times.

Waveforms showing the enable input (En)

to output (Yn) propagation delays and the

output transition times.

APPLICATION INFORMATION

Fig.8

Fig.9

1-of-16 decoder; LOW level output is selected.

1-of-16 demultiplexer; logic level on selected

outputs follow the logic level on the data input.

PACKAGE OUTLINES

See 74HC/HCT/HCU/HCMOS Logic Package Outlines.

September 1993

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

Das könnte Ihnen auch gefallen

- Isd4003 Series: Single-Chip, Multiple-Messages Voice Record/Playback Devices 4-, 5-, 6-, AND 8-MINUTE DURATIONDokument37 SeitenIsd4003 Series: Single-Chip, Multiple-Messages Voice Record/Playback Devices 4-, 5-, 6-, AND 8-MINUTE DURATIONneko1212121515123001Noch keine Bewertungen

- 8 Appendix of Mbus StandardDokument1 Seite8 Appendix of Mbus Standardneko1212121515123001Noch keine Bewertungen

- Pic18f67k22 PDFDokument550 SeitenPic18f67k22 PDFneko1212121515123001Noch keine Bewertungen

- 25w 1250wDokument1 Seite25w 1250wneko1212121515123001Noch keine Bewertungen

- Pic18f66k90t I PTRSLDokument570 SeitenPic18f66k90t I PTRSLneko1212121515123001Noch keine Bewertungen

- 24WC01 PDFDokument10 Seiten24WC01 PDFneko1212121515123001Noch keine Bewertungen

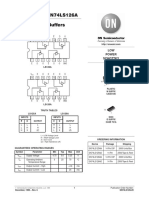

- 74LS125 PDFDokument5 Seiten74LS125 PDFneko1212121515123001Noch keine Bewertungen

- Ads 1248Dokument70 SeitenAds 1248neko1212121515123001Noch keine Bewertungen

- 2n1487 PDFDokument3 Seiten2n1487 PDFneko1212121515123001Noch keine Bewertungen

- 30 BQ060 PB FDokument6 Seiten30 BQ060 PB Fneko1212121515123001Noch keine Bewertungen

- 2 N 6517Dokument9 Seiten2 N 6517neko1212121515123001Noch keine Bewertungen

- Hih4000 PDFDokument6 SeitenHih4000 PDFneko1212121515123001Noch keine Bewertungen

- 74 HC 4060Dokument13 Seiten74 HC 4060anyenkts2Noch keine Bewertungen

- A Oh I H 4000 Install InstructionDokument4 SeitenA Oh I H 4000 Install Instructionneko1212121515123001Noch keine Bewertungen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5795)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- QueueDokument26 SeitenQueuevishnu neupane100% (1)

- 7PA22311 Datasheet En, LockoutDokument2 Seiten7PA22311 Datasheet En, LockoutBimo AdhaNoch keine Bewertungen

- Juniper IJSEC Chapter1 Course OutlineDokument6 SeitenJuniper IJSEC Chapter1 Course OutlineThuan NguyenNoch keine Bewertungen

- CCNA 1 v3.1 Module 2 Networking FundamentalsDokument57 SeitenCCNA 1 v3.1 Module 2 Networking FundamentalsPŘincê ÂĻĩNoch keine Bewertungen

- Chapter 6 Digital Arithmetic: Operations and CircuitsDokument63 SeitenChapter 6 Digital Arithmetic: Operations and CircuitsHugo Arriagada AlbarranNoch keine Bewertungen

- Introduction To The Gedit EditorDokument51 SeitenIntroduction To The Gedit Editortonitt100% (1)

- Balanza Colimatic1 Siwarex Wp231 Quick Guide Siwatool v1 5Dokument13 SeitenBalanza Colimatic1 Siwarex Wp231 Quick Guide Siwatool v1 5willianaJosefinaNoch keine Bewertungen

- Balaraj SR Ui Front End DeveloperDokument10 SeitenBalaraj SR Ui Front End DeveloperharshvardhiniNoch keine Bewertungen

- Elevator Controler Part 4 TKDokument22 SeitenElevator Controler Part 4 TKalfrelia100% (4)

- Eee312 ContentDokument2 SeitenEee312 Contentjames deepbreatheNoch keine Bewertungen

- Agent State FlowchartsDokument8 SeitenAgent State FlowchartseworkflowNoch keine Bewertungen

- 1) Two Vectors A, B Are Orthogonal IfDokument9 Seiten1) Two Vectors A, B Are Orthogonal IfRamesh MallaiNoch keine Bewertungen

- Oracle Solaris 11.3 Security and Hardening Guidelines: Part No: E54807Dokument84 SeitenOracle Solaris 11.3 Security and Hardening Guidelines: Part No: E54807MomateNoch keine Bewertungen

- MTN August Trader 2021Dokument31 SeitenMTN August Trader 2021MECHANICAL ENGINEERINGNoch keine Bewertungen

- Oracle DBA Scripts PDFDokument4 SeitenOracle DBA Scripts PDFhacenelamraoui13% (8)

- Beginner Guide Mimic Training Kit Nordbo RoboticsDokument15 SeitenBeginner Guide Mimic Training Kit Nordbo RoboticsCaio AlvesNoch keine Bewertungen

- 8052com Tutorial Reference Page 34-125Dokument92 Seiten8052com Tutorial Reference Page 34-125indusrilankaNoch keine Bewertungen

- General Purpose RegistersDokument3 SeitenGeneral Purpose RegistersAhmed SalamNoch keine Bewertungen

- 2.1.1 Computer Organization AutosavedDokument15 Seiten2.1.1 Computer Organization AutosavedSnigdha KodipyakaNoch keine Bewertungen

- Specular Tempus: User ManualDokument19 SeitenSpecular Tempus: User ManualMarc RöntschNoch keine Bewertungen

- International Focus Group For IntegrationDokument53 SeitenInternational Focus Group For IntegrationЮлия ВладыковаNoch keine Bewertungen

- AmplifiersDokument2 SeitenAmplifiersJon WestNoch keine Bewertungen

- M1M Firmware Update: Getting StartedDokument8 SeitenM1M Firmware Update: Getting StartedRaimundo FigueiredoNoch keine Bewertungen

- Vue - JS: A Javascript Framework For Building Single Page Apps (Spas)Dokument29 SeitenVue - JS: A Javascript Framework For Building Single Page Apps (Spas)HexennachtNoch keine Bewertungen

- Belarc AdvisorDokument5 SeitenBelarc Advisorneel gNoch keine Bewertungen

- SeisImager Installation Instructions v7.5Dokument1 SeiteSeisImager Installation Instructions v7.5Manuel Alejandro Estrada OchoaNoch keine Bewertungen

- Exam Seating Arrangement ProjectDokument18 SeitenExam Seating Arrangement ProjectPragya Tripathi40% (5)

- Voltages Sources and Current Sources PDFDokument21 SeitenVoltages Sources and Current Sources PDFApostolopoulos SpyrosNoch keine Bewertungen

- Sun Fire EOL (End of Life) Servers List - Acclinet Blog - (888) 486-4948Dokument3 SeitenSun Fire EOL (End of Life) Servers List - Acclinet Blog - (888) 486-4948Nitesh KohliNoch keine Bewertungen

- System Tools and Documentation TechniquesDokument4 SeitenSystem Tools and Documentation TechniquesVenice DatoNoch keine Bewertungen