Beruflich Dokumente

Kultur Dokumente

Ac07 At07

Hochgeladen von

Navaneeth NairOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Ac07 At07

Hochgeladen von

Navaneeth NairCopyright:

Verfügbare Formate

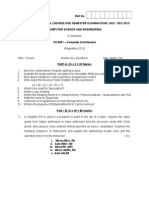

ROLL NO.

___________________

Code: AC07/AT07

Subject: COMPUTER ARCHITECTURE

AMIETE CS/IT (OLD SCHEME)

OCTOBER 2012

Time: 3 Hours

Max. Marks: 100

PLEASE WRITE YOUR ROLL NO. AT THE SPACE PROVIDED ON EACH

PAGE IMMEDIATELY AFTER RECEIVING THE QUESTION PAPER.

NOTE: There are 9 Questions in all.

Question 1 is compulsory and carries 20 marks. Answer to Q.1 must be

written in the space provided for it in the answer book supplied and nowhere

else.

The answer sheet for the Q.1 will be collected by the invigilator after 45

Minutes of the commencement of the examination.

Out of the remaining EIGHT Questions answer any FIVE Questions. Each

question carries 16 marks.

Any required data not explicitly given, may be suitably assumed and stated.

Q.1

Choose the correct or the best alternative in the following:

(2 10)

a. What is the equivalent of (1010.011)2 in decimal?

(A) 10.375

(C) -2.03

(B) 10.03

(D) -2.375

b. How many possible outputs would a decoder have with a 6-bit binary

input?

(A) 16

(C) 64

(B) 32

(D) 128

c. What is the control unit's function in the CPU?

(A)

(B)

(C)

(D)

To transfer data to primary storage

To store program instruction

To perform logic operations

To decode program instruction

d. How many address lines are needed to address each memory locations in a

2048 4 memory chip?

(A) 10

(C) 8

(B) 11

(D) 12

e. Which type of addressing is used in Stack-organized Computer?

(A) Indirect addressing

(C) Zero addressing

AC07/AT07 / OCTOBER 2012

(B) Two-addressing

(D) Index addressing

AMIETE CS/IT (OLD SCHEME)

ROLL NO. ___________________

Code: AC07/AT07

Subject: COMPUTER ARCHITECTURE

f. In which addressing mode is the register transfer instruction AC M[ADR

+ XR]?

(A) Index addressing

(C) Register indirect

(B) Relative addressing

(D) Indirect address

g. What is the complement of F AB CD BD ?

(A) F A BC DB D

(C) F ABCDBD

(B) F A BC DB D

(D) F AB CD BD

h. Which of the following instruction is described by PC AR

(A) Load

(C) Branch unconditional

(B) Store

(D) Branch and save return address

i. Which of the following is faster than the remaining storage devices?

(A) Main memory

(C) Disk Storage

(B) Cache Memory

(D) Local Disks

j. Which type of the RAM is driven with rising clock edge?

(A) Synchronous DRAM

(B) Double data-rate synchronous DRAM

(C) Video RAM

(D) None of these

Answer any FIVE Questions out of EIGHT Questions.

Each question carries 16 marks.

Q.2

a. Given two binary numbers X = 1010100 and Y = 1000011, perform the

subtraction

(i) X Y

(ii) Y X using 2s complement.

(4)

b. Design a 3-to-8-line decoder using NAND gates.

(6)

c. What is a full adder? Draw and explain block diagram and logic diagram

of full-adder circuit.

(6)

Q.3

a. What is the difference between RAM and ROM?

(4)

b. Draw a block diagram to illustrate the basic organisation system and

explain function of various units.

(6)

c. Show the block diagram of the hardware that implements the following

register transfer statement:

yT : R2 R1, R1 R2

(6)

AC07/AT07 / OCTOBER 2012

AMIETE CS/IT (OLD SCHEME)

ROLL NO. ___________________

Code: AC07/AT07

Q.4

Q.5

a. What is a subroutine?

subroutines.

Subject: COMPUTER ARCHITECTURE

Write a program to demonstrate the use of

(8)

b. Explain using a flowchart the steps carried during an interrupt cycle.

(8)

a. Write a program to evaluate (A+B) *(C+D) using

(i) zero address

(ii) one address

(iii) two address

(iv) three address instructions

(8)

b. Explain all addressing modes, with a description of how operands are

located.

(8)

Q.6

a. Explain the four segment instruction pipeline with a flow chart and timing

sequence. What are the major difficulties that cause the instruction

pipeline to deviate from normal operation?

(8)

b. What are the capabilities of address sequencing?

(4)

c. Explain the microprogrammed control unit organization with a block

diagram.

(4)

Q.7

a. Explain Booths algorithm for multiplication. Show the step by step

process of (+15) * (-13)

(10)

b. What is the disadvantage of strobe based communication? How is it

overcome by handshaking? Describe how handshaking based

communication works.

(6)

Q.8

What is virtual memory? Describe how virtual memory is implemented

using paging. Illustrate how logical address gets converted to physical

address.

(16)

Q.9

a. A two-way set associative cache memory uses blocks of four words. The

cache can accommodate a total of 2048 words from main memory. The

main memory size is 128k * 32.

(i) Format all pertinent information required to construct the cache

memory.

(ii) What is the size of the cache memory?

(6)

b. Explain DMA based data transfer with suitable block diagrams.

AC07/AT07 / OCTOBER 2012

(10)

AMIETE CS/IT (OLD SCHEME)

Das könnte Ihnen auch gefallen

- Coa Digital Tutorial Ques AnsDokument129 SeitenCoa Digital Tutorial Ques AnsRajesh TiwaryNoch keine Bewertungen

- Ca Q&aDokument129 SeitenCa Q&aRavi TejaNoch keine Bewertungen

- Ac03 At03Dokument4 SeitenAc03 At03Navaneeth NairNoch keine Bewertungen

- Question Paper Computer System Architecture (MC121) - January 2005Dokument14 SeitenQuestion Paper Computer System Architecture (MC121) - January 2005amitukumarNoch keine Bewertungen

- Computer Architecture-OBJECTIVE TYPE 75 QUESTIONS-GateDokument8 SeitenComputer Architecture-OBJECTIVE TYPE 75 QUESTIONS-GatepranavbommiNoch keine Bewertungen

- Ugc SolutionDokument174 SeitenUgc SolutionNirmal Pandey100% (1)

- 23 02 2014 Knowledge in Access To ComputersDokument21 Seiten23 02 2014 Knowledge in Access To ComputersBrandon SpencerNoch keine Bewertungen

- Computer Concepts C Programming Jan 2013 NewDokument2 SeitenComputer Concepts C Programming Jan 2013 NewPrasad C MNoch keine Bewertungen

- Computer Organization and Architecture BCA Multiple Choice QuestionsDokument2 SeitenComputer Organization and Architecture BCA Multiple Choice QuestionsInayatUllahNoch keine Bewertungen

- Multiple Choice Questions - Coa: Ans: ADokument8 SeitenMultiple Choice Questions - Coa: Ans: A30. Suraj IngaleNoch keine Bewertungen

- Gate CS 2005Dokument12 SeitenGate CS 2005reqtechNoch keine Bewertungen

- Computer Organization and Architecture PDFDokument63 SeitenComputer Organization and Architecture PDFashok psNoch keine Bewertungen

- Test Booklet Electrical Engineering Paper Ii: IES-2011 UPSC (ESE)Dokument20 SeitenTest Booklet Electrical Engineering Paper Ii: IES-2011 UPSC (ESE)kota_265Noch keine Bewertungen

- Interview Questions: 300+ Top Computer Organization & Architecture Mcqs and AnswersDokument55 SeitenInterview Questions: 300+ Top Computer Organization & Architecture Mcqs and AnswersmohammedNoch keine Bewertungen

- CSE211 MCQ'sDokument17 SeitenCSE211 MCQ'sYash Gupta MauryaNoch keine Bewertungen

- 2012 December UGC NET Paper IIIDokument16 Seiten2012 December UGC NET Paper IIIrajasekaranvgNoch keine Bewertungen

- Sample Question Paper Digital Techniques PDFDokument5 SeitenSample Question Paper Digital Techniques PDFAshutosh PatilNoch keine Bewertungen

- Multiple Choice Questions - Coa: Ans: ADokument8 SeitenMultiple Choice Questions - Coa: Ans: ADeepa GoudNoch keine Bewertungen

- CSE211 MCQ S TXT 426394401 CSE211 MCQ SDokument18 SeitenCSE211 MCQ S TXT 426394401 CSE211 MCQ SD StudiosNoch keine Bewertungen

- MCS 012Dokument4 SeitenMCS 012S.M. FarhanNoch keine Bewertungen

- J11 Question PaperDokument4 SeitenJ11 Question PapersearchingubabyNoch keine Bewertungen

- Roll No TCS 402/TIT 402: Time: Two (2) Hrs. Maximum Marks: 60Dokument18 SeitenRoll No TCS 402/TIT 402: Time: Two (2) Hrs. Maximum Marks: 60Obsii ChalaNoch keine Bewertungen

- Computer Studies: Class IX Science Group Time 3:00 Hours Max Marks 75 General InstructionsDokument2 SeitenComputer Studies: Class IX Science Group Time 3:00 Hours Max Marks 75 General InstructionsArshad Baig MughalNoch keine Bewertungen

- 9A04306 Digital Logic DesignDokument4 Seiten9A04306 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- Digital Circuits and Logic DesignDokument6 SeitenDigital Circuits and Logic DesignSharukh BujjiNoch keine Bewertungen

- Midterm LDST 2012 BatchDokument2 SeitenMidterm LDST 2012 BatchyazdanieNoch keine Bewertungen

- Paper 2Dokument8 SeitenPaper 2Antony BrownNoch keine Bewertungen

- 576 - Question - Paperfoc 7Dokument2 Seiten576 - Question - Paperfoc 7rahulgupta32005Noch keine Bewertungen

- CCP Model Question PaperDokument3 SeitenCCP Model Question Papernaveennaik099Noch keine Bewertungen

- Computer Organization & Architecture MCQs and AnswersDokument33 SeitenComputer Organization & Architecture MCQs and AnswersMs.Sangeetha Priya IT DepartNoch keine Bewertungen

- R7220404 Switching Theory and Logic DesignDokument1 SeiteR7220404 Switching Theory and Logic DesignsivabharathamurthyNoch keine Bewertungen

- Ca 13Dokument3 SeitenCa 13krishnasankar95Noch keine Bewertungen

- MCS 012Dokument5 SeitenMCS 012S.M. FarhanNoch keine Bewertungen

- LDCA Previous Year PaperDokument4 SeitenLDCA Previous Year Paperflipkart6392Noch keine Bewertungen

- 07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrDokument8 Seiten07A4EC09 SWITCHINGTHEORYANDLOGICDESIGNfrObula ReddyNoch keine Bewertungen

- Ac15 PDFDokument3 SeitenAc15 PDFNavaneeth NairNoch keine Bewertungen

- 9A12301 Digital Logic Design and Computer OrganizationDokument4 Seiten9A12301 Digital Logic Design and Computer OrganizationsivabharathamurthyNoch keine Bewertungen

- CRC of BCA (2) Assignment (Revised Syllabus)Dokument17 SeitenCRC of BCA (2) Assignment (Revised Syllabus)BshrinivasNoch keine Bewertungen

- Cs8491 Computer Architecture Unit - 2: Ans: ADokument8 SeitenCs8491 Computer Architecture Unit - 2: Ans: AASIF MNoch keine Bewertungen

- Media Communications: Test Booklet Electrical Engineering Paper IiDokument20 SeitenMedia Communications: Test Booklet Electrical Engineering Paper IiRaghuNoch keine Bewertungen

- Dec 13 001Dokument3 SeitenDec 13 001Deepak SharmaNoch keine Bewertungen

- Computer Concepts C Programming Dec 2010Dokument4 SeitenComputer Concepts C Programming Dec 2010Prasad C MNoch keine Bewertungen

- DLA3Dokument3 SeitenDLA3LaxmiNoch keine Bewertungen

- 2017S FE AM QuestionDokument28 Seiten2017S FE AM Questionfqnguyen8Noch keine Bewertungen

- Sample Paper Sample Paper Sample Paper Sample PaperDokument12 SeitenSample Paper Sample Paper Sample Paper Sample PaperAnuragGuptaNoch keine Bewertungen

- 10 Paper III Computer Science Applications PDFDokument15 Seiten10 Paper III Computer Science Applications PDFMohd HafizNoch keine Bewertungen

- Comp Ix F.T 2018-19Dokument2 SeitenComp Ix F.T 2018-19Tanveer AhmedNoch keine Bewertungen

- 10066Dokument13 Seiten10066visitmajeedNoch keine Bewertungen

- FAQs - CS1202 Digital Principles and System DesignDokument13 SeitenFAQs - CS1202 Digital Principles and System DesignsridharanchandranNoch keine Bewertungen

- 11 SDD Independent 2012 1Dokument17 Seiten11 SDD Independent 2012 1ashleyblackbeakNoch keine Bewertungen

- Digital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Dokument4 SeitenDigital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Vikash KumarNoch keine Bewertungen

- Acseh0304 (DLD) 2Dokument5 SeitenAcseh0304 (DLD) 2yt608118Noch keine Bewertungen

- CompTIA A+ Certification All-in-One Exam Questions Prep (220-701 & 220-702)Von EverandCompTIA A+ Certification All-in-One Exam Questions Prep (220-701 & 220-702)Bewertung: 2.5 von 5 Sternen2.5/5 (6)

- Up and Running with AutoCAD 2018: 2D Drafting and DesignVon EverandUp and Running with AutoCAD 2018: 2D Drafting and DesignNoch keine Bewertungen

- Software Development for Engineers: C/C++, Pascal, Assembly, Visual Basic, HTML, Java Script, Java DOS, Windows NT, UNIXVon EverandSoftware Development for Engineers: C/C++, Pascal, Assembly, Visual Basic, HTML, Java Script, Java DOS, Windows NT, UNIXBewertung: 5 von 5 Sternen5/5 (1)

- Linear Programming and Resource Allocation ModelingVon EverandLinear Programming and Resource Allocation ModelingNoch keine Bewertungen

- Field Training Report On TCD, Bengaluru: Telephone Communication Division (TCD)Dokument2 SeitenField Training Report On TCD, Bengaluru: Telephone Communication Division (TCD)Navaneeth NairNoch keine Bewertungen

- 2) VKK-17 DTD 12.05.2019 - Fire Fighting Estimate KadabaDokument1 Seite2) VKK-17 DTD 12.05.2019 - Fire Fighting Estimate KadabaNavaneeth NairNoch keine Bewertungen

- 03.RT Material - FINAL For PrintDokument26 Seiten03.RT Material - FINAL For PrintNavaneeth NairNoch keine Bewertungen

- R&M LetterDokument1 SeiteR&M LetterNavaneeth NairNoch keine Bewertungen

- 1 - 1 Je (NHK)Dokument14 Seiten1 - 1 Je (NHK)Navaneeth NairNoch keine Bewertungen

- Corporate Office in EnglishDokument44 SeitenCorporate Office in EnglishNavaneeth NairNoch keine Bewertungen

- R&M DbpuraDokument402 SeitenR&M DbpuraNavaneeth NairNoch keine Bewertungen

- Ac15 PDFDokument3 SeitenAc15 PDFNavaneeth NairNoch keine Bewertungen

- Officers Pay Scale - 9!3!2018Dokument16 SeitenOfficers Pay Scale - 9!3!2018Navaneeth NairNoch keine Bewertungen

- KPTCL Corporate Office - eDokument66 SeitenKPTCL Corporate Office - eNavaneeth NairNoch keine Bewertungen

- OCTOBER 2012: Amiete - It (Old Scheme)Dokument3 SeitenOCTOBER 2012: Amiete - It (Old Scheme)Navaneeth NairNoch keine Bewertungen

- OCTOBER 2012: Amiete - Cs/It (Old Scheme)Dokument3 SeitenOCTOBER 2012: Amiete - Cs/It (Old Scheme)Navaneeth NairNoch keine Bewertungen

- AE20Dokument3 SeitenAE20Navaneeth NairNoch keine Bewertungen

- OCTOBER 2012: Amiete - Cs/It (Old Scheme)Dokument3 SeitenOCTOBER 2012: Amiete - Cs/It (Old Scheme)Navaneeth NairNoch keine Bewertungen

- OCTOBER 2012: Amiete - It (Old Scheme)Dokument3 SeitenOCTOBER 2012: Amiete - It (Old Scheme)Navaneeth NairNoch keine Bewertungen

- Digital Logic Design - Course - OutlineDokument4 SeitenDigital Logic Design - Course - OutlinechalaNoch keine Bewertungen

- I C-Master Core Specification: Author: Richard HerveilleDokument18 SeitenI C-Master Core Specification: Author: Richard Herveillegeorge guoNoch keine Bewertungen

- LAB-Digital Assignment-Interfacing IC Working IF ALP PDFDokument9 SeitenLAB-Digital Assignment-Interfacing IC Working IF ALP PDFYOGESH PANDITNoch keine Bewertungen

- Design of Binary Multiplier Using Adders-3017 PDFDokument5 SeitenDesign of Binary Multiplier Using Adders-3017 PDFAdrian Walter JavierNoch keine Bewertungen

- Synthesis vs. SimulationDokument15 SeitenSynthesis vs. Simulationnoboder88Noch keine Bewertungen

- Lab ManualDokument10 SeitenLab Manualt.r. SanthoshNoch keine Bewertungen

- Processor SpecificationsDokument43 SeitenProcessor Specificationsshubham pandeyNoch keine Bewertungen

- EE222 Lecture 13-24 8051 MicrocontrollerDokument94 SeitenEE222 Lecture 13-24 8051 MicrocontrollerSalman HadiNoch keine Bewertungen

- EEE598 Final Report v1Dokument42 SeitenEEE598 Final Report v1jaberyemeniNoch keine Bewertungen

- Timing Issues in Digital ASIC DesignDokument101 SeitenTiming Issues in Digital ASIC Designnsai_vs1513Noch keine Bewertungen

- Static Timing Analysis Facts PDFDokument2 SeitenStatic Timing Analysis Facts PDFLalit Gohate100% (3)

- D - To - J-K Flip Flop Conversion VHDL CodeDokument2 SeitenD - To - J-K Flip Flop Conversion VHDL CodeOP2RNoch keine Bewertungen

- Synchronous UpDown Binary CounterDokument6 SeitenSynchronous UpDown Binary CounterRoemil CabalNoch keine Bewertungen

- Digital ElectronicsDokument3 SeitenDigital ElectronicsSoumyadeep PradhanNoch keine Bewertungen

- Chapter 10Dokument25 SeitenChapter 10Deivasigamani Subramaniyan0% (1)

- LD Lab 2Dokument6 SeitenLD Lab 2Nicoll Méndez ChicaNoch keine Bewertungen

- STM32F10xxx FSMC ControllerDokument31 SeitenSTM32F10xxx FSMC ControllerMayam AyoNoch keine Bewertungen

- 07 RTL Optimization TechniquesDokument20 Seiten07 RTL Optimization Techniquesgideontargrave7Noch keine Bewertungen

- Lab 5Dokument13 SeitenLab 5SHAHZAIB AHMAD QURESHINoch keine Bewertungen

- DEDokument28 SeitenDEDavid StuartNoch keine Bewertungen

- Cmos Sram K6X1008C2D Family: Document TitleDokument10 SeitenCmos Sram K6X1008C2D Family: Document TitleНиколайNoch keine Bewertungen

- Fault Tolerant Feedback Shift RegisterDokument7 SeitenFault Tolerant Feedback Shift RegisterVasanth BhaskarNoch keine Bewertungen

- Afc 1563Dokument10 SeitenAfc 1563Eugene FlexNoch keine Bewertungen

- Counters Using D FlipflopsDokument13 SeitenCounters Using D FlipflopsMostafa ElngarNoch keine Bewertungen

- Printed Circuit BoardDokument22 SeitenPrinted Circuit BoardMahiNoch keine Bewertungen

- 0 Lecture CSE - 211 (Computer Organisation and Design)Dokument12 Seiten0 Lecture CSE - 211 (Computer Organisation and Design)Pitla RishithaNoch keine Bewertungen

- Digital FundamentalsDokument28 SeitenDigital Fundamentalsbadhell_18100% (2)

- Flash MemoriesDokument52 SeitenFlash MemoriesJeff GicharuNoch keine Bewertungen

- M29F080DDokument37 SeitenM29F080DHELVER GIOVANNI RODRIGUEZ VEGANoch keine Bewertungen

- 18-Width and Resistance Calculation of PMOS and NMOS in CMOS Logic-03!02!2022 (03-Feb-2022) Material - I - 03!02!2022 - 12a. - Width - Calculation - ofDokument8 Seiten18-Width and Resistance Calculation of PMOS and NMOS in CMOS Logic-03!02!2022 (03-Feb-2022) Material - I - 03!02!2022 - 12a. - Width - Calculation - ofAniket RanjanNoch keine Bewertungen