Beruflich Dokumente

Kultur Dokumente

Vlsi Design (Eee) .Textmark

Hochgeladen von

Sheikh Noor MohammadOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Vlsi Design (Eee) .Textmark

Hochgeladen von

Sheikh Noor MohammadCopyright:

Verfügbare Formate

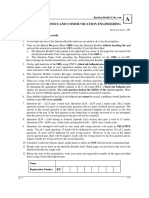

Code No: 57017

Set No. 1

JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

IV B.Tech. I Sem., I Mid-Term Examinations, September - 2014

VLSI DESIGN-[EEE]

Objective Exam

Name: ______________________________ Hall Ticket No.

A

Answer All Questions. All Questions Carry Equal Marks. Time: 20 Min. Marks: 10.

Choose the correct alternative:

1.

The main purpose of the metalization process is

a) To protect the chip for oxide

b) To act as a heat sink

c) To interconnect the various circuit elements

d) To supply a bonding surface for mounting the chip

2.

Increasing the yield of an integrated circuit

[

a) Reduce the individual circuit cost

b) Increase the cost of each good circuit

c) Results in a lower number of good chips per wafer

d) Means that more transistors can be fabricated on the same size wafer

3.

The purpose of the buried layer in a IC design

a) To reduce base resistor

b) To reduce collector resistor

c) To avoid latch up

d) To avoid short circuit

4.

The energy consumed per switching event in CMOS circuit is

a) Delay

b) Power

c) Product of delay and power

RT

AL

TU

PO

5.

.IN

I.

Good logic levels are obtained

a) Transmission gate b) NAND gate

c) NOR gate

d) All of the above

d) NOT gate

[

The thin oxide layer (SiO2) serves the following purposes

a) Enhance the input Impedance of the device

b) Make substrate surface even

c) It acts as a good de coupler between input and output

d) all of the above

7.

PMOS and NMOs are good transfer of

a) 0,1

b) 1,0

c) 0,0

JN

6.

[

d) 1,1

8.

In order to estimate rise time and fall time of inverter delay the rise time and fall time should be

[

]

a) r and f are propositional to 1/vdd

b) r and f are propositional to CL

d) all of the above

c) r = 2.5 f for equal N& P transistor geometrics

9.

Top metal layers are always used to route the signals

a) Vdd

b) Clock

c) Vdd & Clock

d) None

10.

The additional steps required to incorporate the BJT technology in CMOs technology

a) N+ sub collector b) P+ base layer c) BCCD layer d)All of the above

Cont..2

Code No: 57017

:2:

Set No. 1

Fill in the Blanks:

11.

For equal geometries of PMOS and NMOS the rise time is _____________ times of fall time

12.

An inverter driven directly from the output of the another should have Zpu /Zpd the ratio of

____________________

13.

In order to reduce the latch up problem ______________ rings are introduced

14.

In CMOS inverters in order to reduce the PMOS resistance the width of the PMOS always must be

_____________ of NMOS

15.

The size of the transistor usually defined in terms of its ________________

16.

Dynamic power dissipation in CMOS is square of _____________

17.

As the technology is scaling down in deep sub micron technology apart of dynamic power

_____________ power is playing major role

18.

Stick diagram always conveys ______________ information

19.

In CMOS circuit good isolation is done between input and output because of _____________

20.

1 micrometer per side square slab of material has exactly the same resistance as a 1 cm per side

square slab of the same material if _______________ is the same

JN

TU

PO

RT

AL

.IN

II

-oOo-

Code No: 57017

Set No. 2

JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

IV B.Tech. I Sem., I Mid-Term Examinations, September - 2014

VLSI DESIGN-[EEE]

Objective Exam

Name: ______________________________ Hall Ticket No.

A

Answer All Questions. All Questions Carry Equal Marks. Time: 20 Min. Marks: 10.

Choose the correct alternative:

1.

The energy consumed per switching event in CMOS circuit is

a) Delay

b) Power

c) Product of delay and power

Good logic levels are obtained

a) Transmission gate b) NAND gate

c) NOR gate

d) All of the above

RT

AL

2.

.IN

I.

d) NOT gate

3.

The thin oxide layer (SiO2) serves the following purposes

[

a) Enhance the input Impedance of the device

b) Make substrate surface even

c) It acts as a good de coupler between input and output

d) all of the above

4.

PMOS and NMOs are good transfer of

a) 0,1

b) 1,0

c) 0,0

d) 1,1

In order to estimate rise time and fall time of inverter delay the rise time and fall time should be

[

]

b) r and f are propositional to CL

a) r and f are propositional to 1/vdd

c) r = 2.5 f for equal N& P transistor geometrics

d) all of the above

6.

Top metal layers are always used to route the signals

a) Vdd

b) Clock

c) Vdd & Clock

d) None

7.

The additional steps required to incorporate the BJT technology in CMOs technology

a) N+ sub collector b) P+ base layer c) BCCD layer d)All of the above

8.

The main purpose of the metalization process is

a) To protect the chip for oxide

b) To act as a heat sink

c) To interconnect the various circuit elements

d) To supply a bonding surface for mounting the chip

9.

Increasing the yield of an integrated circuit

[

a) Reduce the individual circuit cost

b) Increase the cost of each good circuit

c) Results in a lower number of good chips per wafer

d) Means that more transistors can be fabricated on the same size wafer

10.

The purpose of the buried layer in a IC design

a) To reduce base resistor

b) To reduce collector resistor

c) To avoid latch up

d) To avoid short circuit

JN

TU

PO

5.

Cont..2

Code No: 57017

:2:

Set No. 2

Fill in the Blanks:

11.

In CMOS inverters in order to reduce the PMOS resistance the width of the PMOS always must be

_____________ of NMOS

12.

The size of the transistor usually defined in terms of its ________________

13.

Dynamic power dissipation in CMOS is square of _____________

14.

As the technology is scaling down in deep sub micron technology apart of dynamic power

_____________ power is playing major role

15.

Stick diagram always conveys ______________ information

16.

In CMOS circuit good isolation is done between input and output because of _____________

17.

1 micrometer per side square slab of material has exactly the same resistance as a 1 cm per side

square slab of the same material if _______________ is the same

For equal geometries of PMOS and NMOS the rise time is _____________ times of fall time

RT

AL

18.

.IN

II

An inverter driven directly from the output of the another should have Zpu /Zpd the ratio of

____________________

20.

In order to reduce the latch up problem ______________ rings are introduced.

JN

TU

PO

19.

-oOo-

Code No: 57017

Set No. 3

JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

IV B.Tech. I Sem., I Mid-Term Examinations, September - 2014

VLSI DESIGN-[EEE]

Objective Exam

Name: ______________________________ Hall Ticket No.

A

Answer All Questions. All Questions Carry Equal Marks. Time: 20 Min. Marks: 10.

Choose the correct alternative:

1.

[

The thin oxide layer (SiO2) serves the following purposes

a) Enhance the input Impedance of the device

b) Make substrate surface even

c) It acts as a good de coupler between input and output

d) all of the above

2.

PMOS and NMOs are good transfer of

a) 0,1

b) 1,0

c) 0,0

RT

AL

.IN

I.

d) 1,1

3.

In order to estimate rise time and fall time of inverter delay the rise time and fall time should be

[

]

a) r and f are propositional to 1/vdd

b) r and f are propositional to CL

c) r = 2.5 f for equal N& P transistor geometrics

d) all of the above

4.

Top metal layers are always used to route the signals

a) Vdd

b) Clock

c) Vdd & Clock

d) None

5.

The additional steps required to incorporate the BJT technology in CMOs technology

a) N+ sub collector b) P+ base layer c) BCCD layer d)All of the above

6.

The main purpose of the metalization process is

a) To protect the chip for oxide

b) To act as a heat sink

c) To interconnect the various circuit elements

d) To supply a bonding surface for mounting the chip

7.

Increasing the yield of an integrated circuit

[

a) Reduce the individual circuit cost

b) Increase the cost of each good circuit

c) Results in a lower number of good chips per wafer

d) Means that more transistors can be fabricated on the same size wafer

8.

The purpose of the buried layer in a IC design

a) To reduce base resistor

b) To reduce collector resistor

c) To avoid latch up

d) To avoid short circuit

9.

The energy consumed per switching event in CMOS circuit is

a) Delay

b) Power

c) Product of delay and power

10.

JN

TU

PO

Good logic levels are obtained

a) Transmission gate b) NAND gate

c) NOR gate

d) All of the above

d) NOT gate

Cont..2

Code No: 57017

:2:

Set No. 3

Fill in the Blanks:

11.

Dynamic power dissipation in CMOS is square of _____________

12.

As the technology is scaling down in deep sub micron technology apart of dynamic power

_____________ power is playing major role

13.

Stick diagram always conveys ______________ information

14.

In CMOS circuit good isolation is done between input and output because of _____________

15.

1 micrometer per side square slab of material has exactly the same resistance as a 1 cm per side

square slab of the same material if _______________ is the same

RT

AL

16.

.IN

II

For equal geometries of PMOS and NMOS the rise time is _____________ times of fall time

An inverter driven directly from the output of the another should have Zpu /Zpd the ratio of

____________________

18.

In order to reduce the latch up problem ______________ rings are introduced

19.

In CMOS inverters in order to reduce the PMOS resistance the width of the PMOS always must be

_____________ of NMOS

20.

The size of the transistor usually defined in terms of its ________________

JN

TU

PO

17.

-oOo-

Code No: 57017

Set No. 4

JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

IV B.Tech. I Sem., I Mid-Term Examinations, September - 2014

VLSI DESIGN-[EEE]

Objective Exam

Name: ______________________________ Hall Ticket No.

A

Answer All Questions. All Questions Carry Equal Marks. Time: 20 Min. Marks: 10.

Choose the correct alternative:

1.

In order to estimate rise time and fall time of inverter delay the rise time and fall time should be

[

]

b) r and f are propositional to CL

a) r and f are propositional to 1/vdd

c) r = 2.5 f for equal N& P transistor geometrics

d) all of the above

2.

Top metal layers are always used to route the signals

a) Vdd

b) Clock

c) Vdd & Clock

d) None

3.

The additional steps required to incorporate the BJT technology in CMOs technology

a) N+ sub collector b) P+ base layer c) BCCD layer d)All of the above

4.

The main purpose of the metalization process is

a) To protect the chip for oxide

b) To act as a heat sink

c) To interconnect the various circuit elements

d) To supply a bonding surface for mounting the chip

5.

Increasing the yield of an integrated circuit

[

a) Reduce the individual circuit cost

b) Increase the cost of each good circuit

c) Results in a lower number of good chips per wafer

d) Means that more transistors can be fabricated on the same size wafer

6.

The purpose of the buried layer in a IC design

a) To reduce base resistor

b) To reduce collector resistor

c) To avoid latch up

d) To avoid short circuit

7.

The energy consumed per switching event in CMOS circuit is

a) Delay

b) Power

c) Product of delay and power

RT

AL

TU

PO

JN

8.

.IN

I.

Good logic levels are obtained

a) Transmission gate b) NAND gate

c) NOR gate

d) All of the above

d) NOT gate

9.

[

The thin oxide layer (SiO2) serves the following purposes

a) Enhance the input Impedance of the device

b) Make substrate surface even

c) It acts as a good de coupler between input and output

d) all of the above

10.

PMOS and NMOs are good transfer of

a) 0,1

b) 1,0

c) 0,0

[

d) 1,1

Cont..2

Code No: 57017

:2:

Set No. 4

Fill in the Blanks:

11.

Stick diagram always conveys ______________ information

12.

In CMOS circuit good isolation is done between input and output because of _____________

13.

1 micrometer per side square slab of material has exactly the same resistance as a 1 cm per side

square slab of the same material if _______________ is the same

14.

.IN

II

For equal geometries of PMOS and NMOS the rise time is _____________ times of fall time

An inverter driven directly from the output of the another should have Zpu /Zpd the ratio of

____________________

16.

In order to reduce the latch up problem ______________ rings are introduced

17.

In CMOS inverters in order to reduce the PMOS resistance the width of the PMOS always must be

_____________ of NMOS

18.

The size of the transistor usually defined in terms of its ________________

19.

Dynamic power dissipation in CMOS is square of _____________

20.

As the technology is scaling down in deep sub micron technology apart of dynamic power

_____________ power is playing major role

JN

TU

PO

RT

AL

15.

-oOo-

Das könnte Ihnen auch gefallen

- EEE R13 IV-I - Revised As On 09-08-16Dokument25 SeitenEEE R13 IV-I - Revised As On 09-08-16Sheikh Noor MohammadNoch keine Bewertungen

- 9A04306 Digital Logic DesignDokument1 Seite9A04306 Digital Logic DesignsivabharathamurthyNoch keine Bewertungen

- FPGA Guide: Everything You Need to Know About Field Programmable Gate ArraysDokument14 SeitenFPGA Guide: Everything You Need to Know About Field Programmable Gate ArraysSheikh Noor MohammadNoch keine Bewertungen

- 4 Ece R13 Iv-IDokument25 Seiten4 Ece R13 Iv-ISheikh Noor MohammadNoch keine Bewertungen

- Obul Reddy - EditDokument25 SeitenObul Reddy - EditSheikh Noor MohammadNoch keine Bewertungen

- Paired RegionsDokument12 SeitenPaired RegionsSheikh Noor MohammadNoch keine Bewertungen

- 8086 Processor InterruptsDokument5 Seiten8086 Processor InterruptsSheikh Noor MohammadNoch keine Bewertungen

- 1 Darlington Pair AmplifierDokument2 Seiten1 Darlington Pair AmplifierSheikh Noor MohammadNoch keine Bewertungen

- Shadow Detection and Removal in Single-Image Using Paired RegionsDokument8 SeitenShadow Detection and Removal in Single-Image Using Paired RegionsEditor IJRITCCNoch keine Bewertungen

- Vector Calculus - Corral PDFDokument222 SeitenVector Calculus - Corral PDFMartin Martin MartinNoch keine Bewertungen

- Ec: Electronics and Communication Engineering: Duration: Three HoursDokument24 SeitenEc: Electronics and Communication Engineering: Duration: Three HoursSheikh Noor MohammadNoch keine Bewertungen

- 9a04306-Digital Logic DesignDokument1 Seite9a04306-Digital Logic DesignSheikh Noor MohammadNoch keine Bewertungen

- GSM-based train fire accidents detection and prevention systemDokument27 SeitenGSM-based train fire accidents detection and prevention systemSheikh Noor MohammadNoch keine Bewertungen

- ObulDokument118 SeitenObulSheikh Noor MohammadNoch keine Bewertungen

- Vector Calculus - Corral PDFDokument222 SeitenVector Calculus - Corral PDFMartin Martin MartinNoch keine Bewertungen

- Jntua CSE R13 SyllabusDokument132 SeitenJntua CSE R13 SyllabusSheikh Noor MohammadNoch keine Bewertungen

- JNTUA ECE Course StructureDokument16 SeitenJNTUA ECE Course StructureNaveen YallapuNoch keine Bewertungen

- Content Addressable MemoryDokument2 SeitenContent Addressable MemorySheikh Noor MohammadNoch keine Bewertungen

- Content Addressable MemoryDokument2 SeitenContent Addressable MemorySheikh Noor MohammadNoch keine Bewertungen

- Microprocessors Unit IIDokument47 SeitenMicroprocessors Unit IISheikh Noor MohammadNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- ST Katalog PDFDokument10 SeitenST Katalog PDFAleksandar GrujićNoch keine Bewertungen

- BOQ - Jay Jay Avissawella C8 (COM ROOM)Dokument1 SeiteBOQ - Jay Jay Avissawella C8 (COM ROOM)Isuru PrabodaNoch keine Bewertungen

- Ia q0 Las 1 Epas 7 8 FinalDokument8 SeitenIa q0 Las 1 Epas 7 8 FinalJohn Joel RafaelNoch keine Bewertungen

- Current Transformer GuideDokument79 SeitenCurrent Transformer Guidesabill arasyid100% (1)

- Vemat-Slip Ring MotorsDokument16 SeitenVemat-Slip Ring MotorszoelfiantaNoch keine Bewertungen

- Telemecanique LC1F265 DatasheetDokument28 SeitenTelemecanique LC1F265 DatasheetRAUL ORTIZNoch keine Bewertungen

- EM730UserManual (V100)Dokument345 SeitenEM730UserManual (V100)Salman SakibNoch keine Bewertungen

- Material List PDFDokument2 SeitenMaterial List PDFPower RoboticsNoch keine Bewertungen

- V04 - C03 - Andina Ball Mill Op Manual - 3BHS235454 - EN - Rev - CertDokument115 SeitenV04 - C03 - Andina Ball Mill Op Manual - 3BHS235454 - EN - Rev - CertJuan100% (1)

- Arc Lighter Tutorial Plasma Flyback Transformer Cold Neon Tube LCD High Voltage 2Dokument1 SeiteArc Lighter Tutorial Plasma Flyback Transformer Cold Neon Tube LCD High Voltage 2Martin AmaranteNoch keine Bewertungen

- Henry 2K-3 RF Linear AmplifierDokument27 SeitenHenry 2K-3 RF Linear Amplifierw9fe100% (1)

- NKC 2012300.12 O-ring connectors specificationsDokument1 SeiteNKC 2012300.12 O-ring connectors specificationsNguyễn Quang HuyNoch keine Bewertungen

- 1234345345Dokument11 Seiten1234345345Quảng Thành NamNoch keine Bewertungen

- Center Break DISC FlyerDokument2 SeitenCenter Break DISC FlyerHan HuangNoch keine Bewertungen

- Ceramic CapacitorDokument8 SeitenCeramic CapacitorparapNoch keine Bewertungen

- 1.2Mhz Low-Cost, High-Performance Chargers: General Description FeaturesDokument24 Seiten1.2Mhz Low-Cost, High-Performance Chargers: General Description FeaturesGioVoTamNoch keine Bewertungen

- LM MCCB BrohureDokument20 SeitenLM MCCB BrohureMunavwar ProfessNoch keine Bewertungen

- Lynch MotorDokument1 SeiteLynch MotorJustin SimNoch keine Bewertungen

- Umidificator PDFDokument3 SeitenUmidificator PDFPC MediaPointNoch keine Bewertungen

- Ecu Pinout Dodge NeonDokument9 SeitenEcu Pinout Dodge NeonAmir Arceo CruzNoch keine Bewertungen

- 5824 3181 PDFDokument2 Seiten5824 3181 PDFMuhammad AliNoch keine Bewertungen

- Maxon EC-Max16 5wattDokument1 SeiteMaxon EC-Max16 5wattElectromateNoch keine Bewertungen

- Course OverviewDokument12 SeitenCourse OverviewBhakti MatsyapalNoch keine Bewertungen

- Physics Investigatory Project HesDokument21 SeitenPhysics Investigatory Project HesBk ShreyaNoch keine Bewertungen

- Lab Report IV Characteristics of DiodeDokument5 SeitenLab Report IV Characteristics of DiodeAamir AliNoch keine Bewertungen

- CB Rating NumericalDokument4 SeitenCB Rating NumericalSanjay Agrawal100% (2)

- 998 20845418 EectricalDistribution GMA Catalogue2021 A DE3-NancyEW p81-131 enDokument51 Seiten998 20845418 EectricalDistribution GMA Catalogue2021 A DE3-NancyEW p81-131 entcNoch keine Bewertungen

- EPC bid document electrical equipment price summaryDokument64 SeitenEPC bid document electrical equipment price summaryVimal Singh0% (1)

- Quotation CT PT VCB SF6 HT Panel Isolator DO Fuse Set AB Switch Horn Gap Transmission LineDokument11 SeitenQuotation CT PT VCB SF6 HT Panel Isolator DO Fuse Set AB Switch Horn Gap Transmission LineShokautNoch keine Bewertungen

- Electrical TechnologyDokument8 SeitenElectrical TechnologySuperhypoNoch keine Bewertungen