Beruflich Dokumente

Kultur Dokumente

2:1 Differential-to-LVPECL Multiplexer: Datasheet

Hochgeladen von

Joshua D'CruzOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

2:1 Differential-to-LVPECL Multiplexer: Datasheet

Hochgeladen von

Joshua D'CruzCopyright:

Verfügbare Formate

2:1 Differential-to-LVPECL Multiplexer 853S01

Datasheet

General Description Features

The 853S01 is a high performance 2:1 Differential-to-LVPECL One LVPECL output pair

Multiplexer. The 853S01 can also perform differential translation Two selectable differential LVPECL clock inputs

because the differential inputs accept LVPECL, LVDS and CML

levels. The 853S01 is packaged in a small 3mm x 3mm 16 VFQFN

PCLKx, nPCLKx pairs can accept the following

differential input levels: LVPECL, LVDS, CML

package, making it ideal for use on space constrained boards.

Translates LVCMOS/LVTTL input signals to LVPECL levels by

using a resistor bias network on nPCLKx, nPCLKx

Part-to-part skew: 150ps (maximum)

Propagation delay: 490ps (maximum)

Full 3.3V or 2.5V operating supply

-40C to 85C ambient operating temperature

Available in lead-free (RoHS 6) packages

Block Diagram Pin Assignments

VCC

VEE

VEE

PCLK0 Pulldown

nc

0

nPCLK0 Pullup/Pulldown Q

16 15 14 13

nQ PCLK0 1 12 VEE

PCLK1 Pulldown

Pullup/Pulldown 1 nPCLK0 2 11 Q

nPCLK1

PCLK1 3 10 nQ

CLK_SEL Pulldown nPCLK1 4 9 VEE

5 6 7 8

VBB

CLK_SEL

VCC

nc

VBB

ICS853S01I

16-Lead VFQFN

3mm x 3mm x 0.925mm package body

K Package

Top View

PCLK0 1 16 nc

nPCLK0 2 15 VEE

PCLK1 3 14 VEE

nPCLK1 4 13 VCC

VBB 5 12 VEE

CLK_SEL 6 11 Q

nc 7 10 nQ

VCC 8 9 VEE

853S01

16-Lead TSSOP

4.4mm x 5.0mm x 0.925mm package body

G Package

Top View

2016 Integrated Device Technology, Inc. 1 Revision B, March 4, 2016

853S01 Datasheet

Table 1. Pin Descriptions

Number Name Type Description

1 PCLK0 Input Pulldown Non-inverting differential LVPECL clock input.

Pullup/

2 nPCLK0 Input Inverting differential LVPECL clock input. VCC/2 default when left floating.

Pulldown

3 PCLK1 Input Pulldown Non-inverting differential LVPECL clock input.

Pullup/

4 nPCLK1 Input Inverting differential LVPECL clock input. VCC/2 default when left floating.

Pulldown

5 VBB Output Bias voltage.

Clock select input. When HIGH, selects PCLK1, nPCLK1 inputs. When

6 CLK_SEL Input Pulldown

LOW, selects PCLK0, nPCLK0 inputs. LVCMOS/LVTTL interface levels.

7, 16 nc Unused No connect.

8, 13 VCC Power Positive supply pins.

9, 12, 14, 15 VEE Power Negative supply pins.

10, 11 nQ, Q Output Differential output pair. LVPECL interface levels.

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

Table 2. Pin Characteristics

Symbol Parameter Test Conditions Minimum Typical Maximum Units

CIN Input Capacitance 2 pF

RPULLDOWN Input Pulldown Resistor 37 k

RPULLUP Input Pullup Resistor 37 k

Function Tables

Table 3. Control Input Function Table

CLK_SEL Input Selected

0 PCLK0, nPCLK0

1 PCLK1, nPCLK1

2016 Integrated Device Technology, Inc. 2 Revision B, March 4, 2016

853S01 Datasheet

Absolute Maximum Ratings

NOTE: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond

those listed in the DC Characteristics or AC Characteristics is not implied. Exposure to absolute maximum rating conditions for

extended periods may affect product reliability.

Item Rating

Supply Voltage, VCC 4.6V

Inputs, VI -0.5V to VCC + 0.5V

Outputs, IO

Continuous Current 50mA

Surge Current 100mA

VBB Sink/Source, IBB 0.5mA

Package Thermal Impedance, JA

16 VFQFN 74.7C/W (0 mps)

16 TSSOP 100C/W (0 mps)

Storage Temperature, TSTG -65C to 150C

DC Electrical Characteristics

Table 4A. Power Supply DC Characteristics, VCC = 3.3V5%; VEE = 0V, TA = -40C to 85C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

VCC Positive Supply Voltage 3.135 3.3 3.465 V

IEE Power Supply Current 26 mA

Table 4B. Power Supply DC Characteristics, VCC = 2.5V5%; VEE = 0V, TA = -40C to 85C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

VCC Positive Supply Voltage 2.375 2.5 2.625 V

IEE Power Supply Current 24 mA

Table 4C. LVCMOS/LVTTL DC Characteristics, VCC = 3.3V5% or 2.5V5%; VEE = 0V, TA = -40C to 85C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

VCC = 3.3V 2.2 VCC + 0.3 V

VIH Input High Voltage

VCC = 2.5V 1.7 VCC + 0.3 V

VCC = 3.3V -0.3 0.8 V

VIL Input Low Voltage

VCC = 2.5V -0.3 0.7 V

Input High

IIH CLK_SEL VCC = VIN = 3.465V or 2.625V 150 A

Current

Input Low

IIL CLK_SEL VCC = 3.465V or 2.625V, VIN = 0V -10 A

Current

2016 Integrated Device Technology, Inc. 3 Revision B, March 4, 2016

853S01 Datasheet

Table 4D. LVPECL DC Characteristics, VCC = 3.3V5%; VEE = 0V, TA = -40C to 85C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

PCLK0, PCLK1,

IIH Input High Current VCC = VIN = 3.465V 150 A

nPCLK0, nPCLK1

PCLK0, PCLK1 VCC = 3.465V, VIN = 0V -10 A

IIL Input Low Current

nPCLK0, nPCLK1 VCC = 3.465V, VIN = 0V -150 A

Peak-to-Peak Voltage;

VPP 150 1200 mV

NOTE 1

Common Mode Input Voltage;

VCMR 1.2 VCC V

NOTE 1, 2

Output High Voltage;

VOH VCC 1.125 VCC 0.875 V

NOTE 3

Output Low Voltage;

VOL VCC 1.895 VCC 1.62 V

NOTE 3

VSWING Peak-to-Peak Output Voltage Swing 0.495 0.975 V

VBB Bias Voltage 1.695 2.145 V

NOTE 1: VIL should not be less than VEE 0.3V.

NOTE 2: Common mode input voltage is defined as VIH.

NOTE 3: Outputs terminated with 50 to VCC 2V.

Table 4E. LVPECL DC Characteristics, VCC = 2.5V5%; VEE = 0V, TA = -40C to 85C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

PCLK0, PCLK1,

IIH Input High Current VCC = VIN = 2.625V 150 A

nPCLK0, nPCLK1

PCLK0, PCLK1 VCC = 2.625V, VIN = 0V -10 A

IIL Input Low Current

nPCLK0, nPCLK1 VCC = 2.625V, VIN = 0V -150 A

Peak-to-Peak Voltage;

VPP 150 1200 mV

NOTE 1

Common Mode Input Voltage; NOTE

VCMR 1.2 VCC V

1, 2

Output High Voltage;

VOH VCC 1.125 VCC 0.875 V

NOTE 3

Output Low Voltage;

VOL VCC 1.895 VCC 1.62 V

NOTE 3

VSWING Peak-to-Peak Output Voltage Swing 0.495 0.975 V

VBB Bias Voltage 0.935 1.305 V

NOTE 1: VIL should not be less than VEE 0.3V.

NOTE 2: Common mode input voltage is defined as VIH.

NOTE 3: Outputs terminated with 50 to VCC 2V.

2016 Integrated Device Technology, Inc. 4 Revision B, March 4, 2016

853S01 Datasheet

AC Electrical Characteristics

Table 5A. AC Characteristics, VCC = 3.3V5%; VEE = 0V, TA = -40C to 85C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

fOUT Output Frequency 2.5 GHz

tPD Propagation Delay; NOTE 1 240 490 ps

tsk(i) Input Skew 40 ps

tsk(pp) Part-to-Part Skew; NOTE 2, 3 150 ps

Buffer Additive Phase Jitter, RMS,

622MHz, Integration Range:

tjit refer to Additive Phase Jitter 0.024 ps

12kHz - 20MHz

section; NOTE 4

tR / tF Output Rise/ Fall Time 20% to 80% 100 240 ps

MUXISOL MUX Isolation; NOTE 5 OUT 622MHz 81 dB

NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is

mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium

has been reached under these conditions.

NOTE: All parameters measured at 1.0GHz unless otherwise noted.

NOTE 1: Measured from the differential input crossing point to the differential output crossing point.

NOTE 2: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 3: Defined as skew between outputs on different devices operating at the same supply voltage, same temperature, same frequency and

with equal load conditions at the same temperature. Using the same type of inputs on each device, the outputs are measured at the differential

cross points.

NOTE 4: Driving only one input clock.

NOTE 5: Q, nQ output measured differentially. See Parameter Measurement Information for MUX Isolation diagram

Table 5B. AC Characteristics, VCC = 2.5V5%; VEE = 0V, TA = -40C to 85C

Symbol Parameter Test Conditions Minimum Typical Maximum Units

fOUT Output Frequency 2.5 GHz

tPD Propagation Delay; NOTE 1 240 490 ps

tsk(i) Input Skew 40 ps

tsk(pp) Part-to-Part Skew; NOTE 2, 3 150 ps

Buffer Additive Phase Jitter, RMS,

622MHz, Integration Range:

tjit refer to Additive Phase Jitter 0.024 ps

12kHz - 20MHz

section; NOTE 4

tR / tF Output Rise/ Fall Time 20% to 80% 100 240 ps

MUXISOL MUX Isolation; NOTE 5 OUT 622MHz 81 dB

NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is

mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium

has been reached under these conditions.

NOTE: All parameters measured at 1.0GHz unless otherwise noted.

NOTE 1: Measured from the differential input crossing point to the differential output crossing point.

NOTE 2: This parameter is defined in accordance with JEDEC Standard 65.

NOTE 3: Defined as skew between outputs on different devices operating at the same supply voltage, same temperature, same frequency and

with equal load conditions at the same temperature. Using the same type of inputs on each device, the outputs are measured at the differential

cross points.

NOTE 4: Driving only one input clock.

NOTE 5: Q, nQ output measured differentially. See Parameter Measurement Information for MUX Isolation diagram

2016 Integrated Device Technology, Inc. 5 Revision B, March 4, 2016

853S01 Datasheet

Additive Phase Jitter

The spectral purity in a band at a specific offset from the fundamental of the power in the 1Hz band to the power in the fundamental. When

compared to the power of the fundamental is called the dBc Phase the required offset is specified, the phase noise is called a dBc value,

Noise. This value is normally expressed using a Phase noise plot which simply means dBm at a specified offset from the fundamental.

and is most often the specified plot in many applications. Phase noise By investigating jitter in the frequency domain, we get a better

is defined as the ratio of the noise power present in a 1Hz band at a understanding of its effects on the desired application over the entire

specified offset from the fundamental frequency to the power value of time record of the signal. It is mathematically possible to calculate an

the fundamental. This ratio is expressed in decibels (dBm) or a ratio expected bit error rate given a phase noise plot.

Additive Phase Jitter @ 622MHz

12kHz to 20MHz = 0.024ps (typical)

SSB Phase Noise dBc/Hz

Offset from Carrier Frequency (Hz)

As with most timing specifications, phase noise measurements has The source generator used is, "IFR2042 10kHz 56.4GHz Low

issues relating to the limitations of the equipment. Often the noise Noise Signal Generator as external input to an Agilent 8133A 3GHz

floor of the equipment is higher than the noise floor of the device. This Pulse Generator".

is illustrated above. The device meets the noise floor of what is

shown, but can actually be lower. The phase noise is dependent on

the input source and measurement equipment.

2016 Integrated Device Technology, Inc. 6 Revision B, March 4, 2016

853S01 Datasheet

Parameter Measurement Information

2V

2V

SCOPE SCOPE

VCC Q

VCC Q

LVPECL LVPECL

nQ

nQ

VEE

VEE

-1.3V to 0.165V

-0.5V to 0.125V

3.3V LVPECL Output Load AC Test Circuit 2.5V LVPECL Output Load AC Test Circuit

nPCLK0

PCLK0

VCC

nPCLK1

PCLK1

nPCLKx

V Cross Points V nQ

PP CMR

PCLKx

Q

tPD2

VEE tPD1

tsk(i)

tsk(i) = |tPD1 - tPD2|

Differential Input Level Input Skew

Par t 1

nQ nPCLKx

Q PCLKx

Par t 2 nQ

nQ

Q

Q

tsk(pp) tPD

Part-to-Part Skew Propagation Delay

2016 Integrated Device Technology, Inc. 7 Revision B, March 4, 2016

853S01 Datasheet

Parameter Measurement Information, continued

Spectrum of Output Signal Q

A0 MUX selects active

input clock signal

Amplitude (dB)

nQ

MUX_ISOL = A0 A1

A1 MUX selects static input Q

Frequency

(fundamental)

MUX Isolation Output Rise/Fall Time

2016 Integrated Device Technology, Inc. 8 Revision B, March 4, 2016

853S01 Datasheet

Applications Information

Wiring the Differential Input to Accept Single-Ended Levels

Figure 1A shows how a differential input can be wired to accept single line impedance. For most 50 applications, R3 and R4 can be 100.

ended levels. The reference voltage VREF = VCC/2 is generated by The values of the resistors can be increased to reduce the loading for

the bias resistors R1 and R2. The bypass capacitor (C1) is used to slower and weaker LVCMOS driver. When using single-ended

help filter noise on the DC bias. This bias circuit should be located as signaling, the noise rejection benefits of differential signaling are

close to the input pin as possible. The ratio of R1 and R2 might need reduced. Even though the differential input can handle full rail

to be adjusted to position the VREF in the center of the input voltage LVCMOS signaling, it is recommended that the amplitude be

swing. For example, if the input clock swing is 2.5V and VCC = 3.3V, reduced. The datasheet specifies a lower differential amplitude,

R1 and R2 value should be adjusted to set VREF at 1.25V. The values however this only applies to differential signals. For single-ended

below are for when both the single ended swing and VCC are at the applications, the swing can be larger, however VIL cannot be less

same voltage. This configuration requires that the sum of the output than -0.3V and VIH cannot be more than VCC + 0.3V. Though some

impedance of the driver (Ro) and the series resistance (Rs) equals of the recommended components might not be used, the pads

the transmission line impedance. In addition, matched termination at should be placed in the layout. They can be utilized for debugging

the input will attenuate the signal in half. This can be done in one of purposes. The datasheet specifications are characterized and

two ways. First, R3 and R4 in parallel should equal the transmission guaranteed by using a differential signal.

Figure 1A. Recommended Schematic for Wiring a Differential Input to Accept Single-ended Levels

Wiring the Differential Input to Accept

Single-ended LVPECL Levels VCC

Figure 1B shows an example of the differential input that can be wired

to accept single-ended LVPECL levels. The reference voltage level

VBB generated from the device is connected to the negative input. C1

The C1 capacitor should be located as close as possible to the input 0.1uF

pin.

CLK_IN

PCLK

VBB

nPCLK

Figure 1B. Single-Ended LVPECL Signal Driving

Differential Input

2016 Integrated Device Technology, Inc. 9 Revision B, March 4, 2016

853S01 Datasheet

LVPECL Clock Input Interface (3.3V)

The PCLK/nPCLK accepts LVPECL, LVDS and other differential input interfaces suggested here are examples only. If the driver is

signals. Both VSWING and VOH must meet the VPP and VCMR input from another vendor, use their termination recommendation. Please

requirements. Figures 2A to 2C show interface examples for the consult with the vendor of the driver component to confirm the driver

PCLK/nPCLK input driven by the most common driver types. The termination requirements.

3.3V

3.3V

3.3V

R3 R4

125 125

Zo = 50

PCLK

Zo = 50

nPCLK

LVPECL LVPECL

Input

R1 R2

84 84

Figure 2A. PCLK/nPCLK Input Driven by a 3.3V LVPECL Figure 2B. PCLK/nPCLK Input Driven by a 3.3V LVPECL

Driver Driver with AC Couple

3.3V

3.3V 3.3V

3.3V Zo = 50

Zo = 50

PCLK PCLK

R1

100 R1

100

nPCLK

Zo = 50 nPCLK

LVPECL Zo = 50

LVDS CML Built-In Pullup LVPECL

Input

Input

Figure 2C. PCLK/nPCLK Input Driven by a 3.3V LVDS Figure 2D. PCLK/nPCLK Input Driven by a

Driver Built-In Pullup CML Driver

3.3V

3.3V

3.3V R1 R2

50 50

Zo = 50

PCLK

Zo = 50

nPCLK

CML LVPECL

Input

Figure 2E. PCLK/nPCLK Input Driven by a CML Driver

2016 Integrated Device Technology, Inc. 10 Revision B, March 4, 2016

853S01 Datasheet

LVPECL Clock Input Interface (2.5V)

The PCLK /nPCLK accepts LVPECL, LVDS and other differential input interfaces suggested here are examples only. If the driver is

signals. The differential signal must meet the VPP and VCMR input from another vendor, use their termination recommendation. Please

requirements. Figures 3A to 3C show interface examples for the consult with the vendor of the driver component to confirm the driver

PCLK/nPCLK input driven by the most common driver types. The termination requirements.

PCLK

nPCLK

Figure 3A. PCLK/nPCLK Input Driven by a 2.5V LVDS Figure 3B. PCLK/nPCLK Input Driven by a 3.3V LVPECL

Driver Driver with AC Couple

PCLK

nPCLK

Figure 3C. PCLK/nPCLK Input Driven by a 2.5V LVPECL

Driver

2016 Integrated Device Technology, Inc. 11 Revision B, March 4, 2016

853S01 Datasheet

Recommendations for Unused Input Pins

Inputs:

PCLK/nPCLK Inputs

For applications not requiring the use of a differential input, both the

PCLK and nPCLK pins can be left floating. Though not required, but

for additional protection, a 1k resistor can be tied from PCLK to

ground. For applications

Termination for 3.3V LVPECL Outputs

The clock layout topology shown below is a typical termination for transmission lines. Matched impedance techniques should be used

LVPECL outputs. The two different layouts mentioned are to maximize operating frequency and minimize signal distortion.

recommended only as guidelines. Figures 4A and 4B show two different layouts which are

recommended only as guidelines. Other suitable clock layouts may

The differential output pair is low impedance follower output that exist and it would be recommended that the board designers

generate ECL/LVPECL compatible outputs. Therefore, terminating simulate to guarantee compatibility across all printed circuit and clock

resistors (DC current path to ground) or current sources must be component process variations.

used for functionality. These outputs are designed to drive 50

3.3V

R3 R4

125 125

3.3V

3.3V

Zo = 50

+

_

Input

Zo = 50

R1 R2

84 84

Figure 4A. 3.3V LVPECL Output Termination Figure 4B. 3.3V LVPECL Output Termination

2016 Integrated Device Technology, Inc. 12 Revision B, March 4, 2016

853S01 Datasheet

Termination for 2.5V LVPECL Outputs

Figure 5A and Figure 5B show examples of termination for 2.5V level. The R3 in Figure 5B can be eliminated and the termination is

LVPECL driver. These terminations are equivalent to terminating 50 shown in Figure 5C.

to VCC 2V. For VCC = 2.5V, the VCC 2V is very close to ground

2.5V

VCC = 2.5V

2.5V

2.5V

VCC = 2.5V

R1 R3 50

250 250

+

50

+ 50

50

2.5V LVPECL Driver

R1 R2

2.5V LVPECL Driver 50 50

R2 R4

62.5 62.5

R3

18

Figure 5A. 2.5V LVPECL Driver Termination Example Figure 5B. 2.5V LVPECL Driver Termination Example

2.5V

VCC = 2.5V

50

+

50

2.5V LVPECL Driver

R1 R2

50 50

Figure 5C. 2.5V LVPECL Driver Termination Example

2016 Integrated Device Technology, Inc. 13 Revision B, March 4, 2016

853S01 Datasheet

VFQFN EPAD Thermal Release Path

In order to maximize both the removal of heat from the package and and dependent upon the package power dissipation as well as

the electrical performance, a land pattern must be incorporated on electrical conductivity requirements. Thus, thermal and electrical

the Printed Circuit Board (PCB) within the footprint of the package analysis and/or testing are recommended to determine the minimum

corresponding to the exposed metal pad or exposed heat slug on the number needed. Maximum thermal and electrical performance is

package, as shown in Figure 6. The solderable area on the PCB, as achieved when an array of vias is incorporated in the land pattern. It

defined by the solder mask, should be at least the same size/shape is recommended to use as many vias connected to ground as

as the exposed pad/slug area on the package to maximize the possible. It is also recommended that the via diameter should be 12

thermal/electrical performance. Sufficient clearance should be to 13mils (0.30 to 0.33mm) with 1oz copper via barrel plating. This is

designed on the PCB between the outer edges of the land pattern desirable to avoid any solder wicking inside the via during the

and the inner edges of pad pattern for the leads to avoid any shorts. soldering process which may result in voids in solder between the

exposed pad/slug and the thermal land. Precautions should be taken

While the land pattern on the PCB provides a means of heat transfer to eliminate any solder voids between the exposed heat slug and the

and electrical grounding from the package to the board through a land pattern. Note: These recommendations are to be used as a

solder joint, thermal vias are necessary to effectively conduct from guideline only. For further information, please refer to the Application

the surface of the PCB to the ground plane(s). The land pattern must Note on the Surface Mount Assembly of Amkors Thermally/

be connected to ground through these vias. The vias act as heat Electrically Enhance Leadframe Base Package, Amkor Technology.

pipes. The number of vias (i.e. heat pipes) are application specific

SOLDER SOLDER

PIN EXPOSED HEAT SLUG PIN

PIN PAD GROUND PLANE LAND PATTERN PIN PAD

THERMAL VIA (GROUND PAD)

Figure 6. P.C. Assembly for Exposed Pad Thermal Release Path Side View (drawing not to scale)

2016 Integrated Device Technology, Inc. 14 Revision B, March 4, 2016

853S01 Datasheet

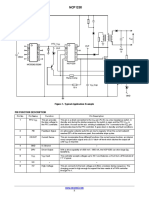

Schematic Example

Figure 7 shows an example of 853S01 application schematic. This input is driven by a LVPECL driver. The decoupling capacitor should

device can accept different types of input signal. In this example, the be located as close as possible to the power pin.

Figure 7. 853S01 Applications Schematic Example

2016 Integrated Device Technology, Inc. 15 Revision B, March 4, 2016

853S01 Datasheet

Power Considerations

This section provides information on power dissipation and junction temperature for the 853S01.

Equations and example calculations are also provided.

1. Power Dissipation.

The total power dissipation for the 853S01 is the sum of the core power plus the power dissipation in the load(s).

The following is the power dissipation for VCC = 3.3V + 5% = 3.465V, which gives worst case results.

NOTE: Please refer to Section 3 for details on calculating power dissipation in the load.

Power (core)MAX = VCC_MAX * IEE_MAX = 3.465V * 26mA = 90.09mW

Power (outputs)MAX = 32mW/Loaded Output pair

Total Power_MAX (3.3V, with all outputs switching) = 90.09mW + 32mW = 122.09mW

2. Junction Temperature.

Junction temperature, Tj, is the temperature at the junction of the bond wire and bond pad directly affects the reliability of the device. The

maximum recommended junction temperature is 125C. Limiting the internal transistor junction temperature, Tj, to 125C ensures that the bond

wire and bond pad temperature remains below 125C.

The equation for Tj is as follows: Tj = JA * Pd_total + TA

Tj = Junction Temperature

JA = Junction-to-Ambient Thermal Resistance

Pd_total = Total Device Power Dissipation (example calculation is in section 1 above)

TA = Ambient Temperature

In order to calculate junction temperature, the appropriate junction-to-ambient thermal resistance JA must be used. Assuming no air flow and

a multi-layer board, the appropriate value is 100C/W per Table 6A below.

Therefore, Tj for an ambient temperature of 85C with all outputs switching is:

85C + 0.122W * 100C/W = 97.2C. This is below the limit of 125C.

This calculation is only an example. Tj will obviously vary depending on the number of loaded outputs, supply voltage, air flow and the type of

board (multi-layer).

Table 6A. Thermal Resistance JA for 16 Lead TSSOP, Forced Convection

JA by Velocity

Meters per Second 0 1 2.5

Multi-Layer PCB, JEDEC Standard Test Boards 100.0C/W 94.2C/W 90.2C/W

Table 6B. Thermal Resistance JA for 16 Lead VFQFN, Forced Convection

JA by Velocity

Meters per Second 0 1 2.5

Multi-Layer PCB, JEDEC Standard Test Boards 74.7C/W 65.3C/W 58.5C/W

2016 Integrated Device Technology, Inc. 16 Revision B, March 4, 2016

853S01 Datasheet

3. Calculations and Equations.

The purpose of this section is to calculate the power dissipation for the LVPECL output pair.

The LVPECL output driver circuit and termination are shown in Figure 8.

VCC

Q1

VOUT

RL

50

VCC - 2V

Figure 8. LVPECL Driver Circuit and Termination

To calculate worst case power dissipation into the load, use the following equations which assume a 50 load, and a termination voltage of

VCC 2V.

For logic high, VOUT = VOH_MAX = VCC_MAX 0.875V

(VCC_MAX VOH_MAX) = 0.875V

For logic low, VOUT = VOL_MAX = VCC_MAX 1.62V

(VCC_MAX VOL_MAX) = 1.62V

Pd_H is power dissipation when the output drives high.

Pd_L is the power dissipation when the output drives low.

Pd_H = [(VOH_MAX (VCC_MAX 2V))/RL] * (VCC_MAX VOH_MAX) = [(2V (VCC_MAX VOH_MAX))/RL] * (VCC_MAX VOH_MAX) =

[(2V 0.875V)/50] * 0.875V = 19.691mW

Pd_L = [(VOL_MAX (VCC_MAX 2V))/RL] * (VCC_MAX VOL_MAX) = [(2V (VCC_MAX VOL_MAX))/RL] * (VCC_MAX VOL_MAX) =

[(2V 1.62V)/50] * 1.62V = 12.31mW

Total Power Dissipation per output pair = Pd_H + Pd_L = 32mW

2016 Integrated Device Technology, Inc. 17 Revision B, March 4, 2016

853S01 Datasheet

Reliability Information

Table 7A. JA vs. Air Flow Table for a 16 Lead VFQFN

JA by Velocity

Meters per Second 0 1 2.5

Multi-Layer PCB, JEDEC Standard Test Boards 74.7C/W 65.3C/W 58.5C/W

Table 7B. JA vs. Air Flow Table for an 16 Lead TSSOP Forced Convection

JA by Velocity

Meters per Second 0 1 2.5

Multi-Layer PCB, JEDEC Standard Test Boards 100.0C/W 94.2C/W 90.2C/W

Transistor Count

The transistor count for 853S01 is: 244

This device is pin and function compatible and a suggested replacement for ICS85301.

2016 Integrated Device Technology, Inc. 18 Revision B, March 4, 2016

853S01 Datasheet

Package Outline and Package Dimensions

Package Outline - G Suffix for 16 Lead TSSOP

Table 8A. Package Dimensions

All Dimensions in Millimeters

Symbol Minimum Maximum

N 16

A 1.20

A1 0.05 0.15

A2 0.80 1.05

b 0.19 0.30

c 0.09 0.20

D 4.90 5.10

E 6.40 Basic

E1 4.30 4.50

e 0.65 Basic

L 0.45 0.75

0 8

aaa 0.10

Reference Document: JEDEC Publication 95, MO-153

2016 Integrated Device Technology, Inc. 19 Revision B, March 4, 2016

853S01 Datasheet

Package Outline - K Suffix for 16 Lead VFQFN

Seating Plane (Ref.)

(ND-1)x e ND & NE

(R ef.) Even

Index Area A1

A3 L

N N e (Typ.)

2 If ND & NE

Anvil 1 are Even

Singulation 2

or E2 (NE -1)x e

E2 (Re f.)

Sawn

2

Top View Singulation

b

e Thermal

A (Ref.)

D D2 Base

ND & NE

2

Odd

Chamfer 4x 0. 08 C D2

0.6 x 0.6 max C

OPTIONAL

Bottom View w/Type A ID Bottom View w/Type C ID

2

2

1

1

CHAMFER RADIUS

4 N N-1 4 N N-1

There are 2 methods of indicating pin 1 corner at the back of the VFQFN package:

1. Type A: Chamfer on the paddle (near pin 1)

2. Type C: Mouse bite on the paddle (near pin 1)

Table 8B. Package Dimensions

JEDEC Variation: VEED-2/-4

All Dimensions in Millimeters

Symbol Minimum Maximum

N 16

A 0.80 1.00

A1 0 0.05

A3 0.25 Ref.

b 0.18 0.30

ND & NE 4

D&E 3.00 Basic

D2 & E2 1.00 1.80

e 0.50 Basic

L 0.30 0.50

Reference Document: JEDEC Publication 95, MO-220

2016 Integrated Device Technology, Inc. 20 Revision B, March 4, 2016

853S01 Datasheet

Ordering Information

Table 9. Ordering Information

Part/Order Number Marking Package Shipping Packaging Temperature

853S01AGILF 53S01AIL Lead-Free 16 Lead TSSOP Tube -40C to 85C

853S01AGILFT 53S01AIL Lead-Free 16 Lead TSSOP Tape & Reel -40C to 85C

853S01AKILF 3S1A Lead-Free 16 Lead VFQFN Tube -40C to 85C

853S01AKILFT 3S1A Lead-Free 16 Lead VFQFN Tape & Reel -40C to 85C

2016 Integrated Device Technology, Inc. 21 Revision B, March 4, 2016

853S01 Datasheet

Revision History Sheet

Rev Table Page Description of Change Date

9 Updated Wiring the Differential Inputs to Accept Single-ended Levels section.

A Updated the 32 VFQFN Bottom View Package Drawing. 11/23/10

20

1 Deleted HiperClockS Logo. Updated GD paragraph to include CML.

Added CML to 3rd bullet.

A 10/29/12

10 Added figures 2D and 2E.

T9 21 Deleted quantity from tape and reel.

Deleted part numbers I prefix throughout the datasheet.

B 2/9/16

Updated datasheet header/footer.

T9 21 Ordering Information- Deleted LF note below table.

B 3/4/16

Corrected Data Sheet header from 12:1 to 2:1.

2016 Integrated Device Technology, Inc. 22 Revision B, March 4, 2016

Corporate Headquarters Sales Tech Support

6024 Silver Creek Valley Road 1-800-345-7015 or 408-284-8200 email: clocks@idt.com

San Jose, CA 95138 USA Fax: 408-284-2775

www.IDT.com

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDTs sole discretion. All information in

this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined

in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether

express or implied, including, but not limited to, the suitability of IDTs products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This

document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDTs products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably

expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology (IDT) assumes no responsibility for either its use or for the infringement of any patents or

other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications, such as

those requiring extended temperature ranges, high reliability or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any

circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Product specification subject to change without notice. Other trademarks and service marks used herein, including protected

names, logos and designs, are the property of IDT or their respective third party owners.

Copyright 2016 Integrated Device Technology, Inc. All rights reserved.

Das könnte Ihnen auch gefallen

- 21bec0499 VL2023240100568 Ast05Dokument4 Seiten21bec0499 VL2023240100568 Ast05Om PotdarNoch keine Bewertungen

- Osciladores de 8 PinesDokument4 SeitenOsciladores de 8 PinesCarlos Reyes RiveraNoch keine Bewertungen

- Max17120 PDFDokument14 SeitenMax17120 PDFAaruran MugunthanNoch keine Bewertungen

- Dual High-Voltage Scan Drivers For TFT LCD: General Description FeaturesDokument14 SeitenDual High-Voltage Scan Drivers For TFT LCD: General Description FeaturesShaileshNoch keine Bewertungen

- MAX17120ETJDokument16 SeitenMAX17120ETJGeovanny SanJuanNoch keine Bewertungen

- Caded Assignment FinalDokument21 SeitenCaded Assignment FinalSiddesh Sanju100% (2)

- SN 74 LV 4040 ADokument23 SeitenSN 74 LV 4040 AmylitalindaNoch keine Bewertungen

- Lv595a PDFDokument22 SeitenLv595a PDFmarpre1983Noch keine Bewertungen

- PC-Interface: I2C - PC: J. WeissDokument3 SeitenPC-Interface: I2C - PC: J. WeissLes Bois FlottésNoch keine Bewertungen

- ECE524: Transient RC Response: Analytical SolutionDokument5 SeitenECE524: Transient RC Response: Analytical SolutionAtiq_2909Noch keine Bewertungen

- Ba 6110Dokument7 SeitenBa 6110John WoeNoch keine Bewertungen

- CXA1646Q/CXA1767Q: Electronic VolumeDokument21 SeitenCXA1646Q/CXA1767Q: Electronic VolumeED LiNoch keine Bewertungen

- 24V, High Current Synchronous Buck Converter With +/-1.5A LDO and Buffed ReferenceDokument21 Seiten24V, High Current Synchronous Buck Converter With +/-1.5A LDO and Buffed Reference8ctanoNoch keine Bewertungen

- Giga Luoc Do Kich NguonDokument2 SeitenGiga Luoc Do Kich NguonĐiện LươngNoch keine Bewertungen

- Giga Luoc Do Kich NguonDokument2 SeitenGiga Luoc Do Kich NguonNguyễn Văn TặngNoch keine Bewertungen

- Zero Delay, Differential-to-LVCMOS/ LVTTL Clock Generator: Not Recommended For New DesignsDokument18 SeitenZero Delay, Differential-to-LVCMOS/ LVTTL Clock Generator: Not Recommended For New DesignsELLVEE TECHNoch keine Bewertungen

- Upb1507gv NecDokument20 SeitenUpb1507gv Necfarid.hamraniNoch keine Bewertungen

- Semiconductor Technical Data: 100 at Frequency of OperationDokument11 SeitenSemiconductor Technical Data: 100 at Frequency of Operationsebastian nasiNoch keine Bewertungen

- STR6553 PDFDokument2 SeitenSTR6553 PDFCarlos Arturo Lopez TorresNoch keine Bewertungen

- An1060 Flyback Converters With The l6561 PFC Controller StmicroelectronicsDokument11 SeitenAn1060 Flyback Converters With The l6561 PFC Controller StmicroelectronicsALAIN GOUDEAUNoch keine Bewertungen

- BS616LV1016: Very Low Power/Voltage CMOS SRAM 64K X 16 BitDokument9 SeitenBS616LV1016: Very Low Power/Voltage CMOS SRAM 64K X 16 BitBuitinės Technikos RemontasNoch keine Bewertungen

- DatasheetDokument27 SeitenDatasheetСтанислав ИвановNoch keine Bewertungen

- D D D D D D D D: Description/ordering InformationDokument27 SeitenD D D D D D D D: Description/ordering InformationNelson BorgesNoch keine Bewertungen

- Data Sheet: Weltrend Semiconductor, IncDokument10 SeitenData Sheet: Weltrend Semiconductor, IncaadNoch keine Bewertungen

- General Description: Level Translating I C-Bus RepeaterDokument19 SeitenGeneral Description: Level Translating I C-Bus RepeatersreekanthNoch keine Bewertungen

- HA16129FPJ Datasheet 1Dokument24 SeitenHA16129FPJ Datasheet 1Dylan FlorezNoch keine Bewertungen

- Mc100Lvel92 5vtriple Pecl Input To Lvpecl Output Translator: DescriptionDokument6 SeitenMc100Lvel92 5vtriple Pecl Input To Lvpecl Output Translator: DescriptionPanagiotis PanagosNoch keine Bewertungen

- General Description: Dual Retriggerable Precision Monostable MultivibratorDokument17 SeitenGeneral Description: Dual Retriggerable Precision Monostable Multivibratorsajad hejaziNoch keine Bewertungen

- 74HC164Dokument8 Seiten74HC164api-3864578100% (1)

- Infineon-Design Guide Boost Type CCM PFC ICE3PCSxx-AN-v02 00-EN PDFDokument26 SeitenInfineon-Design Guide Boost Type CCM PFC ICE3PCSxx-AN-v02 00-EN PDFThai Anh NguyenNoch keine Bewertungen

- PLCC-28: Txcan MIL NC AN3-O2VDokument8 SeitenPLCC-28: Txcan MIL NC AN3-O2V肖磊Noch keine Bewertungen

- LM5030 Application: DC - DC Converter Utilizing The Push-Pull TopologyDokument10 SeitenLM5030 Application: DC - DC Converter Utilizing The Push-Pull TopologyEdoardoNoch keine Bewertungen

- Sana'a University Faculty of Engineering Electrical DeptDokument23 SeitenSana'a University Faculty of Engineering Electrical DeptAliasa ZaidNoch keine Bewertungen

- Low Voltage 1:15 Differential ECL/PECL Clock Divider and Fanout Buffer MC100ES6222Dokument12 SeitenLow Voltage 1:15 Differential ECL/PECL Clock Divider and Fanout Buffer MC100ES6222Panagiotis PanagosNoch keine Bewertungen

- U2741BDokument9 SeitenU2741BSlavko MitrovicNoch keine Bewertungen

- Control Cable TCP01 FOR CONTINUITYDokument23 SeitenControl Cable TCP01 FOR CONTINUITYFendi ahmadNoch keine Bewertungen

- ICL88xx Flyback Design Guide: DG - 2103 - PL39 - 2104 - 160011Dokument64 SeitenICL88xx Flyback Design Guide: DG - 2103 - PL39 - 2104 - 160011Michael WeirichNoch keine Bewertungen

- Practical Feedback Loop Design Considerations For Flyback Converter Using UCC28740Dokument7 SeitenPractical Feedback Loop Design Considerations For Flyback Converter Using UCC28740jay lowkeyNoch keine Bewertungen

- High-Performance Silicon-Gate CMOS: Semiconductor Technical DataDokument9 SeitenHigh-Performance Silicon-Gate CMOS: Semiconductor Technical DataSo Was RedNoch keine Bewertungen

- Classc Sim PDFDokument6 SeitenClassc Sim PDFmastelecentroNoch keine Bewertungen

- HEF4538BDokument14 SeitenHEF4538BAlireza RahimiNoch keine Bewertungen

- ¡ Semiconductor: MSC1162ADokument14 Seiten¡ Semiconductor: MSC1162AspotNoch keine Bewertungen

- Technical Information on AN-80000 Coin Payout Unit/TITLEDokument38 SeitenTechnical Information on AN-80000 Coin Payout Unit/TITLEpastilhasNoch keine Bewertungen

- 74LVC74ADokument19 Seiten74LVC74ALUIS SERRANONoch keine Bewertungen

- 74HC HCT123Dokument20 Seiten74HC HCT123Razak JeyNoch keine Bewertungen

- sn54hc109 Flip FlopDokument19 Seitensn54hc109 Flip FlopCarlos IbaNoch keine Bewertungen

- SSC3S931 Data Sheet: LLC Current-Resonant Off-Line Switching ControllerDokument23 SeitenSSC3S931 Data Sheet: LLC Current-Resonant Off-Line Switching ControllerytnateNoch keine Bewertungen

- MC10H161 Binary To 1 8 Decoder (Low) : DescriptionDokument7 SeitenMC10H161 Binary To 1 8 Decoder (Low) : DescriptionandrebuhlerNoch keine Bewertungen

- 74HC4538 74HCT4538: 1. General DescriptionDokument24 Seiten74HC4538 74HCT4538: 1. General DescriptionremikhaledNoch keine Bewertungen

- Atmel 9111 LIN Networking ATA6612C ATA6613C - Datasheet PDFDokument312 SeitenAtmel 9111 LIN Networking ATA6612C ATA6613C - Datasheet PDFAnkadi Sikari ReddyNoch keine Bewertungen

- 3-Channel Secondary Monitoring IC: Issue Date: File Name Total PagesDokument10 Seiten3-Channel Secondary Monitoring IC: Issue Date: File Name Total PagesRajendra ShettigarNoch keine Bewertungen

- Features Description: LTC7004 Fast 60V High Side NMOS Static Switch DriverDokument19 SeitenFeatures Description: LTC7004 Fast 60V High Side NMOS Static Switch DriverLim VanthienNoch keine Bewertungen

- Features: NC MIL Ain3 Ain2Dokument9 SeitenFeatures: NC MIL Ain3 Ain2肖磊Noch keine Bewertungen

- EEE 4604 Experiment 04Dokument4 SeitenEEE 4604 Experiment 04Tanzina kabir HiaNoch keine Bewertungen

- ¡ Semiconductor: MSM511666C/CLDokument16 Seiten¡ Semiconductor: MSM511666C/CLfloaffloaf72Noch keine Bewertungen

- Ren 84021 DST 20150923Dokument20 SeitenRen 84021 DST 20150923MOHSENNoch keine Bewertungen

- NCN5150 DDokument12 SeitenNCN5150 Dgoingforward77Noch keine Bewertungen

- WaoDokument1 SeiteWaoJoshua D'CruzNoch keine Bewertungen

- Low Light PhotographyDokument17 SeitenLow Light PhotographyGhanbari HadiNoch keine Bewertungen

- Broken OrcaView FileDokument1 SeiteBroken OrcaView FileJoshua D'CruzNoch keine Bewertungen

- Lecture Notes For Section 16-5Dokument20 SeitenLecture Notes For Section 16-5Joshua D'CruzNoch keine Bewertungen

- Route 301 Queen EBDokument1 SeiteRoute 301 Queen EBJoshua D'CruzNoch keine Bewertungen

- Lecture Notes For Sections 17-2-17-3Dokument21 SeitenLecture Notes For Sections 17-2-17-3Joshua D'CruzNoch keine Bewertungen

- Can Filter Selection Reduce HVAC Energy Costs?Dokument3 SeitenCan Filter Selection Reduce HVAC Energy Costs?Joshua D'CruzNoch keine Bewertungen

- Lecture Notes For Section 16-4Dokument15 SeitenLecture Notes For Section 16-4Joshua D'CruzNoch keine Bewertungen

- Lab Report Checklist: - Conclusion & EvaluationDokument2 SeitenLab Report Checklist: - Conclusion & EvaluationJoshua D'CruzNoch keine Bewertungen

- Lecture Notes For Sections 16-1-16-3Dokument25 SeitenLecture Notes For Sections 16-1-16-3Joshua D'CruzNoch keine Bewertungen

- Lecture Notes For Section 17-4Dokument16 SeitenLecture Notes For Section 17-4Joshua D'CruzNoch keine Bewertungen

- Lecture Notes For Section 17-5Dokument20 SeitenLecture Notes For Section 17-5Joshua D'CruzNoch keine Bewertungen

- Lecture Notes For Section 17-1Dokument20 SeitenLecture Notes For Section 17-1Joshua D'CruzNoch keine Bewertungen

- RELATIVE MOTION ANALYSIS: ACCELERATION COMPONENTSDokument25 SeitenRELATIVE MOTION ANALYSIS: ACCELERATION COMPONENTSJoshua D'CruzNoch keine Bewertungen

- Lecture Notes For Section 16-5Dokument20 SeitenLecture Notes For Section 16-5Joshua D'CruzNoch keine Bewertungen

- Lecture Notes For Section 16-6Dokument20 SeitenLecture Notes For Section 16-6Joshua D'CruzNoch keine Bewertungen

- Lecture Notes For Section 16-4Dokument15 SeitenLecture Notes For Section 16-4Joshua D'CruzNoch keine Bewertungen

- BJT Amplifiers Problems & SolutionsDokument14 SeitenBJT Amplifiers Problems & SolutionsThiện Nguyễn100% (5)

- HSPE-144M M6 HC Monofacial 450-460W Rev.00Dokument2 SeitenHSPE-144M M6 HC Monofacial 450-460W Rev.00Alejandro Holguin QuinteroNoch keine Bewertungen

- LweDokument2 SeitenLwesaintkhanNoch keine Bewertungen

- Current Electricity: Key ConceptsDokument19 SeitenCurrent Electricity: Key Concepts68 Kumuda MathapatiNoch keine Bewertungen

- EE2 Lecture 1Dokument44 SeitenEE2 Lecture 1woojoo666Noch keine Bewertungen

- Penguat BJTDokument44 SeitenPenguat BJTMarissa Tania TNoch keine Bewertungen

- Materials Chemistry B: Journal ofDokument32 SeitenMaterials Chemistry B: Journal ofpriyaNoch keine Bewertungen

- Multiple Choice Linear Electronics Circuits - 102409023651 - 1Dokument15 SeitenMultiple Choice Linear Electronics Circuits - 102409023651 - 1Ratheesh Rs50% (2)

- PID Issues in BI-FACIAL MODULESDokument17 SeitenPID Issues in BI-FACIAL MODULESAnjanareddy SettipalliNoch keine Bewertungen

- Yield AnalysisDokument16 SeitenYield AnalysisvpsampathNoch keine Bewertungen

- BNP c3016 (Eng) F PDFDokument442 SeitenBNP c3016 (Eng) F PDFzotya54Noch keine Bewertungen

- Atmel At89sxx IspDokument6 SeitenAtmel At89sxx IspkametocoNoch keine Bewertungen

- Testing A MOSFETDokument3 SeitenTesting A MOSFETttarwinNoch keine Bewertungen

- Investigatory Project On LDRDokument16 SeitenInvestigatory Project On LDRHarsh81% (26)

- Modern Semiconductor Devices For Integrated Circuits 1st Edition Hu Solutions ManualDokument19 SeitenModern Semiconductor Devices For Integrated Circuits 1st Edition Hu Solutions Manualorianahilaryic3u1s100% (21)

- Ceramics PPT CEMDokument37 SeitenCeramics PPT CEMskhanveNoch keine Bewertungen

- CSS Terminating and Connerting Electrical Wiring and Electronic CircuitsDokument19 SeitenCSS Terminating and Connerting Electrical Wiring and Electronic CircuitsRalfh Pescadero De GuzmanNoch keine Bewertungen

- sp3's Experience Using Hot Filament CVD Reactors To Grow Diamond For An Expanding Set of ApplicationsDokument11 Seitensp3's Experience Using Hot Filament CVD Reactors To Grow Diamond For An Expanding Set of Applicationskovah2kNoch keine Bewertungen

- Chemistry Corrected Material Unit 12-17Dokument55 SeitenChemistry Corrected Material Unit 12-17Pandu RockingNoch keine Bewertungen

- 74LS138 9Dokument7 Seiten74LS138 9RizulNoch keine Bewertungen

- SENB8604-02 Systems Operation GlossaryDokument41 SeitenSENB8604-02 Systems Operation GlossaryChristian BedoyaNoch keine Bewertungen

- Level MeasurementDokument59 SeitenLevel MeasurementsuhailfarhaanNoch keine Bewertungen

- Radio Servicing Made Easy Gernsback 1961 Vol 1Dokument182 SeitenRadio Servicing Made Easy Gernsback 1961 Vol 1Supr RayNoch keine Bewertungen

- CE BJT Configuration Parameters and EquationsDokument2 SeitenCE BJT Configuration Parameters and EquationsZeeshanMirzaNoch keine Bewertungen

- Inorganic Chemistry II (100 Items)Dokument11 SeitenInorganic Chemistry II (100 Items)maria jeusa matiasNoch keine Bewertungen

- Photon - Article LIDDokument6 SeitenPhoton - Article LIDBrahadeesh Perinkolam MuraliNoch keine Bewertungen

- Problem Statement:: Fig. 1: Zener Diode SymbolDokument10 SeitenProblem Statement:: Fig. 1: Zener Diode SymbolTalha JabbarNoch keine Bewertungen

- Business PlanDokument25 SeitenBusiness PlanMahesan SinthujanNoch keine Bewertungen

- MEMS (Micro Electromechanical Systems) Introduction - Sabanci University MEMS CourseDokument19 SeitenMEMS (Micro Electromechanical Systems) Introduction - Sabanci University MEMS CoursecmosNoch keine Bewertungen

- BP104 Data SheetsDokument5 SeitenBP104 Data SheetssegalignoNoch keine Bewertungen