Beruflich Dokumente

Kultur Dokumente

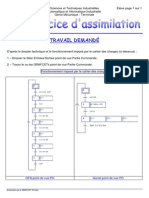

LogiqueSéquentielle Partie2

Hochgeladen von

Mehdi El AlaouiOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

LogiqueSéquentielle Partie2

Hochgeladen von

Mehdi El AlaouiCopyright:

Verfügbare Formate

LQTMY-Tanger M.

SALMANI

Logique squentielle : Partie 2

1. Compteurs

11. Gnralits

111. Dfinition

Un compteur est un circuit logique squentiel constitu dun ensemble de n bascules interconnectes par

des portes logiques. Il permet de dnombrer ou compter, suivant un systme de numration binaire,

le nombre dimpulsions appliques son entre horloge : il reoit les impulsions compter et dlivre en

permanence en sa sortie une combinaison, des tats logiques, image du nombre dimpulsions reues.

112. Classification des compteurs

En logique squentielle, les compteurs peuvent tre dcris en citant les caractristiques suivantes :

Sens de comptage : Evolution de la valeur de sortie dans le temps.

Comptage croissant ou ascendant Compteurs.

Comptage dcroissant ou descendant Dcompteurs.

Code de comptage : Code dans lequel est exprime la valeur de sortie.

Comptage en binaire naturel, en code Gray, en dcimal, etc.

Mode de comptage : Type de basculement asynchrone ou synchrone du compteur.

Compteurs asynchrones ou compteurs synchrones.

Modulo de comptage : Capacit du compteur exprimant le nombre dtats logiques diffrents que peut

prendre la valeur de sortie sur lensemble du cycle de comptage.

Un compteur modulo M compte de 0 (M-1) et comporte n bascules tel que : 2n-1 M 2n .

Cycle de comptage : prcise si la valeur de sortie utilise ou non toutes les combinaisons possibles.

Comptage cycle complet M=2n ou Comptage cycle incomplet M2n .

12. Compteurs asynchrones

121. Dfinition

Un compteur asynchrone est constitu de n bascules JK fonctionnant en mode T (Toggle) : J=K=1.

Ces bascules sont montes en cascade c'est--dire le signal dhorloge commande uniquement la premire

bascule tandis que pour chacune des autres bascules le signal d'horloge est fourni par la sortie de la

bascule de rang immdiatement infrieur.

122. Compteur asynchrone cycle complet

Pour bien comprendre le principe, ralisons un compteur modulo 8 permettant de compter de 0 7.

Pour cela, on a besoin de 3 bascules JK montes de la manire suivante :

J Pr Q J Pr Q J Pr Q

Horloge H H H

K Clr Q K Clr Q K Clr Q

Remise 0

Q0 Q1 Q2

Sciences et technologies lectriques Niveau 1re Sciences de lingnieur Unit ATC 1

LQTMY-Tanger M.SALMANI

Logique squentielle : Partie 2

Les chronogrammes et la table de vrit d'un tel compteur sont donns la figure suivante :

Q0

Q1

Q2

N

123. Compteur asynchrone cycle incomplet

Soit concevoir un compteur asynchrone modulo 10 qui compte de 0 9.

Le nombre n des bascules ncessaires pour la ralisation du compteur est tel que : 10 < 2n soit n=4.

Avec 4 bascules, le modulo du compteur est 16 donc pour avoir un modulo 10 on procde un forage

0 du compteur la combinaison N=10 soit Q3Q2Q1Q0=1010.

Le forage 0 du compteur consiste mettre 0 toutes les sorties Qi des 4 bascules.

On suppose que pour mettre Qi 0 on doit mettre lentre de forage asynchrone Clri 1.

Pour cela on cherche lquation logique de lentre de commande, Remise 0 Raz, en fonctions des Qi.

Raz

Sciences et technologies lectriques Niveau 1re Sciences de lingnieur Unit ATC 2

LQTMY-Tanger M.SALMANI

Logique squentielle : Partie 2

Le cblage dun tel compteur est donn par le schma suivant :

Raz

1

J Pr Q J Pr Q J Pr Q J Pr Q

Horloge H H H H

K Clr Q K Clr Q K Clr Q K Clr Q

Q0 Q1 Q2 Q3

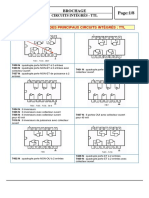

124. Compteurs asynchrones circuits intgrs

Les compteurs 74LS90 (modulo 10), 74LS92 (modulo 12) et 74LS93 (modulo 16) sont des compteurs

asynchrones composs de 4 bascules dont les connexions internes varient suivant le type du compteur.

Remarque :

La 1re bascule, diviseur par 2, est spare des 3 autres bascules qui

sont interconnectes de telle sorte pour former un diviseur par 5

(74LS90), un diviseur par 6 (74LS92) et un diviseur par 8 (74LS93).

Pour avoir un cycle de comptage modulo 10, 12 et 16 il faut relier le

signal dhorloge externe lentre CP0 et la sortie Q0 lentre CP1.

Sciences et technologies lectriques Niveau 1re Sciences de lingnieur Unit ATC 3

LQTMY-Tanger M.SALMANI

Logique squentielle : Partie 2

125. Spcificits des compteurs asynchrones

Lavantage des compteurs asynchrones se constitue la conception et la ralisation simple et facile

par rptition de modules diviseurs de frquence par 2 : mise en cascade des bascules T.

Dans la structure asynchrone, les bascules commutent en cascade partir dun signal dhorloge affect

la premire bascule ce qui entrane les inconvnients suivants :

Un fonctionnement lent du compteur : pour n bascules en cascade, le temps de fonctionnement ou de

propagation vaut n fois le temps de rponse (retard ou temps de propagation) dune bascule.

Lapparition des tats de sortie errons (Glitches) qui peuvent perturber le fonctionnement du systme.

Ces tats transitoires parasites sont appels des alas du fonctionnement (nombres hors comptage).

Par exemple, pour 3 bits, le passage de 011 100 est accompagn des tats parasites 010 et 000.

Le temps de rponse total lors de cette transition vaut 3 fois le temps de rponse dune bascule.

13. Compteurs synchrones

131. Dfinition

Un compteur synchrone est constitu de n bascules qui reoivent en parallle le mme signal dhorloge.

Lentre horloge est donc commune toutes les bascules dont les sorties changent dtats simultanment.

132. Table dexcitation de la bascule JK

Elle permet de dterminer quelles valeurs il faut appliquer aux entres synchrones J et K pour faire

voluer la sortie Q de la bascule dun tat vers un autre.

On note respectivement Q- et Q+ les valeurs de Q avant et aprs limpulsion dhorloge.

X : Quelque soit ltat logique.

Sciences et technologies lectriques Niveau 1re Sciences de lingnieur Unit ATC 4

LQTMY-Tanger M.SALMANI

Logique squentielle : Partie 2

133. Compteur synchrone cycle complet

Pour faire dcrire au compteur une squence dtermine il faut chaque impulsion d'horloge dfinir les

valeurs des entres synchrones J et K. Pour cela on utilise la table de transition de la bascule JK ainsi que

la table des tats dcrivant les diffrentes squences du compteur.

La rsolution du problme consiste donc chercher les quations logiques des entres J et K de chaque

bascule laide de la table des tats recherchs et de la table dexcitation de la bascule JK.

Prenons lexemple dun compteur synchrone modulo 8.

Table des tats du compteur

Equation logiques

J0=K0=1

J1=K1=Q0

J2=K2=Q1Q0

Le cblage du compteur synchrone module 8 est donn par le schma suivant :

J Pr Q J Pr Q J Pr Q

H H H

K Clr Q K Clr Q K Clr Q

Horloge

Q0 Q1 Q2

134. Compteur synchrone cycle incomplet

Soit concevoir un compteur synchrone modulo 10.

Le nombre n des bascules ncessaires pour la ralisation du compteur est tel que : 10 < 2n soit n=4.

Table des tats du compteur Equation logiques

J0=K0=1

J1=Q3Q0

K1=Q0

J2=K2=Q1Q0

J3= Q2Q1Q0

Les tats rejeter sont indiqus par des X K3=Q0

Sciences et technologies lectriques Niveau 1re Sciences de lingnieur Unit ATC 5

LQTMY-Tanger M.SALMANI

Logique squentielle : Partie 2

Le cblage du compteur synchrone module 10 est donn par le schma suivant :

J Pr Q J Pr Q J Pr Q J Pr Q

H H H H

K Clr Q K Clr Q K Clr Q K Clr Q

Horloge

Q0 Q1 Q2 Q3

Sciences et technologies lectriques Niveau 1re Sciences de lingnieur Unit ATC 6

LQTMY-Tanger M.SALMANI

Logique squentielle : Partie 2

135. Spcificits des compteurs synchrones

Avantages :

Temps d'tablissement constant (Une unit de propagation).

Pas de valeurs parasites.

Inconvnients :

Utilisation des circuits logiques combinatoires en plus des bascules.

Les modules sont donc diffrents.

136. Compteurs Spciaux

Compteurs rversibles

Ce sont des compteurs/dcompteurs qui peuvent compter comme ils peuvent dcompter. Le choix de la

fonction comptage ou de la fonction dcomptage seffectue laide dune entre de slection.

Compteurs programmables ou pr-positionns (presettables)

Ce sont des compteurs possdant des entres de pr-chargement qui contiennent la valeur de dpart

du comptage ou de dcomptage. Le chargement du compteur se fait grce une entre de commande.

137. Compteurs synchrones circuits intgrs

On cite titre dexemple :

Les compteurs synchrones pr-positionns modulo 10 : 74LS160 et 74LS162.

Les compteurs synchrones pr-positionns modulo 16 : 74LS161 et 74LS163.

Les compteurs/dcompteurs synchrones pr-positionns modulo 10 : 74LS190 et 74LS192.

Les compteurs/dcompteurs synchrones pr-positionns modulo 16 : 74LS191 et 74LS193.

Sciences et technologies lectriques Niveau 1re Sciences de lingnieur Unit ATC 7

LQTMY-Tanger M.SALMANI

Logique squentielle : Partie 2

2. Registres dcalage

21. Dfinition

Un registre dcalage est une association en cascade de bascules D qui sont interconnectes de faon ce

que l'tat logique de la bascule de rang i puisse tre transmis la bascule de rang i+1 (dcalage droite) ou

i-1 (dcalage gauche) quand un signal d'horloge est appliqu l'ensemble des bascules.

22. Classification des registres dcalage

En logique squentielle, les registres dcalage se distinguent selon les caractristiques suivantes :

221. Type de dcalage

Linformation (une srie de bits de donne) peut tre srialise suivant une direction de dcalage droite,

gauche ou dans ces deux directions (registre bidirectionnel).

222. Type de chargement ou mode dcriture

L'information peut tre charge selon un mode dcriture srie ou parallle. En mode parallle,

la donne est charge dans les bascules dun seul coup dhorloge (registre de mmorisation). En mode

srie, la donne est prsente squentiellement bit aprs bit l'entre de la premire bascule,

le dcalage peut tre alors vers la gauche ou la droite.

Pour le chargement srie, ou aura un 1er chargement et une suite de dcalages et chargements.

223. Mode de lecture

De mme, linformation peut tre lue en srie ou en parallle.

224. Nombre de bits

Le nombre de bits dans les registres est de 4, 5 ou 8. Un registre compos de ces registres lmentaires

peut contenir tout nombre de bits dsir.

23. Types des registres dcalage

Registres entre parallle et sortie parallle : Chargement parallle ou mmorisation de la donne.

Registres entre parallle et sortie srie : Chargement parallle puis dcalage de la donne.

Registres entre srie et sortie srie : Chargement srie puis dcalage de la donne.

Registres entre srie et sortie parallle : Chargement srie puis dcalage de la donne.

Les registres universels rassemblent les 4 modes de fonctionnement dcrits ci-dessus.

Leur structure est donne par le schma synoptique suivant :

Entre parallle

Entre srie gauche Entre srie droite

Horloge Registre Chargement parallle

Commandes

Sens de dcalage

Sortie srie

Sortie parallle

Sciences et technologies lectriques Niveau 1re Sciences de lingnieur Unit ATC 8

LQTMY-Tanger M.SALMANI

Logique squentielle : Partie 2

24. Registres dcalage circuits intgrs

74LS194 est un registre dcalage universel de 4 bits.

Il est utilis en modes srie-srie avec un dcalage gauche ou

droite, srie-parallle, parallle-srie et parallle-parallle.

25. Applications des registres dcalage

Les registres dcalage ont de nombreuses applications. Parmi celles-ci, on trouve :

251. Conversion parallle-srie

La conversion de donnes parallle-srie est utilise pour la transmission de donnes lors de lmission.

On prend des donnes binaires (gnralement un octet) en parallle et on les convertit en un train binaire

srie (74LS165).

252. Conversion srie-parallle

La conversion de donnes srie-parallle est utilise pour la transmission de donnes lors de la rception.

On prend des bits en srie et on les convertit (gnralement sur un octet) en parallle (74LS164).

253. Oprations arithmtiques

Les oprations arithmtiques de la multiplication et de la division utilisent la technique ou le principe de

dcalage. On entre et on sort alors en parallle.

254. Compteurs circulaires

Les compteurs circulaires sont des registres dcalage reboucls (rtroaction) utiliss en mode srie-srie.

Ils sont raliss en connectant la sortie de la dernire bascule lentre de la premire bascule.

Pour cela, il faut effectuer un chargement initial du compteur-registre, puis chaque coup d'horloge le

contenu se dcale en suivant une permutation circulaire.

Sciences et technologies lectriques Niveau 1re Sciences de lingnieur Unit ATC 9

LQTMY-Tanger M.SALMANI

Logique squentielle : Partie 2

On peut raliser ainsi des compteurs en anneau, des compteurs Johnson, des chenillards (jeux de lumire),

des gnrateurs d'horloges dcales, des gnrateurs de squences pseudo-alatoires, etc.

Compteurs Johnson

Il est constitu de n bascules D en cascade en faisant un bouclage de la sortie complmente de la dernire

bascule avec lentre de la premire bascule. Les bascules doivent tre mises 0 la mise sous tension.

On obtient des horloges de mmes priodes, mais dcales en phase. Il sagit dun code jointif comme le code

Gray car il ny a quune sortie qui change chaque coup dhorloge.

Pour comprendre le principe, considrons lexemple suivant de 3 bascules D.

Compteurs en anneau

Il est constitu de n bascules D en cascade en faisant un bouclage de la sortie de la dernire bascule

avec lentre de la premire bascule. Il faut mettre 1 une des bascules la mise sous tension et les

autres bascules sont mises 0. On obtient ainsi des horloges dcales temps jointifs.

Pour comprendre le principe, considrons lexemple suivant de 3 bascules D. Cest un compteur 1 parmi 3.

Le schma est identique au prcdent avec lentre D0 connecte la sortie Q2.

Compteur Johnson circuit intgr : 4017

Sciences et technologies lectriques Niveau 1re Sciences de lingnieur Unit ATC 10

LQTMY-Tanger M.SALMANI

Logique squentielle : Partie 2

3. Mmoires

31. Dfinition

Une mmoire est un circuit semi-conducteur permettant denregistrer, de conserver et de restituer des

informations. Il y a criture lorsqu'on enregistre des informations en mmoire et lecture lorsqu'on rcupre

des informations prcdemment enregistres.

32. Schma fonctionnel dune mmoire

Le schma fonctionnel dune mmoire est donn par le synoptique suivant :

Bus dadresses de p fils Mmoire Bus de donnes de n fils

CS R/W

Notion de bus : Un bus est un ensemble de fils.

Le bus dadresses est un bus unidirectionnel et le bus de donnes est un bus bidirectionnel.

Ladresse fournie par le bus dadresses est le mot binaire de p bits qui permet de localiser la donne.

La donne de n bits peut tre crite dans la mmoire ou lue de la mmoire travers le bus de donnes.

Le choix entre le mode de lecture ou dcriture se fait laide de lentre R/W (Read/Write).

Lentre de commande CS permet de slectionner le circuit ou de le mettre en tat de haute impdance.

La mmoire peut stocker 2p donnes de n bits.

33. Cycle de lecture/criture de la mmoire

Une mmoire peut tre utilise soit en lecture soit en criture.

Lopration de lecture dune mmoire suit le cycle suivant :

Ecrire ladresse de la donne sur le bus dadresses.

Slectionner le botier de la mmoire en appliquant un niveau logique bas sur lentre de commande CS.

Choisir le mode de lecture en appliquant un niveau logique haut sur lentre de commande R/W.

Lire la donne sur le bus de donnes.

Lopration dcriture dans une mmoire suit le cycle suivant :

Ecrire ladresse de la donne sur le bus dadresses.

Slectionner le botier de la mmoire en appliquant un niveau logique bas sur lentre de commande CS.

Choisir le mode dcriture en appliquant un niveau logique bas sur lentre de commande R/W.

Ecrire la donne sur le bus de donnes.

34. Caractristiques dune mmoire

341. Capacit

Cest le nombre total de bits que contient la mmoire. Elle sexprime aussi souvent en octets. Par exemple :

64b (b : bit), 4Kb, 8Ko (o : octet) avec : 1 octet=8 bits, 1K=210=1024, 1M=220=1024 K, 1G=230=1024 M.

342. Format des donnes

Cest le nombre de bits que lon peut mmoriser par case mmoire. On dit aussi que cest la largeur du mot

mmorisable.

Sciences et technologies lectriques Niveau 1re Sciences de lingnieur Unit ATC 11

LQTMY-Tanger M.SALMANI

Logique squentielle : Partie 2

343. Organisation

Elle dfinit le nombre de mots et la largeur de chaque mot. Par exemple :

Une mmoire de 64Kx1 est constitue de 65536 mots de 1 bit. Sa capacit est donc de 64Kb (8Ko).

Une mmoire de 8Kx8 contient 8192 mots de 8 bits. Sa capacit est donc de 64Kb (8Ko).

344. Temps daccs

Cest le temps qui s'coule entre l'instant o a t lance une opration de lecture/criture en mmoire et

l'instant o linformation est effectivement disponible sur le bus de donnes.

345. Temps de cycle

Il reprsente l'intervalle minimum qui doit sparer deux demandes successives de lecture ou d'criture.

346. Dbit

Cest le nombre maximum d'informations lues ou crites par seconde.

347. Volatilit

Elle caractrise la permanence des informations dans la mmoire. L'information stocke est volatile si

elle risque d'tre altre par un dfaut d'alimentation lectrique et non volatile dans le cas contraire.

35. Diffrents types de mmoires

Les mmoires sont classes suivant deux familles :

Mmoires mortes ROM (Read Only Memory) : mmoire lecture seule.

Mmoires vives RAM (Random Access Memory) : mmoire lecture et criture.

351. Mmoires vives

Une mmoire vive sert au stockage temporaire de donnes. Elle doit avoir un temps de cycle trs court pour

ne pas ralentir le microprocesseur. Les mmoires vives sont en gnral volatiles, elles perdent leurs

informations en cas de coupure d'alimentation. Certaines d'entre elles, ayant une faible consommation,

peuvent tre rendues non volatiles par l'adjonction d'une batterie. Il existe deux grandes familles de

mmoires RAM (mmoire accs alatoire) :

Les RAM statiques : Le bit mmoire d'une RAM statique (SRAM) est compos d'une bascule. Chaque

bascule contient entre 4 et 6 transistors.

Les RAM dynamiques : Dans les RAM dynamiques (DRAM), l'information est mmorise sous la forme

d'une charge lectrique stocke dans un condensateur (capacit grille substrat d'un transistor MOS).

352. Mmoires mortes

Pour certaines applications, il est ncessaire de pouvoir conserver des informations de faon permanente

mme lorsque l'alimentation lectrique est interrompue. On utilise alors des mmoires mortes. Ces mmoires

sont non volatiles. Contrairement aux RAM, ces mmoires ne peuvent tre que lues. Linscription des donnes

en mmoire seffectue par programmation. Suivant le type de la ROM, la mthode de la programmation

changera. Il existe donc plusieurs types de ROM :

ROM : Elle est programme par le fabricant et son contenu ne peut plus tre ni modifi, ni effac par

l'utilisateur.

PROM : Cest une ROM qui peut tre programme une seule fois par l'utilisateur (Programmable ROM).

La programmation est ralise partir dun programmateur spcifique.

Sciences et technologies lectriques Niveau 1re Sciences de lingnieur Unit ATC 12

LQTMY-Tanger M.SALMANI

Logique squentielle : Partie 2

EPROM ou UV-EPROM : Pour faciliter la mise au point d'un programme ou tout simplement permettre

une erreur de programmation, il est intressant de pouvoir reprogrammer une PROM.

L'EPROM (Erasable Programmable ROM) est une PROM qui peut tre efface par des rayons ultra violets.

EEPROM : Electically EPROM est une mmoire programmable et effaable lectriquement et peut tre

programme in situ.

FLASH EPROM : La mmoire Flash s'apparente la technologie de lEEPROM. Elle est programmable et

effaable lectriquement comme les EEPROM.

36. Extension de la capacit dune mmoire

Il est courant dans un systme microinformatique de grouper plusieurs circuits pour augmenter la

capacit (nombre des mots et/ou longueur des mots). Par exemple, laide de 4 botiers mmoires de

1Kx4bits, on peut raliser les mmoires suivantes : 1Kx16bits, 4Kx4bits, 2Kx8bits.

Le schma ci-dessous ralise une mmoire de 1Kx16bits (extension de format de la mmoire) partir

d'une mmoire lmentaire de 1Kx4bits :

Ncessit de 4 botiers.

Ncessit de 10 bits dadresses A0 A9.

Ncessit de 16 bits de donnes D0 D15.

AB

A0..A9

A0..A9 A0..A9 A0..A9 A0..A9

CS CS CS CS CS

R/W R/W R/W R/W

D0..D3 D0..D3 D0..D3 D0..D3

R/W

D0..D3 D4..D7 D8..D11 D12..D15

DB

D0..D15

Sciences et technologies lectriques Niveau 1re Sciences de lingnieur Unit ATC 13

Das könnte Ihnen auch gefallen

- Exercices d'optique et d'électromagnétismeVon EverandExercices d'optique et d'électromagnétismeBewertung: 5 von 5 Sternen5/5 (1)

- Direction Assistee ElectrohydrauliqueDokument28 SeitenDirection Assistee Electrohydrauliqueboujbal0% (1)

- Portes LogiquesDokument3 SeitenPortes LogiqueslakiNoch keine Bewertungen

- TP Redressement FiltrageDokument12 SeitenTP Redressement FiltrageJ'aime la Vie33% (3)

- 10 TP Prelude Picaso 10Dokument26 Seiten10 TP Prelude Picaso 10Mounir Kriâa100% (1)

- Electronique Numerique TDDokument2 SeitenElectronique Numerique TDAshraf MedNoch keine Bewertungen

- Administration Des SystemesDokument89 SeitenAdministration Des SystemesYanh DorelNoch keine Bewertungen

- TD Api GsiDokument4 SeitenTD Api Gsikhawlaaaa100% (1)

- TDN°1 Compteur DecompteurDokument1 SeiteTDN°1 Compteur DecompteurKhalil FrikhaNoch keine Bewertungen

- M15 - Logique Séquentielle GE-REEDokument58 SeitenM15 - Logique Séquentielle GE-REEKesraoui HichemNoch keine Bewertungen

- TD4 CorrectionDokument15 SeitenTD4 CorrectionistaitosNoch keine Bewertungen

- Cours Systèmes de Gestion de FichiersDokument37 SeitenCours Systèmes de Gestion de FichiersjouriaNoch keine Bewertungen

- 4 Logique Sequentielle PDFDokument24 Seiten4 Logique Sequentielle PDFkhocineNoch keine Bewertungen

- QCM Reseaux Corrige Interne 2008Dokument9 SeitenQCM Reseaux Corrige Interne 2008wasbac100% (1)

- Rapport de StageDokument18 SeitenRapport de StageLynda Ben Amor67% (3)

- ChapitreV Les HacheursDokument10 SeitenChapitreV Les HacheursAnass TaouFik100% (1)

- TPDokument24 SeitenTPAlassane Diouf100% (3)

- Logique Séquentielle: Compteurs Intégrés AsynchronesDokument16 SeitenLogique Séquentielle: Compteurs Intégrés AsynchronesbejaouiNoch keine Bewertungen

- Exercice de Logique Sequentielle PDFDokument30 SeitenExercice de Logique Sequentielle PDFmohcenNoch keine Bewertungen

- CLE Module1Dokument46 SeitenCLE Module1Mehdi El Alaoui100% (1)

- TP N°1Dokument4 SeitenTP N°1Marouane TaibiniNoch keine Bewertungen

- C Compteurs AsynchronesDokument7 SeitenC Compteurs AsynchronesTaoufiqBaouch100% (1)

- Électronique TsaDokument21 SeitenÉlectronique TsaadamsclovisherbertsNoch keine Bewertungen

- Les CompteursDokument7 SeitenLes CompteursSoufiane AggourNoch keine Bewertungen

- Les Compteurs ISISDokument10 SeitenLes Compteurs ISISDiego MezaNoch keine Bewertungen

- Chap 4 Les Circuits SequentielsDokument17 SeitenChap 4 Les Circuits SequentielsKycelle Mbouzeko100% (1)

- M18 - Logique Combinatoire GE-ESADokument136 SeitenM18 - Logique Combinatoire GE-ESAMohammed Amine Kened50% (4)

- TD Maintenance Idustrielle Electronique 2Dokument1 SeiteTD Maintenance Idustrielle Electronique 2Fth Walter100% (1)

- Circuits Combinatoires Et SéquentielsDokument38 SeitenCircuits Combinatoires Et SéquentielsHicham Wayne100% (3)

- 6-Logique Combinatoire ExosDokument2 Seiten6-Logique Combinatoire Exosoussama bouguerraNoch keine Bewertungen

- A22-Opérations D'arithmétique Binaire - v19 - 2Dokument6 SeitenA22-Opérations D'arithmétique Binaire - v19 - 2Rafik Ben AmorNoch keine Bewertungen

- Corrigés Des Tests N°2: Test N°2 Sujet N°1Dokument10 SeitenCorrigés Des Tests N°2: Test N°2 Sujet N°1koyabeNoch keine Bewertungen

- Correction Bac Blanc FINALDokument3 SeitenCorrection Bac Blanc FINALAh MédNoch keine Bewertungen

- Exercices Sur Le Grafcet PCDokument1 SeiteExercices Sur Le Grafcet PCDeepak Pathania100% (1)

- Cours Combinatoire+et+séquentielle Page Science de L'ingénieur PDFDokument18 SeitenCours Combinatoire+et+séquentielle Page Science de L'ingénieur PDFDivin MakitaNoch keine Bewertungen

- TMEL - Automatisme SchémaDokument4 SeitenTMEL - Automatisme SchémaAina RATSIMBAZAFYNoch keine Bewertungen

- Pic 16 F 877Dokument10 SeitenPic 16 F 877Youssef Boughallad100% (1)

- Compteurs 1Dokument33 SeitenCompteurs 1Mohamed EL MASSOUDINoch keine Bewertungen

- Upload - Série D'exercices N°4-3tech-Bascules-2013-2014-CorrectionDokument5 SeitenUpload - Série D'exercices N°4-3tech-Bascules-2013-2014-CorrectionchediNoch keine Bewertungen

- Examen CombinatoireDokument4 SeitenExamen CombinatoireMohammed El MonadyNoch keine Bewertungen

- Logique Combinatoire Et MultiplexageDokument15 SeitenLogique Combinatoire Et MultiplexagePhenix PhenixNoch keine Bewertungen

- TD-Logique SéquentielleDokument8 SeitenTD-Logique SéquentielleFabrice leonel Toukam PoualeuNoch keine Bewertungen

- EMD0203Dokument11 SeitenEMD0203FouadHbNoch keine Bewertungen

- Additionneur Binaire PDFDokument4 SeitenAdditionneur Binaire PDFnabil abdaoui100% (1)

- TP-LOGIQUE SEQUENTIELLE - Elctronique NumeriqueDokument16 SeitenTP-LOGIQUE SEQUENTIELLE - Elctronique NumeriqueAcse AbdeSsamadNoch keine Bewertungen

- Tp3 Mux DemuxDokument6 SeitenTp3 Mux DemuxAliou DialloNoch keine Bewertungen

- Brochage Des Principaux CI-TTL PDFDokument8 SeitenBrochage Des Principaux CI-TTL PDFFerjani Mohamed100% (1)

- Cours Electronique Numerique-3Dokument76 SeitenCours Electronique Numerique-3koukihamedNoch keine Bewertungen

- M19 - Logique CombinatoireDokument136 SeitenM19 - Logique CombinatoireCoolmanNoch keine Bewertungen

- Bascules SynchronesDokument7 SeitenBascules SynchronesMohamed Ben FredjNoch keine Bewertungen

- 1-Principe de Programmation LadderDokument13 Seiten1-Principe de Programmation LadderElmokh LassaadNoch keine Bewertungen

- Serie Exo AutomatismesDokument8 SeitenSerie Exo AutomatismesSalimMalekNoch keine Bewertungen

- E C Bascules D 3 Merged FAITDokument9 SeitenE C Bascules D 3 Merged FAITMohamed MathématicienNoch keine Bewertungen

- Exo Distributeur de BoissonsDokument2 SeitenExo Distributeur de BoissonsMila z100% (1)

- TD 10Dokument2 SeitenTD 10Wided MaghraouiNoch keine Bewertungen

- Logique Combinatoire (TP Automatisme ... Adder 4 Bits Soustracter 4bits Multiplieur 4 Bits .....Dokument37 SeitenLogique Combinatoire (TP Automatisme ... Adder 4 Bits Soustracter 4bits Multiplieur 4 Bits .....Soufiane El AoufiNoch keine Bewertungen

- Cours Et Exercices - Moteurs-Pas-A-PasDokument3 SeitenCours Et Exercices - Moteurs-Pas-A-Paskada saiNoch keine Bewertungen

- TD 03 PDFDokument6 SeitenTD 03 PDFmarwenNoch keine Bewertungen

- Serie D'exercices 4 BASCULES 2021-2022Dokument3 SeitenSerie D'exercices 4 BASCULES 2021-2022Manel AsnicarNoch keine Bewertungen

- TP1 LogiqueDokument5 SeitenTP1 LogiqueasmaNoch keine Bewertungen

- EXAM BLANC EP BonDokument2 SeitenEXAM BLANC EP BonAllegro Presto ModeratoNoch keine Bewertungen

- TDu CDokument49 SeitenTDu CnawzatNoch keine Bewertungen

- TP Initiation A La Programmation Du C PIC 16F84A en Mikro CDokument6 SeitenTP Initiation A La Programmation Du C PIC 16F84A en Mikro CPaty MuyengwaNoch keine Bewertungen

- CHAPITRE II Circuits Séquentiels PDFDokument35 SeitenCHAPITRE II Circuits Séquentiels PDFTimble PuteurNoch keine Bewertungen

- Algo PDFDokument27 SeitenAlgo PDFMehdi El AlaouiNoch keine Bewertungen

- Ift2255 ch2 ProcessusDokument8 SeitenIft2255 ch2 ProcessusMehdi El AlaouiNoch keine Bewertungen

- Manipulation Sous R - Régression Linéaire SimpleDokument2 SeitenManipulation Sous R - Régression Linéaire SimpleMehdi El AlaouiNoch keine Bewertungen

- La Technologie RaidDokument45 SeitenLa Technologie RaidCissé Aziz Mame AbdouNoch keine Bewertungen

- CH MemoiresDokument71 SeitenCH MemoiresN El kechaiNoch keine Bewertungen

- La Sauvegarde - V2Dokument28 SeitenLa Sauvegarde - V2Martin SimonetNoch keine Bewertungen

- Tarif 6632 PDFDokument39 SeitenTarif 6632 PDFAyoub MaskNoch keine Bewertungen

- WP RAID FRDokument14 SeitenWP RAID FRpapefayeNoch keine Bewertungen

- Info BTSDokument70 SeitenInfo BTSirieNoch keine Bewertungen

- (Pantalla NS5-SQ00-V2) - V083-ES2-03+NS+SetupManual PDFDokument257 Seiten(Pantalla NS5-SQ00-V2) - V083-ES2-03+NS+SetupManual PDFarmani_crupierNoch keine Bewertungen

- Atelier Système D'exploitation UNIXLINUXDokument5 SeitenAtelier Système D'exploitation UNIXLINUXFarah BeltaiefNoch keine Bewertungen

- td5 Sur Chapitre 3. Automate ProgrammableDokument9 Seitentd5 Sur Chapitre 3. Automate ProgrammableJean Louis KouassiNoch keine Bewertungen

- L'Ordinateur Et Ses ComposantsDokument27 SeitenL'Ordinateur Et Ses ComposantsChali JaliNoch keine Bewertungen

- Fiche 15 L-'Unité CentraleDokument4 SeitenFiche 15 L-'Unité CentraleMarikAvilNoch keine Bewertungen

- Les 45 Commandes Linux Les Plus UtilesDokument25 SeitenLes 45 Commandes Linux Les Plus UtilesFatim EzzahraNoch keine Bewertungen

- G en Eralit Es 1: Zaghdoudi Salima - Bourai Nour El Houda February 17, 2020Dokument12 SeitenG en Eralit Es 1: Zaghdoudi Salima - Bourai Nour El Houda February 17, 2020Debbiche LoubnaNoch keine Bewertungen

- Livre APC 2CDokument167 SeitenLivre APC 2CDassie joseph ChristineNoch keine Bewertungen

- RAPPORT DE STAGE GRACIA - New1Dokument36 SeitenRAPPORT DE STAGE GRACIA - New1T'grave TréjoNoch keine Bewertungen

- Cours ArchitectureDokument89 SeitenCours ArchitectureHabib TanouNoch keine Bewertungen

- Rapport PFE VTLDokument64 SeitenRapport PFE VTLYoussef BaloukiNoch keine Bewertungen

- Chapitre - 5 - Gestion de Mémoire PDFDokument34 SeitenChapitre - 5 - Gestion de Mémoire PDFImad EL IDRISSINoch keine Bewertungen

- TP2 Se1Dokument2 SeitenTP2 Se1Amine LahlalNoch keine Bewertungen

- M07 - Utilisation D'un Micro-Ordinateur GE-REEDokument139 SeitenM07 - Utilisation D'un Micro-Ordinateur GE-REEKesraoui HichemNoch keine Bewertungen

- Cours TIC 2015-2016Dokument19 SeitenCours TIC 2015-2016nounoulekNoch keine Bewertungen

- Cluster CommandesDokument6 SeitenCluster CommandesKouessan TogbedjiNoch keine Bewertungen

- TD3 - Corrigé - Pagination A La DemandeDokument8 SeitenTD3 - Corrigé - Pagination A La DemandeAbdelbassit Abed-meraimNoch keine Bewertungen

- Memoire CacheDokument56 SeitenMemoire CacheImane el omariNoch keine Bewertungen

- DefinitionDokument3 SeitenDefinitionAdama Djibril DialloNoch keine Bewertungen