Beruflich Dokumente

Kultur Dokumente

bsc019n04nsg Infineon

Hochgeladen von

doraemon007Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

bsc019n04nsg Infineon

Hochgeladen von

doraemon007Copyright:

Verfügbare Formate

BSC019N04NS G

OptiMOS3 Power-Transistor

Product Summary

Features

V DS 40 V

Fast switching MOSFET for SMPS

R DS(on),max 1.9 m

Optimized technology for DC/DC converters

ID 100 A

1)

Qualified according to JEDEC for target applications

N-channel

PG-TDSON-8

Normal level

Excellent gate charge x R DS(on) product (FOM)

Very low on-resistance R DS(on)

Superior thermal resistance

100% Avalanche tested

Pb-free plating; RoHS compliant

Type Package Marking

BSC019N04NS G PG-TDSON-8 019N04NS

Maximum ratings, at T j=25 C, unless otherwise specified

Parameter Symbol Conditions Value Unit

Continuous drain current ID V GS=10 V, T C=25 C 100 A

V GS=10 V, T C=100 C 100

V GS=10 V, T A=25 C,

29

R thJA=50 K/W 2)

Pulsed drain current3) I D,pulse T C=25 C 400

Avalanche current, single pulse 4) I AS T C=25 C 50

Avalanche energy, single pulse E AS I D=50 A, R GS=25 295 mJ

Gate source voltage V GS 20 V

1)

J-STD20 and JESD22

Rev. 1.1 page 1 2008-08-11

BSC019N04NS G

Maximum ratings, at T j=25 C, unless otherwise specified

Parameter Symbol Conditions Value Unit

Power dissipation P tot T C=25 C 125 W

T A=25 C,

2.5

R thJA=50 K/W 2)

Operating and storage temperature T j, T stg -55 ... 150 C

IEC climatic category; DIN IEC 68-1 55/150/56

Parameter Symbol Conditions Values Unit

min. typ. max.

Thermal characteristics

Thermal resistance, junction - case R thJC - - 1 K/W

Device on PCB R thJA 6 cm2 cooling area2) - - 50

Electrical characteristics, at T j=25 C, unless otherwise specified

Static characteristics

Drain-source breakdown voltage V (BR)DSS V GS=0 V, I D=1 mA 40 - - V

Gate threshold voltage V GS(th) V DS=V GS, I D=85 A 2 - 4

V DS=40 V, V GS=0 V,

Zero gate voltage drain current I DSS - 0.1 1 A

T j=25 C

V DS=40 V, V GS=0 V,

- 10 100

T j=125 C

Gate-source leakage current I GSS V GS=20 V, V DS=0 V - - 100 nA

Drain-source on-state resistance R DS(on) V GS=10 V, I D=50 A - 1.6 1.9 m

Gate resistance RG - 1.3 -

|V DS|>2|I D|R DS(on)max,

Transconductance g fs 60 120 - S

I D=50 A

2)

Device on 40 mm x 40 mm x 1.5 mm epoxy PCB FR4 with 6 cm2 (one layer, 70 m thick) copper area for drain

connection. PCB is vertical in still air.

3)

See figure 3 for more detailed information

4)

See figure 13 for more detailed information

Rev. 1.1 page 2 2008-08-11

BSC019N04NS G

Parameter Symbol Conditions Values Unit

min. typ. max.

Dynamic characteristics

Input capacitance C iss - 6600 8800 pF

V GS=0 V, V DS=20 V,

Output capacitance C oss - 1800 2400

f =1 MHz

Reverse transfer capacitance Crss - 70 -

Turn-on delay time t d(on) - 22 - ns

Rise time tr V DD=20 V, V GS=10 V, - 5.6 -

Turn-off delay time t d(off) I D=30 A, R G=1.6 - 33 -

Fall time tf - 6.6 -

Gate Charge Characteristics 5)

Gate to source charge Q gs - 32 - nC

Gate charge at threshold Q g(th) - 20 -

Gate to drain charge Q gd V DD=20 V, I D=30 A, - 10 -

Q sw V GS=0 to 10 V

Switching charge - 22 -

Gate charge total Qg - 81 108

Gate plateau voltage V plateau - 4.9 - V

V DS=0.1 V,

Gate charge total, sync. FET Q g(sync) - 77 - nC

V GS=0 to 10 V

Output charge Q oss V DD=20 V, V GS=0 V - 66 -

Reverse Diode

Diode continuous forward current IS - - 100 A

T C=25 C

Diode pulse current I S,pulse - - 400

V GS=0 V, I F=50 A,

Diode forward voltage V SD - 0.85 1.2 V

T j=25 C

V R=20 V, I F=I S,

Reverse recovery charge Q rr - 100 - nC

di F/dt =400 A/s

5)

See figure 16 for gate charge parameter definition

Rev. 1.1 page 3 2008-08-11

BSC019N04NS G

1 Power dissipation 2 Drain current

P tot=f(T C) I D=f(T C); V GS10 V

140 120

120

100

100

80

80

P tot [W]

I D [A]

60

60

40

40

20

20

0 0

0 40 80 120 160 0 40 80 120 160

T C [C] T C [C]

3 Safe operating area 4 Max. transient thermal impedance

I D=f(V DS); T C=25 C; D =0 Z thJC=f(t p)

parameter: t p parameter: D =t p/T

103 10

limited by on-state

resistance 1 s

10 s

102 100 s

1

DC

Z thJC [K/W]

1 ms 0.5

I D [A]

1

10

0.2

10 ms

0.1

0.1

100 0.05

0.02

0.01

10-1 0.01 0

single pulse

0 0 0 0 0 1

-1 0 1 2

10 10 10 10 10-6 10-5 10-4 10-3 10-2 10-1 100

V DS [V] t p [s]

Rev. 1.1 page 4 2008-08-11

BSC019N04NS G

5 Typ. output characteristics 6 Typ. drain-source on resistance

I D=f(V DS); T j=25 C R DS(on)=f(I D); T j=25 C

parameter: V GS parameter: V GS

400 6

10 V

7V

5.5 V

6.5 V

5

300

R DS(on) [m]

5V

6V

I D [A]

200 3

6V

6.5 V

2 7V

5.5 V

10 V

100

1

5V

0 0

0 1 2 3 0 10 20 30 40 50

V DS [V] I D [A]

7 Typ. transfer characteristics 8 Typ. forward transconductance

I D=f(V GS); |V DS|>2|I D|R DS(on)max g fs=f(I D); T j=25 C

parameter: T j

400 250

200

300

150

g fs [S]

I D [A]

200

100

150 C

100

25 C

50

0 0

2 3 4 5 6 7 8 0 40 80 120 160

V GS [V] I D [A]

Rev. 1.1 page 5 2008-08-11

BSC019N04NS G

9 Drain-source on-state resistance 10 Typ. gate threshold voltage

R DS(on)=f(T j); I D=50 A; V GS=10 V V GS(th)=f(T j); V GS=V DS; I D=85 A

3.5 4.5

3 4

2.5 3.5

R DS(on) [m]

2 98 %

3

V GS(th) [V]

typ

1.5 2.5

1 2

0.5 1.5

0 1

-60 -20 20 60 100 140 180 -60 -20 20 60 100 140 180

T j [C] T j [C]

11 Typ. capacitances 12 Forward characteristics of reverse diode

C =f(V DS); V GS=0 V; f =1 MHz I F=f(V SD)

parameter: T j

104 10000

1000

Ciss

Coss

150 C, 98%

25 C

103 1000

100

150 C

C [pF]

I F [A]

25 C, 98%

102 100

Crss 10

101 10

1

0 10 20 30 40 0.0 0.5 1.0 1.5 2.0

V DS [V] V SD [V]

Rev. 1.1 page 6 2008-08-11

BSC019N04NS G

13 Avalanche characteristics 14 Typ. gate charge

I AS=f(t AV); R GS=25 V GS=f(Q gate); I D=30 A pulsed

parameter: T j(start) parameter: V DD

100 12

20 V

10

25 C

8V

100 C

32 V

125 C

8

V GS [V]

I AV [A]

10 6

1 0

1 10 100 1000 0 20 40 60 80 100

t AV [s] Q gate [nC]

15 Drain-source breakdown voltage 16 Gate charge waveforms

V BR(DSS)=f(T j); I D=1 mA

45

V GS

Qg

40

35

V BR(DSS) [V]

30 V g s(th)

25

Q g(th) Q sw Q g ate

Q gs Q gd

20

-60 -20 20 60 100 140 180

T j [C]

Rev. 1.1 page 7 2008-08-11

BSC019N04NS G

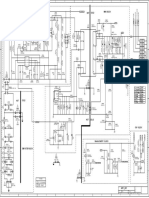

Package Outline PG-TDSON-8

PG-TDSON-8: Outline

Footprint

Dimensions in mm

Rev. 1.1 page 8 2008-08-11

BSC019N04NS G

Package Outline

PG-TDSON-8: Tape

Dimensions in mm

Rev. 1.1 page 9 2008-08-11

BSC019N04NS G

Published by

Infineon Technologies AG

81726 Munich, Germany

2008 Infineon Technologies AG

All Rights Reserved.

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of

conditions or characteristics. With respect to any examples or hints given herein, any typical

values stated herein and/or any information regarding the application of the device,

Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind,

including without limitation, warranties of non-infringement of intellectual property rights

of any third party.

Information

For further information on technology, delivery terms and conditions and prices, please

contact the nearest Infineon Technologies

(www.infineon.com).

Warnings

Due to technical requirements, components may contain dangerous substances. For information

on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with

the express written approval of Infineon Technologies, if a failure of such components can

reasonably be expected to cause the failure of that life-support device or system or to affect

the safety or effectiveness of that device or system. Life support devices or systems are

intended to be implanted in the human body or to support and/or maintain and sustain

and/or protect human life. If they fail, it is reasonable to assume that the health of the user

or other persons may be endangered.

Rev. 1.1 page 10 2008-08-11

www.s-manuals.com

Das könnte Ihnen auch gefallen

- Cossor 343Dokument42 SeitenCossor 343doraemon007Noch keine Bewertungen

- TV Samsung Chassi Uwj - 52 Ue - 40 - 48 - 55 Ju 6000 K UhdDokument68 SeitenTV Samsung Chassi Uwj - 52 Ue - 40 - 48 - 55 Ju 6000 K Uhddoraemon007100% (1)

- BLE Temperature and Humidity LoggerDokument2 SeitenBLE Temperature and Humidity Loggerdoraemon007Noch keine Bewertungen

- 4600 OsmDokument149 Seiten4600 Osmdoraemon007Noch keine Bewertungen

- Schneider Electronics Manual Provides Safety InstructionsDokument38 SeitenSchneider Electronics Manual Provides Safety Instructionsdoraemon007Noch keine Bewertungen

- KV SZ29M50 BX1LDokument9 SeitenKV SZ29M50 BX1LttNoch keine Bewertungen

- Model 92E RF Millivoltmeter Instruction ManualDokument47 SeitenModel 92E RF Millivoltmeter Instruction Manualdoraemon007Noch keine Bewertungen

- Calstan 223 SetDokument7 SeitenCalstan 223 Setdoraemon007Noch keine Bewertungen

- Calstan 223 User ManualDokument4 SeitenCalstan 223 User Manualdoraemon007Noch keine Bewertungen

- TCL Led32e3020-Ms82cd-La Service Manual RarDokument42 SeitenTCL Led32e3020-Ms82cd-La Service Manual Rarchad tan100% (1)

- Everyday Practical Electronics 2010-04 LevelDokument10 SeitenEveryday Practical Electronics 2010-04 Leveldoraemon007Noch keine Bewertungen

- LG 32LK330-DBDokument63 SeitenLG 32LK330-DBdoraemon007100% (2)

- 59 LFcoilsDokument13 Seiten59 LFcoilsdoraemon007Noch keine Bewertungen

- CT5038G6X Chasis AA41Dokument39 SeitenCT5038G6X Chasis AA41erepairman100% (1)

- BN44 00473a Ue40d5003 PDFDokument6 SeitenBN44 00473a Ue40d5003 PDFRondownload KibaNoch keine Bewertungen

- Service ManualDokument24 SeitenService ManualAhmed RedaNoch keine Bewertungen

- Epson LQ-870 LQ-1170 PDFDokument143 SeitenEpson LQ-870 LQ-1170 PDFdoraemon007Noch keine Bewertungen

- Samsung bn44-00340b PDFDokument2 SeitenSamsung bn44-00340b PDFsylvan_Noch keine Bewertungen

- Tvpana CT-F2136LP PDFDokument10 SeitenTvpana CT-F2136LP PDFdoraemon007Noch keine Bewertungen

- Nakamichi CD Player 4 SMDokument46 SeitenNakamichi CD Player 4 SMdoraemon007Noch keine Bewertungen

- CT-F2136LP: Colour TelevisionDokument10 SeitenCT-F2136LP: Colour Televisiondoraemon007Noch keine Bewertungen

- Apple Ipad 4 SCHDokument41 SeitenApple Ipad 4 SCHdoraemon007Noch keine Bewertungen

- PW Energizer ManualDokument31 SeitenPW Energizer Manualdoraemon007Noch keine Bewertungen

- JVC AV-21B117BDokument10 SeitenJVC AV-21B117Bdoraemon007100% (1)

- Canon Mvx200 Mvx250i-SmDokument259 SeitenCanon Mvx200 Mvx250i-Smdoraemon007Noch keine Bewertungen

- Philips DVD Hts3357Dokument32 SeitenPhilips DVD Hts3357doraemon007Noch keine Bewertungen

- Canon Mvx100 Mvx150i-SmDokument233 SeitenCanon Mvx100 Mvx150i-Smdoraemon007Noch keine Bewertungen

- Fan7024 FairchildDokument17 SeitenFan7024 Fairchilddoraemon007Noch keine Bewertungen

- 1993 AccordDokument178 Seiten1993 Accorddoraemon007Noch keine Bewertungen

- bsc027n04lsg Infineon PDFDokument11 Seitenbsc027n04lsg Infineon PDFdoraemon007Noch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- OIL PUMP SPECIFICATION AND OPERATING PRINCIPLEDokument2 SeitenOIL PUMP SPECIFICATION AND OPERATING PRINCIPLEPedroNoch keine Bewertungen

- 04 Samss 042Dokument6 Seiten04 Samss 042ShojikuriakoseTNoch keine Bewertungen

- Quidway AR 46 Series Routers Installation ManualDokument188 SeitenQuidway AR 46 Series Routers Installation ManualcharliilNoch keine Bewertungen

- TSG PRD TS 11 V17 Cover - Device Field and Lab Test GuidelinesDokument18 SeitenTSG PRD TS 11 V17 Cover - Device Field and Lab Test GuidelinesAlberto Martín JiménezNoch keine Bewertungen

- How To Simplify Compliance With The New ISO 13485 2016 Final PDFDokument63 SeitenHow To Simplify Compliance With The New ISO 13485 2016 Final PDFAymen Bekir100% (3)

- Upgrade 9600 LH System with MPT-HL Extendable TechnologyDokument26 SeitenUpgrade 9600 LH System with MPT-HL Extendable TechnologyAtanda Babatunde MutiuNoch keine Bewertungen

- KP-00+++-CQ712-G0011 - Rev.A - ITP For For Cathodic Protection (CP)Dokument7 SeitenKP-00+++-CQ712-G0011 - Rev.A - ITP For For Cathodic Protection (CP)Utku Can Kılıç100% (2)

- D4239-05 Sulfur High Temperature TubeDokument8 SeitenD4239-05 Sulfur High Temperature TubeVladimir KrzalicNoch keine Bewertungen

- ProStar® Chassis Built June 14, 2010 and AfterDokument319 SeitenProStar® Chassis Built June 14, 2010 and AfterHilario Gayosso CruzNoch keine Bewertungen

- M89 7R1Dokument3 SeitenM89 7R1oscar horacio flores100% (2)

- Cost-effective 1,500 VDC modular inverters for large-scale solar plantsDokument2 SeitenCost-effective 1,500 VDC modular inverters for large-scale solar plantsGregorio VillarrealNoch keine Bewertungen

- Iso16063 162014Dokument22 SeitenIso16063 162014Fallo SusiloNoch keine Bewertungen

- UCL's Global Civil Engineering MScDokument4 SeitenUCL's Global Civil Engineering MScNaufal HaniefNoch keine Bewertungen

- Understanding NIST HL7 v2 Test Tools: Focus On ONC 2015 Health IT CertificationDokument61 SeitenUnderstanding NIST HL7 v2 Test Tools: Focus On ONC 2015 Health IT CertificationSpit FireNoch keine Bewertungen

- Call 800-DIESELS (343-7357) : Natural Gas EngineDokument10 SeitenCall 800-DIESELS (343-7357) : Natural Gas EnginereycoeleNoch keine Bewertungen

- Unit IGC 2 - Element 5: Electrical SafetyDokument5 SeitenUnit IGC 2 - Element 5: Electrical SafetyHamid Rehman100% (1)

- CASE 595 P100 Trainings Manual GB PDFDokument195 SeitenCASE 595 P100 Trainings Manual GB PDFjulianmata100% (2)

- Passive Fire Protection Testing & CertificationDokument9 SeitenPassive Fire Protection Testing & CertificationVikas Kumar Pathak100% (1)

- Transformer Bushings PDFDokument36 SeitenTransformer Bushings PDFhashamNoch keine Bewertungen

- Controller SMGDokument696 SeitenController SMGJonathan EdvardsNoch keine Bewertungen

- Electrical Specs Jan. 2019Dokument374 SeitenElectrical Specs Jan. 2019MiyakhanNoch keine Bewertungen

- CIS Microsoft SQL Server 2019 Benchmark v1.0.0 PDFDokument100 SeitenCIS Microsoft SQL Server 2019 Benchmark v1.0.0 PDFConciencia ImmortalNoch keine Bewertungen

- Field Bus PrinciplesDokument18 SeitenField Bus PrinciplesRahul TiwariNoch keine Bewertungen

- Flange Insulating Gasket Kits: Advance Products & SystemsDokument8 SeitenFlange Insulating Gasket Kits: Advance Products & SystemsJF ZLNoch keine Bewertungen

- Interview Questions With AnswersDokument3 SeitenInterview Questions With AnswersDarshan GhadiNoch keine Bewertungen

- Texatherm: Industrial Heat Transfer OilDokument2 SeitenTexatherm: Industrial Heat Transfer OilCharith LiyanageNoch keine Bewertungen

- ACM Data Sheet Rev 04 10 - 14 PDFDokument2 SeitenACM Data Sheet Rev 04 10 - 14 PDFJosephNoch keine Bewertungen

- SecureClient 5.6 UsersGuide All ENUDokument124 SeitenSecureClient 5.6 UsersGuide All ENUnxth@inbox.comNoch keine Bewertungen

- BS en 148 1 (1999) - Respiratory Protective Devices PDFDokument12 SeitenBS en 148 1 (1999) - Respiratory Protective Devices PDFck19654840Noch keine Bewertungen

- Modbus Rtu With VBDokument8 SeitenModbus Rtu With VBSatria RonalNoch keine Bewertungen