Beruflich Dokumente

Kultur Dokumente

Lista 1 Prova SD

Hochgeladen von

Rafael MironOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Lista 1 Prova SD

Hochgeladen von

Rafael MironCopyright:

Verfügbare Formate

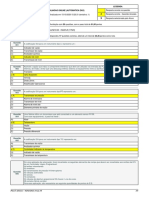

UFPel CEng - Engenharia Eletrnica

Sistemas Digitais I Cdigo: 1420009

Exerccios referentes primeira avaliao

1. Projete uma mquina sequencial que implemente na sua sada uma contagem em cdigo Gray de

3 bits. Utilize flip-flops do tipo D.

2. Obtenha a implementao de uma FSM para reconhecer o padro 1010110.

3. Determine a tabela de estados correspondente ao diagrama de transio de estados abaixo, e

simplifique o nmero de estados. (4,0)

4. Determine a tabela mnima para a FSM caracterizada pela tabela de estados abaixo.

s(t+1) o(t+1)

s(t) i(t) = a i(t) = b i(t) = a i(t) = b

A F C 0 0

B H A 1 1

C H D 0 1

D B H 0 0

E G C 0 0

F C E 1 1

G H E 1 1

H C A 0 1

5. Faa o projeto (especificao PC-PO) de um circuito controlador de temperatura para uma sala

climatizada. A entrada t_sel (8 bits) corresponde ao valor de temperatura que deve ser mantido pelo

sistema, entre 0C e 80C. A entrada t_med (8 bits) corresponde ao valor da temperatura medida na

sala. A sada Q controla um sistema aquecedor, e a sada F controla um sistema refrigerador. A

tolerncia do sistema de 4C.

6. Desenvolva o circuito de um multiplicador sequencial (especificao PC-PO) para nmeros de 8

bits sem sinal, segundo o algoritmo da acumulao sucessiva. A entrada ini indica quando a

operao deve ser iniciada. As entradas A e B contm os valores (8 bits) para multiplicao. A sada

R contm o resultado da operao. A sada P indica (valor '1' por um ciclo de clock) quando o

resultado est disponvel. A sada busy indica (valor '1') quando o resultado est sendo calculado.

7. Faa o projeto (especificao PC-PO) de um circuito somador serial de 8 bits. A entrada ini

indica quando a operao deve ser iniciada. As entradas A e B contm os valores (8 bits) para

adio. A sada R contm o resultado da operao. A sada P indica (valor '1' por um ciclo de clock)

quando o resultado est disponvel. A sada busy indica (valor '1') quando o resultado est sendo

calculado. O somador deve utilizar um nico bloco de somador completo.

8. Apresente o esquema de conexo de full-adders para uma rvore de reduo de produtos parciais

do tipo Wallace, para um multiplicador de 8x8 bits.

9. Apresente o esquema de conexes de um somador do tipo ripple-carry de 12 bits, na verso

combinacional e nas verses pipeline de 2, 3 e 4 estgios. Considere os tempos de retardo de

propagao dos full-adders como sendo de 1 ns, e o tempo de propagao dos registradores como

sendo de 0,1 ns. Compare o desempenho dos circuitos.

10. Elabore o projeto (especificao PC-PO) de um circuito para o clculo do quadrado de um

nmero (S = N2).

Das könnte Ihnen auch gefallen

- Pliometria Sequencia Racional - João Coutinho PDFDokument90 SeitenPliometria Sequencia Racional - João Coutinho PDFFernando Galvão100% (3)

- Lista de Exercícios - Eletrônica DigitalDokument6 SeitenLista de Exercícios - Eletrônica Digitalanon_790987447Noch keine Bewertungen

- Lista de Exercícios - Circuitos Digitais - Resolução - Frank VahidDokument19 SeitenLista de Exercícios - Circuitos Digitais - Resolução - Frank VahidElder SantosNoch keine Bewertungen

- Manual Avançado - Clambunk 895Dokument43 SeitenManual Avançado - Clambunk 895Eloir Moraes100% (1)

- Avaliação Barroco 1º AnoDokument3 SeitenAvaliação Barroco 1º AnoKellin Callegari100% (3)

- RA.1 - Compreender Princípios e Conceitos Básicos de Um Sistema EconómicoDokument26 SeitenRA.1 - Compreender Princípios e Conceitos Básicos de Um Sistema EconómicoStelio Cuinica100% (4)

- Gerenciamento Do Descarte de ResíduosDokument46 SeitenGerenciamento Do Descarte de ResíduosCristiano Partata BorgesNoch keine Bewertungen

- Marketing de Vendas - PaperDokument13 SeitenMarketing de Vendas - Paperthiagoreisrs100% (4)

- Manual Orona Arca 2Dokument201 SeitenManual Orona Arca 2Jó RamosNoch keine Bewertungen

- Somador 1, 4, 8, 16, 32 e 64 Bits (VHDL)Dokument26 SeitenSomador 1, 4, 8, 16, 32 e 64 Bits (VHDL)Quelita Araújo92% (13)

- Teste PlantasDokument5 SeitenTeste Plantaslilianarmdias67% (3)

- Avaliação Online de Automação ElétricaDokument5 SeitenAvaliação Online de Automação ElétricaKelitonNoch keine Bewertungen

- Circuitos lógicos - Lista de exercícios capítulo 3Dokument2 SeitenCircuitos lógicos - Lista de exercícios capítulo 3Yuri CardosoNoch keine Bewertungen

- Lista de exercícios avaliativa de circuitos digitaisDokument4 SeitenLista de exercícios avaliativa de circuitos digitaisElder SantosNoch keine Bewertungen

- Circuitos Digitais - ListaDokument4 SeitenCircuitos Digitais - ListaAndré Araújo de Souza SilvaNoch keine Bewertungen

- Relatório Projeto1 IncompletoDokument6 SeitenRelatório Projeto1 IncompletoMMO PlayEasyNoch keine Bewertungen

- TelecomDokument9 SeitenTelecomTrambucoNoch keine Bewertungen

- Apostila WinCupl PDFDokument26 SeitenApostila WinCupl PDFmbenencaseNoch keine Bewertungen

- Roteiro Exp 4Dokument4 SeitenRoteiro Exp 4rafa_preussNoch keine Bewertungen

- Exercícios Blocos Lógicos Memórias e ConversoresDokument6 SeitenExercícios Blocos Lógicos Memórias e ConversoresCedeps facensNoch keine Bewertungen

- Sistemas Digitais: 1º Ano de Engenharia Electrotécnica e de ComputadoresDokument8 SeitenSistemas Digitais: 1º Ano de Engenharia Electrotécnica e de ComputadoresRita SeixasNoch keine Bewertungen

- Exp 3 - Gabriel Nazario GonçalvesDokument5 SeitenExp 3 - Gabriel Nazario GonçalvesGabriel NazarioNoch keine Bewertungen

- Eletronica Digital II Conversores D A eDokument35 SeitenEletronica Digital II Conversores D A eAntonio EduardoNoch keine Bewertungen

- Aula 5 - Exercicios 8085Dokument16 SeitenAula 5 - Exercicios 8085Paulo EduardoNoch keine Bewertungen

- Arquitetura de Computadores - Questionário 9Dokument10 SeitenArquitetura de Computadores - Questionário 9Marcus RamosNoch keine Bewertungen

- Fundamentos de Processos Estocásticos - 4a. Lista de ExercíciosDokument2 SeitenFundamentos de Processos Estocásticos - 4a. Lista de ExercíciosSlime TutorialsNoch keine Bewertungen

- Lista Exercícios Função Transferência ModelagemDokument7 SeitenLista Exercícios Função Transferência ModelagemSaymmon GomesNoch keine Bewertungen

- Formas padronizadas de funções lógicas e portas lógicasDokument4 SeitenFormas padronizadas de funções lógicas e portas lógicasLucas GabrielNoch keine Bewertungen

- Lista de exercícios avaliativa de circuitos digitaisDokument9 SeitenLista de exercícios avaliativa de circuitos digitaisElder SantosNoch keine Bewertungen

- TP2 AtmDokument2 SeitenTP2 AtmBrenda CarolineNoch keine Bewertungen

- Arquitetura de Computadores – Questionário 9Dokument10 SeitenArquitetura de Computadores – Questionário 9Marcus RamosNoch keine Bewertungen

- Avaliação 2 de MicrocontroladoresDokument2 SeitenAvaliação 2 de MicrocontroladoresDiego AguiarNoch keine Bewertungen

- Desafio3 1AndOrDokument2 SeitenDesafio3 1AndOral29346Noch keine Bewertungen

- ECompDokument12 SeitenECompDavid FilipeNoch keine Bewertungen

- Linguagem CDokument41 SeitenLinguagem CCassia Cruz LuizNoch keine Bewertungen

- Slebf 20082009 ErDokument1 SeiteSlebf 20082009 ErHelder RamiresNoch keine Bewertungen

- SDex1998 1 1 ResolucaoDokument6 SeitenSDex1998 1 1 ResolucaoluisjeNoch keine Bewertungen

- Preparação Do Laboratório 3Dokument10 SeitenPreparação Do Laboratório 3Max SousaNoch keine Bewertungen

- Modelos dinâmicos lista exercíciosDokument1 SeiteModelos dinâmicos lista exercíciosViniciusNoch keine Bewertungen

- Micro Process AdoresDokument130 SeitenMicro Process Adoreswesley_wsyNoch keine Bewertungen

- TP3 - Tow ThomasDokument1 SeiteTP3 - Tow ThomasFAUSTONoch keine Bewertungen

- Controlo de sistemas amostrados por computadorDokument4 SeitenControlo de sistemas amostrados por computadorcunha40956Noch keine Bewertungen

- ListaExercíciosArquiteturaComputadoresDokument21 SeitenListaExercíciosArquiteturaComputadoresoctaviooliNoch keine Bewertungen

- Guia Do Experimento 3 Módulo 2018.1Dokument4 SeitenGuia Do Experimento 3 Módulo 2018.1Felipe de SouzaNoch keine Bewertungen

- Primeiro Trabalho Sic XeDokument8 SeitenPrimeiro Trabalho Sic XeAnna Gabriele Marques de OliveiraNoch keine Bewertungen

- 1 Lista de ExercíciosDokument8 Seiten1 Lista de ExercíciosThiago Abrantes0% (1)

- Lista Exerc 02Dokument3 SeitenLista Exerc 02Philip ApsNoch keine Bewertungen

- PSC - Aula 03 - Métodos de Sintonia PIDDokument16 SeitenPSC - Aula 03 - Métodos de Sintonia PIDluisinchannelNoch keine Bewertungen

- Cursos Engenharia Computação EletrônicaDokument4 SeitenCursos Engenharia Computação EletrônicaTales Pinheiro VasconcelosNoch keine Bewertungen

- Sist Dig V21Dokument57 SeitenSist Dig V21Nuno CarvalhoNoch keine Bewertungen

- Serie Problemas 2023Dokument12 SeitenSerie Problemas 2023Rafael MedeirosNoch keine Bewertungen

- ACQA - Sistemas Digitais MicrocontroladosDokument5 SeitenACQA - Sistemas Digitais MicrocontroladosHeder RezendeNoch keine Bewertungen

- Sistemas Digitais II Slides 1Dokument52 SeitenSistemas Digitais II Slides 1Benvindo XavierNoch keine Bewertungen

- Aula 07 - Projeto de Circuitos CombinacionaisDokument22 SeitenAula 07 - Projeto de Circuitos CombinacionaisLuciana Recart CardosoNoch keine Bewertungen

- Balanceamento de uma linha de produção em 4 PTsDokument8 SeitenBalanceamento de uma linha de produção em 4 PTsEric MansurNoch keine Bewertungen

- SEL0414 Lista1Dokument4 SeitenSEL0414 Lista1Comi SaudavelNoch keine Bewertungen

- l3 - Circ Log Comb - 16 v4Dokument3 Seitenl3 - Circ Log Comb - 16 v4marcus correiaNoch keine Bewertungen

- APOSTILA - Balanceamento de Uma Linha de Produção PDFDokument11 SeitenAPOSTILA - Balanceamento de Uma Linha de Produção PDFRenan SantosNoch keine Bewertungen

- Contadores DigitaisDokument5 SeitenContadores DigitaisRicardo AkermanNoch keine Bewertungen

- Projeto Jogo Batalha Naval 4x4Dokument2 SeitenProjeto Jogo Batalha Naval 4x4Maira GomesNoch keine Bewertungen

- Ficha Log 2017Dokument1 SeiteFicha Log 2017Leonor MariaNoch keine Bewertungen

- Bases de Numeração e AritméticaDokument17 SeitenBases de Numeração e AritméticaJuliano Oliveira DiasNoch keine Bewertungen

- Programação em CLP ATOSDokument4 SeitenProgramação em CLP ATOSGabriel DiodatoNoch keine Bewertungen

- Princípios de Comunicação: Lista de Exercícios No1Dokument5 SeitenPrincípios de Comunicação: Lista de Exercícios No1diogo edlerNoch keine Bewertungen

- LE4: Circuitos Sequencias: Latches (Aula 5-1)Dokument5 SeitenLE4: Circuitos Sequencias: Latches (Aula 5-1)anyaNoch keine Bewertungen

- Modelação e Simulação: V - de Forma Simplificada, Um Altifalante Consiste NumaDokument5 SeitenModelação e Simulação: V - de Forma Simplificada, Um Altifalante Consiste NumaFrancisco RosaNoch keine Bewertungen

- Eletrônica de Potência IDokument45 SeitenEletrônica de Potência IRafael MironNoch keine Bewertungen

- Respostas Exercicio Fenomenos de TrasnporteDokument5 SeitenRespostas Exercicio Fenomenos de TrasnporteRafael MironNoch keine Bewertungen

- Exercícios Med Grand MecDokument10 SeitenExercícios Med Grand MecRafael MironNoch keine Bewertungen

- AjustesDokument76 SeitenAjustesRafael MironNoch keine Bewertungen

- LogixPro Introdução Lógica RelésDokument6 SeitenLogixPro Introdução Lógica RelésValdir Silva100% (1)

- AjustesDokument76 SeitenAjustesRafael MironNoch keine Bewertungen

- TCC Pic PDFDokument55 SeitenTCC Pic PDFRafael MironNoch keine Bewertungen

- EC1 ExerciciosDokument170 SeitenEC1 ExerciciosLetícia CâmaraNoch keine Bewertungen

- AjustesDokument44 SeitenAjustesRafael MironNoch keine Bewertungen

- Apostila 1Dokument97 SeitenApostila 1Rafael MironNoch keine Bewertungen

- Apostila PMDokument248 SeitenApostila PMPaulo SideresNoch keine Bewertungen

- Guia Ref PDFDokument79 SeitenGuia Ref PDFRafael MironNoch keine Bewertungen

- EI Cap4 Comando e Proteção Jul15Dokument14 SeitenEI Cap4 Comando e Proteção Jul15Rafael MironNoch keine Bewertungen

- Apostila 1Dokument97 SeitenApostila 1Rafael MironNoch keine Bewertungen

- Elementos Da Eletrônica Digital - Idoeta & Capuano PDFDokument271 SeitenElementos Da Eletrônica Digital - Idoeta & Capuano PDFAndré S Rocha50% (2)

- IntroFiltros PDFDokument27 SeitenIntroFiltros PDFRafael MironNoch keine Bewertungen

- EI Cap6 Sist Aux Mar15 RevDokument9 SeitenEI Cap6 Sist Aux Mar15 RevRafael MironNoch keine Bewertungen

- EI Cap5 Dimens Condut Jun15Dokument25 SeitenEI Cap5 Dimens Condut Jun15Rafael MironNoch keine Bewertungen

- Cartilha Do EstudanteDokument28 SeitenCartilha Do EstudanteFernanda BeatrizNoch keine Bewertungen

- Modelo de Relatório. 2015Dokument2 SeitenModelo de Relatório. 2015Rafael MironNoch keine Bewertungen

- Os desafios da música lírica em AngolaDokument30 SeitenOs desafios da música lírica em AngolaNúrio VenâncioNoch keine Bewertungen

- Sequência Didática FábulasDokument34 SeitenSequência Didática FábulasKelin Albani SchwaabNoch keine Bewertungen

- Infecções HospitalaresDokument11 SeitenInfecções HospitalaresLéuzia casteloNoch keine Bewertungen

- Pontualidade na EscolaDokument1 SeitePontualidade na EscolaMarcio Luiz EwaldNoch keine Bewertungen

- Material Concurso - Resumo Currículo PDFDokument5 SeitenMaterial Concurso - Resumo Currículo PDFKaIque StefannoNoch keine Bewertungen

- Plano de Contas DetalhadoDokument12 SeitenPlano de Contas DetalhadoKaryn FerreiraNoch keine Bewertungen

- Arte Pré-Histórica: Paleolítico e NeolíticoDokument2 SeitenArte Pré-Histórica: Paleolítico e NeolíticoFulano TalNoch keine Bewertungen

- G551 1823 - BA - Rev 0 1 0 - 2017 06 28 - PTBDokument76 SeitenG551 1823 - BA - Rev 0 1 0 - 2017 06 28 - PTBlincon com.brNoch keine Bewertungen

- Exercício de HTML e CSS - Arquivo 2Dokument5 SeitenExercício de HTML e CSS - Arquivo 2Pedro PauloNoch keine Bewertungen

- Estilistas Da Moda Afro Brasileira A Identidade Que Se TraduzDokument12 SeitenEstilistas Da Moda Afro Brasileira A Identidade Que Se TraduzWeslley OliveiraNoch keine Bewertungen

- Adesão à Ata de Registro de Preço para serviços de iluminação públicaDokument416 SeitenAdesão à Ata de Registro de Preço para serviços de iluminação públicaChouji FragosoNoch keine Bewertungen

- Sem Isolamento: Etnografia de Pessoas em Situação de Rua Na Pandemia de Covid-19Dokument8 SeitenSem Isolamento: Etnografia de Pessoas em Situação de Rua Na Pandemia de Covid-19Ana De Moraes QuintasNoch keine Bewertungen

- Catalogo2022 V1.0Dokument113 SeitenCatalogo2022 V1.0DLR SOLUTIONS LIMEIRANoch keine Bewertungen

- IST Transferencia de Massa PDFDokument27 SeitenIST Transferencia de Massa PDFxcite4everNoch keine Bewertungen

- Cifras Ceia Do Senhor 2020Dokument12 SeitenCifras Ceia Do Senhor 2020Milton AlvesNoch keine Bewertungen

- Patologias em DermatologiaDokument8 SeitenPatologias em DermatologiaCristiane SlugovieskiNoch keine Bewertungen

- Talhas Berg-SteelDokument2 SeitenTalhas Berg-SteelFrederico Marconi CosenzaNoch keine Bewertungen

- Apresentação no TemploDokument52 SeitenApresentação no TemploPauloViníciusCostaOliveiraNoch keine Bewertungen

- Você É Precioso para Ele - David Wilkerson PDFDokument9 SeitenVocê É Precioso para Ele - David Wilkerson PDFAnonymous ncYGha5Noch keine Bewertungen

- Investigação Da Condutividade Elétrica em Solução de KCL A 0,01MDokument3 SeitenInvestigação Da Condutividade Elétrica em Solução de KCL A 0,01MbrumaiafotosNoch keine Bewertungen

- Cristalografia e formas dos mineraisDokument24 SeitenCristalografia e formas dos mineraisOsmar Juazeiro0% (1)

- LISTA 03 - Aulas 01 Até 06 - EsPCEx - Fusos HorariosDokument6 SeitenLISTA 03 - Aulas 01 Até 06 - EsPCEx - Fusos HorariosJoel Rossato FilhoNoch keine Bewertungen