Beruflich Dokumente

Kultur Dokumente

Address Decoding

Hochgeladen von

Veeranjaneyulu DhikondaCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Address Decoding

Hochgeladen von

Veeranjaneyulu DhikondaCopyright:

Verfügbare Formate

10/25/2017 Address Decoding

Address Decoding

On the 6800 CPU, the memory space is 64K bytes as there are 16 address lines and the data bus

is 8-bits.

The method that we use to select the correct location on the correct chip is called address

decoding and we use the address bus to accomplish the selection. Notice that it is critical that

each address selects a unique location.

Each chip (whether it is a memory chip or a peripheral device chip) has an input called chip select

or enable. These inputs can be active low or active high. If active low, we must send a logic "0" (0

volts) to this input, to enable it, because it uses negative logic. If there is a logic "1" (+5 volts)

connected to this input, the chip is inactive.

If active high, a logic "1" on this input selects the device and a logic "0" on the input disables it. The

fact that we can activate or deactivate a chip allows us to select the correct chip for a particular

address.

When you specify a particular address, the corresponding location exists only in one of those

chips. Part of the address selects the correct chip (the upper part of the address), while the rest of

the address selects the correct location on that chip. You can look at the low order bits as forming

an offset from the first location on the chip to the correct location on the chip for the address you

are specifying.

Address Decoding can be achieved using:

1) Combinational Logic, (AND, NAND, OR, NOR and INVERTERS)

2) Address Decoders (2 to 4, 3 to 8, etc.),

3) Programmable Logic Device:

bu Programmable Logic Array (PLA),

bu Programmable Array Logic (PAL),

bu Gated Array Logic(GAL).

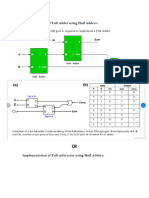

EXAMPLE 1:

Show how a single 2-line to 4-line decoder whose outputs, and a single gate enable input, are all

active low could be used to fully decode four 4K x 8 EPROMS, having an active low Chip Select

(/CS) line, from address $0000 to $3FFF. Assume that the system has a 16-bit address bus and an

8-bit data bus.

First, we will specify all sixteen addresses in binary, showing which address lines will have high

voltage ("1") and which will have low voltage ("0") for any particular address.

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

$0000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

BLOCK 0

$0FFF 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1

BLOCK 1 $1000 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0

http://www.electronics.dit.ie/staff/tscarff/6800/Address_dec_6800/address_decoding.htm 1/2

10/25/2017 Address Decoding

$1FFF 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1

$2000 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0

BLOCK 2

$2FFF 0 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1

$3000 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0

BLOCK 3

$3FFF 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1

The Truth Table for 2 to 4 Decoder

http://www.electronics.dit.ie/staff/tscarff/6800/Address_dec_6800/address_decoding.htm 2/2

Das könnte Ihnen auch gefallen

- Micropro Compilation ReinierDokument16 SeitenMicropro Compilation ReinierKei DeeNoch keine Bewertungen

- Elec 2210 - Experiment 1 Basic Digital Logic Circuits: ObjectivesDokument5 SeitenElec 2210 - Experiment 1 Basic Digital Logic Circuits: ObjectivesSameer IbrahimNoch keine Bewertungen

- Birla Institute of Technology and ScienceDokument19 SeitenBirla Institute of Technology and ScienceAniruddha KarveNoch keine Bewertungen

- 68HC11 Introduction.: Bits and BytesDokument22 Seiten68HC11 Introduction.: Bits and BytesmohanaakNoch keine Bewertungen

- Led LCDDokument19 SeitenLed LCDSoumya Ranjan PandaNoch keine Bewertungen

- 1b. CS602 Microprocessor and Microcontroller - Memory Interfacing - 5+1 ExamplesDokument14 Seiten1b. CS602 Microprocessor and Microcontroller - Memory Interfacing - 5+1 ExamplesRehan NightNoch keine Bewertungen

- TI 32k ModDokument10 SeitenTI 32k Modoscar tebarNoch keine Bewertungen

- Data Hasil Percobaan: Tabel 6.1. Rangkaian Encoder 8 To 3Dokument2 SeitenData Hasil Percobaan: Tabel 6.1. Rangkaian Encoder 8 To 3fardanNoch keine Bewertungen

- Solution of Homework#06Dokument10 SeitenSolution of Homework#06farahNoch keine Bewertungen

- Solution of Homework#06Dokument10 SeitenSolution of Homework#06hamim ahmedNoch keine Bewertungen

- DEMSTDokument10 SeitenDEMSTSaloni VaniNoch keine Bewertungen

- Laboratory 5 AnswersDokument3 SeitenLaboratory 5 AnswersJenemarNoch keine Bewertungen

- ECE3073 P4 Bus Interfacing Answers PDFDokument3 SeitenECE3073 P4 Bus Interfacing Answers PDFkewancamNoch keine Bewertungen

- Dataholster Project Package: DisclaimersDokument29 SeitenDataholster Project Package: DisclaimersPurp TrapNoch keine Bewertungen

- SC2240B OTP EncoderDokument3 SeitenSC2240B OTP EncoderGary Daniels ANoch keine Bewertungen

- Decodere and Ncoder: ObjectivesDokument3 SeitenDecodere and Ncoder: ObjectivesIqea janNoch keine Bewertungen

- ISO Magnetic Stripe Card StandardsDokument4 SeitenISO Magnetic Stripe Card Standardschparrab0% (1)

- Digital Logic Design Lab 11Dokument3 SeitenDigital Logic Design Lab 11M. Ahmad RazaNoch keine Bewertungen

- cs502snscm4 PDFDokument26 Seitencs502snscm4 PDFTheStupidityOfPplNoch keine Bewertungen

- Exp 8 (DLD)Dokument4 SeitenExp 8 (DLD)shah hassaanNoch keine Bewertungen

- Tribhuvan University Institute of Engineering Pulchowk, Lalipur A Lab Report On Embedded SystemDokument22 SeitenTribhuvan University Institute of Engineering Pulchowk, Lalipur A Lab Report On Embedded SystemSaroj KatwalNoch keine Bewertungen

- ManualDokument21 SeitenManualRamaDinakaran100% (1)

- Lab 9 Encoders and DecodersDokument7 SeitenLab 9 Encoders and Decoderssafdarmunir070Noch keine Bewertungen

- Exp 8 DecoderDokument4 SeitenExp 8 DecoderabdallaNoch keine Bewertungen

- MODbus Communication Protocol 2017-1-11Dokument30 SeitenMODbus Communication Protocol 2017-1-11Anh NguyễnNoch keine Bewertungen

- PCDokument25 SeitenPCPrasun BiswasNoch keine Bewertungen

- Title:Implementation of 4-Line-To - 2-Line Encoder & 8-Line-To-3-Line Encoder Lab Worksheet #10Dokument5 SeitenTitle:Implementation of 4-Line-To - 2-Line Encoder & 8-Line-To-3-Line Encoder Lab Worksheet #10MUNEEB SHAHNoch keine Bewertungen

- Xilinx Spartax XC3S400 TQG1445PQ034 D3057375A 4CDokument19 SeitenXilinx Spartax XC3S400 TQG1445PQ034 D3057375A 4CVenugopal PonnurajNoch keine Bewertungen

- 8085 PRJ Schematic 1Dokument44 Seiten8085 PRJ Schematic 1Jani ServiniNoch keine Bewertungen

- Using Ostinato V1-0Dokument16 SeitenUsing Ostinato V1-0JOEL RAMIREZNoch keine Bewertungen

- 1-Basics of MicroprocessorDokument9 Seiten1-Basics of Microprocessorafzal_a100% (1)

- Fanuc 0T-C RS232 ParameterDokument1 SeiteFanuc 0T-C RS232 ParameterNestor Hugo Garcia RomoNoch keine Bewertungen

- 8051 Internal ArchitectureDokument16 Seiten8051 Internal ArchitectureDr-Samson ChepuriNoch keine Bewertungen

- ST Micro Interview Questions For Circuit DesignDokument10 SeitenST Micro Interview Questions For Circuit DesignvenegallaraghuNoch keine Bewertungen

- 2016 Summer Model Answer PaperDokument28 Seiten2016 Summer Model Answer Paperharshalkhandar1Noch keine Bewertungen

- MicroprocessorDokument44 SeitenMicroprocessorgaur saab100% (1)

- Input and Output (I/O)Dokument17 SeitenInput and Output (I/O)Chandru PrasathNoch keine Bewertungen

- Kode SBCDICDokument3 SeitenKode SBCDICMamanJosh Scott KennedyNoch keine Bewertungen

- Cao Lab ManualDokument28 SeitenCao Lab Manualabhisheksingh89208Noch keine Bewertungen

- Chapter 12Dokument5 SeitenChapter 12Saad LatifNoch keine Bewertungen

- 8051 InterfacingDokument6 Seiten8051 Interfacingravi sainiNoch keine Bewertungen

- Notes DEE604 Unit1Dokument16 SeitenNotes DEE604 Unit1arselankhan9415Noch keine Bewertungen

- MULTIPLXERSDokument6 SeitenMULTIPLXERSdetectionisimpressionNoch keine Bewertungen

- Lab1 MicropDokument11 SeitenLab1 MicropFauzan AriqNoch keine Bewertungen

- 4, Encoder & Decoder MUX and DEMUX EEngDokument46 Seiten4, Encoder & Decoder MUX and DEMUX EEngIsrael EliasNoch keine Bewertungen

- Week 8 - Module 7 Design of Combinational Circuits 2Dokument8 SeitenWeek 8 - Module 7 Design of Combinational Circuits 2Ben GwenNoch keine Bewertungen

- Digital Electronics Circuit: Assignment - 2Dokument28 SeitenDigital Electronics Circuit: Assignment - 2Rubal SharmaNoch keine Bewertungen

- 1.internal Architecture 1Dokument19 Seiten1.internal Architecture 1Dr-Samson ChepuriNoch keine Bewertungen

- Capitulo 3Dokument15 SeitenCapitulo 3Juan GonzalesNoch keine Bewertungen

- Microcontrollers Lab 18ECL47: Vtu SyllabusDokument66 SeitenMicrocontrollers Lab 18ECL47: Vtu SyllabusRamesh HegdeNoch keine Bewertungen

- CM12-16 DescriptionDokument6 SeitenCM12-16 DescriptionJoscatNoch keine Bewertungen

- DecoderDokument7 SeitenDecodervaani munjalNoch keine Bewertungen

- DLD Lecture 4Dokument53 SeitenDLD Lecture 4sjbv.hardik582Noch keine Bewertungen

- ADE - Exp 6Dokument16 SeitenADE - Exp 6shashwatNoch keine Bewertungen

- AAROH-A Step Towards Real Engineering: Day2 Seven Segment DisplayDokument9 SeitenAAROH-A Step Towards Real Engineering: Day2 Seven Segment DisplayBrajesh ChouhanNoch keine Bewertungen

- Combinational Circuits - 3Dokument76 SeitenCombinational Circuits - 3harshulyagnik.cseNoch keine Bewertungen

- Atmega 2560 Ingles (031-060)Dokument30 SeitenAtmega 2560 Ingles (031-060)Yovan MamaniNoch keine Bewertungen

- Course of Digital Techniques Lectures2 017 - PDF - 1Dokument51 SeitenCourse of Digital Techniques Lectures2 017 - PDF - 1juber mullaNoch keine Bewertungen

- Decoder ProblemDokument3 SeitenDecoder ProblemrayNoch keine Bewertungen

- Memory PDFDokument27 SeitenMemory PDFVeeranjaneyulu DhikondaNoch keine Bewertungen

- Built-In Self-Test Technique For Selective Detection of Neighbourhood Pattern Sensitive Faults in MemoriesDokument4 SeitenBuilt-In Self-Test Technique For Selective Detection of Neighbourhood Pattern Sensitive Faults in MemoriesVeeranjaneyulu DhikondaNoch keine Bewertungen

- Channel Connected ComponentDokument5 SeitenChannel Connected ComponentVeeranjaneyulu DhikondaNoch keine Bewertungen

- Hiertest RAK Lab 16.1Dokument41 SeitenHiertest RAK Lab 16.1Veeranjaneyulu Dhikonda100% (1)

- DetectedDokument1 SeiteDetectedVeeranjaneyulu DhikondaNoch keine Bewertungen

- DDR WriteDokument50 SeitenDDR WriteVeeranjaneyulu Dhikonda100% (1)

- Early Effect - WikipediaDokument6 SeitenEarly Effect - WikipediaVeeranjaneyulu DhikondaNoch keine Bewertungen

- Memory BIST PDFDokument52 SeitenMemory BIST PDFMuralikrishna UttaradiNoch keine Bewertungen

- Analog Circuits - Unit 2 - Week 1 - Obtaining Power Gain-Need For NonlinearityDokument7 SeitenAnalog Circuits - Unit 2 - Week 1 - Obtaining Power Gain-Need For NonlinearityVeeranjaneyulu DhikondaNoch keine Bewertungen

- Boundary Scan: - Developed To Test Interconnect Between Chips On PCBDokument8 SeitenBoundary Scan: - Developed To Test Interconnect Between Chips On PCBVeeranjaneyulu DhikondaNoch keine Bewertungen

- Edt GDDokument330 SeitenEdt GDVeeranjaneyulu DhikondaNoch keine Bewertungen

- SDF To Verilog Construct MatchingDokument3 SeitenSDF To Verilog Construct MatchingVeeranjaneyulu DhikondaNoch keine Bewertungen

- New Microsoft Office Word DocumentDokument35 SeitenNew Microsoft Office Word DocumentVeeranjaneyulu DhikondaNoch keine Bewertungen

- 1100Dokument51 Seiten1100Veeranjaneyulu DhikondaNoch keine Bewertungen

- Vim Commands Cheat SheetDokument7 SeitenVim Commands Cheat SheetVeeranjaneyulu DhikondaNoch keine Bewertungen

- Guanhao Yunyi TalkDokument35 SeitenGuanhao Yunyi TalkVeeranjaneyulu DhikondaNoch keine Bewertungen

- 4 2paper PDFDokument12 Seiten4 2paper PDFVeeranjaneyulu DhikondaNoch keine Bewertungen

- Design For Test - DFT Q & A - Part 1Dokument3 SeitenDesign For Test - DFT Q & A - Part 1Veeranjaneyulu Dhikonda0% (1)

- 15-Chapter 10 BSCAN 1500 PDFDokument81 Seiten15-Chapter 10 BSCAN 1500 PDFVeeranjaneyulu DhikondaNoch keine Bewertungen

- 21 FSM ExamplesDokument4 Seiten21 FSM ExamplesvikramkolanuNoch keine Bewertungen

- TCL OperatorsDokument4 SeitenTCL OperatorsVeeranjaneyulu DhikondaNoch keine Bewertungen

- TCL File I/O: Opening FilesDokument4 SeitenTCL File I/O: Opening FilesVeeranjaneyulu DhikondaNoch keine Bewertungen

- ASIC-System On Chip-VLSI Design - Setup TimeDokument5 SeitenASIC-System On Chip-VLSI Design - Setup TimeVeeranjaneyulu DhikondaNoch keine Bewertungen

- 0310 PDFDokument51 Seiten0310 PDFGunjan JhaNoch keine Bewertungen

- Lab 3 - Top-Down ASIC Design With DFTDokument16 SeitenLab 3 - Top-Down ASIC Design With DFTVeeranjaneyulu DhikondaNoch keine Bewertungen

- TCL File I/O: Opening FilesDokument4 SeitenTCL File I/O: Opening FilesVeeranjaneyulu DhikondaNoch keine Bewertungen

- TCL Regular ExpressionsDokument5 SeitenTCL Regular ExpressionsVeeranjaneyulu DhikondaNoch keine Bewertungen

- Pratical Exam QPDokument4 SeitenPratical Exam QPrajec99Noch keine Bewertungen

- Intro SDL SuiteDokument32 SeitenIntro SDL Suitegsmman2006Noch keine Bewertungen

- Cloud StorageDokument5 SeitenCloud StoragejunigrNoch keine Bewertungen

- Superstar 3900EDokument34 SeitenSuperstar 3900EsoehtNoch keine Bewertungen

- CMW500 - Wireless Device Production Test PDFDokument34 SeitenCMW500 - Wireless Device Production Test PDFAlvaro Cea CamposNoch keine Bewertungen

- OS NotesDokument8 SeitenOS NotesPritam KiskuNoch keine Bewertungen

- Tisoft 2 ManualDokument418 SeitenTisoft 2 ManualDaniel100% (1)

- IOS Security Guide Oct 2014Dokument50 SeitenIOS Security Guide Oct 2014Vishwas GuptaNoch keine Bewertungen

- Darktrace Appliance Specs (DCIP-S DCIP-M DCPI-X DCIP-Z)Dokument2 SeitenDarktrace Appliance Specs (DCIP-S DCIP-M DCPI-X DCIP-Z)Aristides QuispeNoch keine Bewertungen

- Lecture9 Memory OrganizationDokument32 SeitenLecture9 Memory Organizationecevitmert1453Noch keine Bewertungen

- Catalogo FESTOONDokument68 SeitenCatalogo FESTOONmaciasrobNoch keine Bewertungen

- Trimco CatalogDokument72 SeitenTrimco CatalogscribdnowayNoch keine Bewertungen

- R-5000Series 230231325A RelNotes PDFDokument17 SeitenR-5000Series 230231325A RelNotes PDFBayu Yudi PrasajaNoch keine Bewertungen

- PowerShell Chapter 3 LabDokument3 SeitenPowerShell Chapter 3 LabkuproporufNoch keine Bewertungen

- CSO Computer ProgrammingDokument73 SeitenCSO Computer ProgrammingAjNoch keine Bewertungen

- Training Manual LSEDokument530 SeitenTraining Manual LSEBulu Mihai100% (1)

- Linear and Non Linear TextDokument26 SeitenLinear and Non Linear TextMartha Andrea PatcoNoch keine Bewertungen

- CompX Security Products Catalog, Nov 2009Dokument20 SeitenCompX Security Products Catalog, Nov 2009Kip LavingerNoch keine Bewertungen

- CircuitDokument25 SeitenCircuitSubhajit ChakrabortyNoch keine Bewertungen

- PyGTK TutorialDokument412 SeitenPyGTK TutorialMarcel CaracioloNoch keine Bewertungen

- Clare CupDokument5 SeitenClare CuphelpieNoch keine Bewertungen

- 5 Computer All MCQsDokument176 Seiten5 Computer All MCQsFaisal NadeemNoch keine Bewertungen

- Glitch Works 8085 SBC Rev 3 GW-8085SBC-3: User's Manual and Assembly GuideDokument17 SeitenGlitch Works 8085 SBC Rev 3 GW-8085SBC-3: User's Manual and Assembly Guidegord12Noch keine Bewertungen

- Errors 7800Dokument1 SeiteErrors 7800Глеб НутельсNoch keine Bewertungen

- Final Cut ProDokument16 SeitenFinal Cut ProRijy LoranceNoch keine Bewertungen

- Toshiba SD 120 220 e SMDokument104 SeitenToshiba SD 120 220 e SMenergiculNoch keine Bewertungen

- PIC18F4550 Timer Capture (CCP) Mode - PIC ControllersDokument6 SeitenPIC18F4550 Timer Capture (CCP) Mode - PIC ControllersKrishanu Modak100% (1)

- Fan 7392NDokument18 SeitenFan 7392NKhaleel MohammadNoch keine Bewertungen

- Research Papers On Analog Integrated CircuitsDokument4 SeitenResearch Papers On Analog Integrated Circuitsafmcmuugo100% (1)

- HMT Pinjore HaryanaDokument12 SeitenHMT Pinjore HaryanaAnurag KumarNoch keine Bewertungen