Beruflich Dokumente

Kultur Dokumente

Jeu d'Instructions ΜC 16F84

Hochgeladen von

Khalil FatehCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Jeu d'Instructions ΜC 16F84

Hochgeladen von

Khalil FatehCopyright:

Verfügbare Formate

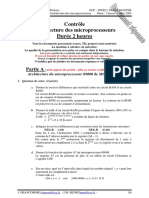

Jeu d'instructions des PIC 16F84A,

16F628A, 16F88, 16F876A et 16F886

Les PIC 16F84A, 16F628A, 16F88, 16F876A, 16F886 (famille mid-range) ont le

mme jeu d'instructions, constitu de seulement 35 instructions (architecture RISC

:Reduced Instruction-Set Computer).

Une instruction est code par un mot de 14 bits.

La mmoire programme (de type Flash) a une taille de :

1792 octets (16F84A)

3584 octets (16F628A)

7168 octets (16F88)

14 336 octets (16F876A - 16F886)

ce qui permet de stocker un programme de :

1024 instructions (16F84A)

2048 instructions (16F628A)

4096 instructions (16F88)

8192 instructions (16F876A - 16F886)

Une instruction ncessite 1 cycle, ou bien 2 cycles dans le cas d'une instruction de

branchement (GOTO, CALL ...).

Avec une horloge quartz de 20 MHz, un cycle correspond 4/(20.106) = 200

nanosecondes.

Le microcontrleur peut donc excuter jusqu' 5 millions d'instructions par seconde

(5 MIPS) !

Jeu d'instructions

W : registre de travail (accumulateur), taille 8 bits

k : valeur littrale, taille 8 bits

Mnmonique, bit du registre nombre de

Description

oprande STATUS affect cycles

MOVLW k k (8 bits) est charg dans (W) - 1

ADDLW k Additionne k (8 bits) et (W) et

C, DC, Z 1

place le rsultat dans (W)

SUBLW k Soustrait W de k (8 bits) et

place le rsultat dans (W) C, DC, Z 1

k - (W) -> (W)

ANDLW k Ralise un ET logique entre k

(8 bits) et (W), et place le Z 1

rsultat dans (W)

IORLW k Ralise un OU logique

(inclusif) entre k (8 bits) et

Z 1

(W), et place le rsultat dans

(W)

XORLW k Ralise un OU exclusif entre k

(8 bits) et (W), et place le Z 1

rsultat dans (W)

L : label (tiquette)

Mnmonique, bit du registre nombre de

Description

oprande STATUS affect cycles

GOTO L Branchement l'adresse L - 2

CALL L Appelle un sous-programme

(subroutine) situ l'adresse - 2

L

RETURN Retour de sous-programme - 2

RETLW k Retour de sous-programme,

avec chargement de la valeur - 2

littrale k (8 bits) dans (W)

RETFIE Retour de sous-programme

- 2

d'interruption

CLRWDT Efface le Watchdog /TO, /PD 1

SLEEP Place le microcontrleur en

/TO, /PD 1

mode sommeil

f : registre (spcial ou d'usage gnral)

b : position du bit (0 7)

Mnmonique, bit du registre nombre

Description

oprande STATUS affect de cycles

BCF f , b Mise 0 du bme bit du

- 1

registre f

BSF f , b Mise 1 du bme bit du

- 1

registre f

BTFSC f , b Si le bme bit du registre f est

gal 0, alors l'instruction

suivante est ignore, et une

- 1 ou 2

instruction NOP est

excute la place (soit 2

cycles)

BTFSS f , b Si le bme bit du registre f est

gal 1, alors l'instruction

suivante est ignore, et une

- 1 ou 2

instruction NOP est

excute la place (soit 2

cycles)

f : registre (spcial ou d'usage gnral)

d : registre de destination (on peut choisir entre le registre de travail W et

le registre f).

bit du

registre

Mnmonique, nombre

Description STATU

oprande de cycles

S

affect

MOVWF f (W) est charg dans (f) - 1

MOVF f , d (f) (8 bits) est charg dans (destination) Z 1

ADDWF f , d Additionne le contenu du registre f (8 bits)

C, DC,

et (W), et place le rsultat dans 1

Z

(destination)

SUBWF f , d Soustrait (W) de (f) (8 bits) et place le

C, DC,

rsultat dans (destination). 1

Z

(f) - (W) ->(destination)

ANDWF f , d Ralise un ET logique entre (f) (8 bits) et

Z 1

(W), et place le rsultat dans (destination)

IORWF f , d Ralise un OU logique (inclusif) entre (f)

(8 bits) et (W), et place le rsultat dans Z 1

(destination)

XORWF f , d Ralise un OU exclusif entre (f) (8 bits) et

Z 1

(W), et place le rsultat dans (destination)

COMF f , d Ralise le complment logique de (f) (8

bits), et place le rsultat dans (destination) Z 1

DECF f, d Dcrmente (f) et place le rsultat dans

(destination). Z 1

(f) - 1 -> (destination)

DECFSZ f, d Dcrmente (f) et place le rsultat dans

(destination).

Si le rsultat est 0, alors l'instruction - 1 ou 2

suivante est ignore, et une instruction

NOP est excute la place (soit 2 cycles)

INCF f, d Incrmente (f) et place le rsultat dans

(destination). Z 1

(f) + 1 -> (destination)

INCFSZ f, d Incrmente (f) et place le rsultat dans

(destination).

Si le rsultat est 0, alors l'instruction - 1 ou 2

suivante est ignore, et une instruction

NOP est excute la place (soit 2 cycles)

CLRF f Efface le contenu du registre (f).

Z 1

Remarque : le bit Z est donc mis 1.

CLRW Efface le contenu de l'accumulateur (W).

Z 1

Remarque : le bit Z est donc mis 1.

RLF f , d Ralise une rotation circulaire gauche :

C 1

Le rsultat est plac dans (destination).

RRF f, d Ralise une rotation circulaire droite :

C 1

Le rsultat est plac dans (destination).

SWAPF f, d Les 4 bits de poids forts et les 4 bits de

poids faibles de (f) sont changs. - 1

Le rsultat est plac dans (destination).

NOP Cette instruction ne fait rien (dure 1

- 1

cycle).

Das könnte Ihnen auch gefallen

- Jeu D'instructions 16F84A 16F628A 16F88 16F876A 16F886Dokument4 SeitenJeu D'instructions 16F84A 16F628A 16F88 16F876A 16F886MoprometheusNoch keine Bewertungen

- Cours 3 - Programmation en Assembleur Du PIC 16F84Dokument41 SeitenCours 3 - Programmation en Assembleur Du PIC 16F84KhadidjaNoch keine Bewertungen

- CH3 Convertisseur AnalogiqueDokument12 SeitenCH3 Convertisseur AnalogiqueMohammed AbdiNoch keine Bewertungen

- Chapitre 5 Systeme de Premier OrdreDokument9 SeitenChapitre 5 Systeme de Premier OrdremoipopNoch keine Bewertungen

- ECE 2004-Corrige PDFDokument6 SeitenECE 2004-Corrige PDFbaydiNoch keine Bewertungen

- 1-Commande D'un Afficheur Et Un PortaileDokument15 Seiten1-Commande D'un Afficheur Et Un PortaileBarchan Yâ SînNoch keine Bewertungen

- Les TimersDokument6 SeitenLes TimersHammadi GharsNoch keine Bewertungen

- Sup'Ptic: Itt2 ANNEE ACADEMIQUE 2017-2018Dokument2 SeitenSup'Ptic: Itt2 ANNEE ACADEMIQUE 2017-2018Angel100% (1)

- TP Initiation A La Programmation Du C PIC 16F84A en Mikro CDokument6 SeitenTP Initiation A La Programmation Du C PIC 16F84A en Mikro CPaty MuyengwaNoch keine Bewertungen

- Les Compteurs ISISDokument10 SeitenLes Compteurs ISISDiego MezaNoch keine Bewertungen

- TP AutomatiqueDokument63 SeitenTP AutomatiqueNabil BounouNoch keine Bewertungen

- TP TemporisationDokument6 SeitenTP TemporisationfaridNoch keine Bewertungen

- A22-Opérations D'arithmétique Binaire - v19 - 2Dokument6 SeitenA22-Opérations D'arithmétique Binaire - v19 - 2Rafik Ben AmorNoch keine Bewertungen

- Devoir D'automatique: 1 Etude PR EliminaireDokument3 SeitenDevoir D'automatique: 1 Etude PR EliminaireZøů HåïŕNoch keine Bewertungen

- Grafcets Ravoux Module 2Dokument12 SeitenGrafcets Ravoux Module 2youri59490Noch keine Bewertungen

- Gestion D'un Feu TricoloreDokument9 SeitenGestion D'un Feu TricolorelfadliNoch keine Bewertungen

- Cours RegistresDokument8 SeitenCours RegistresAnais Nour GhellamNoch keine Bewertungen

- Devoir 3 Si 2 Bac STM Tri de CaisseDokument11 SeitenDevoir 3 Si 2 Bac STM Tri de CaisseHajar Ben GaraâNoch keine Bewertungen

- C - Présentation - Correction - PDF Microcontroleur (2020 - 8 - 10)Dokument8 SeitenC - Présentation - Correction - PDF Microcontroleur (2020 - 8 - 10)WaSsIM100% (1)

- Amplificateur SélectifDokument5 SeitenAmplificateur SélectifOthman NchifaNoch keine Bewertungen

- Système de Gestion de Feux de CarrefourDokument4 SeitenSystème de Gestion de Feux de CarrefourjfNoch keine Bewertungen

- Chapitre 4 Analyse en Régime SinusoïdalDokument3 SeitenChapitre 4 Analyse en Régime SinusoïdalsalimiyounessNoch keine Bewertungen

- Mikroc - Programmation Des PIC - GLT - GSIDokument31 SeitenMikroc - Programmation Des PIC - GLT - GSIImane LamdaineNoch keine Bewertungen

- Exo Machine Automatique CorrectionDokument3 SeitenExo Machine Automatique CorrectionMila zNoch keine Bewertungen

- Upload - Série D'exercices N°10-Pic-2014-2015-CorrectionDokument28 SeitenUpload - Série D'exercices N°10-Pic-2014-2015-CorrectionHabib Ben Ammar100% (2)

- Upload - Résumé Du Cours-Microcontroleurs - 2016-2017Dokument7 SeitenUpload - Résumé Du Cours-Microcontroleurs - 2016-2017Habib Ben AmmarNoch keine Bewertungen

- Leçon A3-2 - Notion D'interruptionDokument6 SeitenLeçon A3-2 - Notion D'interruptionMehdi Bouchami100% (1)

- Cours3 Uc Ports Finale Étudiants PDFDokument10 SeitenCours3 Uc Ports Finale Étudiants PDFYoussef HaidaNoch keine Bewertungen

- Ado 1ap 21-22 TD4Dokument2 SeitenAdo 1ap 21-22 TD4Hamza BoutlihNoch keine Bewertungen

- Labview Cahier TDDokument33 SeitenLabview Cahier TDNajimMdi100% (1)

- TD RedreDokument2 SeitenTD RedreAnas AsranNoch keine Bewertungen

- Systeme de Gestion de Feux de CarrefourDokument4 SeitenSysteme de Gestion de Feux de CarrefourYOUNES KABBAJNoch keine Bewertungen

- Rapport de AKAFFOUDokument16 SeitenRapport de AKAFFOUkpea chris dylanNoch keine Bewertungen

- Cours Et Exercices - Moteurs-Pas-A-PasDokument3 SeitenCours Et Exercices - Moteurs-Pas-A-Paskada saiNoch keine Bewertungen

- TP 1 Info Indus07Dokument15 SeitenTP 1 Info Indus07MOHAMED TAMZAITINoch keine Bewertungen

- Filtres ActifsDokument3 SeitenFiltres ActifsMouad Elmekaoui100% (1)

- 1-Principe de Programmation LadderDokument13 Seiten1-Principe de Programmation LadderElmokh LassaadNoch keine Bewertungen

- Exercices Gracets CoordonnesDokument5 SeitenExercices Gracets CoordonnessaulnierNoch keine Bewertungen

- TD1 ContinuDokument4 SeitenTD1 Continudhaouadi hazemNoch keine Bewertungen

- Corrigé Type Examen Final Microprocesseurs Et API Master ELMDokument4 SeitenCorrigé Type Examen Final Microprocesseurs Et API Master ELMMohammed ALMUSHIAANoch keine Bewertungen

- Devoir de Synthèse N°1 - Génie Électrique Tri de Boitiers - Bac Technique (2014-2015) MR YagoubiDokument8 SeitenDevoir de Synthèse N°1 - Génie Électrique Tri de Boitiers - Bac Technique (2014-2015) MR YagoubiFethi BenmassoudeNoch keine Bewertungen

- CFL02 - Introduction À L'automatisme Sous FluidSIM - Pilotage Des Stations MPSDokument12 SeitenCFL02 - Introduction À L'automatisme Sous FluidSIM - Pilotage Des Stations MPSYassine AzougaghNoch keine Bewertungen

- 05 - ALI Corrige1Dokument14 Seiten05 - ALI Corrige1aissatou dia gayeNoch keine Bewertungen

- Chapitre 3 Filtrage Signaux Deterministes Temps ContinuDokument7 SeitenChapitre 3 Filtrage Signaux Deterministes Temps Continuarbaoui11Noch keine Bewertungen

- Les Codeurs PDFDokument5 SeitenLes Codeurs PDFtarikmlilasNoch keine Bewertungen

- Correction EXamen 2018 Actionneur SpéciauxDokument4 SeitenCorrection EXamen 2018 Actionneur Spéciauxkhaled100% (1)

- 01 - Structure Des Systèmes MicroprogrammésDokument40 Seiten01 - Structure Des Systèmes Microprogrammésrachid BASSELAMNoch keine Bewertungen

- Section Sciences Techniques Epreuve Technologie: Devoir de Controle N°1Dokument5 SeitenSection Sciences Techniques Epreuve Technologie: Devoir de Controle N°1Lotfi NairiNoch keine Bewertungen

- 2systeme EncaissageDokument39 Seiten2systeme Encaissageダークライオン ダークライオンNoch keine Bewertungen

- Série D'exercices N°10 - Génie Électrique - Microcontrôleurs - Bac Technique (2015-2016) MR Raouafi AbdallahDokument8 SeitenSérie D'exercices N°10 - Génie Électrique - Microcontrôleurs - Bac Technique (2015-2016) MR Raouafi AbdallahZak MtcmNoch keine Bewertungen

- Programmes Détaillés S5-S6-Electronique PDFDokument45 SeitenProgrammes Détaillés S5-S6-Electronique PDFWiam KhettabNoch keine Bewertungen

- 151 Exercice Pi Avance Phase PDFDokument3 Seiten151 Exercice Pi Avance Phase PDFZakaria BdrNoch keine Bewertungen

- Exercices PICvers2Dokument3 SeitenExercices PICvers2sanonymeNoch keine Bewertungen

- Parking GrafcetDokument2 SeitenParking GrafcetErragueb Moussaoui IdrissiNoch keine Bewertungen

- Mini Projet - AUTO-maalej PDFDokument8 SeitenMini Projet - AUTO-maalej PDFSarah SfaxiNoch keine Bewertungen

- TP5-1 FeuxDokument6 SeitenTP5-1 FeuxsakiinaNoch keine Bewertungen

- TD2 AssembleurDokument3 SeitenTD2 AssembleurZayneb TekarriNoch keine Bewertungen

- Aide - Memoire - PIC - BTS - BT (Rétabli)Dokument11 SeitenAide - Memoire - PIC - BTS - BT (Rétabli)Gered BiokaNoch keine Bewertungen

- Aide Memoire PIC BTS BTDokument11 SeitenAide Memoire PIC BTS BTsami j15Noch keine Bewertungen

- DVB NGHDokument10 SeitenDVB NGHKhalil FatehNoch keine Bewertungen

- Codes Et TurbocodesDokument408 SeitenCodes Et TurbocodesKhalil FatehNoch keine Bewertungen

- PHD Dore 26102007 VFDokument216 SeitenPHD Dore 26102007 VFKhalil FatehNoch keine Bewertungen

- Rapport de StageDokument75 SeitenRapport de StageKhalil FatehNoch keine Bewertungen

- Astuces de Programmation en Assembleur EN C PDFDokument31 SeitenAstuces de Programmation en Assembleur EN C PDFKhalil FatehNoch keine Bewertungen

- VHDLDokument16 SeitenVHDLKhalil Fateh100% (2)

- Rapport Projet RS232Dokument9 SeitenRapport Projet RS232Khalil Fateh0% (1)

- SYS Up Serie3 12-13 S5 PDFDokument3 SeitenSYS Up Serie3 12-13 S5 PDFlahjaouziNoch keine Bewertungen

- Le Nombre Et Le Type de BipDokument2 SeitenLe Nombre Et Le Type de BipEwan ReynoldsNoch keine Bewertungen

- Camara BLUESTORK QIG - 03072015 All Languages FinalDokument199 SeitenCamara BLUESTORK QIG - 03072015 All Languages FinalprofetecnoesoNoch keine Bewertungen

- VC Plan D'équipement 2018 Base de DonnéesDokument13 SeitenVC Plan D'équipement 2018 Base de Donnéeshocine faliNoch keine Bewertungen

- Cours 6e ModifiéDokument30 SeitenCours 6e ModifiéTheresa Djimele100% (1)

- Rootvg Powerpath FRDokument12 SeitenRootvg Powerpath FRYoussef YouNoch keine Bewertungen

- TP1 KernelDokument6 SeitenTP1 KernelMohamed ES-SEDRATYNoch keine Bewertungen

- Architectures Des Systèmes InformatiquesDokument392 SeitenArchitectures Des Systèmes Informatiquessb aliNoch keine Bewertungen

- SpagyrieDokument27 SeitenSpagyrieGreg FiccaNoch keine Bewertungen

- Analyser Le Processus de Traitement Des Données Du Système D'exploitation.Dokument16 SeitenAnalyser Le Processus de Traitement Des Données Du Système D'exploitation.dualcorefree0% (1)

- Glossaire Ou Jargon InformatiqueDokument4 SeitenGlossaire Ou Jargon InformatiqueAndreNoch keine Bewertungen

- (DIY) Arduino Voiture Télécommandée Par Bluetooth + Code, Câblage PDFDokument1 Seite(DIY) Arduino Voiture Télécommandée Par Bluetooth + Code, Câblage PDFAidoudi Mohamed NidhalNoch keine Bewertungen

- InterruptionDokument28 SeitenInterruptionbellali badreNoch keine Bewertungen

- Bascules Et Compteurs PDFDokument15 SeitenBascules Et Compteurs PDFAva KevinNoch keine Bewertungen

- TD I2cDokument2 SeitenTD I2crukundojtNoch keine Bewertungen

- Examen1 Electronique Et Composants Des SystèmesDokument3 SeitenExamen1 Electronique Et Composants Des Systèmesfouzikr22Noch keine Bewertungen

- 1 SI Et ERP RapportDokument22 Seiten1 SI Et ERP RapportRachid Ben El GhaziNoch keine Bewertungen

- Exam Rattrapage FINAL 05 12 2020Dokument5 SeitenExam Rattrapage FINAL 05 12 2020ihonkNoch keine Bewertungen

- TP2 S EtudiantsDokument5 SeitenTP2 S EtudiantsOussama BouhounNoch keine Bewertungen

- Les InterruptionsDokument10 SeitenLes InterruptionsEL AFOUNoch keine Bewertungen

- TD 4 Pagination & SegDokument2 SeitenTD 4 Pagination & SegDoc TelNoch keine Bewertungen

- Support de Cours Maintenance Informatique LP1 AgitelDokument22 SeitenSupport de Cours Maintenance Informatique LP1 AgitelmutNoch keine Bewertungen

- Gestion de ProcessusDokument42 SeitenGestion de ProcessusLePrinceNoch keine Bewertungen

- Peripheriques 221114 213148Dokument4 SeitenPeripheriques 221114 213148Aaron Stifler ASNoch keine Bewertungen

- Imprimante Laser HP Laserjet Pro M15W Monochrome Wifi (W2G51A) - SYNOTECDokument1 SeiteImprimante Laser HP Laserjet Pro M15W Monochrome Wifi (W2G51A) - SYNOTECBarkaoui brahimNoch keine Bewertungen

- Bultain CderDokument2 SeitenBultain Cderbeddar antarNoch keine Bewertungen

- Facture Format A4 - CopieDokument2 SeitenFacture Format A4 - CopieAnonymous wIeJN9BHNoch keine Bewertungen

- TP1 - InterruptionsDokument11 SeitenTP1 - InterruptionsNesrine BerrahmouneNoch keine Bewertungen