Beruflich Dokumente

Kultur Dokumente

Final Sup Exam

Hochgeladen von

tesfuCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Final Sup Exam

Hochgeladen von

tesfuCopyright:

Verfügbare Formate

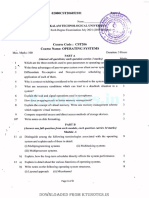

Debre Tabor University

Faculty of Technology

Department of Electrical & Computer Engineering

Computer Architecture & Organization Final Sup exam

Program: Regular 3rd Year Total time allowed: 2.5 hrs

Exam Date: 10/2/10 e.c. Max Mark: 40%

Instructors: Mr. Tesfaye Z., Mr. Tibebu E. Course Code: ECEg 3143

Name ________________________________Id no. ______________________________Sec_____

General Instructions

Write your name and ID number on the space provided.

There are 10 pages in this test, including this cover page. Please check that you

have them all.

Please write neatly. Illegible answers will be assumed to be incorrect.

Any kind of cheating leads you a penalty.

For Instructors use only

P-IV P-V Total

Part P-I (13%) P-II (4%) P-III (13%)

(5%) (5%) (40%)

Marks

Obtained

Good Luck!

Oct 20, 2017 1

Part I: Conceptual Explanation (13%)

1. Compare and contrast direct and indirect Addressing modes?

2. What are the advantages and disadvantages of using a fixed-length

instruction format?

Oct 20, 2017 2

3. Explain what the processor is required to do and the main components

of processor?

4. What is instruction pipelining? Explain pipeline hazard?

Oct 20, 2017 3

5. Mention and explain in detail the common types of registers?

Oct 20, 2017 4

Part II: Short answer (4%)

1. Assume an instruction set that uses a fixed 16-bit instruction

length.Operand specifiers are 6 bits in length. There are K two-operand

instructions and L zero-operand instructions.What is the maximum

number of one-operand instructions that can be supported?

2. If the last operation performed on a computer with an 8-bit word was

an addition in which the two operands were 00000010 and 11111110,

what would be the value of the following flags?

a. Carry flag __________________________________

b. Zero flag __________________________________

c. Overflow flag ___________________________________

d. Sign flag ___________________________________

3. Assume a CPU has 31 different operations. Only register addressing

mode is used, and CPU has 8 user visible registers. The maximum

number of operands allowed in the instruction is three. What should be

the length of the instruction, if fixed-length instruction format is

required?

Oct 20, 2017 5

Part III: Pipeline Hazard (13%)

1. A computer has a ve-stage instruction pipeline of one cycle each. The

ve stages are: Instruction Fetch (IF), Instruction Decode (ID), Operand

Fetch (OF), Instruction Execution (IE), and Operand Store (OS).

Consider the following code sequence, which is to be run on a computer

with 1kHz clock rate.

MOV R1, 2

MOV R4, [100]

ADD R1, R2

ADD R3, R1

a. Calculate the time needed to execute the above code without

pipelining?

b. Calculate (using the Gantts chart below) the number of cycles

needed to execute the above code if the pipeline described above

is used. Assume the approach used to handle pipeline hazard is

Detect and Stall.

Clock cycle

Instructions 1 2 3 4 5 6 7 8 9 10 11 12 13

MOV R1, 2

MOV R4,[100]

ADD R1, R2

ADD R3, R1

Oct 20, 2017 6

c. Calculate the speedup factor.

d. Explain in detail the types of pipeline hazards that occur in the

above program? Explain how and when (at which clock cycle

number) the hazards occurred?

Oct 20, 2017 7

2. What kind of Data hazards are between the following instructions

(Circle one of four):

a. ADD R1, R2

ADD R3, R1

i) RAW ii) WAR iii) WAW iv) None

b. ADD R1, R2

ADD R2, R3

i) RAW ii) WAR iii) WAW iv) None

c. ADD R1, R2

ADD R4, R3

i) RAW ii) WAR iii) WAW iv) None

Oct 20, 2017 8

Part IV: Assembly Program output (5%)

Instruction:

1. Consider the assembly program given below and answer the following

questions.

a. Determine the values of the registers and the memory after the

execution of the program.

b. Describe shortly what the program will do, or what is the application

of the program?

Memory

MOV R1 , 5 99 23

Loop: MOV R2 , [R1+100] 100 105

SUB R2, AC 101 91

JS skipupdating 102 5

MOV AC , [R1+100] 103 90

Skipupdating: DEC R1 104 20

JNZ Loop 105 50

MOV [106], AC 106 0

CPU registers

AC 0

R1 0

R2 0

JS = Jump sign, jump if the previous operation result is negative.

JNZ = Jump not zero, jump if the previous operation result is not zero.

Oct 20, 2017 9

Part V: Writing an Assembly Program (5%)

Instruction:

1. Write an assembly program that calculates the average value of the

numbers located in memory location 11, 12,13,14 & 15, and store the

result in memory location 16.

Your program must use branch instruction and assume the processor

has only four user-visible registers (R1, R2, R3 and AC).

You can assume any machine instructions. But you must describe the

machine instructions you use in your program.

Oct 20, 2017 10

Das könnte Ihnen auch gefallen

- Numerical: Central Processing UnitDokument28 SeitenNumerical: Central Processing UnityounisNoch keine Bewertungen

- Sample Final Exam EECS388 - Fall 2020Dokument19 SeitenSample Final Exam EECS388 - Fall 2020Jeren ChenNoch keine Bewertungen

- Schmidt CoDokument6 SeitenSchmidt CoVirendra SabbanwarNoch keine Bewertungen

- Unit5-Energy Efficiency in Wireless NetworksDokument63 SeitenUnit5-Energy Efficiency in Wireless NetworkstesfuNoch keine Bewertungen

- ArtCAM Pro UserGuide FRADokument511 SeitenArtCAM Pro UserGuide FRAMohammed Lamsalli80% (5)

- Engineering Circuit Analysis 8th Edition Solution PDFDokument4 SeitenEngineering Circuit Analysis 8th Edition Solution PDFhardik saini0% (2)

- OSX Technology OverviewDokument135 SeitenOSX Technology Overviewno000bNoch keine Bewertungen

- H12-211 - Huawei Real Exam Questions - 100% Free - Exam-LabsDokument217 SeitenH12-211 - Huawei Real Exam Questions - 100% Free - Exam-LabsRoman TravinNoch keine Bewertungen

- Result and DiscussionDokument14 SeitenResult and DiscussionJames Carpen Soriano50% (2)

- High Performance Computer Architecture (CS60003)Dokument2 SeitenHigh Performance Computer Architecture (CS60003)Venkata PranavNoch keine Bewertungen

- Mit VliwDokument30 SeitenMit VliwjahNoch keine Bewertungen

- ESD Mid Sem Exam 2019 - KeyDokument5 SeitenESD Mid Sem Exam 2019 - Keyashish6789Noch keine Bewertungen

- CS-3010 (HPC) - CS Mid Sept 2023Dokument7 SeitenCS-3010 (HPC) - CS Mid Sept 2023rajeevkgrd20Noch keine Bewertungen

- Practice Final SolnDokument17 SeitenPractice Final SolnJimmie J MshumbusiNoch keine Bewertungen

- Microcontroller Lab ManualDokument26 SeitenMicrocontroller Lab Manualssmtejani2Noch keine Bewertungen

- Sheet7 SolutionDokument11 SeitenSheet7 SolutionMd. Imran AhmedNoch keine Bewertungen

- cs146 Fall2017 Midterm1xxDokument12 Seitencs146 Fall2017 Midterm1xxgrizzyleoNoch keine Bewertungen

- CS433 hw1 Fall 07Dokument3 SeitenCS433 hw1 Fall 0798140207Noch keine Bewertungen

- CST206 Operating Systems, July 2021Dokument3 SeitenCST206 Operating Systems, July 2021Althaf AsharafNoch keine Bewertungen

- Assignment 1 2020coaDokument5 SeitenAssignment 1 2020coaAmit ChinaraNoch keine Bewertungen

- HW 1 Muhammad Farhan HaniftyajiDokument3 SeitenHW 1 Muhammad Farhan HaniftyajiMuhammad FarhanNoch keine Bewertungen

- 2019 Enel3ds - Exam - MainDokument15 Seiten2019 Enel3ds - Exam - MainNOMPUMELELO MTHETHWANoch keine Bewertungen

- Midtermarch 2Dokument9 SeitenMidtermarch 2Ghina BaassiriNoch keine Bewertungen

- Model QP Os Set 3 UpdatedDokument3 SeitenModel QP Os Set 3 Updatednarenmadhavan5Noch keine Bewertungen

- Aca Midsem2011 Question PaperDokument1 SeiteAca Midsem2011 Question PaperKartik MakkarNoch keine Bewertungen

- CA1 QB For Computer ArchitectureDokument4 SeitenCA1 QB For Computer ArchitectureRajat SharmaNoch keine Bewertungen

- Quiz 1Dokument12 SeitenQuiz 1RexChandu100% (1)

- Indian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Dokument4 SeitenIndian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Utkarsh PatelNoch keine Bewertungen

- CS211 ExamDokument10 SeitenCS211 ExamTetzNoch keine Bewertungen

- CENG400 Midterm Fall 2015Dokument10 SeitenCENG400 Midterm Fall 2015Mohamad IssaNoch keine Bewertungen

- Comp Architecture Sample QuestionsDokument9 SeitenComp Architecture Sample QuestionsMohamaad SihatthNoch keine Bewertungen

- Laboratory - Manual For 8051Dokument20 SeitenLaboratory - Manual For 8051jasoneinsteinNoch keine Bewertungen

- Exam2 Fa2014 SolutionDokument14 SeitenExam2 Fa2014 Solutionrafeak rafeakNoch keine Bewertungen

- Midterm1 Soln Fall09 PDFDokument6 SeitenMidterm1 Soln Fall09 PDFbsudheertecNoch keine Bewertungen

- Ece3003 - MC Cat-1 QP Am - AnsDokument6 SeitenEce3003 - MC Cat-1 QP Am - AnsNanduNoch keine Bewertungen

- 18 MHC 205 JDokument3 Seiten18 MHC 205 JSem 4thNoch keine Bewertungen

- 172 CSE313 FinalDokument3 Seiten172 CSE313 FinalSabbir HossainNoch keine Bewertungen

- BaiTap Chuong123Dokument19 SeitenBaiTap Chuong123Nguyễn Ngọc TúNoch keine Bewertungen

- CS311 ExamDokument16 SeitenCS311 ExamTetzNoch keine Bewertungen

- Your Name:: Final ExamDokument9 SeitenYour Name:: Final ExamDaniel EcheverriaNoch keine Bewertungen

- 06 CS81 ACADec 10Dokument2 Seiten06 CS81 ACADec 10Mohammed YasinNoch keine Bewertungen

- Comparch Comparch-002 Exams Midterm A8Xj46NCRoDokument9 SeitenComparch Comparch-002 Exams Midterm A8Xj46NCRoMattia LeNoch keine Bewertungen

- ESD TutoDokument5 SeitenESD TutoSwaroop MohapatraNoch keine Bewertungen

- Cs2106 1617s1 Midterm SolutionDokument13 SeitenCs2106 1617s1 Midterm SolutionReynard ArdianNoch keine Bewertungen

- C) A Software Application Used To Test A Single Software ComponentDokument4 SeitenC) A Software Application Used To Test A Single Software ComponentMarin AlexNoch keine Bewertungen

- Microprocessors: Familiarization With The Edsim51 Simulator and The 8051 Instruction SetDokument11 SeitenMicroprocessors: Familiarization With The Edsim51 Simulator and The 8051 Instruction SetDioselle CastilloNoch keine Bewertungen

- Assignment Solution Week11Dokument5 SeitenAssignment Solution Week11Rahi SarkarNoch keine Bewertungen

- M116C 1 EE116C-Midterm2-w15 SolutionDokument8 SeitenM116C 1 EE116C-Midterm2-w15 Solutiontinhtrilac100% (1)

- Hw4 SolutionDokument14 SeitenHw4 SolutionTun LeNoch keine Bewertungen

- National University of Computer and Emerging Sciences, Lahore CampusDokument4 SeitenNational University of Computer and Emerging Sciences, Lahore CampusxxxNoch keine Bewertungen

- ECE 341 Final Exam Solution: Problem No. 1 (10 Points)Dokument9 SeitenECE 341 Final Exam Solution: Problem No. 1 (10 Points)bsudheertecNoch keine Bewertungen

- Computer Architecture Quiz-II SolutionDokument4 SeitenComputer Architecture Quiz-II SolutionAkram MohammadNoch keine Bewertungen

- Exit Exam Mode1 ECE ComputerDokument54 SeitenExit Exam Mode1 ECE ComputerBerentoNoch keine Bewertungen

- Question Paper Code: 17071: Reg. NoDokument6 SeitenQuestion Paper Code: 17071: Reg. NoHari RamNoch keine Bewertungen

- Final Exam CAAL 2020Dokument3 SeitenFinal Exam CAAL 2020hassanNoch keine Bewertungen

- Assessment 1Dokument9 SeitenAssessment 1Shivam SinghNoch keine Bewertungen

- EXAMDec2012 SolutionDokument8 SeitenEXAMDec2012 Solutionخالد ناهض نايف نجمNoch keine Bewertungen

- MC MergedDokument506 SeitenMC Mergedsadanand joriNoch keine Bewertungen

- PLCDokument3 SeitenPLCgowthaman rajNoch keine Bewertungen

- PLCDokument3 SeitenPLCgowthaman rajNoch keine Bewertungen

- Ricochet and VCCS PDFDokument5 SeitenRicochet and VCCS PDFVenkatesh MerugaNoch keine Bewertungen

- Projects With Microcontrollers And PICCVon EverandProjects With Microcontrollers And PICCBewertung: 5 von 5 Sternen5/5 (1)

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemVon EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNoch keine Bewertungen

- Digital EditingDokument18 SeitenDigital EditingtesfuNoch keine Bewertungen

- Energ Gy Eff (E Ficient E2Dym T Dyna Mo) R Amic M Routin Mane NG Pro Et On Otocol N-Dema andDokument5 SeitenEnerg Gy Eff (E Ficient E2Dym T Dyna Mo) R Amic M Routin Mane NG Pro Et On Otocol N-Dema andtesfuNoch keine Bewertungen

- Quiz 2Dokument2 SeitenQuiz 2tesfuNoch keine Bewertungen

- A REVIEW: Distributed File System: Original Review By: Shiva Asadianfam, Mahboubeh Shamsi and Shahrad KashanyDokument3 SeitenA REVIEW: Distributed File System: Original Review By: Shiva Asadianfam, Mahboubeh Shamsi and Shahrad KashanytesfuNoch keine Bewertungen

- Java NotesDokument208 SeitenJava NotestesfuNoch keine Bewertungen

- Processing IDE Version 3.1.1: 2. Inkscape Version 0.48.5. Download It From Here: 3. GRBL Controller (Optional)Dokument1 SeiteProcessing IDE Version 3.1.1: 2. Inkscape Version 0.48.5. Download It From Here: 3. GRBL Controller (Optional)tesfuNoch keine Bewertungen

- Handbook of Interconnect Theory and Design Practices. Wiley. New York 2000Dokument1 SeiteHandbook of Interconnect Theory and Design Practices. Wiley. New York 2000tesfuNoch keine Bewertungen

- Power Electronics Chapter 2-2: Applications of Semiconductor DevicesDokument18 SeitenPower Electronics Chapter 2-2: Applications of Semiconductor DevicestesfuNoch keine Bewertungen

- A Trust-Based Approach To Control Privacy Exposure inDokument15 SeitenA Trust-Based Approach To Control Privacy Exposure intesfuNoch keine Bewertungen

- How To ns-2Dokument23 SeitenHow To ns-2tesfuNoch keine Bewertungen

- Tomasulo 2Dokument8 SeitenTomasulo 2tesfuNoch keine Bewertungen

- Unit7-Mobiliy and Handover Management in Mobile NetworksDokument54 SeitenUnit7-Mobiliy and Handover Management in Mobile NetworkstesfuNoch keine Bewertungen

- Electrical Propulsion: Ethiopia Maritime Training InstituteDokument25 SeitenElectrical Propulsion: Ethiopia Maritime Training InstitutetesfuNoch keine Bewertungen

- Lab Exam (Copy)Dokument1 SeiteLab Exam (Copy)tesfu100% (1)

- Line Chart - PassionDokument1 SeiteLine Chart - PassiontesfuNoch keine Bewertungen

- Answers: Project EulerDokument4 SeitenAnswers: Project EulerpallaviNoch keine Bewertungen

- DivyanshDokument21 SeitenDivyanshKhushal JangidNoch keine Bewertungen

- CEH v5 Module 10 Session Hijacking PDFDokument38 SeitenCEH v5 Module 10 Session Hijacking PDFreader onlyNoch keine Bewertungen

- Jannie PR ReportDokument15 SeitenJannie PR ReportJannah Grace Antiporta AbrantesNoch keine Bewertungen

- Chapter 6 Global Marketing Information Systems and ResearchDokument3 SeitenChapter 6 Global Marketing Information Systems and ResearchAvinash JosephNoch keine Bewertungen

- Samp AttachementDokument13 SeitenSamp AttachementJackNoch keine Bewertungen

- JsonDokument6 SeitenJsonLemuel BacliNoch keine Bewertungen

- Sage X3 - User Guide - A Quick Tour of F9 PDFDokument27 SeitenSage X3 - User Guide - A Quick Tour of F9 PDFcaplusincNoch keine Bewertungen

- Active Directory TutorialDokument30 SeitenActive Directory TutorialBadrinath KadamNoch keine Bewertungen

- Contoh Soalan Ulangkaji UAK WAJ 3105Dokument6 SeitenContoh Soalan Ulangkaji UAK WAJ 3105ShareenNoch keine Bewertungen

- XL Miner User GuideDokument420 SeitenXL Miner User GuideMary WilliamsNoch keine Bewertungen

- IBC CHED Basic Calculus WorksheetsDokument37 SeitenIBC CHED Basic Calculus WorksheetsCharleymaine Venus BelmonteNoch keine Bewertungen

- RoboticsDokument24 SeitenRoboticsSuleimAanBinFaizNoch keine Bewertungen

- Cloud Native PythonDokument367 SeitenCloud Native Pythontelecomprofi100% (1)

- Hill CipherDokument3 SeitenHill Cipherchime dolkarNoch keine Bewertungen

- Bloated N4Dokument6 SeitenBloated N4PG ChongNoch keine Bewertungen

- Comandos MikrotikDokument4 SeitenComandos MikrotikDaniel ReynaNoch keine Bewertungen

- Safenet Etoken 5300 PB v9 PDFDokument2 SeitenSafenet Etoken 5300 PB v9 PDFMONTESERBNoch keine Bewertungen

- Wall Mart AssignmentDokument7 SeitenWall Mart AssignmentAishwarya MuraliNoch keine Bewertungen

- 2.4.3 Fiduccia-Mattheyses (FM) AlgorithmDokument25 Seiten2.4.3 Fiduccia-Mattheyses (FM) AlgorithmHaiNguyenNoch keine Bewertungen

- Quantum Supremacy Using A Programmable Superconducting ProcessorDokument12 SeitenQuantum Supremacy Using A Programmable Superconducting ProcessorAlexandre Couto100% (1)

- IT1T1Dokument2 SeitenIT1T1Vyshnavi ThottempudiNoch keine Bewertungen

- Basic Concepts of Probability and Statistics HydrologyDokument14 SeitenBasic Concepts of Probability and Statistics HydrologyShirly Mae Dinong67% (3)